# MITSUBISHI <Dig./Ana.INTERFACE> M62015L,FP M62016L,FP

LOW POWER 2 OUTPUT SYSTEM RESET IC

**PIN CONFIGURATION (TOP VIEW)**

RESET 1

Cd 2

Vcc 3

NC 4

5 Vcc

4 Cd

2 | INT

**Outline 5P5T**

**Outline 8P2S-A**

NC: NO CONNECTION

3 RESET

GND

8 INT

7 GND

6 NC

5 NC

#### DESCRIPTION

The M62015, M62016 are semiconductor integrated circuits whose optimum use is for the detection of the rise and fall in the power supply to a microcomputer system in order to reset or release the microcomputer system.

The M62015, M62016 carry out voltage detection in 2 steps and have 2 output pins. As Bi-CMOS process and low power dissipating circuits are employed, they output optimum signals through each output pin to a system that requires RAM backup.

These ICs also support the backup mode of Mitsubishi microcomputer the M16C.

#### FEATURES

• Bi-CMOS process realizes a configuration of low current dissipating circuits.

Circuit current

Icc=3µA (Typ. , normal mode, Vcc=3.0V)

- Icc=1µA (Typ. , backup mode, Vcc=2.5V)

- Two-step detection of supply voltage Detection voltage in normal mode Vs=2.7V (Typ.) Detection voltage in backup mode VBATT=2.0V (Typ.)

- Two outputs Reset output (RESET) : Output of compulsive reset signal Interruption output (INT) : Output of interruption signal

- Output forms

CMOS output : M62015 Open drain : M62016

#### APPLICATION

Prevention of malfunction of microcomputer systems in electronic, equipment such as OA equipment, industrial equipment, and homeuse electronic appliances.

# MITSUBISHI <Dig./Ana.INTERFACE> M62015L,FP / M62016L,FP

#### LOW POWER 2 OUTPUT SYSTEM RESET IC

### ABSOLUTE MAXIMUM RATINGS (Ta=25°C, unless otherwise noted.)

| Symbol | Parameter             | Conditions | Ratings     | Unit   |

|--------|-----------------------|------------|-------------|--------|

| Vcc    | Supply voltage        |            | 8           | V      |

| Isink  | Output sink voltage   |            | 4           | mA     |

| Pd     | Power dissipation     |            | 440         | mW     |

| Kθ     | Thermal derating      | (Ta 25°C)  | 4.4         | mW/ °C |

| Topr   | Operating temperature |            | -20 to +75  | °C     |

| Tstg   | Storage temperature   |            | -40 to +125 | °C     |

### ELECTRICAL CHARACTERISTICS (Ta=25°C, unless otherwise noted.)

| Symbol         | Parameter                         | Test Conditions                    | Limits |      |      | Unit |

|----------------|-----------------------------------|------------------------------------|--------|------|------|------|

|                |                                   |                                    | Min    | Тур  | Max  | Onic |

| Vs             | Supply voltage                    | Interruption level during Vcc drop | 2.55   | 2.70 | 2.85 | V    |

| VBATT          | Battery voltage                   | Reset level at backup              | 1.85   | 2.00 | 2.15 | V    |

| Vs             | Hysteresis voltage                | Vs=VsH-VsH                         |        | 60   |      | mV   |

| Icc            | Circuit current                   | Vcc=3.0V : In normal mode          |        | 3.0  | 12   | μA   |

|                |                                   | VCC=2.5V : In backup mode          |        | 1.0  | 4.0  | μA   |

| Vsat           | Sink ability                      | VCC=2.5V, Isink=2mA                |        | 0.4  | 0.6  | V    |

| td             | Delay time                        | External capacitance Cd=0.33µF     |        | 50   |      | ms   |

| <b>t</b> RESET | Reset output response time        | When Vcc falling                   |        | 50   |      | μs   |

| tint           | Interruption output response time | When VCC falling                   |        | 40   |      | μs   |

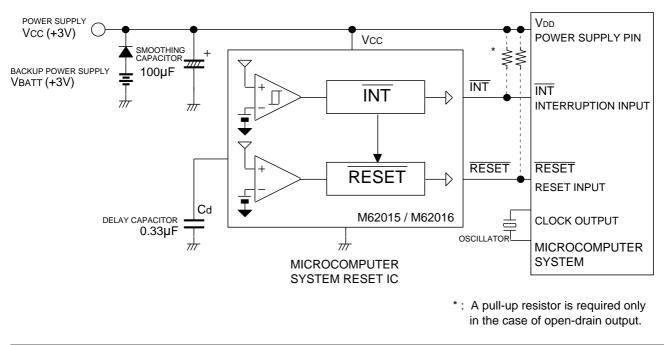

## **APPLICATION EXAMPLE**

# MITSUBISHI <Dig./Ana.INTERFACE> M62015L,FP / M62016L,FP

### LOW POWER 2 OUTPUT SYSTEM RESET IC

### **OPERATION DESCRIPTION**

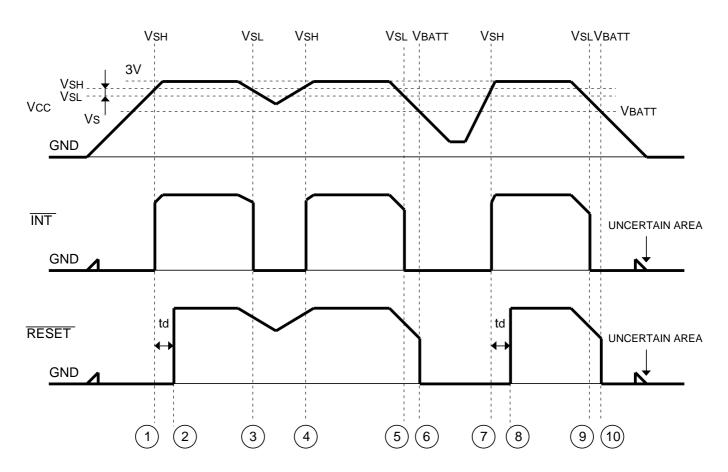

- 1). If VCC rises to VSH(2.76V), the  $\overline{INT}$  output is set to high level.

- 3. If VCC drops to VSH (2.70V), INT goes low.

☆RESET output continues to be held high.

- (4). If VCC returns to VSH, the INT output is set to high level.

5). Same as (3)

$\widehat{6}$  . If VCC becomes lower than VBATT (2.00V), the

RESET output is set to low thereby resetting the microcomputer and initializing system.

- 7

. Same as

1

8

. Same as

2

- 9). Same as (3) and (5)

- (10). Same as (6)