# ML4869

# Medium Current Boost Regulator with Load Disconnect

### GENERAL DESCRIPTION

The ML4869 is a continuous conduction boost regulator designed for DC to DC conversion in multiple cell battery power systems. Continuous conduction allows the regulator to maximize output current for a given inductor. The maximum switching frequency can exceed 200kHz, allowing the use of small, low cost inductors. The ML4869 is capable of start-up with input voltages as low as 1.8V, and is available in 5V and 3.3V output versions with an output voltage accuracy of  $\pm 3\%$ .

An integrated synchronous rectifier eliminates the need for an external Schottky diode and provides a lower forward voltage drop, resulting in higher conversion efficiency. In addition, low quiescent current and variable frequency operation result in high efficiency even at light loads. The ML4869 requires only a few external components to build a very small regulator capable of achieving conversion efficiencies approaching 85%.

The SHDN input allows the user to stop the regulator from switching, and provides complete isolation of the load from the battery.

### **FEATURES**

- Guaranteed full load start-up and operation at 1.8V input

- Continuous conduction mode for high output current

- Pulse Frequency Modulation and internal synchronous rectification for high efficiency

- Isolates the load from the input during shutdown

- Minimum external components

- Low ON resistance internal switching FETs

- Low supply current

- 5V and 3.3V output versions

- Shutdown current = 1µA MAX

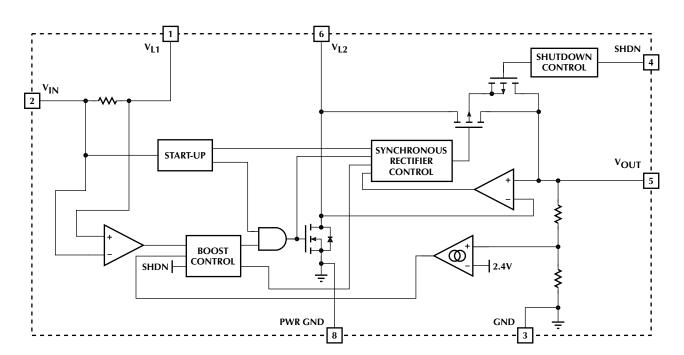

### **BLOCK DIAGRAM**

# ML4869

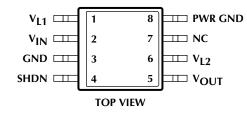

# PIN CONFIGURATION

#### ML4869 8-Pin SOIC (S08)

### PIN DESCRIPTION

| PIN | NAME            | FUNCTION                                                                                        | PIN | NAME             | FUNCTION                              |

|-----|-----------------|-------------------------------------------------------------------------------------------------|-----|------------------|---------------------------------------|

| 1   | $V_{L1}$        | Boost inductor connection                                                                       | 5   | V <sub>OUT</sub> | Boost regulator output                |

| 2   | V <sub>IN</sub> | Battery input voltage                                                                           | 6   | $V_{L2}$         | Boost inductor connection             |

| 3   | GND             | Ground                                                                                          | 7   | NC               | No connection                         |

| 4   | SHDN            | Pulling this pin to V <sub>IN</sub> shuts down the regulator, isolating the load from the input | 8   | PWR GND          | Return for the NMOS output transistor |

# ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

| V <sub>OUT</sub>                           | 7V             |

|--------------------------------------------|----------------|

| Voltage on any other pin GND - 0.3         |                |

| Peak Switch Current (I <sub>PEAK</sub> )   | 2A             |

| Average Switch Current (I <sub>AVG</sub> ) | 1A             |

| Junction Temperature                       | 150°C          |

| Storage Temperature Range                  | –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec)       |                |

| Thermal Resistance $(\theta_{JA})$         | 160°C/W        |

## **OPERATING CONDITIONS**

| Temperature Range   |                                 |

|---------------------|---------------------------------|

| ML4869CS-X          | 0°C to 70°C                     |

| ML4869ES-X          | 20°C to 70°C                    |

| VIN Operating Range | 1.8V to V <sub>OUT</sub> - 0.2V |

# ELECTRICAL CHARACTERISTICS

Unless otherwise specified,  $V_{IN}$  = Operating Voltage Range,  $T_A$  = Operating Temperature Range (Note 1)

| SYMBOL              | PARAMETER                                    | CONDITI                                            | IONS                        | MIN        | ТҮР        | MAX        | UNITS    |

|---------------------|----------------------------------------------|----------------------------------------------------|-----------------------------|------------|------------|------------|----------|

| SUPPLY              | 1                                            | ł                                                  |                             |            |            |            | -        |

| I <sub>IN(Q)</sub>  | V <sub>IN</sub> Quiescent Current            | $V_{IN} = V_{OUT} - 0.2V, S$                       | SHDN = 0V                   |            | 3          | 6          | μΑ       |

|                     |                                              | $V_{IN} = SHDN = 2.4V$                             | , $V_{OUT} = 0V$            |            | 0.3        | 1          | μΑ       |

| I <sub>OUT(Q)</sub> | V <sub>OUT</sub> Quiescent Current SHDN = 0V |                                                    |                             | 25         | 35         | μΑ         |          |

|                     |                                              | $V_{IN} = SHDN = 2.4V$<br>$V_{OUT} = V_{OUT(NOM)}$ |                             |            | 14         | 20         | μΑ       |

| PFM REGL            | JLATOR                                       |                                                    |                             |            |            |            |          |

| I <sub>PEAK</sub>   | I <sub>L</sub> Peak Current                  | VIN = 2.4V                                         | –3 Suffix<br>–5 Suffix      | 700<br>750 | 800<br>850 | 900<br>950 | mA<br>mA |

| V <sub>OUT</sub>    | Output Voltage                               | $I_{OUT} = 0$                                      | -3 Suffix                   | 3.30       | 3.35       | 3.40       | V        |

|                     |                                              | See Figure 1                                       | -5 Suffix                   | 4.95       | 5.05       | 5.15       | V        |

|                     | Load Regulation                              | -3 Suffix, V <sub>IN</sub> = 2.4V                  | ', I <sub>OUT</sub> = 310mA | 3.20       | 3.25       | 3.40       | V        |

|                     |                                              | -5 Suffix, $V_{IN} = 2.4V$                         | ', I <sub>OUT</sub> = 185mA | 4.85       | 4.95       | 5.15       | V        |

| SHUTDOW             | -<br>WN                                      |                                                    |                             |            |            |            |          |

|                     |                                              |                                                    |                             |            |            |            |          |

| VIL             | Input Low Voltage  |                       | 0.5 | V  |

|-----------------|--------------------|-----------------------|-----|----|

| $V_{\text{IH}}$ | Input High Voltage | V <sub>IN</sub> - 0.5 |     | V  |

|                 | Input Bias Current | -100                  | 100 | nA |

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

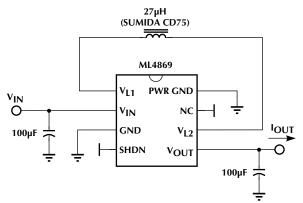

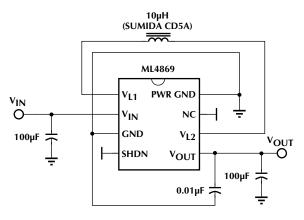

Figure 1. Application Test Circuit

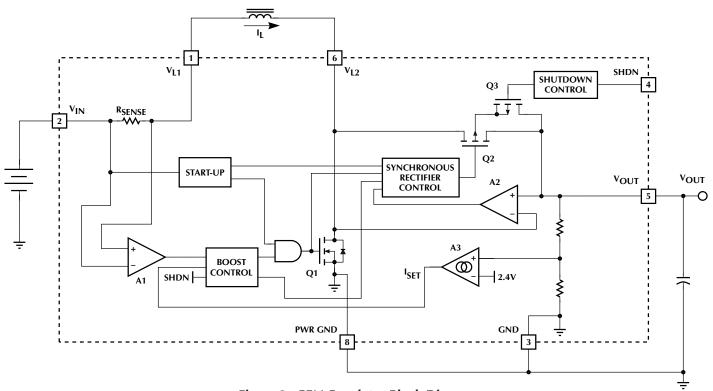

Figure 2. PFM Regulator Block Diagram

Micro Linear

# FUNCTIONAL DESCRIPTION

The ML4869 combines a unique form of current mode control with a synchronous rectifier to create a boost converter that can deliver high currents while maintaining high efficiency. Current mode control allows the use of a very small high frequency inductor and output capacitor. Synchronous rectification replaces the conventional external Schottky diode with an on-chip P-channel MOSFET to reduce losses, eliminate an external component, and provide the means for load disconnect. Also included on-chip are an N-channel MOSFET main switch and a current sense resistor.

#### **REGULATOR OPERATION**

The ML4869 is a variable frequency, current mode switching regulator. Its unique control scheme converts efficiently over more than three decades of load current. A block diagram of the boost converter including the key external components is shown in Figure 2.

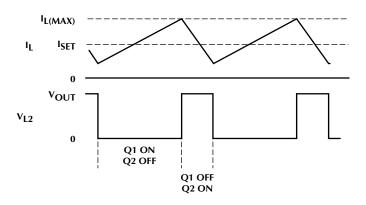

Error amp A3 converts deviations in the desired output voltage to a small current,  $I_{SET}$ . The inductor current is measured through a current sense resistor ( $R_{SENSE}$ ) which is amplified by A1. The boost control block matches the average inductor current to a multiple of the  $I_{SET}$  current by switching Q1 on and off. The peak inductor current is limited by the controller to about 650mA.

At light loads,  $I_{SET}$  will momentarily reach zero after an inductor discharge cycle , causing Q1 to stop switching. Depending on the load, this idle time can extend to tenths of seconds. When the circuit is not switching, only 25µA of supply current is drawn from the output. This allows the part to remain efficient even when the load current drops below 250µA.

Amplifier A2 and the PMOS transistor Q2 work together to form a low forward drop diode. When transistor Q1 turns off, the current flowing in the inductor causes  $V_{L2}$  to go high. As the voltage on  $V_{L2}$  rises above  $V_{OUT}$ , amplifier A2 allows the PMOS transistor Q2 to turn on. In discontinuous operation, (where I<sub>L</sub> always returns to zero), A2 uses the resistive drop across the PMOS switch Q2 to sense zero inductor current and turns the PMOS switch off. In continuous operation, the PMOS turn off point is independent of A2 and is determined by the boost control circuitry.

Typical continuous mode inductor current and voltage waveforms are shown in Figure 3.

#### SHUTDOWN

The ML4869 output can be shut down by pulling the SHDN pin high (to  $V_{IN}$ ). When SHDN is high, the regulator stops switching, the control circuitry is powered down, and the body diode of the PMOS synchronous rectifier is disconnected from the output. By switching Q1, Q2, and Q3 off, the load is isolated from the input. This allows the output voltage to be independent of the input while in shutdown.

# DESIGN CONSIDERATIONS

#### OUTPUT CURRENT CAPABILITY

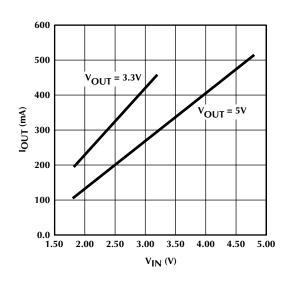

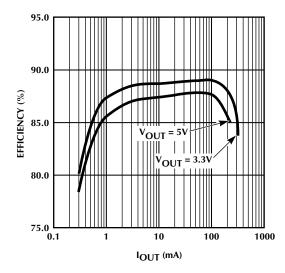

The maximum current available at the output of the regulator is related to the maximum inductor current by the ratio of the input to output voltage and the conversion efficiency. The maximum inductor current is limited by the boost converter to about 650mA. The conversion efficiency is determined mainly by the internal switches as well as the external components, but can be estimated at about 80%. The maximum average output current can be estimated by using the typical performance curves shown in Figures 4 and 5, or by calculation using the following equations:

$$I_{OUT(5V)} = 0.686 \times \left(\frac{V_{IN(MIN)}}{5V}\right) - 0.144A$$

(1)

$$I_{OUT(3.3V)} = 0.619 \times \left(\frac{V_{IN(MIN)}}{3.3V}\right) - 0.144A$$

(2)

Since the maximum output current is based on when the inductor current goes into current limit, it is not recommended to operate the ML4869 at the maximum output current continuously. Applications that have high transient load currents should be evaluated under worst case conditions to determine suitability.

#### **INDUCTOR SELECTION**

The ML4869 is able to operate over a wide range of inductor values. A value of  $10\mu$ H is a good choice, but any value between  $5\mu$ H and  $33\mu$ H is acceptable. As the inductor value changes, the control circuitry will automatically adjust to keep the inductor current under control. Choosing an inductance value of less than  $10\mu$ H will reduce the component's footprint, but the efficiency and maximum output current may drop.

It is important to use an inductor that is rated to handle 1.0A peak currents without saturating. Also choose an inductor with low winding resistance. A good rule of thumb is to allow 5 to  $10m\Omega$  of resistance for each  $1\mu$ H of inductance.

The final selection of the inductor will be based on tradeoffs between size, cost and efficiency. Inductor tolerance, core and copper loss will vary with the type of inductor selected and should be evaluated with a ML4869 under worst case conditions to determine its suitability.

Several manufacturers supply standard inductance values in surface mount packages:

| Coilcraft   | (847) 639-6400 |

|-------------|----------------|

| Coiltronics | (561) 241-7876 |

| Dale        | (605) 665-9301 |

| Sumida      | (847) 956-0666 |

### DESIGN CONSIDERATIONS (Continued)

### OUTPUT CAPACITOR

The output capacitor filters the pulses of current from the switching regulator. Since the switching frequency will vary with inductance, the minimum output capacitance required to reduce the output ripple to an acceptable level will be a function of the inductor used. Therefore, to maintain an output voltage with less than 100mV of ripple at full load current, use the following equation:

$$C_{OUT} = \frac{44 \times L}{V_{OUT}}$$

(3)

The output capacitor's Equivalent Series Resistance (ESR) and Equivalent Series Inductance (ESL), also contribute to the ripple. Just after the Q1 turns off, the current in the output capacitor ramps quickly to between 0.3A and

0.9A. This fast change in current through the capacitor's ESL causes a high frequency (5ns) spike to appear on the output. After the ESL spike settles, the output still has a ripple component equal to the product of inductor discharge current and the ESR. To minimize these effects, choose an output capacitor with less than 10nH of ESL and less than 100m $\Omega$  of ESR.

Suitable tantalum capacitors can be obtained from the following vendors:

| AVX     | (207) 282-5111 |  |  |

|---------|----------------|--|--|

| Kemet   | (846) 963-6300 |  |  |

| Sprague | (207) 324-4140 |  |  |

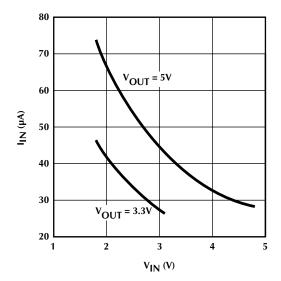

Figure 4. I<sub>OUT</sub> vs. V<sub>IN</sub> Using the Circuit of Figure 8

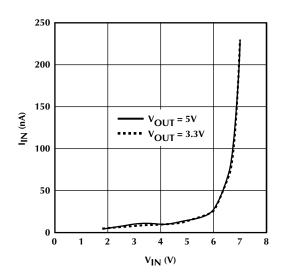

Figure 6. Input Leakage vs. V<sub>IN</sub> in Shutdown

Micro Linear

Figure 5. Efficiency vs. I<sub>OUT</sub> Using the Circuit of Figure 8

# DEISGN CONSIDERATIONS (Continued)

In applications where the ML4869 is operated at or near the maximum output current, it is recommended to add a 10nF to 100nF ceramic or film capacitor from  $V_{OUT}$  to GND. The optimum value of the high frequency bypass capacitor is dependent on the layout and the value of the bulk output capacitor selected.

### INPUT CAPACITOR

Due to the high input current drawn at startup and possibly during operation, it is recommended to decouple the input with a capacitor with a value of  $47\mu$ F to  $100\mu$ F. This filtering prevents the input ripple from affecting the ML4869 control circuitry, and also improves the efficiency by reducing the I<sup>2</sup>R losses during the charge cycle of the inductor. Again, a low ESR capacitor (such as tantalum) is recommended.

It is also recommended that low source impedance batteries be used. Otherwise, the voltage drop across the source impedance during high input current situations will cause the ML4869 to fail to startup or to operate unreliably. In general, for two cell applications the source impedance should be less than  $400 \text{m}\Omega$ , which means that small alkaline cells should be avoided.

### SHUTDOWN

To guarantee proper operation, SHDN must be pulled to within 0.5V of GND or  $V_{\rm IN}$  to prevent excessive power dissipation and possible oscillations. A graph of input leakage current while in shutdown is shown in Figure 6.

# LAYOUT

Good layout practices will ensure the proper operation of the ML4869. Some layout guidelines follow:

- Use adequate ground and power traces or planes

- Keep components as close as possible to the ML4869

- Use short trace lengths from the inductor to the  $V_{L1}$  and  $V_{L2}$  pins and from the output capacitor to the  $V_{OUT}$  pin

- Use a single point ground for the ML4869 PWR GND pin and the input and output capacitors, and connect the GND pin to PWR GND using a separate trace

- Separate the ground for the converter circuitry from the ground of the load circuitry and connect at a single point

Figure 8. Design Example Schematic Diagram

# DESIGN EXAMPLE

In order to design a boost converter using the ML4869, it is necessary to define the values of a few parameters. For this example, we have assumed that  $V_{IN} = 3.0V$  to 3.6V,  $V_{OUT} = 5.0V$ , and  $I_{OUT(MAX)} = 250$ mA

First, it must be determined whether the ML4869 is capable of delivering the output current. This is done using Equation 1:

$$I_{OUT(5V)} = 0.686 \times \left(\frac{V_{IN(MIN)}}{5V}\right) - 0.267A$$

Next, select an inductor:

As previously mentioned, it is the recommended inductance is  $10\mu$ H. Make sure that the peak current rating of the inductor is at least 1.0A, and that the DC resistance of the inductor is in the range of 50 to 100m $\Omega$ .

Finally, the value of the output capacitor is determined using Equation 3:

$$C_{OUT} = \frac{44 \times 10\mu H}{5.0V} = 88\mu F$$

The closest standard value would be a  $100\mu$ F capacitor with an ESR rating of  $100m\Omega$ . If such a low ESR value cannot be found, two  $47\mu$ F capacitors in parallel could also be used.

The complete circuit is shown in Figure 8. As mentioned previously, the use of an input supply bypass capacitor is strongly recommended.

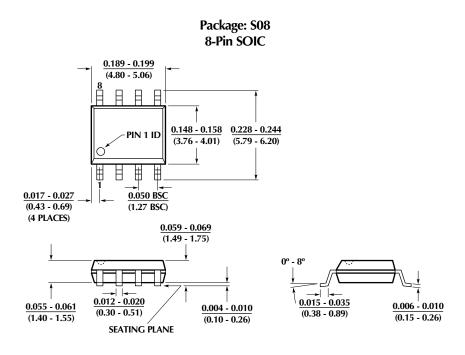

### PHYSICAL DIMENSIONS inches (millimeters)

### ORDERING INFORMATION

| PART NUMBER | OUTPUT VOLTAGE | E TEMPERATURE RANGE PACKA |                  |

|-------------|----------------|---------------------------|------------------|

| ML4869CS-3  | 3.3V           | 0°C to 70°C               | 8-Pin SOIC (S08) |

| ML4869CS-5  | 5V             | 0°C to 70°C               | 8-Pin SOIC (S08) |

| ML4869ES-3  | 3.3V           | -20°C to 70°C             | 8-Pin SOIC (S08) |

| ML4869ES-5  | 5V             | -20°C to 70°C             | 8-Pin SOIC (S08) |

#### DS4869-01

© Micro Linear 1998. 🕸 Micro Linear is a registered trademark of Micro Linear Corporation. All other trademarks are the property of their respective owners.

Products described herein may be covered by one or more of the following U.S. patents: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,565,761; 5,592,128; 5,594,376; 5,652,479; 5,661,427; 5,663,874; 5,672,959; 5,689,167; 5,714,897; 5,717,798; 5,742,151; 5,747,977; 5,754,012; 5,757,174; 5,767,653; Japan: 2,598,946; 2,619,299; 2,704,176. Other patents are pending.

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or design. Micro Linear does not assume any liability arising out of the application or use of any product described herein, neither does it convey any license under its patent right nor the rights of others. The circuits contained in this data sheet are offered as possible applications only. Micro Linear makes no warranties or representations as to whether the illustrated circuits infringe any intellectual property rights of others, and will accept no responsibility or liability for use of any application herein. The customer is urged to consult with appropriate legal coursel before deciding on a particular application.

2092 Concourse Drive San Jose, CA 95131 Tel: (408) 433-5200 Fax: (408) 432-0295 www.microlinear.com

04/1/99 Printed in U.S.A.