# **MOSEL VITELIC**

# V61C51161024 64K x 16 HIGH SPEED STATIC RAM

### Features

- High-speed: 10, 12, 15 ns

- All inputs and outputs directly TTL compatible

- Three state outputs

- Byte Control Pins

- Single 5V ± 10% Power Supply

- Packages

- 44-pin TSOP (Standard)

- 44-pin 400 mil SOJ

## Description

The V61C51161024 is a 1,048,576-bit static random-access memory organized as 65,536 words by 16 bits. Inputs and three-state outputs are TTL compatible and allow for direct interfacing with common system bus structures.

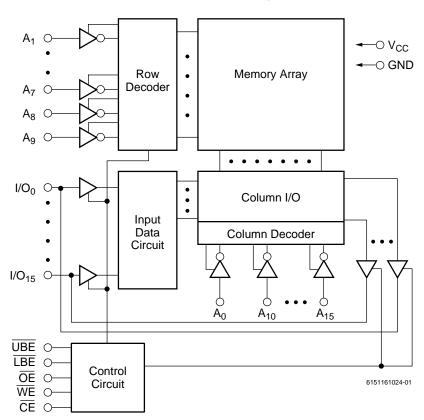

# Functional Block Diagram

# Device Usage Chart

| Operating<br>Temperature | Package Outline |   | A  | ccess Time (n | Temperature |       |  |

|--------------------------|-----------------|---|----|---------------|-------------|-------|--|

| Range                    | Т               | к | 10 | 12            | 15          | Mark  |  |

| 0°C to 70 °C             | •               | • | •  | •             | •           | Blank |  |

## Pin Descriptions

## A<sub>0</sub>-A<sub>15</sub> Address Inputs

These 16 address inputs select one of the 64K x 16 bit segments in the RAM.

## **CE** Chip Enable Input

CE is active LOW. It must be active to read from or write to the device. If chip enable is not active, the device is deselected and is in a standby power mode. The I/O pins will be in the high-impedance state when deselected.

### OE Output Enable Input

The output enable input is active LOW. When  $\overline{OE}$  is Low with  $\overline{CE}$  Low and  $\overline{WE}$  High, data will be presented on the I/O pins. The I/O pins will be in the high impedance state when  $\overline{OE}$  is High.

## UBE, LEB Byte Enable

Active low inputs. These inputs are used to enable the upper or lower data byte.

## WE Write Enable Input

The write enable input is active LOW and controls read and write operations. With the chip enabled, when  $\overline{WE}$  is HIGH and  $\overline{OE}$  is LOW, output data will be present at the I/O pins; when  $\overline{WE}$  is LOW and  $\overline{OE}$  is HIGH, the data present on the I/O pins will be written into the selected memory locations.

I/O<sub>0</sub>-I/O<sub>15</sub> Data Input and Data Output Ports These 16 bidirectional ports are used to read data from and write data into the RAM.

V<sub>CC</sub> Power Supply

GND Ground

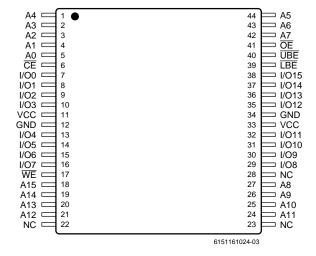

# Pin Configurations (Top View)

# 44-Pin SOJ

#### □ A<sub>6</sub> 43 42 □ ŌE □ ŪBE CE d 39 ☐ LBE 38 | I/O<sub>15</sub> I/O₁ □ 8 □ I/O<sub>14</sub> 36 | I/O<sub>13</sub> I/O<sub>3</sub> 🖂 10 I/O₁₂ V<sub>CC</sub> □ 11 34 GND GND 🖂 12 33 □ V<sub>CC</sub> I/O<sub>4</sub> 🔲 13 □ I/O<sub>11</sub> I/O<sub>5</sub> 🖂 14 31 | I/O<sub>10</sub> I/O<sub>6</sub> 🖂 15 30 | I/O<sub>9</sub> □ I/O<sub>8</sub> 29 WE $\square$ 28 □ NC A<sub>15</sub> □ 27 □ A<sub>9</sub> A<sub>14</sub> 🔲 19 26 A<sub>13</sub> □ $\Box$ A<sub>10</sub> $\Box$ $A_{11}$ A<sub>12</sub> □ 21 NC [ 23 ¬ NC 6151161024-02

### 44-Pin TSOP-II (Standard)

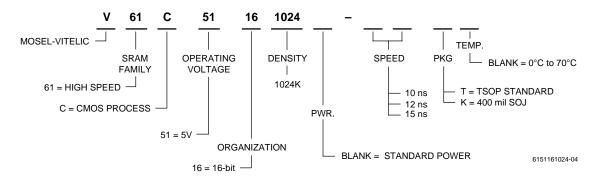

## **Part Number Information**

# Absolute Maximum Ratings (1)

| Symbol            | Parameter                    | Commercial            | Units |

|-------------------|------------------------------|-----------------------|-------|

| V <sub>CC</sub>   | Supply Voltage               | -0.5 to +7            | V     |

| V <sub>IN</sub>   | Input Voltage                | -0.5 to +7            | V     |

| $V_{DQ}$          | Input/Output Voltage Applied | V <sub>CC</sub> + 0.5 | V     |

| T <sub>BIAS</sub> | Temperature Under Bias       | -10 to +85            | °C    |

| T <sub>STG</sub>  | Storage Temperature          | -65 to +150           | °C    |

### NOTE:

1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

$\textit{Capacitance*} \ T_A = 25^{\circ}C, \, f = 1.0 MHz$

| Symbol           | Parameter          | Conditions            | Max. | Unit |

|------------------|--------------------|-----------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{IN} = 0V$         | 6    | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>I/O</sub> = 0V | 8    | pF   |

### NOTE:

1. This parameter is guaranteed by design and not tested.

# Truth Table

| Mode           | CE | ŌĒ | WE | UBE | LBE | I/O <sub>8-15</sub><br>Operation | I/O <sub>0-7</sub><br>Operation |

|----------------|----|----|----|-----|-----|----------------------------------|---------------------------------|

| Standby        | Н  | Х  | Х  | Х   | Х   | High Z                           | High Z                          |

| Output Disable | L  | Х  | Х  | Н   | Н   | High Z                           | High Z                          |

| Output Disable | L  | Н  | Н  | Х   | Х   | High Z                           | High Z                          |

| Read           | L  | L  | Н  | L   | L   | D <sub>OUT</sub>                 | D <sub>OUT</sub>                |

| Read           | L  | L  | Н  | L   | Н   | D <sub>OUT</sub>                 | High Z                          |

| Read           | L  | L  | Н  | Н   | L   | High Z                           | D <sub>OUT</sub>                |

| Write          | L  | Х  | L  | L   | L   | D <sub>IN</sub>                  | D <sub>IN</sub>                 |

| Write          | L  | Х  | L  | L   | Н   | D <sub>IN</sub>                  | High Z                          |

| Write          | L  | Х  | L  | Н   | L   | High Z                           | D <sub>IN</sub>                 |

NOTE:

X = Don't Care, L = LOW, H = HIGH

# **DC Electrical Characteristics** (over all temperature ranges, $V_{CC} = 5V \pm 10\%$ )

| •                |                                              |                                                                                          | -10  |      | -10 -12 |      | -15  |      |       |

|------------------|----------------------------------------------|------------------------------------------------------------------------------------------|------|------|---------|------|------|------|-------|

| Symbol           | Parameter                                    | Test Conditions                                                                          | Min. | Max. | Min.    | Max. | Min. | Max. | Units |

| I <sub>IL</sub>  | Input Leakage Current                        | $V_{CC} = MAX$ , $V_{IN} = GND$ to $V_{CC}$                                              | _    | 5    | _       | 5    | _    | 5    | μΑ    |

| I <sub>OL</sub>  | Output Leakage Current                       | $\overline{CE} = V_{IH}, V_{CC} = Max,$ $V_{OUT} = GND \text{ to } V_{CC}$               | _    | 5    | _       | 5    | 1    | 5    | μА    |

| lcc              | Operating Power Supply<br>Current            | $\overline{CE} = V_{IL}$ , $I_{OUT} = 0$ , $f = f_{max}$                                 | _    | 220  | _       | 210  | _    | 200  | mA    |

| ISB              | Standby Power Supply<br>Current (TTL Level)  | $\overline{CE} = V_{IH}, f = f_{max}$                                                    | _    | 60   | _       | 50   | _    | 40   | mA    |

| I <sub>SB1</sub> | Standby Power Supply<br>Current (CMOS Level) | $\overline{CE} \ge V_{CC} - 0.2V, f = 0, V_{IN} \le 0.2V$<br>or $V_{IN} > V_{CC} - 0.2V$ | _    | 5.0  | _       | 5.0  | _    | 5.0  | mA    |

| V <sub>OL</sub>  | Output Low Voltage                           | I <sub>OL</sub> = 8mA                                                                    | _    | 0.4  | _       | 0.4  | _    | 0.4  | V     |

| V <sub>OH</sub>  | Output High Voltage                          | I <sub>OH</sub> = -4mA                                                                   | 2.4  | _    | 2.4     | _    | 2.4  | _    | V     |

### NOTES:

- 1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

- 2.  $V_{IL}$  (Min.) = -3.0V for pulse width < 20ns.

- 3.  $f_{MAX} = 1/t_{RC}$ .

- 4. Maximum values.

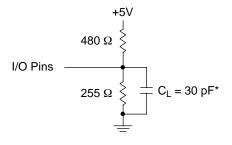

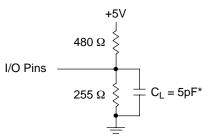

# **AC Test Conditions**

| Input Pulse Levels        | 0 to 3V   |

|---------------------------|-----------|

| Input Rise and Fall Times | 3 ns      |

| Timing Reference Levels   | 1.5V      |

| Output Load               | see below |

# Key to Switching Waveforms

| WAVEFORM | INPUTS                                 | OUTPUTS                                            |

|----------|----------------------------------------|----------------------------------------------------|

|          | MUST BE<br>STEADY                      | WILL BE<br>STEADY                                  |

|          | MAY CHANGE<br>FROM H TO L              | WILL BE<br>CHANGING<br>FROM H TO L                 |

|          | MAY CHANGE<br>FROM L TO H              | WILL BE<br>CHANGING<br>FROM L TO H                 |

|          | DON'T CARE:<br>ANY CHANGE<br>PERMITTED | CHANGING:<br>STATE<br>UNKNOWN                      |

|          | DOES NOT<br>APPLY                      | CENTER<br>LINE IS HIGH<br>IMPEDANCE<br>"OFF" STATE |

# AC Test Loads and Waveforms

for  $t_{\text{CLZ}}$ ,  $t_{\text{CHZ}}$ ,  $t_{\text{OLZ}}$ ,  $t_{\text{WHZ}}$ ,  $t_{\text{OW}}$ , and  $t_{\text{OHZ}}$

\* Includes scope and jig capacitance

6151161024-05

# AC Electrical Characteristics

(over all temperature ranges)

# Read Cycle

| Parameter        |                                    | -1   | -10  |      | 12   | -15  |      |      |

|------------------|------------------------------------|------|------|------|------|------|------|------|

| Name             | Parameter                          | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

| t <sub>RC</sub>  | Read Cycle Time                    | 10   | _    | 12   | _    | 15   | _    | ns   |

| t <sub>AA</sub>  | Address Access Time                | _    | 10   | _    | 12   | _    | 15   | ns   |

| t <sub>ACS</sub> | Chip Enable Access Time            | _    | 10   | _    | 12   | _    | 15   | ns   |

| t <sub>BA</sub>  | UBE, LBE Access Time               | _    | 5    | _    | 6    | _    | 7    | ns   |

| t <sub>OE</sub>  | Output Enable to Output Valid      | _    | 5    | _    | 6    | _    | 7    | ns   |

| t <sub>CLZ</sub> | Chip Enable to Output in Low Z     | 0    | _    | 0    | _    | 0    | _    | ns   |

| t <sub>BLZ</sub> | UBE, LBE to Output in Low Z        | 0    | _    | 0    | _    | 0    | _    | ns   |

| t <sub>OLZ</sub> | Output Enable to Output in Low Z   | 0    | _    | 0    | _    | 0    | _    | ns   |

| t <sub>CHZ</sub> | Chip Disable to Output in High Z   | 0    | 5    | 0    | 6    | 0    | 7    | ns   |

| t <sub>OHZ</sub> | Output Disable to Output in High Z | 0    | 5    | 0    | 6    | 0    | 7    | ns   |

| t <sub>BHZ</sub> | UBE, LBE to Output in High Z       | 0    | 5    | 0    | 6    | 0    | 7    | ns   |

| t <sub>OH</sub>  | Output Hold from Address Change    | 2    | _    | 3    | _    | 3    | _    | ns   |

# **Write Cycle**

| Parameter        |                               | -1   | 10   | -12  |      | -15  |      |      |  |

|------------------|-------------------------------|------|------|------|------|------|------|------|--|

| Name             | Parameter                     | Min. | Max. | Min. | Max. | Min. | Max. | Unit |  |

| t <sub>WC</sub>  | Write Cycle Time              | 10   | _    | 12   | _    | 15   | _    | ns   |  |

| t <sub>CW</sub>  | Chip Enable to End of Write   | 7    | _    | 8    | _    | 10   | _    | ns   |  |

| t <sub>AS</sub>  | Address Setup Time            | 0    | _    | 0    | _    | 0    | _    | ns   |  |

| t <sub>AW</sub>  | Address Valid to End of Write | 7    | _    | 8    | _    | 10   | _    | ns   |  |

| t <sub>WP</sub>  | Write Pulse Width             | 7    | _    | 8    | _    | 10   | _    | ns   |  |

| t <sub>WR</sub>  | Write Recovery Time           | 0    | _    | 0    | _    | 0    | _    | ns   |  |

| t <sub>WHZ</sub> | Write to Output High-Z        | 0    | 5    | 0    | 6    | 0    | 7    | ns   |  |

| t <sub>WLZ</sub> | Write to Output Low Z         | 3    | _    | 3    | _    | 5    | _    | ns   |  |

| t <sub>DW</sub>  | Data Setup to End of Write    | 5    | _    | 6    | _    | 7    | _    | ns   |  |

| t <sub>DH</sub>  | Data Hold from End of Write   | 0    | _    | 0    | _    | 0    | _    | ns   |  |

| t <sub>BW</sub>  | UBE, LBE to End of Write      | 7    | _    | 8    | _    | 10   | _    | ns   |  |

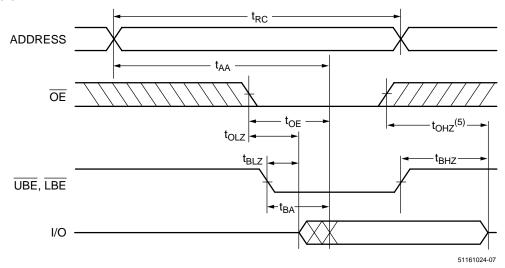

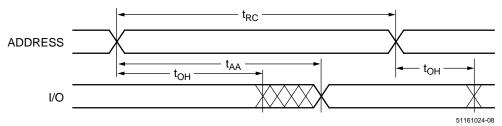

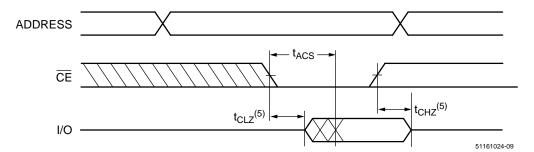

# Switching Waveforms (Read Cycle)

# Read Cycle 1<sup>(1, 2)</sup>

# Read Cycle 2<sup>(1, 2, 4)</sup>

# Read Cycle 3<sup>(1, 3, 4)</sup>

## NOTES:

- $\overline{OE} = V_{1L}$ .

Transition is measured ±500mV from steady state with  $C_L = 5pF$ . This parameter is guaranteed and not 100% tested.

- $\overline{\mathsf{UBE}} = \mathsf{V}_{\mathsf{IL}}, \, \overline{\mathsf{LBE}} = \mathsf{V}_{\mathsf{IL}}.$

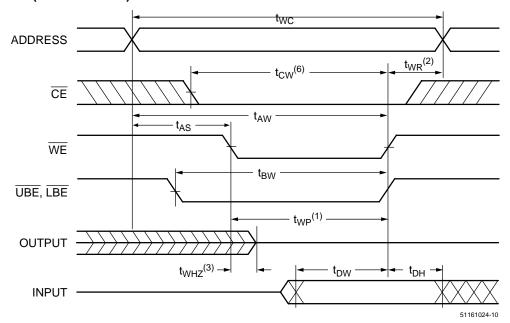

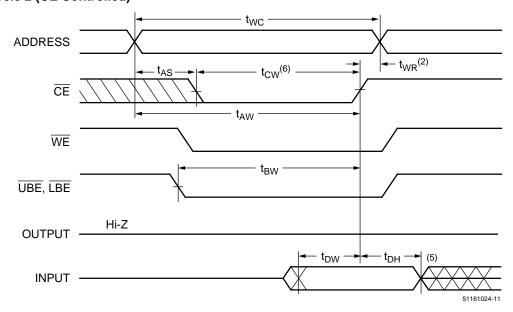

# Switching Waveforms (Write Cycle)

# Write Cycle 1 (WE Controlled)(4)

# Write Cycle 2 (CE Controlled)(4)

### NOTES:

- The internal write time of the memory is defined by the overlap of \(\overlap{\overlap}{\overlap}\) active and \(\overlap{\overlap}{\overlap}\) low. All signals must be active to initiate and any one signal can terminate a write by going inactive. The data input setup and hold timing should be referenced to the second transition edge of the signal that terminates the write.

- 2.  $t_{WR}$  is measured from the earlier of  $\overline{CE}$  or  $\overline{WE}$  going high.

- 3. During this period, I/O pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.

- 4.  $\overline{OE} = V_{IL}$  or  $V_{IH}$ . However it is recommended to keep  $\overline{OE}$  at  $V_{IH}$  during write cycle to avoid bus contention.

- 5. If CE is LOW during this period, I/O pins are in the output state. Then the data input signals of opposite phase to the outputs must not be applied to them.

- 6.  $t_{CW}$  is measured from  $\overline{CE}$  going low to the end of write.

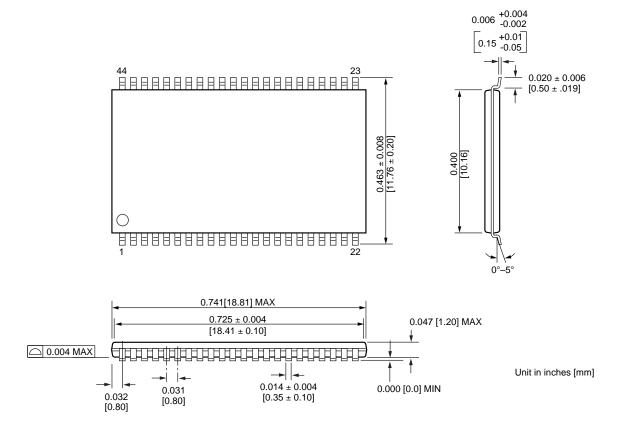

# Package Diagrams

# 44-pin 400 mil TSOP-II

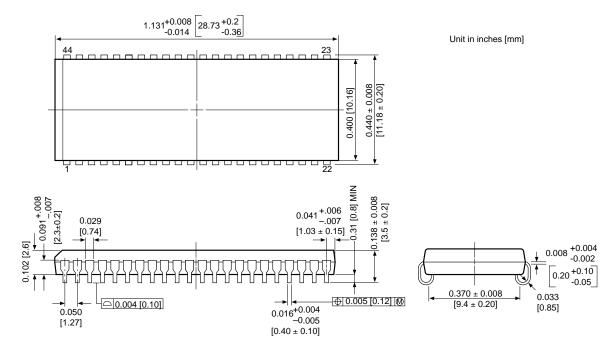

# Package Diagrams

# 44-pin 400 mil SOJ (450 mil pin-to-pin)

## **MOSEL VITELIC**

### **WORLDWIDE OFFICES**

### V61C51161024

### U.S.A.

3910 NORTH FIRST STREET SAN JOSE, CA 95134 PHONE: 408-433-6000 FAX: 408-433-0185

### **HONG KONG**

19 DAI FU STREET TAIPO INDUSTRIAL ESTATE TAIPO, NT, HONG KONG PHONE: 852-2665-4883 FAX: 852-2664-7535

### TAIWAN

7F, NO. 102 MIN-CHUAN E. ROAD, SEC. 3 TAIPEI

PHONE: 886-2-2545-1213 FAX: 886-2-2545-1209

1 CREATION ROAD I SCIENCE BASED IND. PARK HSIN CHU, TAIWAN, R.O.C. PHONE: 886-3-578-3344 FAX: 886-3-579-2838

### **JAPAN**

WBG MARINE WEST 25F 6, NAKASE 2-CHOME MIHAMA-KU, CHIBA-SHI CHIBA 261-71

PHONE: 81-43-299-6000 FAX: 81-43-299-6555

### **IRELAND & UK**

BLOCK A UNIT 2 BROOMFIELD BUSINESS PARK MALAHIDE CO. DUBLIN, IRELAND

PHONE: +353 1 8038020 FAX: +353 1 8038049

### GERMANY (CONTINENTAL EUROPE & ISRAEL)

71083 HERRENBERG BENZSTR. 32 GERMANY

PHONE: +49 7032 2796-0 FAX: +49 7032 2796 22

## U.S. SALES OFFICES

### **NORTHWESTERN**

3910 NORTH FIRST STREET SAN JOSE, CA 95134 PHONE: 408-433-6000 FAX: 408-433-0185

### **NORTHEASTERN**

SUITE 436 20 TRAFALGAR SQUARE NASHUA, NH 03063 PHONE: 603-889-4393 FAX: 603-889-9347

### **SOUTHWESTERN**

SUITE 200 5150 E. PACIFIC COAST HWY. LONG BEACH, CA 90804 PHONE: 562-498-3314 FAX: 562-597-2174

### **CENTRAL & SOUTHEASTERN**

604 FIELDWOOD CIRCLE RICHARDSON, TX 75081 PHONE: 972-690-1402 FAX: 972-690-0341

© Copyright 1997, MOSEL VITELIC Inc.

7/98 Printed in U.S.A.

The information in this document is subject to change without notice.

MOSEL VITELIC makes no commitment to update or keep current the information contained in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of MOSEL-VITELIC.

MOSEL VITELIC subjects its products to normal quality control sampling techniques which are intended to provide an assurance of high quality products suitable for usual commercial applications. MOSEL VITELIC does not do testing appropriate to provide 100% product quality assurance and does not assume any liability for consequential or incidental arising from any use of its products. If such products are to be used in applications in which personal injury might occur from failure, purchaser must do its own quality assurance testing appropriate to such applications.