# Quad EIA-422/423 Line Receiver

Motorola's Quad EIA-422/3 Receiver features four independent receiver chains which comply with EIA Standards for the Electrical Characteristics of Balanced/Unbalanced Voltage Digital Interface Circuits. Receiver outputs are 74LS compatible, three-state structures which are forced to a high impedance state when the appropriate output control pin reaches a logic zero condition. A PNP device buffers each output control pin to assure minimum loading for either logic one or logic zero inputs. In addition, each receiver chain has internal hysteresis circuitry to improve noise margin and discourage output instability for slowly changing input waveforms. A summary of MC3486 features include:

- Four Independent Receiver Chains

- Three-State Outputs

- High Impedance Output Control Inputs (PIA Compatible)

- Internal Hysteresis 30 mV (Typical) @ Zero Volts Common Mode

- Fast Propagation Times 25 ns (Typical)

- TTL Compatible

- Single 5.0 V Supply Voltage

- DS 3486 Provides Second Source

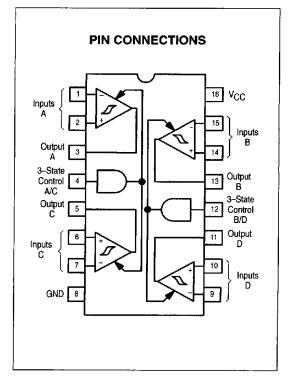

# Receiver Chain Block Diagram Three-State Control Input Input Network Hysteresis Level Translator Amplifier Amplifier

# MC3486

# QUAD EIA-422/3 LINE RECEIVER WITH THREE-STATE OUTPUTS

SEMICONDUCTOR TECHNICAL DATA

D SUFFIX

PLASTIC PACKAGE

CASE 751B

(SO-16)

P SUFFIX PLASTIC PACKAGE CASE 648

### **ORDERING INFORMATION**

| Device  | Operating<br>Temperature Range | Package     |

|---------|--------------------------------|-------------|

| MC3486P | T 0 to 170°C                   | Plastic DIP |

| MC3486D | T <sub>A</sub> = 0 to +70°C    | SO-16       |

6367253 0097836 145

7-86

**MOTOROLA ANALOG IC DEVICE DATA**

### **MAXIMUM RATINGS**

| Rating                            | Symbol | Value       | Unit<br>Vdc |  |

|-----------------------------------|--------|-------------|-------------|--|

| Power Supply Voltage              | Vcc    | 8.0         |             |  |

| Input Common Mode Voltage         | VICM   | ± 15        | Vdc         |  |

| Input Differential Voltage        | VID    | ± 25        | Vdc         |  |

| Three-State Control Input Voltage | VI     | 8.0         | Vdc         |  |

| Output Sink Current               | lo     | 50          | mA          |  |

| Storage Temperature               | Tstg   | -65 to +150 | °C          |  |

| Operating Junction Temperature    | TJ     | +150        | °C          |  |

### **RECOMMENDED OPERATING CONDITIONS**

| Rating                           | Symbol           | Value        | Unit |

|----------------------------------|------------------|--------------|------|

| Power Supply Voltage             | Vcc              | 4.75 to 5.25 | Vdc  |

| Operating Ambient Temperature    | TA               | 0 to +70     | °C   |

| Input Common Mode Voltage Range  | VICR             | -7.0 to +7.0 | Vdc  |

| Input Differential Voltage Range | V <sub>IDR</sub> | 6.0          | Vdc  |

ELECTRICAL CHARACTERISTICS (Unless otherwise noted, minimum and maximum limits apply over recommended temperature and power supply voltage ranges. Typical values are for  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5.0 \text{ V}$  and  $V_{IK} = 0 \text{ V}$ . See Note 1.)

| Characteristic                                                                                                                                                                                                                                                                                                                   | Symbol                 | Min         | Тур           | Max                                  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|---------------|--------------------------------------|------|

| Input Voltage – High Logic State<br>(Three–State Control)                                                                                                                                                                                                                                                                        | VIH                    | 2.0         | _             | _                                    | ٧    |

| Input Voltage – Low Logic State<br>(Three–State Control)                                                                                                                                                                                                                                                                         | VIL                    | _           | _             | 0.8                                  | ٧    |

| Differential Input Threshold Voltage, Note 2<br>$(-7.0 \text{ V} \leq \text{V}_{\text{IC}} \leq 7.0 \text{ V}, \text{V}_{\text{IH}} = 2.0 \text{ V})$<br>$(\text{I}_{\text{O}} = -0.4 \text{ mA}, \text{V}_{\text{OH}} \geq 2.7 \text{ V})$<br>$(\text{I}_{\text{O}} = 8.0 \text{ mA}, \text{V}_{\text{OL}} \geq 0.5 \text{ V})$ | VTH(D)                 |             | -             | 0.2<br>- 0.2                         | V    |

| Input Bias Current (V <sub>CC</sub> = 0 V or 5.25) (Other Inputs at 0 V) (V <sub>I</sub> = - 10 V) (V <sub>I</sub> = - 3.0 V) (V <sub>I</sub> = + 3.0 V) (V <sub>I</sub> = + 10 V)                                                                                                                                               | liB(D)                 | -<br>-<br>- | -<br>-<br>-   | - 3.25<br>- 1.50<br>+ 1.50<br>+ 3.25 | mA   |

| Input Balance and Output Level $(-7.0 \text{ V} \leq \text{V}_{\text{IC}} \leq 7.0 \text{ V}, \text{V}_{\text{IH}} = 2.0 \text{ V}, \text{Note 3})$ $(I_{\text{O}} = -0.4 \text{ mA}, \text{V}_{\text{ID}} = 0.4 \text{ V})$ $(I_{\text{O}} = 8.0 \text{ mA}, \text{V}_{\text{ID}} = -0.4 \text{ V})$                            | V <sub>OH</sub><br>VoL | 2.7         | <u>-</u><br>- | _<br>0.5                             | ٧    |

| Output Third State Leakage Current<br>(V <sub>I</sub> (D) = + 3.0 V, V <sub>IL</sub> = 0.8 V, V <sub>OL</sub> = 0.5 V)<br>(V <sub>I</sub> (D) = - 3.0 V, V <sub>IL</sub> = 0.8 V, V <sub>OH</sub> = 2.7 V)                                                                                                                       | loz                    |             | _<br>         | - 40<br>40                           | μА   |

| Output Short–Circuit Current $(V_{I(D)} = 3.0 \text{ V, } V_{IH} = 2.0 \text{ V, } V_{O} = 0 \text{ V, Note 4})$                                                                                                                                                                                                                 | los                    | - 15        | -             | - 100                                | mA   |

| Input Current – Low Logic State (Three–State Control) (VIL = 0.5 V)                                                                                                                                                                                                                                                              | Iμ                     | _           | _             | - 100                                | μА   |

| Input Current – High Logic State (Three–State Control) (VIH = 2.7 V) (VIH = 5.25 V)                                                                                                                                                                                                                                              | ЧН                     | -           |               | 20<br>100                            | μА   |

| Input Clamp Diode Voltage (Three-State Control) (I <sub>IK</sub> = -10 mA)                                                                                                                                                                                                                                                       | VIK                    | -           | -             | - 1.5                                | V    |

| Power Supply Current<br>(V <sub>IL</sub> = 2.0 V)                                                                                                                                                                                                                                                                                | lcc                    | ~           | _             | 85                                   | mA   |

NOTES: 1. All currents into device pins are shown as positive, out of device pins are negative. All voltage referenced to ground unless otherwise noted.

2. Differential input threshold voltage and guaranteed output levels are done simultaneously for worst case.

3. Refer to EIA-422/3 for exact conditions. Input balance and guaranteed output levels are done simultaneously for worst case.

4. Only one output at a time should be shorted.

**=** 6367253 0097837 081 **=**

7-87

## **SWITCHING CHARACTERISTICS** (Unless otherwise noted, $V_{CC} = 5.0 \text{ V}$ and $T_A = 25^{\circ}\text{C.}$ )

| Characteristics                                           | Symbol              | Min | Тур | Max           | Unit |

|-----------------------------------------------------------|---------------------|-----|-----|---------------|------|

| Propagation Delay Time - Differential<br>Inputs to Output |                     |     |     |               | ns   |

| (Output High to Low)                                      | t <sub>PHL(D)</sub> | _   | _   | 35            |      |

| (Output Low to High)                                      | tPLH(D)             |     | _   | 30            | 1    |

| Propagation Delay time Three-State                        |                     |     |     | 1 - 1 - 1 - 1 | ns   |

| Control to Output                                         | 1                   |     |     |               |      |

| (Output Low to Third State)                               | tPLZ                | _   | _   | 35            |      |

| (Output High to Third State)                              | t <sub>PHZ</sub>    | _   | -   | 35            | i    |

| (Output Third State to High)                              | tPZH                | _   | _   | 30            |      |

| (Output Third State to Low)                               | <sup>t</sup> PZL    |     | _   | 30            |      |

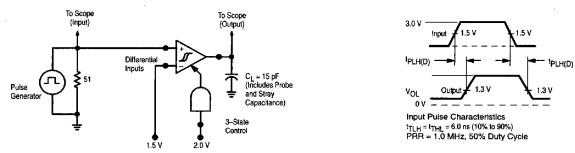

Figure 1. Switching Test Circuit and Waveforms

### **Propagation Delay Differential Input to Output**

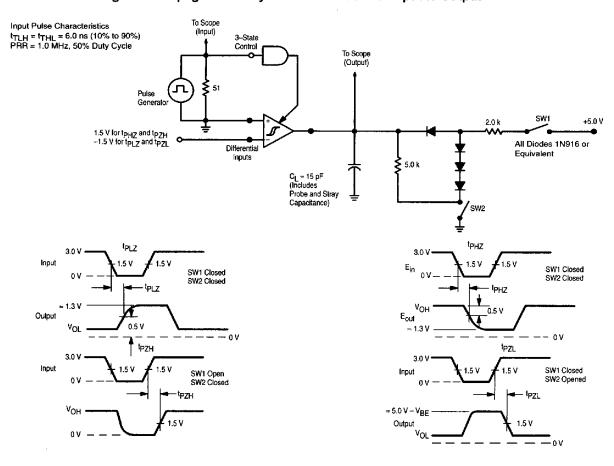

Figure 2. Propagation Delay Three-State Control Input to Output

6367253 0097838 Tl8 🖿

**MOTOROLA ANALOG IC DEVICE DATA**