# MOTOROLA SEMICONDUCTOR: TECHNICAL DATA

# MC145000 MC145001

# SERIAL INPUT MULTIPLEXED LCD DRIVERS (MASTER AND SLAVE)

The MC145000 (Master) LCD Driver and the MC145001 (Slave) LCD Driver are CMOS devices designed to drive liquid crystal displays in a multiplexed-by-four configuration. The Master unit generates both frontplane and backplane waveforms, and is capable of independent operation. The Slave unit generates only frontplane waveforms, and is synchronized with the backplanes from the Master unit. Several Slave units may be cascaded from the Master unit to increase the number of LCD segments driven in the system. The maximum number of frontplanes is dependent upon the capacitive loading on the backplane drivers and the drive frequency. The devices use data from a microprocessor or other serial data and clock source to drive one LCD segment per bit.

- Direct Interface to CMOS Microprocessors

- Serial Data Port, Externally Clocked

- Multiplexing-By-Four

- Net dc Drive Component Less Than 50 mV

- Master Drives 48 LCD Segments

- Slave Provides Frontplane Drive for 44 LCD Segments

- Drives Large Segments Up to one Square Centimeter

- Supply Voltage Range = 3 V to 6 V

- Latch Storage of Input Data

- Low Power Dissipation

- Logic Input Voltage Can Exceed VDD

- Accomodates External Temperature Compensation

- Chip Complexities: MC145000 1723 FETs or 431 Equivalent Gates MC145001 – 1495 FETs or 374 Equivalent Gates

# **CMOS LSI**

(LOW-POWER COMPLEMENTARY MOS)

SERIAL INPUT MULTIPLEXED LCD DRIVERS (MASTER AND SLAVE)

P SUFFIX PLASTIC DIP CASE 707

FN SUFFIX PLCC CASE 776

### ORDERING INFORMATION

MC14500xP MC14500xFN Plastic DIP

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that  $V_{In}$  and  $V_{Out}$  be constrained to the ranges  $V_{SS}\!\leq\!V_{Out}\!\leq\!V_{DD}$  and  $V_{SS}\!\leq\!V_{in}\!\leq\!15$  V

Unused inputs must always be tied to an appropriate logic voltage level.

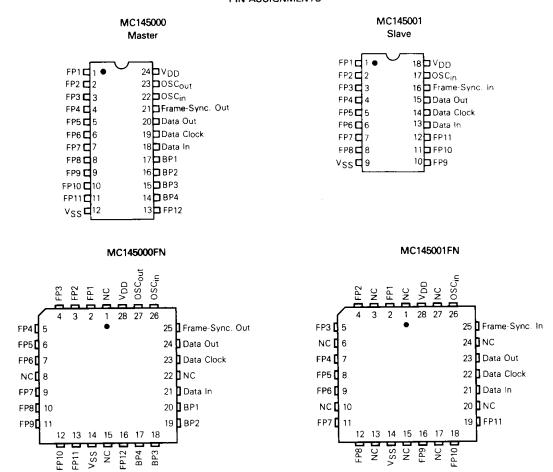

# PIN ASSIGNMENTS

# Mux-by-4 LCD Manufacturers

NOTE: Motorola cannot recommend one supplier over another and in no way suggests that this is a complete listing of LCD suppliers.

| Supplier         | Contact Information                          |

|------------------|----------------------------------------------|

| Polytronix, Inc. | Phone: (214) 238-7045<br>FAX: (214) 644-0805 |

| LXD, Inc.        | Phone: (216) 292-3300<br>FAX: (216) 292-4727 |

| UCE, Inc.        | Phone: (203) 838-7500<br>FAX: (203) 838-2566 |

| Hamlin, Inc.     | Phone: (414) 648-1000<br>FAX: (414) 648-1001 |

MAXIMUM RATINGS (Voltages referenced to VSS)

| Characteristic                        | Symbol              | Value                          | Unit |

|---------------------------------------|---------------------|--------------------------------|------|

| DC Supply Voltage                     | V <sub>DD</sub>     | -0.5 to +6.5                   | V    |

| Input Voltage, Data In and Data Clock | V <sub>in</sub>     | - 0.5 to 15                    | V    |

| Input Voltage, OSCin of Master        | V <sub>in osc</sub> | - 0.5 to V <sub>DD</sub> + 0.5 | V    |

| DC Input Current, per Pin             | lin                 | ± 10                           | mA   |

| Operating Temperature Range           | TA                  | 40 to +85                      | °C   |

| Storage Temperature Range             | Tsta                | - 65 to + 150                  | °C   |

ELECTRICAL CHARACTERISTICS (Voltages referenced to VSS)

| Characteristic                                     | Symbol    | VDD                 | - 4        | Ю°С      |         | 25°C       | 85        |              |            |           |               |  |

|----------------------------------------------------|-----------|---------------------|------------|----------|---------|------------|-----------|--------------|------------|-----------|---------------|--|

| Characteristic                                     |           | Symbol              | V          | Min      | Min Max |            | Typ#      | Max          | Min        | Max       | Unit          |  |

| RMS Voltage Across a Segment                       | ON        | V.0                 | 3.0        | _        | -       | T -        | 1.73      |              | -          | <u> </u>  | $\overline{}$ |  |

| (BPi-FPj)                                          | Segment   | VON                 | 6.0        |          | -       | -          | 3.46      |              | _          | -         | ٧             |  |

|                                                    | "OFF"     | Voce                | 3.0        | _        |         | _          | 1.00      | T -          | -          | -         | V             |  |

|                                                    | Segment   | VOFF                | 6.0        | _        | _       | -          | 2.00      | -            | -          | _         | V             |  |

| Average DC Offset Voltage                          |           | Vdc                 | 3.0        | -        | 30      | -          | 10        | 30           | -          | 30        | mV            |  |

|                                                    |           | , de                | 6.0        | -        | 50      | _          | 20        | 50           | _          | 50        | 1110          |  |

| Input Voltage                                      | "0" Level | $  v_{\text{IL}}  $ | 3.0        | -        | 0.90    | -          | 1.35      | 0.90         |            | 0.90      | V             |  |

|                                                    |           | , '                 | 6.0        | _        | 1.80    | ļ -        | 2.70      | 1.80         |            | 1.80      |               |  |

|                                                    | "1" Level | VIH                 | 3.0<br>6.0 | 2.10     | -       | 2.10       | 1.65      | -            | 2.10       | -         | ٧             |  |

| Output Drive Current - Backplanes                  |           | -                   | 0.0        | 4.20     |         | 4.20       | 3.30      |              | 4.20       | -         |               |  |

| High-Current State*                                |           |                     |            |          |         | ļ          | 1         | 1            |            |           |               |  |

| V <sub>O</sub> = 2.85 V                            |           |                     |            | 150      | _       | 75         | 190       | _            | 35         |           |               |  |

| V <sub>O</sub> = 1.85 V                            |           | ¹вн                 | 3.0        | 220      | _       | 110        | 200       | _            | 55         | _         | μΑ            |  |

| V <sub>O</sub> = 1.15 V                            |           | 1                   |            | 160      | _       | 80         | 200       | l _          | 40         | _         |               |  |

| V <sub>O</sub> = 0.15 V                            |           |                     |            | 400      | _       | 200        | 300       | _            | 100        |           |               |  |

| $V_0 = 5.85 \text{ V}$                             |           |                     |            | 500      | _       | 250        | 300       |              | 125        | _         |               |  |

| $V_0 = 3.85 \text{ V}$                             |           | ١,                  |            | 1000     | _       | 500        | 600       | _            | 250        | _         |               |  |

| $V_0 = 2.15 \text{ V}$                             |           | ¹вн                 | 6.0        | 800      | -       | 400        | 500       | _            | 200        | _         | μΑ            |  |

| $V_0 = 0.15 \text{ V}$                             |           |                     |            | 500      | _       | 250        | 300       | _            | 125        |           |               |  |

| Low-Current State*                                 |           |                     |            |          | ]       | l          |           |              |            |           |               |  |

| $V_0 = 2.85 \text{ V}$                             |           |                     |            | 140      | _       | 70         | 80        | -            | 35         | _         |               |  |

| V <sub>O</sub> = 1.85 V                            |           | IBL                 | 3.0        | 2.4      | _       | 1.2        | 2.8       | _            | 0.6        | - 1       | μΑ            |  |

| V <sub>O</sub> = 1.15 V                            |           |                     |            | 2.2      | _       | 1.1        | 2.5       | _            | 0.5        | _         |               |  |

| $V_0 = 0.15 \text{ V}$                             |           |                     |            | 400      | -       | 200        | 330       | _            | 100        | -         |               |  |

| V <sub>O</sub> = 5.85 V                            |           |                     |            | 190      | _       | 95         | 105       | <del> </del> | 45         |           |               |  |

| $V_0 = 3.85 \text{ V}$                             |           | l                   |            | 15       | _       | 7.5        | 10        | _            | 3.7        | _         |               |  |

| $V_0 = 2.15 \text{ V}$                             |           | BL                  | 6.0        | 13       | -       | 6.5        | 9         | _            | 3.2        | _         | μΑ            |  |

| $V_{O} = 0.15 \text{ V}$                           |           |                     |            | 850      | -       | 425        | 570       |              | 210        | -         |               |  |

| Output Drive Current - Frontplanes                 |           |                     |            |          |         |            |           |              |            |           |               |  |

| High-Current State*                                |           |                     |            |          |         |            | ,         |              |            |           |               |  |

| $V_0 = 2.85 \text{ V}$                             |           | l <sub>EH</sub>     | 3 0        | 80       | -       | 40         | 60        | -            | 20         | -         | ٨             |  |

| V <sub>O</sub> = 1.85 V                            |           | 'FM                 | 50         | 140      | - !     | 70         | 120       | -            | 35         | - 1       | μΑ            |  |

| $V_0 = 1.15 \text{ V}$                             |           |                     |            | 180      | -       | 60         | 100       | -            | 30         | -         |               |  |

| $V_0 = 0.15 \text{ V}$                             |           |                     |            | 100      |         | 50         | 95        |              | 25         |           |               |  |

| V <sub>O</sub> = 5 85 V                            |           |                     |            | 140      | -       | 70         | 90        | _            | 35         | - [       |               |  |

| $V_O = 3.85 \text{ V}$                             |           | IFH                 | 60         | 360      | _       | 180        | 250       | -            | 90         | -         | μΑ            |  |

| V <sub>O</sub> = 2 15 V                            |           | 171                 |            | 400      |         | 200        | 240       |              | 100        | -         | μ             |  |

| $V_0 = 0.15 \text{ V}$                             |           |                     |            | 100      | - 1     | 50         | 120       |              | 25         | -         |               |  |

| Low-Current State*                                 |           |                     |            |          |         |            |           |              |            |           |               |  |

| $V_0 = 2.85 \text{ V}$                             |           |                     |            | 60       | -       | 30         | 40        | -            | 15         | _         |               |  |

| $V_0 = 1.85 \text{ V}$                             |           | lFL                 | 3.0        | 2 8      | -       | 1.4        | 2.8       |              | 0.7        | -         | μА            |  |

| $V_O = 1.15 \text{ V}$<br>$V_O = 0.15 \text{ V}$   |           | i                   |            | 2.2      | -       | 1.1        | 2.5       | -            | 0.5        | -         |               |  |

|                                                    |           |                     |            | 100      | _       | 50         | 100       |              | 25         | -         |               |  |

| V <sub>O</sub> = 5.85 V                            |           |                     |            | 100      | - :     | 50         | 60        | -            | 25         | -         |               |  |

| V <sub>O</sub> = 3.85 V<br>V <sub>O</sub> = 2.15 V |           | IFL                 | 60         | 16<br>13 | _       | 8.0<br>6.5 | 10<br>9   | _            | 4.0<br>3.2 | -         | μΑ            |  |

| $V_0 = 0.15 \text{ V}$                             |           |                     |            | 200      | _       | 100        | 175       | _            | 3.2<br>50  | _ [       | •             |  |

| Input Current                                      |           | l <sub>in</sub>     | 6.0        | -        | ± 0.1   | -          | ± 0.00001 | ± 0.1        |            | ± 1.0     | μА            |  |

| Input Capacitance                                  |           | Ciu                 | - 0.0      |          | ± 0.1   |            | 5.0       | 7.5          | _          | ± 1.0     | ρF            |  |

| Quiescent Current (Per Package)                    |           | - Un                | 3.0        |          | 10      | _          |           |              | _          |           | μr            |  |

| $V_{in} = 0$ or $V_{DD}$ , $I_{out} = 0 \mu A$     |           | lDD                 | 60         | _        | 185     | _          | 2.5<br>50 | 15<br>175    | _          | 20<br>130 | μΑ            |  |

|                                                    |           |                     |            |          |         |            |           | 170          | _          | 130       |               |  |

<sup>\*</sup>For a time (t \(\perp 2.56\)/osc, freq.) after the backplane or frontplane waveform changes to a new voltage level, the circuit is maintained in the high-current state to allow the load capacitances to charge quickly. Then the circuit is returned to the low-current state until the next voltage level change occurs.

#Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

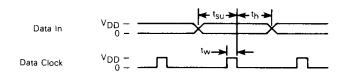

# SWITCHING CHARACTERISTICS ( $C_L = 50 \text{ pF}, T_A = 25 \text{ °C}$ )

| Characteristic                      | Symbol                          | VDD        | Min      | Тур#       | Max         | Unit |

|-------------------------------------|---------------------------------|------------|----------|------------|-------------|------|

| Data Clock Frequency                | fcI                             | 3.0<br>6.0 | -        | 12.5<br>24 | 7 5<br>12 5 | MHz  |

| Rise and Fall Times - Data clock    | t <sub>r</sub> , t <sub>f</sub> | 3.0<br>6.0 | -        | -          | 125<br>10   | μS   |

| Setup Time<br>Data In to Data Clock | t <sub>su</sub>                 | 3.0<br>6.0 | 48<br>16 | - 1        | -           | ns   |

| Hold Time<br>Data In to Data Clock  | th                              | 3.0<br>6.0 | - 5<br>0 | -          | -           | ns   |

| Pulse Width<br>Data Clock           | t <sub>W</sub>                  | 3.0<br>6.0 | 65<br>40 | -          | -           | ns   |

#Data labelled "Typ" is not to be used for design purposes but is intended as an indication of the IC's potential performance.

### SWITCHING WAVEFORMS

### **DEVICE OPERATION**

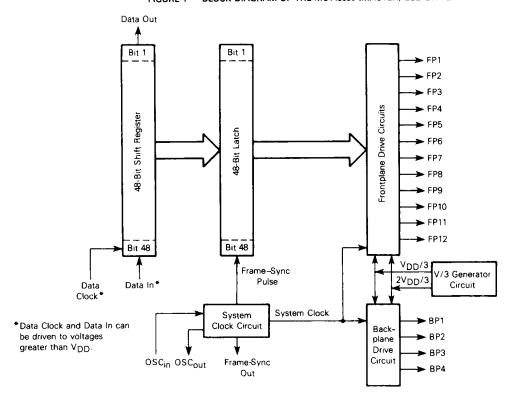

Figure 1 shows a block diagram of the Master unit. The unit is composed of two independent circuits: the data input circuit with its associated data clock, and the LCD drive circuit with its associated system clock.

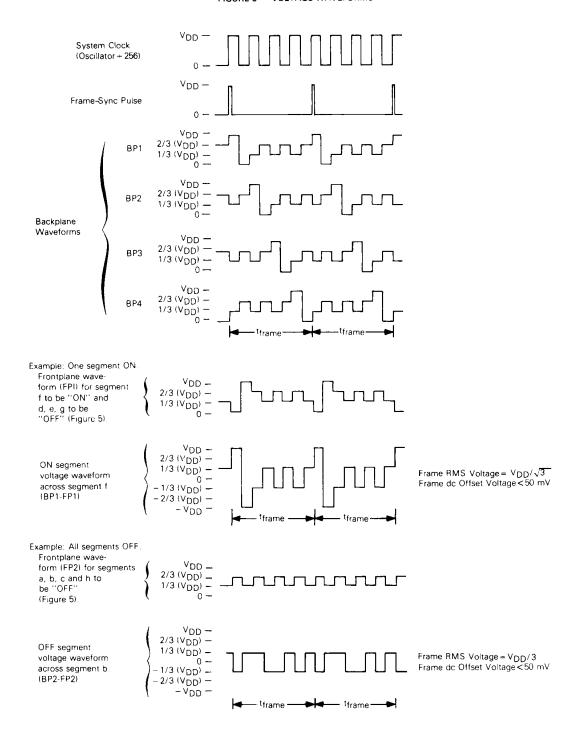

Forty-eight bits of data are serially clocked into the shift register on the falling edges of the external data clock. Data in the shift register is latched into the 48-bit latch at the beginning of each frame period. (As shown in Figure 3, the frame period, tframe, is the time during which all the LCD segments are set to the desired "ON" or "OFF" states.)

The binary data present in the latch determines the appropriate waveform signal to be generated by the frontplane drive circuits, whereas the backplane waveforms are invariant. The frontplane and backplane waveforms, FPn and BPn, are generated using the system clock (which is the oscillator divided by 256) and voltages from the V/3 generator circuit (which divides Vpp into one-third increments). As shown in Figure 3, the frontplane and backplane waveforms and the "ON" and "OFF" segment waveforms have periods equal to tframe and frequencies equal to the system clock divided by four.

Twelve frontplane and four backplane drivers are available from the Master unit. The latching of the data at the beginning of each frame period and the carefully balanced voltage-generation circuitry minimize the generation of a net dc component across any LCD segment.

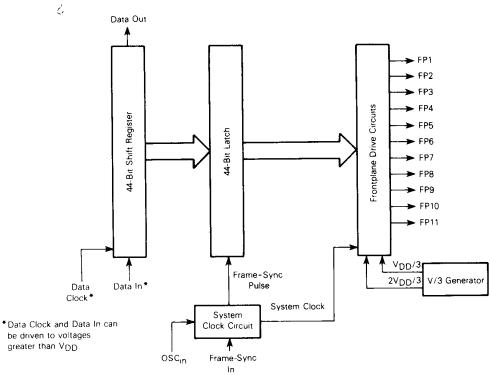

The Slave unit (Figure 2) consists of the same circuitry as the Master unit, with two exceptions: it has no backplane drive circuitry, and its shift register and latch hold 44 bits. Eleven frontplane and no backplane drivers are available from the Slave unit.

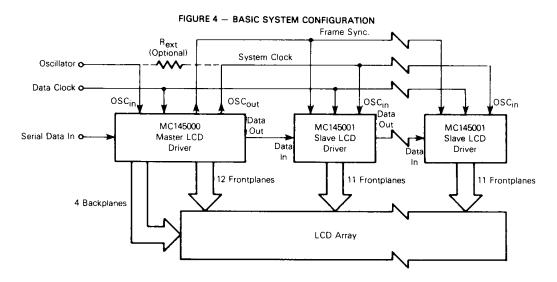

### LCD DRIVER SYSTEM CONFIGURATIONS

Figure 4 shows a basic LCD Driver system configuration, with one Master and several Slave units. The maximum number of slave units in a system is dictated by the maximum backplane drive capability of the device and by the system data update rate. Data is serially shifted first into the Master unit and then into the following Slave units on the falling edge of the common data clock. The oscillator is common to the Master unit and each of the Slave units. At the beginning of each frame period, tframe, the Master unit generates a frame-sync pulse (Figure 3) which is received by the Slave units. The pulse is to ensure that all Slave unit frontplane drive circuits are synchronized to the Master unit's backplane drive circuits.

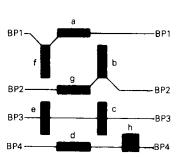

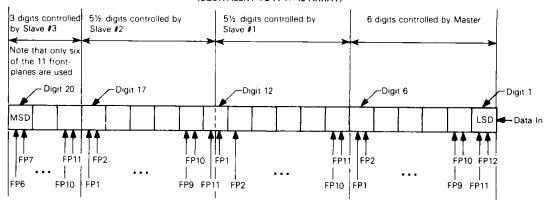

A single multiplexed-by-four, 7-segment (plus decimal point) LCD and possible frontplane and backplane connections are shown in Figure 5. When several such displays are used in a system, the four backplanes generated by the Master unit are common to all the LCD digits in the system. The twelve frontplanes of the Master unit are capable of controlling forty-eight LCD segments (6 LCD digits), and the eleven frontplanes of each Slave unit are capable of controlling forty-four LCD segments (5½ LCD digits).

FIGURE 1 - BLOCK DIAGRAM OF THE MC145000 (MASTER) LCD DRIVER

FIGURE 2 — BLOCK DIAGRAM OF THE MC145001 (SLAVE) LCD DRIVER

FIGURE 3 - VOLTAGE WAVEFORMS

FIGURE 5 — FRONTPLANE AND BACKPLANE CONNECTIONS TO A MULTIPLEXED-BY-FOUR 7-SEGMENT (PLUS DECIMAL POINT) LCD

SEGMENT TRUTH TABLE\*

|     | FP1 | FP2 |

|-----|-----|-----|

| BP1 | f   | а   |

| BP2 | g   | b   |

| BP3 | е   | С   |

| BP4 | d   | h   |

Because there is no standard for backplane and frontplane connections on multiplexed displays, this truth table may be used only for this example.

### Typical Backplane Configuration

Typical Frontplane Configuration

### PIN DESCRIPTIONS

### FRONTPLANE DRIVE OUTPUTS

(Master: FP1-FP12) (Slave: FP1-FP11)

The frontplane drive waveforms for the LCDs.

# BACKPLANE DRIVE OUTPUTS (Master: BP1-BP4)

The backplane drive waveforms for the LCDs.

### DATA IN (Master and Slave)

The serial data input pin. Data is clocked into the shift register on the falling edge of the data clock. A high logic level will cause the corresponding LCD segment to be turned on, and a low logic level will cause the segment to be turned off. This pin can be driven to 15 volts regardless of the value of VDD, thus permitting optimum display drive voltage.

### DATA CLOCK (Master and Slave)

The input pin for the external data clock, which controls the shift registers. This pin can be driven to 15 volts regardless of the value of  $V_{DD}$ .

# DATA OUT (Master and Slave)

The serial data output pin.

# FRAME-SYNC OUT (Master)

The output pin for the frame-sync pulse, which is generated by the Master unit at the beginning of each frame period, tframe. From Figure 1, the 48-bit latch is loaded during the positive Frame-Sync Out pulse. Therefore, if the Data Clock is active during this load interval, the display will flicker.

### FRAME-SYNC IN (Slave)

The input pin for the frame-sync pulse from the Master unit. The frame-sync pulse synchronizes the Slave front-plane drive waveforms to the Master backplane drive waveforms.

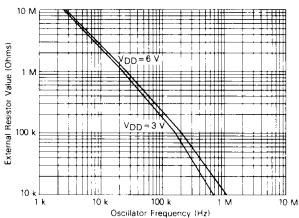

### OSCin (Master and Slave)

The input pin to the system clock circuit. The oscillator frequency is either obtained from an external oscillator or generated in the Master unit by connecting an external resistor between the OSC<sub>in</sub> pin and the OSC<sub>out</sub> pin. Figure 6 shows the relationship between resistor value and frequency.

### OSCout (Master)

The output pin of the system clock circuit. This pin is connected to the  ${\sf OSC}_{in}$  input of each Slave unit.

#### V<sub>DD</sub> (Master and Slave)

The positive supply voltage.

#### VSS (Master and Slave)

The negative supply (or ground) voltage

### **APPLICATIONS**

The following examples are presented to give the user further insight into the operation and organization of the Master and Slave LCD Drivers.

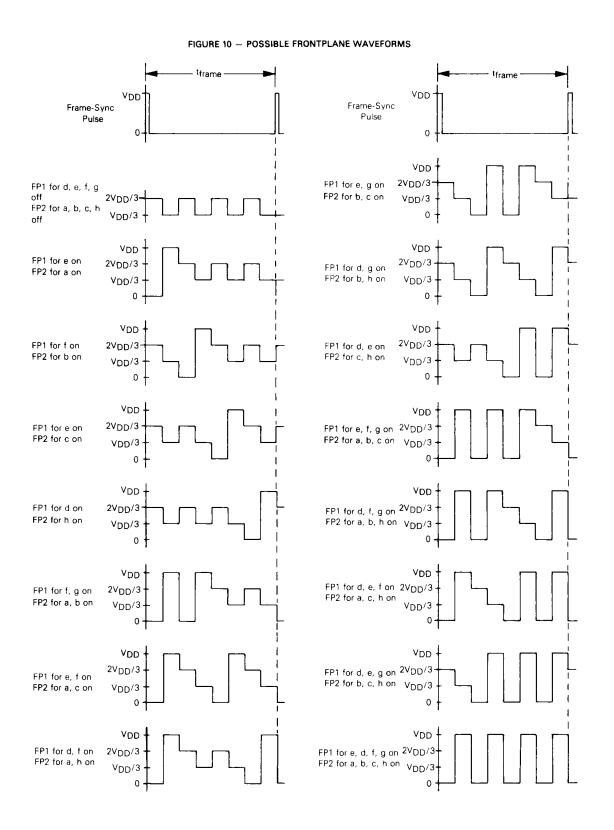

An LCD segment is turned either on or off depending upon the RMS value of the voltage across it. This voltage is equal to the backplane voltage waveform minus the front-plane voltage waveform. As previously stated, the backplane waveforms are invariant (see Figure 3). Figure 10 shows one period of every possible frontplane waveform.

For a detailed explanation of the operation of liquid crystal materials and multiplexed displays, refer to a brochure entitled "Multiplexed Liquid Crystal Displays," by Gregory A. Zaker, General Electric Company, Liquid XTAL Displays Operation, 24500 Highpoint Road, Cleveland, Ohio 44122.

**Example 1:** Many applications (e.g., meters, gasoline pumps, pinball machines, and automobile dashboard displays! require that, for each display update, an entirely new set of data must be shifted into the Master and cascaded Slave units. The correspondence between the frontplane-backplane intersections at the LCD segments and the data bit locations in the 48-bit latch of the Master (or 44-bit latch of the Slave) is necessary information to the system designer. In Figure 1, it is shown that data is serially shifted first into the 48th-bit location of the shift register of the Master. Thus, after 48 data bits have been shifted in, the

first bit to be entered has been shifted into bit-location one, the second bit into bit-location two, and so on. Table 1 shows the bit location in the latch that controls the corresponding frontplane-backplane intersection. For example, the information stored in the 26th-bit location of the latch controls the LCD segment at the intersection of FP7 and BP3. The voltage waveform across that segment is equal to (BP3 minus FP7). The same table, but with the column for FP12 deleted, describes the operation of the Slave unit.

In applications of this type, all the necessary data to completely update the display are serially shifted into the Master and succeeding Slave units within a frame period. Typically, a microprocessor is used to accomplish this.

**Example 2:** Many keyboard-entry applications, such as calculators, require that the most significant digit be entered and displayed first. Then as each succeeding digit is entered, the previously entered digits must shift to the left. It is, therefore, neither necessary nor desirable to enter a completely new set of data for each display change. Figure 7 shows a representation of a system consisting of one Master and three Slave units and displaying 20 LCD digits. If each digit has the frontplane-backplane configuration shown in Figure 5, the relationship between frontplanes, backplanes, and LCD segments in the display is shown in Table 2.

Digits (or alphanumeric characters) are entered, mostsignificant digit first, by using a keyboard and a decoder external to the MC145000. Data is entered into the Master and cascaded Slave units according to the following format:

1) Initially, all registers and latches must be cleared by entering 160 zero data bits. This turns off all 160 segments of the display.

2) Entering the most-significant digit from the keyboard causes the appropriate eight bits to be serially shifted into the Master unit. These eight bits control LCD segments a through h of digit 1, and cause the desired digit to be displayed in the least-significant digit location.

3) Entering the second-most-significant digit from the keyboard causes eight more bits to be serially shifted into the Master unit. These eight bits now control LCD segments a

through h of digit 1, and the previously entered eight bits now control segments a through h of digit 2. Thus the two digits are displayed in the proper locations.

4) Entering the remaining 18 digits from the keyboard fills the 20-digit display. Entering an extra digit will cause the first digit entered to be shifted off the display.

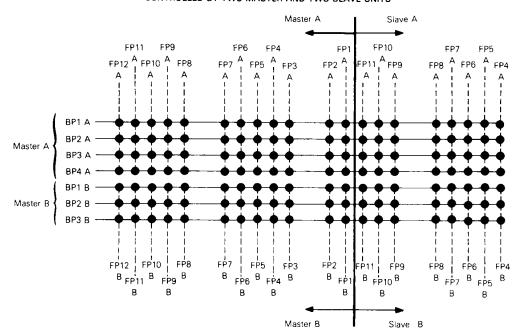

**Example 3:** In addition to controlling 7-segment (plus decimal point) digital displays, the MC145000 and MC145001 may be used to control displays using  $5\times7$  dot matrices. A Master and three Slave units can drive 180 LCD segments, and therefore are capable of controlling five  $5\times7$  dot matrices (175 segments). Two control schemes are presented in Figures 8 and 9; one using a single Master unit, and one using two Master units.

TABLE 1 — THE BIT LOCATIONS, IN THE LATCH, THAT CONTROL THE LCD SEGMENTS LOCATED AT EACH FRONTPLANE-BACKPLANE INTERSECTION

#### **FRONTPLANES**

| ES    |     | FP1 | FP2 | FP3 | FP4 | FP5 | FP6 | FP7 | FP8 | FP9 | FP10 | FP11 | FP12 |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| (PLAN | BP1 | 4   | 8   | 12  | 16  | 20  | 24  | 28  | 32  | 36  | 40   | 44   | 48   |

|       | BP2 | 3   | 7   | 11  | 15  | 19  | 23  | 27  | 31  | 35  | 39   | 43   | 47   |

| Ş     | BP3 | 2   | 6   | 10  | 14  | 18  | 22  | 26  | 30  | 34  | 38   | 42   | 46   |

| æ     | BP4 | 1   | 5   | 9   | 13  | 17  | 21  | 25  | 29  | 33  | 37   | 41   | 45   |

# FIGURE 7 — A 20-DIGIT DISPLAY (EQUIVALENT TO A 4×40 ARRAY)

TABLE 2 - THE RELATIONSHIP BETWEEN FRONTPLANE-BACKPLANE INTERSECTIONS AND LCD SEGMENTS FOR THE SYSTEM CONFIGURATION OF FIGURE 7

|     | Master — |      |            |     |       |            |      | -    | Slave #1———Slave #2——— |       |      |      |       |     |  |      | Slave #3 |      |      |       |      |      |

|-----|----------|------|------------|-----|-------|------------|------|------|------------------------|-------|------|------|-------|-----|--|------|----------|------|------|-------|------|------|

|     | FP12     | FP11 | FP10       | FP9 | • • • | FP2        | FP1  | FP11 | FP10                   | • • • | FP1  | FP11 | FP10  | FP9 |  | FP2  | FP1      | FP11 | FP10 | • • • | FP7  | FP6  |

| BP1 | a1       | f1   | <b>a</b> 2 | f2  |       | a6         | f6   | a7   | f7                     |       | a12  | f12  | a13   | f13 |  | a17  | f17      | a18  | f18  |       | a20  | f20  |

| BP2 | b1       | g1   | ь2         | g2  |       | b6         | g6   | b7   | g7                     |       | b12  | g12  | b13   | g13 |  | b17  | g17      | b18  | g18  |       | ь20  | g20  |

| ВР3 | c1       | e1   | c2         | e2  |       | c <b>6</b> | e6   | с7   | e7                     |       | c12  | e12  | c13   | e13 |  | c17  | e17      | c18  | e18  |       | c20  | e20  |

| BP4 | h1       | d1   | h2         | d2  |       | h6         | d6   | h7   | d7                     |       | h12  | d12  | h13   | d13 |  | h17  | d17      | h18  | d18  |       | h20  | d20  |

|     | dig      | nt 1 | dig        | t 2 | •••   | dig        | ıt 6 | dig  | ut 7                   | • • • | digi | t 12 | digit | 13  |  | digi | 1 17     | digi | t 18 |       | diai | ι 20 |

Master Slave #1 Slave #2 Slave #3 FP11 FP9 FP2 FP4 FP2 FP6 FP6 FP4 FP8 FP12 FP10 FP7 FP5 FP3 FP5 BP4 FP9 FP11 FP2 FP9 FP4 FP2 FP6 FP6 FP1 FP4 FP8 FP10 FP8 FP10

FIGURE 8 - EXAMPLE OF A 5×7 DOT MATRIX DISPLAY SYSTEM CONTROLLED BY ONE MASTER AND THREE SLAVE UNITS

# FIGURE 9 - EXAMPLE OF A $5\times7$ DOT MATRIX DISPLAY SYSTEM CONTROLLED BY TWO MASTER AND TWO SLAVE UNITS