$\mathbf{T}$  he  $\mathbf{I}$  nfinite  $\mathbf{P}$  ower of  $\mathbf{I}$  nnovation

# LX1562/1563

SECOND-GENERATION POWER FACTOR CONTROLLER

PRODUCTION DATA SHEET

## DESCRIPTION

The LX1562 is a second-generation family of power factor correction controllers using a discontinuous mode of operation. They are optimized for electronic ballast applications. Many improvements have been made over the original SG3561A controller introduced by Silicon General Semiconductor in 1992.

New features include the addition of an internal start-up circuit eliminating bulky external components while allowing independent boost converter operation. Addition of internal current sense blanking eliminating the need for an external R/C filter network. Internal clamping of the error amplifier and multiplier outputs improves turn on overshoot characteristics and current limiting. Special circuitry has also been added to prevent no load runaway conditions. And finally, output drive clamps limiting power MOSFET gate drive independent of supply voltage greatly enhance the products practical application.

Although the IC design has been optimized for electronic ballast applications, it can also be used for power factor correction in lower power (typ < 300W) AC-DC converters. One unique feature of the device is encompassed by the addition of internal logic circuitry to detect zero crossing of the inductor current thus maintaining the discontinuous current mode of operation. This feature prevents large current gaps from appearing thereby minimizing distortion and enhancing power factor correction.

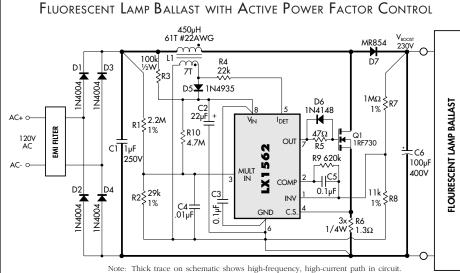

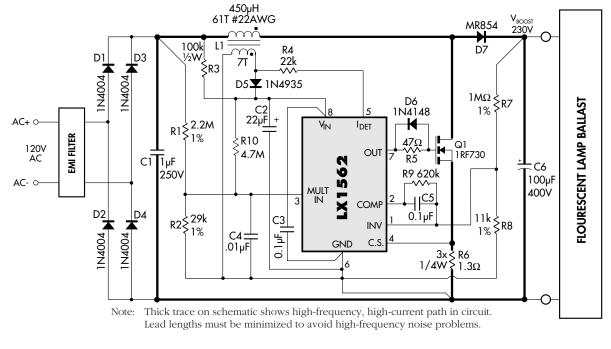

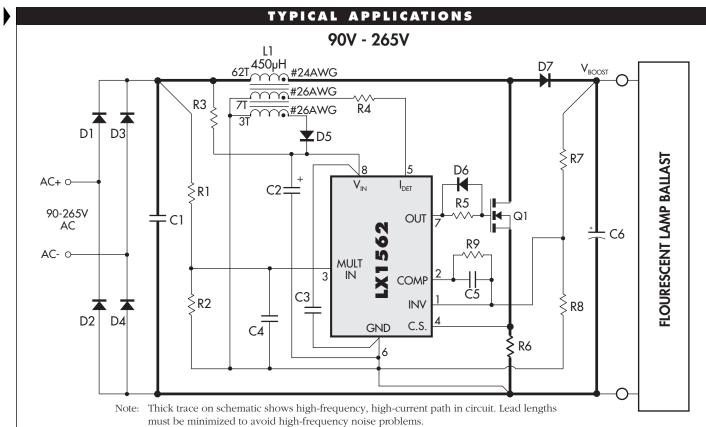

## PRODUCT HIGHLIGHT Typical Application of the LX1562 in an 80W

Lead lengths must be minimized to avoid high-frequency noise problems.

| PACKA               | GE ORDER               | INFORMATION                     |

|---------------------|------------------------|---------------------------------|

| Т <sub>А</sub> (°С) | M Plastic DIP<br>8-pin | <b>DM</b> Plastic SOIC<br>8-pin |

| 0 to 100            | LX1562IM               | LX1562IDM                       |

| 0 to 100            | LX1563IM               | LX1563IDM                       |

Note: All surface-mount packages are available in Tape & Reel. Append the letter "T" to part number. (i.e. LX1562IDMT)

### FOR FURTHER INFORMATION CALL (714) 898-8121

11861 WESTERN AVENUE, GARDEN GROVE, CA. 92841

# INTERNAL START-UP CIRCUIT

**KEY FEATURES**

- INTERNAL CURRENT SENSE BLANKING

- IMPROVED MICROPOWER START-UP CURRENT (300µA max.)

- CLAMPED E.A. OUTPUT FOR LOWER TURN-ON OVERSHOOT

- MULTIPLIER CLAMP LIMITS MAXIMUM INPUT CURRENT

- INTERNAL OVERVOLTAGE PROTECTION REPLACES BUILT-IN C.S. OFFSET

- PWM OUTPUT CLAMP LIMITS MOSFET GATE DRIVE VOLTAGE

- INCREASED UVLO HYSTERESIS REDUCES START-UP TIMING (LX1562 only)

- LOW OPERATING CURRENT CONSUMPTION

- INTERNAL 1.5% REFERENCE

- TOTEM POLE OUTPUT STAGE

- AUTOMATIC CURRENT LIMITING OF BOOST STAGE

- DISCONTINUOUS MODE OF OPERATION WITH NO CURRENT GAPS

- NO SLOPE COMPENSATION REQUIRED

## APPLICATIONS

- ELECTRONIC BALLAST

- SWITCHING POWER SUPPLIES

| AVAILABLE | $O_{PTIONS}$        | per Part #            |

|-----------|---------------------|-----------------------|

| Part #    | Start-Up<br>Voltage | Hysteresis<br>Voltage |

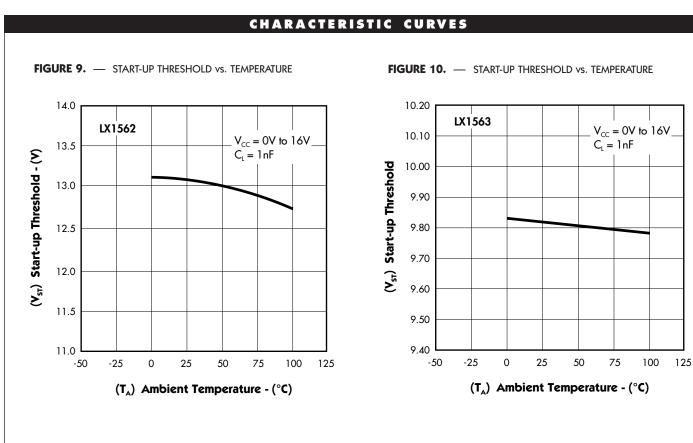

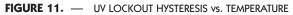

| LX1562    | 13.1V               | 5.2V                  |

| LX1563    | 9.8V                | 2.1V                  |

# **Second-Generation Power Factor Controller**

## PRODUCTION DATA SHEET

| ABSOLUTE MAXIMUM RATINGS | (Note 1) |

|--------------------------|----------|

|--------------------------|----------|

| Supply Voltage $(V_{N})$                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                             |

| Peak Driver Output Current (Note 3) ±500mA                                                                                                                  |

| Driver Output Clamping Diodes                                                                                                                               |

| $V_{o} > V_{cc}$ or $V_{o} < -0.3V$ $\pm 10mA$                                                                                                              |

| Detector Clamping Diodes                                                                                                                                    |

| $V_{DET} > 6V \text{ or } V_{DET} < 0.9V \dots \pm 10 \text{ mA}$                                                                                           |

| Error Amp, Multiplier, and Comparator Input Voltages0.3V to 6V                                                                                              |

| Detector Input Voltage (Note 2)0.3 to 6V                                                                                                                    |

| Operating Junction Temperature                                                                                                                              |

| Plastic (M and DM Packages)                                                                                                                                 |

| Storage Temperature Range                                                                                                                                   |

| Lead Temperature (Soldering, 10 Seconds)                                                                                                                    |

| Note 1. Values beyond which damage may occur. All voltages are specified with respect to ground, and all currents are positive into the specified terminal. |

Note 2. With no limiting resistor.

Note 3. Current duty cycle is chosen such that  $T_1$  is below 150°C.

## THERMAL DATA

### M PACKAGE:

| THERMAL RESISTANCE-JUNCTION TO AMBIENT, $\theta_{JA}$                 | 95°C/W  |

|-----------------------------------------------------------------------|---------|

| DM PACKAGE:                                                           |         |

| THERMAL RESISTANCE-JUNCTION TO AMBIENT, $\boldsymbol{\theta}_{_{JA}}$ | 165°C/W |

|                                                                       |         |

Junction Temperature Calculation:  $T_{I} = T_{A} + (P_{D} \ge \theta_{IA}).$

The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow

## PACKAGE PIN OUTS

(Top View)

| E.A. INV.     | 1 8 | Ъ | V <sub>IN</sub>  |  |  |

|---------------|-----|---|------------------|--|--|

| E.A. OUT 🖂    | 2 7 |   | OUT              |  |  |

| MULT. INPUT 🖂 | 3 6 |   | GROUND           |  |  |

| c.s. 🞞        | 4 5 |   | I <sub>det</sub> |  |  |

| DM PACKAGE    |     |   |                  |  |  |

(Top View)

# SECOND-GENERATION POWER FACTOR CONTROLLER

**PRODUCTION DATA SHEET**

| RECOMMENDED OPERATING CONDITIONS (Note 4)         |        |      |      |      |       |  |

|---------------------------------------------------|--------|------|------|------|-------|--|

| Parameter Symbol Recommended Operating Conditions |        |      |      |      |       |  |

| Falallietei                                       | Symoon | Min. | Тур. | Max. | Units |  |

| Supply Voltage Range                              |        | 11   |      | 25   | V     |  |

| Peak Driver Output Current                        |        |      | ±200 |      | mA    |  |

| Operating Ambient Temperature Range:              |        |      |      |      |       |  |

| LX1562/1563                                       |        | 0    |      | 100  | °C    |  |

Note 4. Range over which the device is functional.

## ELECTRICAL CHARACTERISTICS

(Unless otherwise specified, these specifications apply over the operating ambient temperatures for the LX1562/1563 with  $0^{\circ}C \le T_{A} \le 100^{\circ}C$ ;  $V_{IN} = 12V$ . Low duty cycle pulse testing techniques are used which maintains junction and case temperatures equal to the ambient temperature.)

| Parameter                             | Symbol           | Symbol Test Conditions                                    |                  | 15621/15 | 631           | – Units          |

|---------------------------------------|------------------|-----------------------------------------------------------|------------------|----------|---------------|------------------|

| Falalleter                            | Symoor           | Test conditions                                           | Min.             | Тур.     | Max.          | Units            |

| Under-Voltage Lockout Section         |                  |                                                           |                  |          |               |                  |

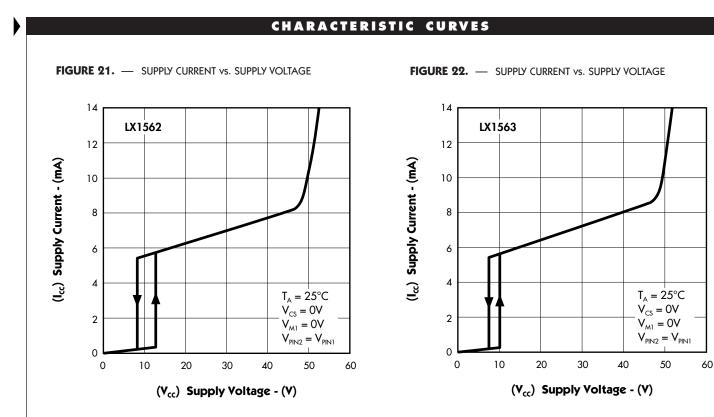

| Start Threshold Voltage               | V <sub>st</sub>  | LX1562 Only                                               | 12               | 13.1     | 14            | V                |

|                                       |                  | LX1563 Only                                               | 9.2              | 9.8      | 10.6          | V                |

| UV Lockout Hysteresis                 | $\Delta V_{H}$   | LX1562 Only                                               | 4                | 5.2      | 6             | V                |

|                                       |                  | LX1563 Only                                               | 1.7              | 2.1      | 2.5           | V                |

| Supply Current Section                |                  |                                                           |                  |          |               |                  |

| Start-Up Supply Current               | I <sub>st</sub>  | V <sub>IN</sub> < V <sub>TH</sub>                         |                  | 200      | 300           | μA               |

| Operating Supply Current              | I <sub>o</sub>   | $V_{N} = 12V$ , Output Not Switching                      |                  | 5        | 8             | mA               |

| Dynamic Operating Supply Current      | I <sub>OP</sub>  | V <sub>IN</sub> = 12V, 50kHz, CGS = 1000pF                |                  | 6        | 10            | mA               |

| Reference Section (Note 5)            |                  |                                                           | ·                |          |               |                  |

| Initial Accuracy (Note 8)             | V <sub>R</sub>   | $I_{REF} = 0mA$ , $T_A = 25^{\circ}C$                     | 2.465            | 2.50     | 2.535         | V                |

|                                       |                  | $I_{REF} = 0mA$                                           | 2.44             |          | 2.56          | V                |

| Line Regulation                       | $\Delta V_{I}$   | 12V < V <sub>IN</sub> < 25V                               |                  | 0.1      |               | mV               |

| Load Regulation                       | $\Delta V_{L}$   | $0 < I_{REF} < 2mA$                                       |                  | 1.3      |               | mV               |

| Temperature Stability                 | $\Delta V_T$     |                                                           |                  | 20       |               | mV               |

| Error Amplifier Section               |                  |                                                           | -                |          |               |                  |

| Input Bias Current                    | I <sub>B</sub>   |                                                           | -500             | 50       | 500           | nA               |

| Large Signal Open Loop Voltage Gain   | A <sub>VOL</sub> | (Note 5)                                                  | 60               | 80       |               | dB               |

| Slew Rate                             | S                |                                                           |                  | 0.63     |               | V/µsec           |

| Power Supply Rejection Ratio (Note 5) | PSRR             | 11 to 25V                                                 | 60               | 80       |               | dB               |

| Output Source Current                 | I <sub>sr</sub>  | V <sub>OH</sub> = 3V                                      | -2               | -4.5     |               | mA               |

| Output Sink Current                   | I <sub>sk</sub>  | $V_{OL} = 2V$                                             | 3                | 4.5      |               | mA               |

| Output Voltage Range (Note 7)         | E.A.o            | No Load on E.A. Output                                    | 1.2              |          | 3.8           | V                |

| Unity Gain Bandwidth                  | f <sub>B</sub>   |                                                           |                  | 1.7      |               | MHz              |

| Phase Margin                          | φ <sub>B</sub>   |                                                           |                  | 49       |               | 0                |

| Multiplier Section                    |                  |                                                           |                  | ·        |               |                  |

| Mult. Input Voltage Range             | V <sub>M1</sub>  |                                                           | 0                |          | 2             | V                |

| M2 Input Voltage Range                | V <sub>M2</sub>  |                                                           | V <sub>REF</sub> |          | $V_{REF} + 1$ | V                |

| Mult. Input Bias Current (M1)         | I <sub>MB</sub>  |                                                           |                  | -0.24    | 1361          | μA               |

| Multiplier Gain (Note 5 & 6)          | K                | $V_{M1} = 1V_{A1} \Delta V_{EA0} = 2.7V \text{ to } 3.3V$ | 0.55             | 0.68     | 0.8           | V/V <sup>2</sup> |

|                                       |                  | $\Delta V_{M1} = 0.5V$ to 1.5V, $V_{EAQ} = V_{REF} + 1V$  | 0.55             | 0.61     | 0.75          | V/V <sup>2</sup> |

| Multiplier Gain Temperature Stability | $\Delta K_T$     |                                                           |                  | -0.2     |               | %/°C             |

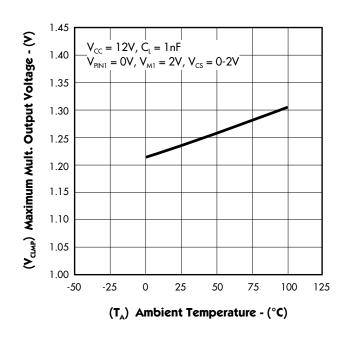

| Maximum Multiplier Output Voltage     | V                | $V_{M1} = 2V, V_{PIN1} = 0V$                              | 1.1              | 1.24     | 1.45          | V                |

(Electrical Characteristics continue next page.)

MICROELECTRONICS

# **Second-Generation Power Factor Controller**

## **PRODUCTION DATA SHEET**

| Parameter                       | Symbol           | Test Conditions                                      | LX1562I/1563I |      |      | Units |

|---------------------------------|------------------|------------------------------------------------------|---------------|------|------|-------|

| Farameter                       | Sylliool         |                                                      | Min.          | Тур. | Max. | Units |

| Current Sense Comparator Sec    | tion             |                                                      |               |      |      |       |

| Input Bias Current              | I <sub>CSB</sub> | $0V \le V_{cs} \le 1.7V$                             | -1            | -0.3 | 1    | μA    |

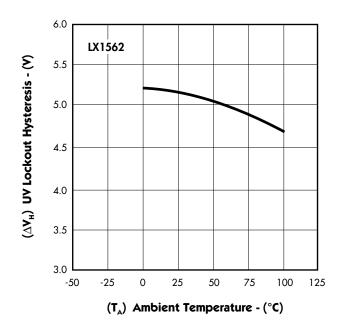

| Current Sense Delay to Output   | t <sub>d</sub>   | $E.A{OUT} = 3.7V, V_{CS} = 0$ to $1.2V, V_{M1} = 1V$ |               | 280  | 500  | ns    |

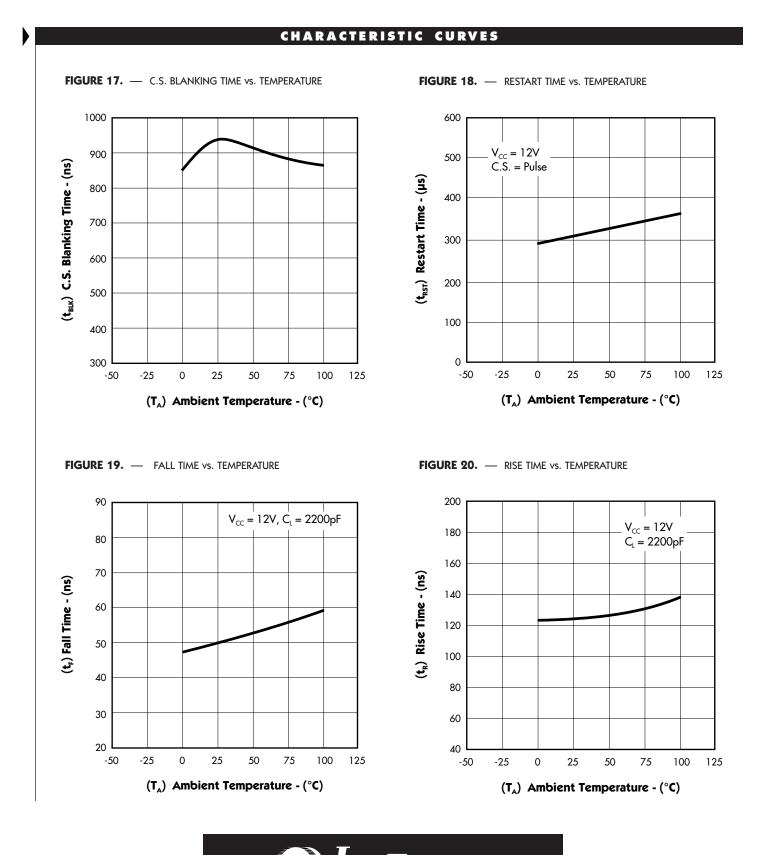

| C.S. Blanking Time              | t <sub>BLK</sub> |                                                      | 0.4           | 0.9  | 1.2  | μs    |

| C.S. Input Offset Voltage       | V                | $V_{EA0} = 2.2V, V_{M1} = 0V, I_{DETC} = 0V$         | -20           | 3    | 20   | mV    |

| Detect Section                  |                  |                                                      |               |      |      |       |

| Input Voltage Threshold - High  | V <sub>H</sub>   |                                                      | 1.6           | 1.72 | 1.9  | V     |

| Hysteresis                      | H <sub>D</sub>   |                                                      | 180           | 240  | 300  | m٧    |

| Input LO Clamp Voltage          | V <sub>DL</sub>  | I <sub>DET</sub> = 100μA                             | 0.4           | 0.62 | 0.85 | V     |

| Input HI Clamp Voltage          | V <sub>DZ</sub>  | I <sub>DET</sub> = 3mA                               | 7.0           | 7.8  | 8.6  | V     |

| InputCurrent                    | I <sub>DB</sub>  | $1V \le V_{DET} \le 6V$                              | -1            | -0.2 | 1    | μA    |

| Input HI/LO Clamp Diode Current | I <sub>DMX</sub> | $V_{det} < 0.9V, V_{det} > 6V$                       |               |      | ±3   | mA    |

| <b>Restart Timer Section</b>    |                  |                                                      |               |      |      |       |

| Restart Time                    | t <sub>RST</sub> |                                                      |               | 300  |      | µsec  |

| Output Driver Section           |                  |                                                      |               |      |      |       |

| Output High Voltage             | V <sub>PRH</sub> | $I_{L} = -10 \text{mA}, V_{N} = 12 \text{V}$         | 8.5           | 9    |      | V     |

| Output Low Voltage              | V <sub>PRL</sub> | $I_{L} = 10 \text{mA}, V_{IN} = 12 \text{V}$         |               | 0.8  | 1    | V     |

| Output Rise Time                | t <sub>R</sub>   | $C_{L} = 1000 pF$                                    |               | 130  | 200  | ns    |

| Output Fall Time                | t <sub>f</sub>   | $C_{L} = 1000 \text{pF}$                             |               | 50   | 120  | ns    |

| Maximum Output Voltage          | V                | V <sub>IN</sub> = 20V                                | 13            | 13.8 | 15   | V     |

Notes: 5. Because the reference is not brought out externally, these specifications are tested at probe only, and cannot be tested on the packaged part. They are guaranteed by design, and shown for illustrative purposes only.

This parameter, although guaranteed, is not tested in production.

Initial accuracy includes input offset voltage of error amplifier.

# **Second-Generation Power Factor Controller**

PRODUCTION **Δ** Α Τ Α **S** н е е т

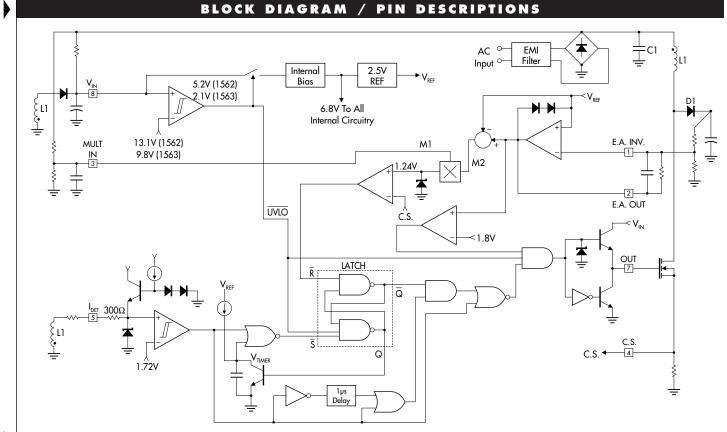

## **BLOCK DIAGRAM / PIN DESCRIPTIONS**

#### FUNCTIONAL DESCRIPTION

| Pin              | # | Description                                                                                                                                                                                                                                                                                      |

|------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IN</sub>  | 8 | Input supply voltage.                                                                                                                                                                                                                                                                            |

| GND              | 6 | Input supply voltage return. Must always be the lowest potential of all the pins.                                                                                                                                                                                                                |

| INV              | 1 | Inverting input of the Error Amplifier. The output of the Boost converter should be resistively divided to 2.5V and connected to this pin.                                                                                                                                                       |

| E.A. OUT         | 2 | The output of the Error Amplifier. A feedback compensation network is placed between this pin and the INV pin.                                                                                                                                                                                   |

| MULT IN          | 3 | Input to the multiplier stage. The full-wave rectified AC is divided to less than 2V and is connected to this pin.                                                                                                                                                                               |

| C.S.             | 4 | Input to the PWM comparator. Current is sensed in the Boost stage MOSFET by a resistor in the source lead, and is fed to this pin. An internal blanking circuit eliminates the RC low pass filter that otherwise is required to eliminate leading edge spike.                                    |

| I <sub>DET</sub> | 5 | A current driven logic input with internal clamp.<br>A second winding on the Boost inductor senses the flyback voltage associated with the zero crossing of the inductor current and feeds it to the $I_{DET}$ pin through a limiting resistor. Low on this pin causes $V_0$ (pin 7) to go high. |

| OUT              | 7 | PWM output pin. A totem-pole output stage specially designed for direct driving the MOSFET.                                                                                                                                                                                                      |

# Second-Generation Power Factor Controller

### PRODUCTION DATA SHEET

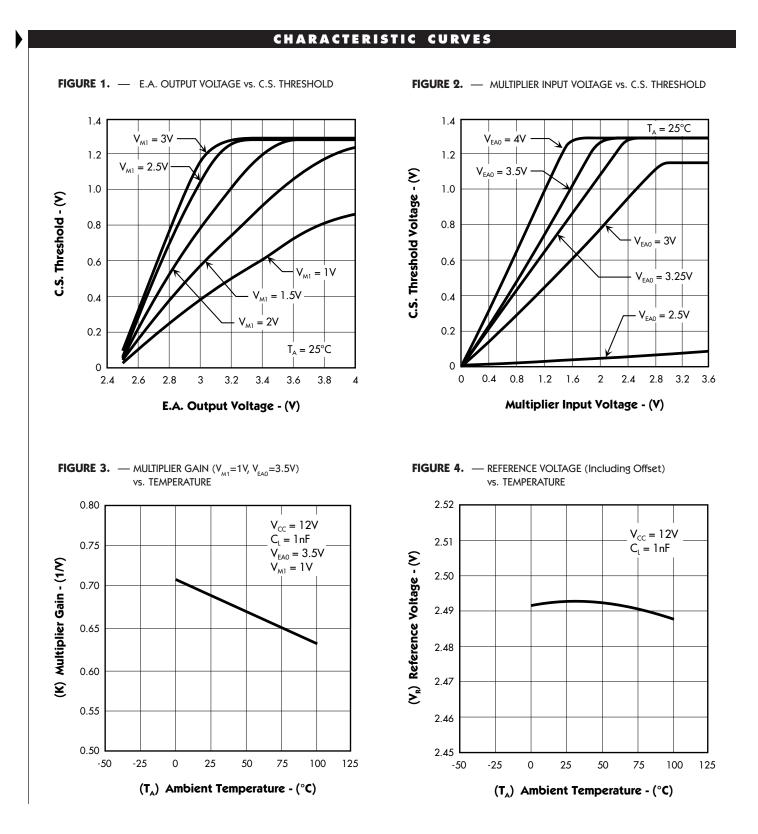

## GRAPH / CURVE INDEX

### **Characteristic Curves**

#### FIGURE #

- 1. E.A. OUTPUT VOLTAGE vs. C.S. THRESHOLD

- 2. MULTIPLIER INPUT VOLTAGE vs. C.S. THRESHOLD

- 3. MULTIPLIER GAIN (V<sub>M1</sub>=1V, V<sub>EA0</sub>=3.5V) vs. TEMPERATURE

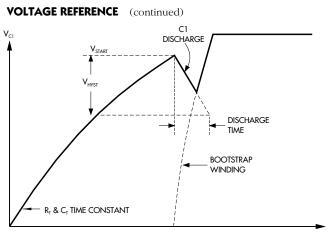

- 4. REFERENCE VOLTAGE (Including Offset) vs. TEMPERATURE

- 5. E.A. INPUT BIAS CURRENT vs. TEMPERATURE

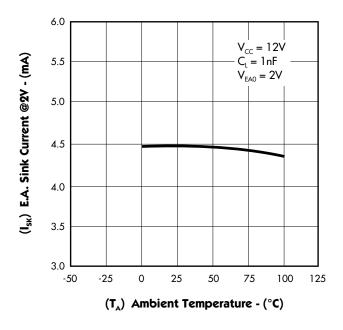

- 6. E.A. SINK CURRENT @2V vs. TEMPERATURE

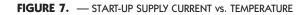

- 7. START-UP SUPPLY CURRENT vs. TEMPERATURE (LX1563)

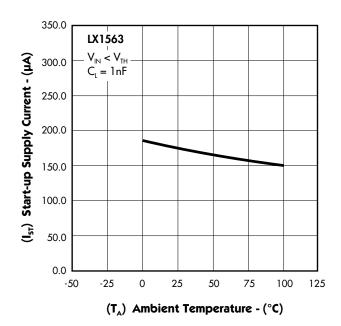

- 8. START-UP SUPPLY CURRENT vs. TEMPERATURE (LX1562)

- 9. START-UP THRESHOLD vs. TEMPERATURE (LX1562)

- 10. START-UP THRESHOLD vs. TEMPERATURE (LX1563)

- 11. UV LOCKOUT HYSTERESIS vs. TEMPERATURE (LX1562)

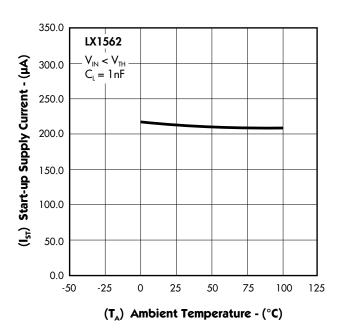

- **12.** UV LOCKOUT HYSTERESIS vs. TEMPERATURE (LX1563)

- **13.** I<sub>DET</sub> THRESHOLD HIGH vs. TEMPERATURE

- 14. I<sub>DET</sub> INPUT HYSTERESIS vs. TEMPERATURE

- 15. RUN-AWAY COMPARATOR THRESHOLD vs. TEMPERATURE

- 16. C.S. DELAY TO OUTPUT vs. TEMPERATURE

- 17. C.S. BLANKING TIME vs. TEMPERATURE

- **18.** RESTART TIME vs. TEMPERATURE

- 19. FALL TIME vs. TEMPERATURE

- 20. RISE TIME vs. TEMPERATURE

- 21. SUPPLY CURRENT vs. SUPPLY VOLTAGE (LX1562)

- 22. SUPPLY CURRENT vs. SUPPLY VOLTAGE (LX1563)

- 22a. MAXIMUM MULTIPLIER OUTPUT VOLTAGE vs. TEMPERATURE

### FIGURE INDEX

### **IC Description**

## FIGURE #

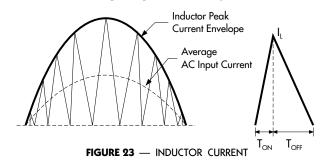

- INDUCT CURRENT

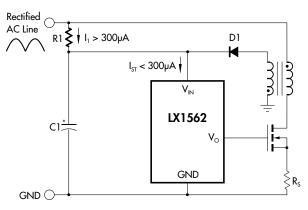

TYPICAL APPLICATION OF START-UP CIRCUITRY

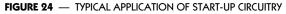

- **25.** START-UP CAPACITOR VOLTAGE

- 26. VOLTAGE REFERENCE vs. TEMPERATURE

- 27. THE AMPLIFIER CONFIGURED AS AN INTEGRATOR FOR LOOP COMPENSATION

- 28. MULTIPLIER SECTION

- 29. CURRENT SENSE SECTION

- 30. START-UP TIMER

### **Application Information**

#### FIGURE #

- **31.** TYPICAL APPLICATION OF THE LX1562 IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL

- 32. NORMALIZED OPERATING FREQUENCY vs. OFF-TIME DUTY CYCLE

- 33. INDUCT CURRENT

- 34. LOAD TRANSIENT RESPONSE CIRCUIT

- 35. FLYBACK VOLTAGE ACROSS I DET WINDING

### **Typical Applications**

#### FIGURE #

- **36.** TYPICAL APPLICATION OF THE LX1562 IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL - **120V**

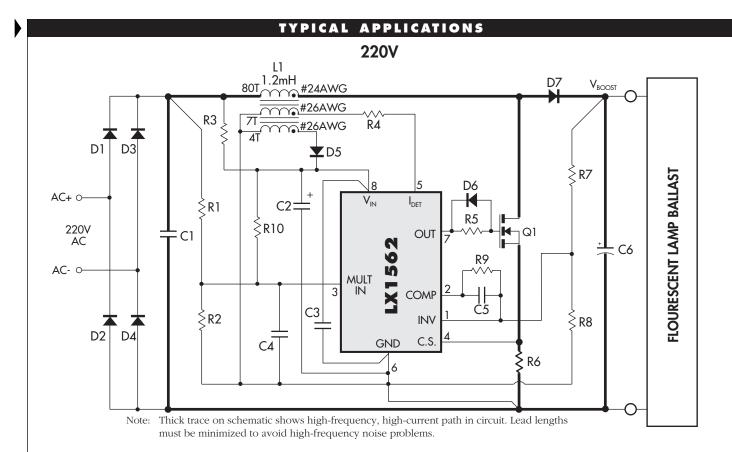

- **37.** TYPICAL APPLICATION OF THE LX1562 IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL **220V**

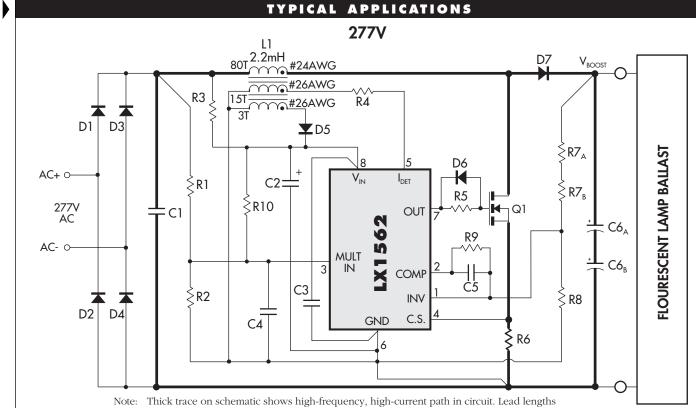

- 38. TYPICAL APPLICATION OF THE LX1562 IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL - 277V

## **SECOND-GENERATION POWER FACTOR CONTROLLER**

**PRODUCTION DATA SHEET**

## **SECOND-GENERATION POWER FACTOR CONTROLLER**

**PRODUCTION DATA SHEET**

#### FIGURE 6. — E.A. SINK CURRENT @2V vs. TEMPERATURE

FIGURE 8. — START-UP SUPPLY CURRENT vs. TEMPERATURE

## **SECOND-GENERATION POWER FACTOR CONTROLLER**

**PRODUCTION DATA SHEET**

FIGURE 12. — UV LOCKOUT HYSTERESIS vs. TEMPERATURE

## **Second-Generation Power Factor Controller**

**PRODUCTION DATA SHEET**

## **SECOND-GENERATION POWER FACTOR CONTROLLER**

**PRODUCTION DATA SHEET**

Copyright © 1996 Rev. 1.3 12/96

# SECOND-GENERATION POWER FACTOR CONTROLLER

**PRODUCTION DATA SHEET**

# SECOND-GENERATION POWER FACTOR CONTROLLER

### PRODUCTION DATA SHEET

### FUNCTIONAL DESCRIPTION

The operation of the IC is best described by referring to the block-diagram. The output of the multiplier stage generates a voltage proportional to the product of the rectified AC line and the output of the error amplifier. This voltage serves as the reference for the inductor peak current that is sensed by the resistor in series with the external power MOSFET. When the sense voltage exceeds this threshold, C.S. comparator trips and resets the latch as well as turning the power MOSFET off.

The energy stored during switch on-time is now transferred and stored in the output capacitor, causing the inductor current

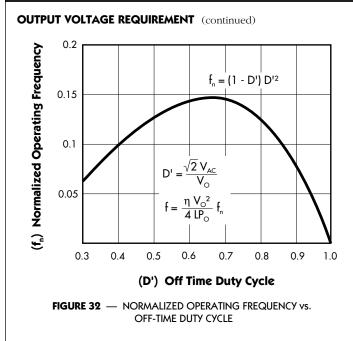

to ramp down. When current reaches zero level (inductor runs out of energy), boost diode (D1) stops conducting and the residual inductor energy and the drain to source capacitance of the power MOSFET create an LC tank circuit which causes drain voltage to resonate at this frequency. The resonating voltage is detected by the secondary winding (Idet winding) of the inductor. When this voltage swings negative "I detect" pin senses it and activates the blanking circuit , sets the latch, and turns power MOSFET on, repeating the cycle. This operation continues for the entire cycle of the AC rectified input resulting in an inductor current as shown in Figure 23. The high frequency content of this current is then filtered by the input capacitor (C1) resulting in a sine wave input current in phase with the AC line voltage.

Output voltage regulation is accomplished when the error amplifier compares this voltage to an internal 2.5V reference and generates an error voltage. This voltage then controls the amplitude of the multiplier output adjusting the peak inductor current proportional to the load and line variations, maintaining a well regulated voltage.

#### IC DESCRIPTION

#### UNDERVOLTAGE LOCK OUT

The LX1562/63 undervoltage lock-out is designed to maintain an ultra low quiescent current of less than 300µA, while guaranteeing the IC is fully functional before the output stage is activated. Comparing this to the SG3561A device, a 40% reduction in start-up current is achieved, resulting in 40% less power dissipation in the start-up resistor. This is especially important in electronic ballast applications that are designed to operate in harsh environments, with convection cooling as the only means of heat dissipation.

Figure 24 shows an efficient supply voltage using the ultra low start-up current of the LX1562 in conjunction with a bootstrap winding off of the power transformer. Circuit operation is as follows:

The start-up capacitor (C1) is charged by current through resistor (R1) minus the start-up current drawn by the IC. This resistor is typically chosen to provide 2X the maximum start-up current at low line to guarantee start-up under the worst case condition. Once the capacitor voltage reaches the start-up threshold, the IC turns on, starting the switching cycle. The operation of the IC demands an increase in operating current which results in discharging the capacitor. During the discharge cycle, the flyback voltage of the auxiliary winding is rectified and filtered via rectifier (D1) and charges the capacitor above the minimum operating voltage of the device and takes over as the supply voltage. The start-up capacitor and auxiliary winding must be selected such that it satisfies worst case IC conditions. Figure 25 shows start-up time and voltage of capacitor C1. Table 1 shows the start-up voltage and hysteresis for LX1562 and LX1563. The LX1562 is used for stand alone pre-regulator applications while LX1563 is ideal for applications where supply voltage is derived elsewhere and requires less than 14V start-up.

| TABLE 1 |                     |                       |  |  |

|---------|---------------------|-----------------------|--|--|

| Part #  | Start-Up<br>Voltage | Hysteresis<br>Voltage |  |  |

| LX1562  | 13.1V               | 5.2V                  |  |  |

| LX1563  | 9.8V                | 2.1V                  |  |  |

## SECOND-GENERATION POWER FACTOR CONTROLLER

**PRODUCTION DATA SHEET**

### IC DESCRIPTION

FIGURE 25 — START-UP CAPACITOR VOLTAGE

#### **VOLTAGE REFERENCE**

The voltage reference is a low drift bandgap design which provides a stable  $\pm 2.5V$  output with maximum of  $\pm 1.5\%$  initial accuracy. This voltage is internally tied to the non-inverting input of the amplifier and is not available for external connection. The initial accuracy of the reference includes error amplifier input offset voltage. Figure 26 shows typical variation of the reference voltage vs. temperature.

FIGURE 26 — REFERENCE VOLTAGE (Including Offset) vs. TEMPERATURE

#### ERROR AMPLIFIER

The error amplifier is an internally compensated op-amp with access to the inverting input and the output pin. The noninverting input is internally connected to the voltage reference and is not available for external connection. The amplifier is designed for an open loop gain of 80dB, along with a typical bandwidth of 1.7MHz and 49 degrees of phase margin. The boost output voltage of the power factor pre-regulator is divided down and monitored by the inverting input. Input bias current (0.5µA max) can cause an output voltage error that is equal to the product of the input bias current and the value of the upper divider resistor. The amplifier's output is available for external loop compensation. Typically, the loop bandwidth is set below 10Hz in order to reject the low frequency ripple associated with 2X the line frequency. For example, if the error amplifier is configured as an integrator with 1.2Hz bandwidth, it will have 40dB ripple rejection at 120Hz frequency. This means that if the output of the error amp is allowed to have 100mV of ripple, the boost converter must be limited to less than 10V of ripple on its output.

To prevent boost output run away condition that may occur during removal of the output load, a separate comparator monitors the E.A. output voltage and compares it to an internal 1.8V reference. When load is removed, E.A. output swings lower than 1.8V, trips the comparator and turns output driver off till the inverting input voltage drops below 2.5V. At this point, the E.A. output swings positive, turns the output driver back on and repeats the cycle until the load is returned to normal condition.

To reduce output overshoot during line and load transients, the E.A. output is clamped to two diode drops above the reference voltage. This prohibits the amplifier from being saturated, allowing it to recover faster thus minimizing the boost voltage overshoot.

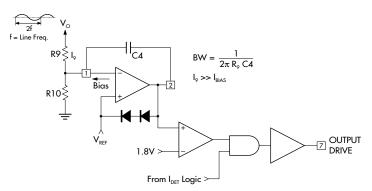

FIGURE 27 — THE AMPLIFIER CONFIGURED AS AN INTEGRATOR FOR LOOP COMPENSATION

## Second-Generation Power Factor Controller

**PRODUCTION DATA SHEET**

## IC DESCRIPTION

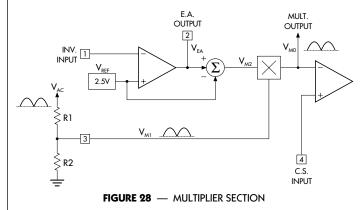

### MULTIPLIER

The LX1562/63 features a one quadrant multiplier stage having two inputs. One  $(V_{M2})$  is internally driven by a DC voltage which is the difference of E.A. output and  $V_{REF}$ . The other  $(V_{M1})$ , is connected to an external resistor divider monitoring the rectified AC line. The output of the multiplier which is a function of both inputs, controls inductor peak current during each cycle of operation. This allows the inductor peak current to follow the AC line thus forcing the average input current to be sinusoidal.

The multiplier is in the linear region if the  $V_{_{M1}}$  input is limited to less than 2V and the E.A. output is kept below 3.5V under all line and load conditions. The output is internally clamped to 1.24V typically to limit the MOSFET peak current during turn on or under excessive load conditions. The equation below describes the relationship between multiplier output voltage and the its inputs.

$$V_{M0} = K * V_{M1} * (V_{EA0} - V_{REF})$$

where: K = Multiplier gain (typ. 0.65)  $V_{M1}$  = Voltage at pin3 (0 to 2V)  $V_{EA0}$  = Error amp output voltage (2.5 to 3.5V)  $V_{M0}$  = Multiplier output voltage

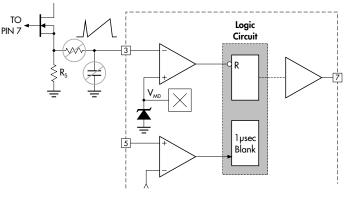

#### CURRENT SENSE COMPARATOR

Current sense comparator is configured as a PNP input differential stage with one input internally tied to the multiplier output and the other available for current sensing. Current is converted to voltage using an external sense resistor in series with the external power MOSFET. When sense voltage exceeds the threshold set by the multiplier output, the current sense comparator terminates the gate drive to the MOSFET and resets the PWM latch. The latch insures that the output remains in a low state after the switch current falls back to zero. The LX1562/63 features a leading edge blanking circuit that eliminates the need for an external RC filter otherwise required for proper operation of the circuit. This function is described in detail under "current detect logic" section.

The current sense comparator voltage is limited by an internal 1.24V (typ.) voltage clamp of the multiplier output. Therefore maximum switch current is typically given by:

$$I_{PK(MAX)} = 1.24 V / R_{s}$$

Maximum switch peak current happens at full load and minimum line conditions.

FIGURE 29 — CURRENT SENSE SECTION

#### **CURRENT DETECT LOGIC**

The function of "current detect logic" is to sense the operating state of the boost inductor and to enable the output driver accordingly. To achieve this, the downward slope of the inductor current is indirectly detected by monitoring the voltage across a separate winding and connecting it to the detector input "I<sub>DET</sub>" pin. Once the inductor current reaches ground level, the voltage across the winding reverses polarity and changes the "I<sub>DET</sub>" input and the comparator output to the low state (See Figure 30). When comparator changes state, it sets the latch and turns on the output driver for a period of 1µs (typ.) regardless of any changes in the latch output ( $\overline{Q}$ ) within this period. This ensures that if the C.S. comparator changes state due to any turn-on spike, the driver output remains on and does not turn off prematurely.

However if the spike lasts longer than 1µs, the output driver turns off and the MOSFET stops conducting. This type of digital current sense blanking which is not amplitude dependent has higher noise immunity than the commonly used external RC filtering, allowing for more flexibility in board layout.

Since inductor voltage swings both positive and negative, internal voltage clamping is provided to protect the IC. The

## Second-Generation Power Factor Controller

PRODUCTION DATA SHEET

## IC DESCRIPTION

#### CURRENT DETECT LOGIC (continued)

upper 7.8V clamp prevents input overvoltage breakdown during switch off time, while during the on time the lower 0.7V clamp prevents substrate injection. An internal current limit resistor protects the lower clamp transistor in case the " $I_{DET}$ " pin is accidently shorted to ground.

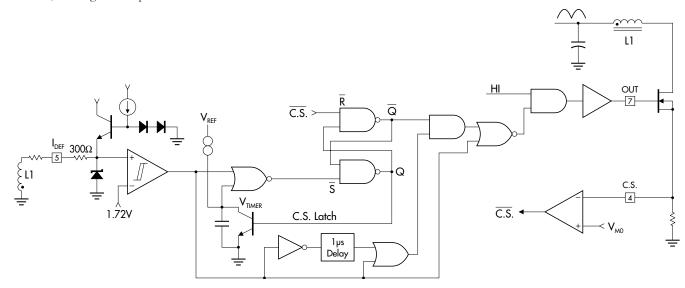

#### START-UP TIMER

A start-up timer circuit eliminates the need for an external oscillator when used in stand alone applications. The timer, as shown in Figure 30, provides a means to automatically start the pre converter if the latch output  $\overline{Q}$  comes up in a wrong (HI) state. The timer capacitor ramps up and resets the latch to a low state, turning the output driver on.

#### OUTPUT DRIVER STAGE

The LX1562/63 output driver is designed for direct driving of an external power MOSFET. It is a totem pole stage with ±500mA peak current capability. This typically results in a 130ns rise and fall times into a 1000pF capacitive load. Additionally the output is held low during the undervoltage condition to ensure that the MOSFET remains in the off state until supply voltage reaches the start-up threshold.

Internal voltage clamping ensures that output driver is always lower than 13.8V (typ.) when supply voltage variation exceeds more than rated  $V_{\rm GS}$  threshold (typ 20V) of the external MOSFET. This eliminates an external zener diode and extra power dissipation associated with it that otherwise is required for reliable circuit operation.

FIGURE 30 — START-UP TIMER & CURRENT DETECT LOGIC CIRCUITRY

## Second-Generation Power Factor Controller

**PRODUCTION DATA SHEET**

### **APPLICATION INFORMATION**

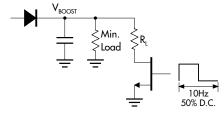

#### TYPICAL APPLICATION

The application circuit shown in Figure 31 uses the LX1562 as the controller to implement a boost type power factor regulator. The I.C. controls the regulator, such that the inductor current is always operating in a discontinuous conduction mode with no current gaps. This mode of operation has several advantages over the fixed frequency discontinuous conduction mode: 1) The switching frequency adjusts itself to the AC line envelope, causing a sinusoidal current draw, 2) Since there is no current gap between the switching cycles, the inductor voltage does not oscillate, causing less radiated noise, 3) The lower peak inductor current causes less power dissipation in the power MOSFET.

A set of formulas have been derived specifically for this mode, and are used throughout the design procedure. An example with the following specifications for the boost converter is given as:

| Input Voltage Range       | - | 100 to 130V RMS     |

|---------------------------|---|---------------------|

| Output Power              | - | 80W                 |

| Efficiency                | - | 95% at full load    |

| Power Factor              | - | > 0.99 at full load |

| Total Harmonic Distortion | - | < 10% at full load  |

|                           |   |                     |

followed by a step by step design procedure which walks through component selection.

#### **OUTPUT VOLTAGE REQUIREMENT**

Since the converter is a boost type topology, it requires the output voltage to always be higher than the input voltage. It is recommended to select this voltage at least 15% higher than the maximum input voltage in order to: A) Avoid the inductor saturation during line transience, and B) To keep the operating frequency above the audible range at high line.

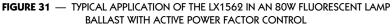

Figure 32 (next page) shows that when boost voltage is selected near the maximum AC line, the increase in off-time could reduce the operating frequency below the audible frequency and cause inductor humming. In fact, Figure 32 (next page) shows

that for  $\pm 13\%$  (100V to 130V) change in the line voltage the optimum range of the operating frequency is when off-time duty cycle (D') is between 0.57 and 0.75. This means that the boost voltage needs to be 245V when selecting D' = 0.75 at maximum AC line.

In this example, D' is chosen to be 0.8, to slightly reduce the voltage rating of the back end DC to AC fluorescent lamp inverter. This sets the boost voltage at:

$$V_{o} = \frac{130 * \sqrt{2}}{0.8} = 230V$$

## **Second-Generation Power Factor Controller**

**PRODUCTION DATA SHEET**

### **APPLICATION INFORMATION**

### INDUCTOR PEAK CURRENT

It can be shown by referring to Figure 33 that the inductor peak current is always twice the average input current.

Maximum peak input current can be calculated using:

$$I_{p} = \frac{2P_{o}}{\eta V_{p}}$$

where:  $\eta \equiv \text{Converter efficiency}$  $V_p \equiv \text{Peak AC input voltage}$

assuming:  $\eta = 95\%$ ,  $P_{\Omega} = 80W$ ,  $V_{P_{min}} = 100\sqrt{2} = 141$

$$I_{p} = \frac{2 \times 80}{(.95)(141)} = 1.2A$$

$$I_{LP/min AC} = 2 * 1.2 = 2.4A$$

### INDUCTOR DESIGN

The inductor value is calculated assuming a 50KHz operating frequency at the nominal AC voltage using the following equation:

$$L_{1} = \frac{\eta \frac{V_{o} \cdot V_{p}}{V_{o}} T V_{p}^{2}}{4 P_{o}} \quad \text{where:} \quad \eta \equiv \text{Efficiency} \\ V_{o} \equiv \text{Output DC voltage} \\ V_{p} \equiv \text{Peak AC input voltage} \\ T \equiv \text{Switching period} \\ P_{o} \equiv \text{Output Power} \end{cases}$$

$$L_{1} = \frac{.95\left(\frac{2.00}{230}\right) 20 * 10^{-6} * (120\sqrt{2})^{2}}{4 * 80} = 448\mu H$$

choose  $T = 20\mu sec (50kHz)$

Figure 32 shows that at nominal AC line (D' = 0.74) the normalized frequency is 0.142 and dropping to 0.13 at maximum line condition. This translates to a 10% drop in operating frequency which is still well above the audible range.

Once the inductance is known, we can either use the area product method (AP) or the  $K_g$  (based on copper losses method), for selecting proper core size. In this example, we apply the  $K_g$  approach using the following steps:

**Step 1:** Calculate K<sub>a</sub> using

$$K_{g} = \frac{\Omega}{P_{cU}} \left(\frac{L_{1}L_{P}^{2}}{B}\right)^{2}$$

where:  $L_{1} \equiv \text{Required inductance}$

$\Omega \equiv 1.724 * 10^{-8} \text{ m}$

$B \equiv \text{Maximum flux density}$

$I_{LP} \equiv \text{Maximum peak inductor current}$

$P_{cU} \equiv \text{Maximum copper dissipation}$

Assume:  $P_{cU} = 1.6W$  (2% of total output)

$$K_{g} = \frac{1.724 * 10^{-8}}{1.6} \left[ \frac{450 * 10^{-6} * (2.4)^{2}}{0.15} \right]^{2} = 3.21 * 10^{-12} \text{ m}^{5}$$

## Second-Generation Power Factor Controller

PRODUCTION DATA SHEET

APPLICATION INFORMATION

#### **INDUCTOR DESIGN** (continued)

**Step 2:** Choose a core with higher

$$K_g$$

than the one calculated in

Step 1.

$K_g/core = k \frac{A_w A_E^2}{l_w}$

where:  $k \equiv$  Winding coefficient (typ. k=0.4)

$A_w \equiv$  Bobbin window area

$A_E \equiv$  Effective core area

$l_w \equiv$  Mean length per turn

$K_g$  factor for TDK PQ2625:

$A_w = 47.7 \text{mm}^2$

$A_E = 118 \text{mm}^2$

$l_w = 56.2 \text{mm}$

$$K_g = 0.4 \frac{(47.7) (118)^2}{56.2} (mm)^5 = 4.7 * 10^{-12} m^5$$

Step 3: Determine number of turns.

$$N = \frac{L I_{LP}}{B A_{E}}$$

$$N = \frac{450 * 10^{-6} * 2.4}{0.15 * 118 * 10^{-6}} = 61 \text{ turns}$$

$$A_{WIRE} = k \frac{A_{W}}{N} = 0.4 \frac{47.7}{61} = 0.31 \text{ mm}^{2}$$

choose #22 AWG with r =  $0.0165\Omega$ /feet resistance.

$$R_{w} = N * l_{w} * r$$

$$R_{w} = 0.185\Omega$$

Step 4: Calculate air gap.

$$l_{g} = \frac{\mu_{o} N^{2} A_{E}}{L}$$

$$l_{q} = \frac{4\pi * 10^{-7} * (61)^{2} * 118 * 10^{-6}}{450 * 10^{-6}} = 0.122 \text{ cm} = 48 \text{ mil}$$

#### **CURRENT SENSE RESISTOR**

Current sense resistor, R6 is selected using the minimum multiplier output clamp voltage and the maximum inductor peak current such that:

$$\mathrm{R6} = \frac{V_{\mathrm{CLAMP(MIN)}}}{I_{\mathrm{L}~(\mathrm{MAX})}} = \frac{1.1}{2.4} = 0.45 \Omega$$

Power dissipation is approximated by:

$$\begin{split} P_{\rm R} &\approx \frac{1}{6} \ I_{2\,({\rm MAX})}^2 \ (1 - D'_{\rm MIN}), \quad \text{where } D'_{\rm MIN} = 1 - \frac{\sqrt{2} \ V_{\rm AC(MIN)}}{V_{\rm BOOST}} \\ P_{\rm R} &\approx \frac{1}{6} \ (2.4)^2 \ (1 - 0.61) = 0.374 \end{split}$$

Select **THREE** 1.3 $\Omega$ , <sup>1</sup>/<sub>4</sub>W carbon comp resistors in parallel.

#### MULTIPLIER COMPONENT SELECTION

Calculate R1 & R2 resistor values such that under low line AC input the multiplier output is lower than the minimum clamp voltage.

$$\frac{\text{R2}}{\text{R1} + \text{R2}} * \sqrt{2} \text{ V}_{\text{AC (MIN)}} * \text{K} * (\text{V}_{\text{EA0 (MAX)}} - \text{V}_{\text{REF}}) < \text{V}_{\text{CLAMP (MIN)}}$$

where:  $K \equiv$  Mult. Gain

$V_{EA)(MAX)} \equiv$  Maximum error amp output where multiplier is still in linear range. This voltage is  $\approx 3.5$ V.

For K = 0.65 &  $V_{\text{CLAMP (MIN)}}$  = 1.1V, the ratio of R1/R2 is:

$$\frac{R1}{R2} > 83$$

Assuming R1 is selected to be:

R2 =

$$\frac{2.2M}{83}$$

= 26.4k (1%) select R<sub>2</sub> = 26.7k (1%)

\* For high input applications such as 277V, R1 must be divided into two resistors in series to meet the maximum rated voltage of the resistors.

To improve THD further (typ. 2-3%), a high value resistor can be connected from the supply voltage to this pin to allow an increase in the switch on-time at the zero crossing by adding an effective offset at the multiplier output.

#### ERROR AMPLIFIER COMPONENT SELECTION

Boost voltage is programmed with R7 & R8 resistor dividers using the following equation:

$$\frac{R7}{R8} = \frac{V_{BOOST}}{V_{RFF}} -1,$$

assuming that the product of R7 and the E.A. input bias current does not cause significant error in the output voltage setting.

Assuming  $\mathbf{R7} = \mathbf{1M\Omega}$  (for output voltage of higher than 250V, two resistors may be added in series to meet the voltage requirement of the resistor.)

$$\Delta V_{\text{ERROR}}$$

(10<sup>6</sup>) (0.5 \* 10<sup>-6</sup>) = 0.5V, which is < 0.25% of the output voltage.

Calculating R8:

$$R8 = \frac{R7}{\frac{V_{BOOST}}{V_{REF}}} - 1 = 11k \quad (1\%)$$

Worst case output tolerance is the total of  $\pm 3.75\%$  which is the sum of  $\pm 1.5\%$  (Ref),  $\pm 2\%$  (resistor dividers), and  $\pm 0.25\%$  (E.A. input bias current).

## Second-Generation Power Factor Controller

**PRODUCTION DATA SHEET**

### APPLICATION INFORMATION

#### ERROR AMPLIFIER COMPONENT SELECTION (continued)

Capacitor C5 is primarily selected to reject the output ripple associated with twice the line frequency. For a 40dB ripple rejection:

C5

$$\geq \frac{100}{2\pi f_1 R7}$$

where  $f_1 = 2x$  line frequency

C5  $\geq \frac{100}{2\pi * 120 * 2.2 * 10^6} = 0.062\mu F$ , Select **C5 = 0.1 $\mu$ F**

Resistor R9 can be used to improve load transient response at the cost of loosing 1 or 2% of load regulation. The value of this resistor should be much greater than R8:

### R9 = 620k

One way of achieving desired load transient response without resorting to a complex mathematical model of the converter, is to dynamically switch the output load and empirically find the compensation network. The value of resistor R9 is selected using the method shown in Figure 34.

FIGURE 34 — LOAD TRANSIENT RESPONSE CIRCUIT

## I<sub>DETECT</sub> COMPONENT SELECTION

Figure 35 shows voltage envelope generated by flyback voltage across  $I_{\mbox{\tiny DFT}}$  winding:

Select turns ratio n such that,

$$n = \frac{5V}{V_{BOOST} - \sqrt{2} V_{AC (MAX)}}$$

$$n = \frac{5V}{\sqrt{2}} = 0.11$$

FIGURE 35 — FLYBACK VOLTAGE

ACROSS I DET WINDING

$I_{_{\rm DET}}$  winding turns are selected to be 7T.

$230 - \sqrt{2} * 130$

and R4 resistor:

$$\frac{n * V_{BOOST}}{3 * 10^{-3}} < R4 < 500k$$

$$\frac{0.11 * 230}{3 * 10^{-3}} < R4 < 500k, \text{ or } 8.4k < R4 < 500k$$

Select R4 = 22k

SUPPLY VOLTAGE

Resistor R3 must be selected such that it ensures converter startup at low line and is rated for high line power dissipation.

$$R3 < \frac{\sqrt{2} V_{AC (MIN)}}{I_{ST (MAX)}} \quad \text{where: } I_{ST} \equiv \text{Maximum start-up} \\ V_{T} \equiv \text{Start-up voltage} \\ T_{ST(MAX)}^{ST} \equiv \text{Maximum start-up} \\ R3 < \frac{\sqrt{2} * 100}{0.3 * 10^{-3}} = 466 \text{k}\Omega$$

$R3 > 4 V_{AC(MAX)}$  (to keep power dissipation below 0.5W)

R3 > 68k, select **R3 = 120k.**

Start-up time of converter is given by:

$$T_{\text{ST (MAX)}} \approx C2 \frac{V_{\text{ST}}}{\frac{\sqrt{2} V_{\text{AC (MIN)}}}{R_3} - I_{\text{ST}}}$$

for our application this will be  $25 \text{ms/}\mu\text{F}$ .

The start-up capacitor is selected such that capacitor discharge time is always longer than the time it takes for the bootstrap voltage to reach above the minimum start-up threshold of the IC.

$$C3 < \frac{I_{OP} * \Delta t}{\Delta V_{MIN}} \quad \text{where: } I_{OP} \equiv \text{Maximum dynamic} \\ \text{supply current of the IC} \\ \Delta t \equiv \text{Rise time of the} \\ \text{bootstrap voltage} \\ \Delta V_{MIN} \equiv \text{Minimum hysteresis} \\ \text{voltage (4V for 1562, 1.7V for 1563)} \\ C3 < \frac{10 * 10^{-3} * 10 * 10^{-3}}{4} = 29 \mu \text{F}$$

Select C3 = 33µF.

Start-up time is approximately 0.8 seconds.

The auxiliary winding turns are selected such that it provides 15V of operating voltage.

$$N_s \approx N_p^* \cdot \frac{V_s}{V_o} = 61^* \cdot \frac{V_s}{V_o} = 4T$$

However, in this example  $I_{DETECT}$  winding is used to power the IC which eliminates the need for a third winding. This is possible since the internal clamping of the output drive limits the gate drive voltage to 14V (typ.) if the supply voltage exceeds this limit.

## **SECOND-GENERATION POWER FACTOR CONTROLLER**

**PRODUCTION DATA SHEET**

### **APPLICATION INFORMATION**

#### POWER MOSFET SELECTION

The voltage rating of MOSFET and rectifier must be higher than the maximum value of the output voltage.

$$V_{DS} \ge 1.2 V_{OMAX}$$

$V_{DS} \ge 282V$

The RMS current can be approximated by multiplying the RMS current at the peak of the line by 0.7.

$$I_{RMS} = 0.7 I_{LP} \sqrt{D/3} \qquad D \equiv On-time duty cycle$$

$$D = 0.39 \text{ at } V_{AC} = 100V$$

$$I_{LP} = 2.4A$$

$$I_{RMS} = (0.7)(2.4)(\sqrt{.39/3}) = 0.61A$$

$$R_{DS} \leq \frac{P_{DC}}{I_{RMS}^{2}}$$

$$P_{DC} \equiv allowable power$$

$$I_{RMS}/triangle = I_{LP} \sqrt{D/3}$$

$P_{DC} \equiv$  allowable power dissipation. 1

$R_{DS} \le \frac{1}{0.61} = 1.6\Omega$

**IRF730 with R\_{DS} = 1\Omega and V\_{DS} = 400V** meets the above requirements.

#### INPUT RECTIFIER AND CAPACITOR SELECTION

The current through each diode is a half-wave rectified sine wave. The maximum current happens at minimum line with a peak value of 1.2A.

$$I_{AVE} = \frac{I_{PEAK}}{\pi} = \frac{1.2}{\pi} = 0.38A$$

choose 1N4004 with 1A rating.

$$P_{DISS} = (I_{AVE}) (V_F) = 0.38 \ge 0.344 W$$

$$T_J = T_A + P_D \ge \theta_{JA}$$

assuming  $\theta_{JA} = 65^{\circ}C/W$  for 1/8" lead length.

$$T_{t} = 80 + (.344)(65) = 102^{\circ}C$$

Assuming  $\phi$  is the percentage of allowable input current ripple, C1 can be calculated using the following equations:

$$R_{EFF} = \frac{2 P_{O}}{\eta I_{P}^{2}}$$

$$C1 \ge \frac{1}{\varphi \ 2\pi \ R_{EFF}} f_{SW}$$

f<sub>sw</sub> ≡ Switching frequency of inductor current at peak input voltage.

if

$$\varphi = 3\%$$

$$R_{EFF} = \frac{2 \times 80}{(.95)(1.2)^2} = 117\Omega$$

$$C1 \ge \frac{1}{(.03)(2\pi)(117)(50000)} = 0.9\mu F$$

choose 1µF, 250V capacitor.

#### OUTPUT CAPACITOR SELECTION

There are mainly two criteria for selecting the output capacitor: A large enough capacitance to maintain a low ripple voltage, and a low ESR value in order to prevent high power dissipation due to RMS currents.

The output capacitance can be approximated from the following equation:

$$C6 \ge \frac{I_{DC}}{2\pi f_{LINE} \Delta V} \qquad \text{where: } I_{DC} \equiv DC \text{ output current} \\ DV \equiv Output \text{ ripple} \\ I_{DC} = \frac{80}{230} = 0.348A$$

assuming 5% peak to peak ripple,

$$C6 \ge \frac{0.348}{2\pi (60) (11.5)} = 81\mu F$$

choose C6 = 100µF.

# SECOND-GENERATION POWER FACTOR CONTROLLER

**PRODUCTION DATA SHEET**

must be minimized to avoid high-frequency noise problems.

| Rei.                                                                                                         | Component                                                                                                                                                                                                                                                                                                                              | Manuf.                                                       | Ref.                             | Component                                                                                                                                                                                                            | Manuf.   |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| IC<br>Q1<br>D1-D4<br>D5<br>D6<br>D7<br>R1<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7<br>R8<br>R7<br>R8<br>R9<br>R10 | LX1562<br>PQ2625/H7C1 Core<br>IRF730, 400V, 1Ω rds<br>IN4004 1A, 400V<br>1N4935 1A<br>1N4148 (improves Q1 power dissipation)<br>MR854, 3A, 400V<br>2.2MΩ, $\pm 1\%$<br>26.7kΩ, $\pm 1\%$<br>100kΩ, $\frac{1}{2}W$<br>22kΩ<br>47Ω<br>1.5Ω, Carbon type (3X)<br>1MΩ, 1%<br>11kΩ, 1%<br>620kΩ (improves load transient response)<br>4.7MΩ | Linfinity<br>TDK<br>I.R.<br>Motorola<br>Motorola<br>Motorola | C1<br>C2<br>C3<br>C4<br>C5<br>C6 | QXF2E105KRPT<br>1µF/250V - Plastic Film (high freq.)<br>22µF/35V - Electrolytic<br>0.1µF/50V - Ceramic<br>0.1µF/50V - Ceramic<br>LGQ2G101MHS A/Z*<br>100µF/400V - Electrolytic<br>* A = 25mm diam.<br>Z = 22mm diam. | Nichicor |

A complete evaluation board is available from Linfinity Microelectronics Inc.

# **SECOND-GENERATION POWER FACTOR CONTROLLER**

**PRODUCTION DATA SHEET**

FIGURE 37 — TYPICAL APPLICATION OF THE LX1562 IN AN 80W FLUORESCENT LAMP BALLAST WITH ACTIVE POWER FACTOR CONTROL.

| Specifica<br>Ref.                                                                                                    | Component                                                                                                                                                                                                                                                                                                                                        | Manuf.                                                       | Ref.                              | Component                                                                                                                                                                                                                          | Manuf.   |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Ref.<br>IC<br>L1<br>Q1-D4<br>D5<br>D6<br>D7<br>R1<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7<br>R8<br>R7<br>R8<br>R9<br>R10 | LX1562<br>PQ2625/H7C1 Core<br>IRF830, 500V, $1.5\Omega$ rds<br>IN4007 1A, 1000V<br>1N4935 1A<br>1N4148 (improves Q1 power dissipation)<br>MR856, 3A, 600V<br>2.2MΩ, $\pm 1\%$<br>12kΩ, $\pm 1\%$<br>220kΩ, $\frac{1}{2}W$<br>22kΩ<br>47Ω<br>1.8Ω, Carbon type (2X)<br>1MΩ, 1%<br>6.19kΩ, 1%<br>620kΩ (improves load transient response)<br>2.7MΩ | Linfinity<br>TDK<br>I.R.<br>Motorola<br>Motorola<br>Motorola | C1<br>C2<br>C3<br>C4<br>C5<br>C6* | QXF2J224KRPT<br>$0.22\mu$ F/630V - Plastic Film<br>$22\mu$ F/35V - Electrolytic<br>$0.1\mu$ F/50V - Ceramic<br>$0.1\mu$ F/50V - Ceramic<br>LGQ2W680MHS A/Z*<br>$68\mu$ F/450V - Electrolytic<br>* A = 25mm diam.<br>Z = 22mm diam. | Nichicor |

A complete evaluation board is available from Linfinity Microelectronics Inc.

# SECOND-GENERATION POWER FACTOR CONTROLLER

**PRODUCTION DATA SHEET**

must be minimized to avoid high-frequency noise problems.

$\label{eq:Figure 38} \mbox{ Figure 38} \mbox{ mypical application of the LX1562 in an 80W} \mbox{ fluorescent Lamp Ballast with active power factor control.}$

| Reî.                                                                                                         | Component                                                                                                                                                                                                                                                                                                                                       | Manuf.                                                       | Ref.                             | Component                                                                                                                                                            | Manuf.   |

|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| IC<br>Q1<br>D1-D4<br>D5<br>D6<br>D7<br>R1<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7<br>R8<br>R7<br>R8<br>R9<br>R10 | LX1562<br>PQ2625/H7C1 Core<br>IRF830, 500V, 1.5Ω rds<br>IN4007 1A, 1000V<br>1N4935 1A<br>1N4148 (improves Q1 power dissipation)<br>MR856, 3A, 600V<br>2.2MΩ, $\pm$ 1%<br>10kΩ, $\pm$ 1%<br>390kΩ, $\frac{1}{2}$ W<br>22kΩ<br>47Ω<br>2.2Ω, Carbon type (2X)<br>499kΩ, 1% (2X)<br>5.23kΩ, 1%<br>620kΩ (improves load transient response)<br>2.2MΩ | Linfinity<br>TDK<br>I.R.<br>Motorola<br>Motorola<br>Motorola | C1<br>C2<br>C3<br>C4<br>C5<br>C6 | QXF2J224KRPT<br>0.22µF/630V - Plastic Film<br>22µF/35V - Electrolytic<br>0.1µF/50V - Ceramic<br>0.22µF/50V - Ceramic<br>UVZ2F470MEH (2X)<br>47µF/315V - Electrolytic | Nichicon |

A complete evaluation board is available from Linfinity Microelectronics Inc.

# **SECOND-GENERATION POWER FACTOR CONTROLLER**

**PRODUCTION DATA SHEET**

| Electrico<br>Specific                                                                     |                                                                                                                                                                                                                                                                                                                                               | 90-265VAC Input — 400VDC / 80W Output |                                   |                                                                                                                                                                                                            |          |  |  |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

| Ret.                                                                                      | Component                                                                                                                                                                                                                                                                                                                                     | Manuf.                                | Ref.                              | Component                                                                                                                                                                                                  | Manuf.   |  |  |

| IC<br>Q1<br>D1-D4<br>D5<br>D6<br>D7<br>R1<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7<br>R8<br>R9 | LX1562<br>PQ2625/H7C1 Core<br>IRF840, 500V, 1Ω rds<br>IN4007 1A, 1000V<br>1N4935 1A<br>1N4148 (improves Q1 power dissipatio<br>MR856, 3A, 600V<br>2.2MΩ, $\pm$ 1%<br>16.3kΩ, $\pm$ 1%<br>130kΩ, $\pm$ 1%<br>130kΩ, $\frac{1}{2}$ W<br>22kΩ<br>47Ω<br>1Ω, Carbon type (4X)<br>1MΩ, 1%<br>6.19kΩ, 1%<br>620kΩ (improves load transient response | Motorola                              | C1<br>C2<br>C3<br>C4<br>C5<br>C6* | QXF2J224KRPT<br>0.47µF/630V - Plastic Film<br>22µF/35V - Electrolytic<br>0.1µF/50V - Ceramic<br>0.33µF/50V - Ceramic<br>LGQ2W680MHS A/Z*<br>68µF/450V - Electrolytic<br>* A = 25mm diam.<br>Z = 22mm diam. | Nichicon |  |  |

A complete evaluation board is available from Linfinity Microelectronics Inc.

MICROELEC