# 75 VOLT 8 AMP MOSFET H-BRIDGE PWM MOTOR DRIVER/AMPLIFIER

4221

4707 Dev Road Liverpool, N.Y. 13088

(315) 701-6751

#### FEATURES:

- · Low Cost Complete H-Bridge

- 8 Amp Capability, 75 Volt Maximum Rating

- · Self-contained Smart Lowside/Highside Drive Circuitry

- · Shoot-through Protection

- · Isolated Case Allows Direct Heatsinking

- · Four Quadrant Operation, Torque Control Capability

- · Logic Level Disable Input

- · Logic Level High Side Enable Input for Special Modulation or Function

- · Internal Divider Reference for Threshold Voltage

#### **DESCRIPTION:**

The MSK 4221 is a complete H-Bridge circuit to be used for DC brushed motor control or Class D switchmode amplifiers. All of the drive/control circuitry for the lowside and highside switches are included internally. The user provides a digitally compatible PWM signal (a reference divider is provided for TTL compatability or the user provides their own to the VREF IN) for simultaneous amplitude and direction control in four quadrant mode. The internal drive circuitry will provide proper deadtime/shoot-through protection for each half-bridge. All N-channel FETs mean the best efficiency for the size, both in terms of on-resistance and switching capability. For an idle/sleep mode or for fault protection, a TTL compatible disable pin is provided so as to shut down all four transistors. The MSK4221 is constructed on a space efficient ceramic coated insulated metal substrate that can be directly connected to a heat

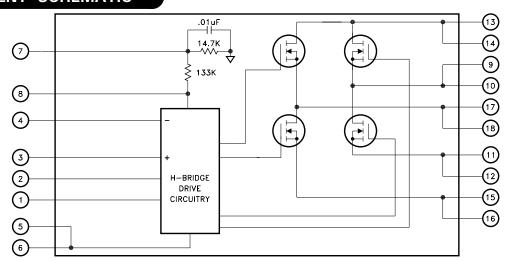

# **EQUIVALENT SCHEMATIC**

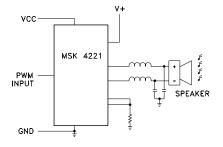

# TYPICAL APPLICATIONS

# VCC WSK 4221 PWM DC WOTOR GND DC WOTOR

1

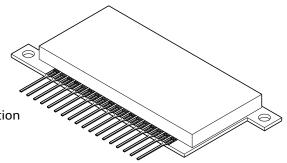

# PIN-OUT INFORMATION

1 HEN 18 Output B 2 Disable Output B Rsense B 3 Input 15 Rsense B 4 Vref in 14 V+ 5 Ground 6 Ground 13 V+ 7 Vref out 12 Rsense A 8 Vcc 11 Rsense A

10

Output A

Output A

# **ABSOLUTE MAXIMUM RATINGS**

| V +         | High Voltage Supply                          | $T_{ST}$ | Storage Temperature Range65°C to +150°C |

|-------------|----------------------------------------------|----------|-----------------------------------------|

| Vcc         | Logic Supply                                 | $T_LD$   | Lead Temperature Range 300°C            |

| louт        | Continuous Output Current 8A                 |          | (10 Seconds)                            |

| <b>I</b> PK | Peak Output Current                          | Tc       | Case Operating Temperature              |

| $V_OUT$     | Output Voltage Range GND-2V min. To V + max. |          | MSK422125°C to +125°C                   |

| hetaJC      | Thermal Resistance 5.3°C/W                   | Tл       | Junction Temperature + 150°C            |

|             | (Output Switches)                            |          |                                         |

# **ELECTRICAL SPECIFICATIONS**

All Ratings: Tc = +25°C Unless Otherwise Specified

|                                | Test Conditions ②                      |      | MSK 4221 |      |       |

|--------------------------------|----------------------------------------|------|----------|------|-------|

| Parameter                      |                                        |      | Тур.     | Max. | Units |

| OUTPUT CHARACTERISTICS         |                                        |      |          |      |       |

| VDS(ON) Voltage ①              | Each MOSFET ID = 10A ③                 | -    | 1.7      | 2.5  | V     |

| Instantaneous Forward Voltage  | Each MOSFET Is = 10A Intrinsic Diode ③ | -    | 2.0      | 2.5  | V     |

| Reverse Recovery Time ①        | Intrinsic Diode                        | -    | -        | 280  | nS    |

| Leakage Current 1              | Each MOSFET V + = 70V                  | -    | 1.0      | 25   | uA    |

| Vref Output                    | Ivref = 0mA                            | 1.16 | 1.2      | 1.23 | V     |

| Vcc SUPPLY CHARACTERISTICS     |                                        |      |          |      |       |

| Quiescent Bias Current         | Input = 0Vpc                           | -    | 20       | 25   | mA    |

| Vcc Voltage Range ①            |                                        | 9    | 12       | 16   | V     |

| INPUT SIGNAL CHARACTERISTICS ① |                                        |      |          |      |       |

| VREF Input Current - Low       |                                        | -2   | -        | -    | uA    |

| VREF Input Current - High      |                                        | -    | -        | 2    | uA    |

| Input Current - Low            |                                        | -2   | -        | -    | uA    |

| Input Current - High           |                                        | -    | -        | 2    | uA    |

| PWM Pulse Low Voltage          | Vref Out Connected to Vref In          | 0    | -        | 0.8  | V     |

| PWM Pulse High Voltage         | Vref Out Connected to Vref In          | 2.7  | -        | 5.0  | V     |

| PWM Frequency                  |                                        | -    | 45       | 250  | KHz   |

| LOGIC CONTROL INPUTS ①         |                                        |      |          |      |       |

|                                | Input Voltage LO                       | -    | -        | 0.8  | V     |

| Disable Input                  | Input Voltage HI                       | 2.7  | -        | -    | V     |

|                                | Input Current (DISABLE=0V)             | -    | -        | -135 | uA    |

|                                | Input Voltage LO                       | -    | -        | 0.8  | V     |

| HEN Input                      | Input Voltage HI                       | 2.7  | -        | -    | V     |

|                                | Input Current (HEN = 0V)               | -    | -        | -270 | uA    |

| SWITCHING CHARACTERISTICS ①    |                                        |      |          |      |       |

| Rise-Time                      |                                        | -    | 140      | 200  | nS    |

| Fall-Time                      |                                        | -    | 680      | 1000 | nS    |

| Dead-Time                      |                                        | -    | 100      | -    | nS    |

# NOTES:

2

Guaranteed by design but not tested. Typical parameters are representative of actual device performance but are for reference only.

Vcc = + 12V and VREF Out connected to VREF IN unless otherwise specified.

Measure using a 300µS pulse with a 2% Duty Cycle.

## **APPLICATION NOTES**

#### MSK 4221 PIN DESCRIPTIONS

**VCC** - Is the low voltage supply for powering internal logic and drivers for the lowside and highside MOSFETS. The supplies for the highside drivers are derived from this voltage.

**V**+ - Is the higher voltage H-bridge supply. The MOSFETS obtain the drive current from this supply pin. The voltage on this pin is limited by the drive IC. The MOSFETS are rated at 100 volts. Proper by-passing to **GND** with sufficient capacitance to suppress any voltage transients, and to ensure removing any drooping during switching, should be done as close to the pins on the module as possible.

**OUTPUT A** - Is the output pin for one half of the bridge. Increasing the duty cycle of the input causes increasing duty cycles at this output.

**OUTPUT B** - Is the output pin for the other half of the bridge. Decreasing the duty cycle of the input causes increasing duty cycles at this output.

**RSENSE A** - Is the connection for the bottom of the A half bridge. This can have a sense resistor connection to the V+ return ground for current limit sensing, or can be connected directly to ground. The maximum voltage on this pin is  $\pm 2$  volts with respect to GND.

**RSENSE B** - Is the connection for the bottom of the B half bridge. This can have a sense resistor connection to the V+ return ground for current limit sensing, or can be connected directly to ground. The maximum voltage on this pin is  $\pm 2$  volts with respect to GND.

**GND** - Is the return connection for the input logic and Vcc.

**INPUT** - Is digital input for controlling the PWM pulse width of the bridge. A duty cycle higher than 50% will produce greater than 50% duty cycle pulses out of OUTPUT A. A duty cycle lower than 50% will produce greater than 50% duty cycle pulses out of OUTPUT B.

**DISABLE** - Is the connection for disabling all 4 output switches. DISABLE high overrides all other inputs. When taken low, everything functions normally. An internal pullup to Vcc will keep DISABLE high if left unconnected.

**HEN** - Is the connection for enabling the high side output switches. When taken low, HEN overrides other inputs and the high side switches remain off. When HEN is high everything functions normally. An internal pullup to Vcc will keep HEN high if left unconnected.

**VREF OUT** - Is a pin providing a resistor divider network dividing Vcc voltage down to be used as a default reference level input for the INPUT signal threshold. It is set up primarily to be used as a TTL threshold. To use, just connect VREF OUT to VREF IN. VREF OUT is bypassed internally with a capacitor.

**VREF IN** - Is a pin provided to allow the user to tailor the INPUT threshold to their particular logic level requirements. In a default configuration, VREF IN gets connected to VREF OUT for TTL threshold level requirements.

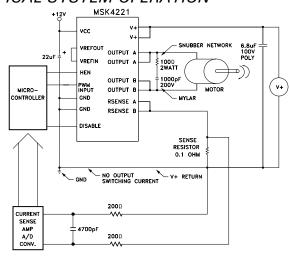

## TYPICAL SYSTEM OPERATION

This is a diagram of a typical application of the MSK 4221. The design Vcc voltage is +12 volts and should have a good low ESR bypass capacitor such as a tantalum electrolytic. The input will be a pulse width modulated digital signal from a microcontroller, DSP or other microprocessor. A 50% duty cycle input will cause zero average current through the load. A smaller duty cycle input will cause increasing average current in one direction, a larger duty cycle input will cause increasing average current in the other direction. The gain of the current control amplifier will have to be set to obtain the proper amount of current limiting required by the system.

Current sensing is done in this case by a 0.1 ohm sense resistor to sense current from the common source of the bridge together. It is important to make the high current traces as big as possible to keep inductance down. The storage capacitor connected to the V+ and the module should be large enough to provide the high energy pulse without the voltage sagging too far. A low ESR ceramic capacitor or large polypropylene capacitor will be required. Mount the capacitor as close to the module as possible. The connection between GND and the V+ return should not be carrying any motor current. The sense resistor signal is common mode filtered as necessary to feed the limiting circuitry for the microprocessor. This application will allow full four quadrant torque control for a closed loop servo system.

A snubber network is usually required, due to the inductance in the power loop. It is important to design the snubber network to suppress any positive spikes above 75V and negative spikes below -2V with respect to ground.

3

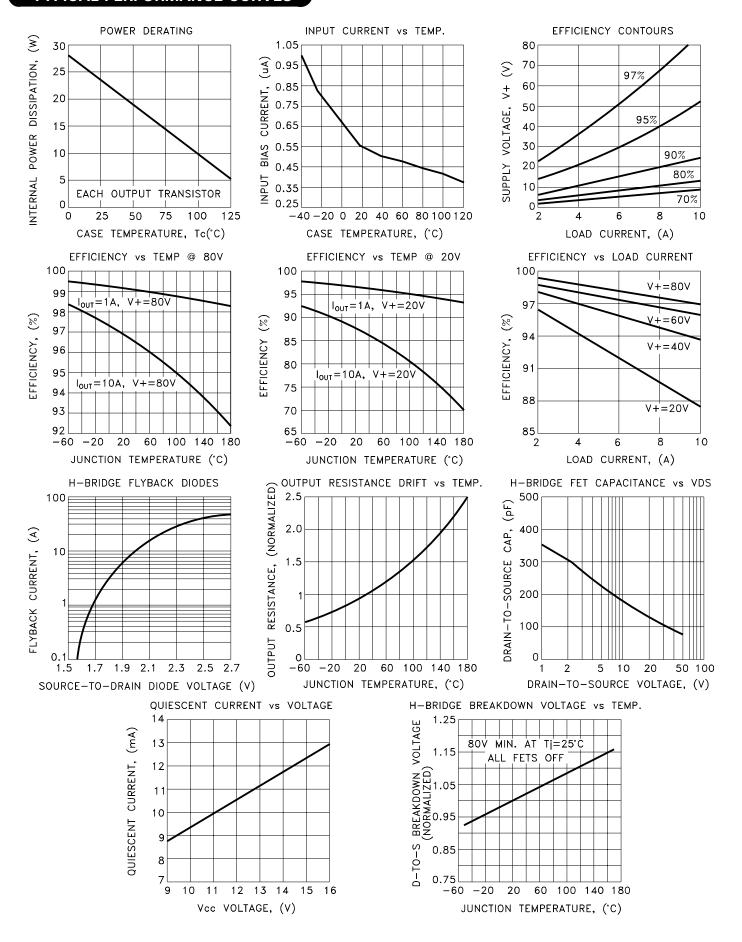

# **TYPICAL PERFORMANCE CURVES**

4

Rev. C 6/00

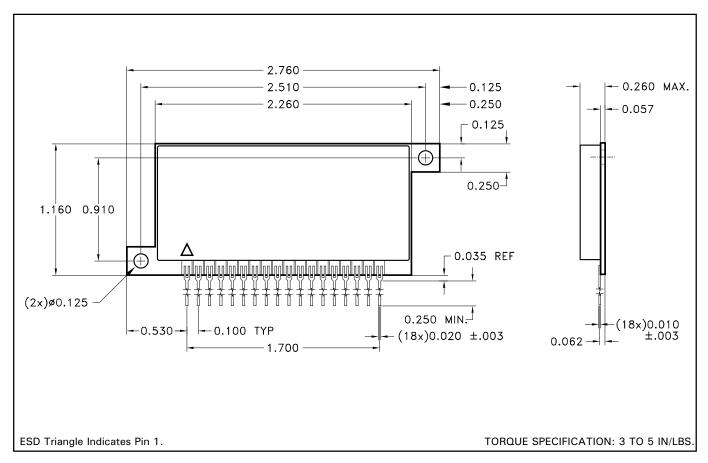

NOTE: ALL DIMENSIONS ARE  $\pm 0.010$  UNLESS OTHERWISE LABELED.

# ORDERING INFORMATION

| Part<br>Number | Screening Level |

|----------------|-----------------|

| MSK4221        | Industrial      |

M.S. Kennedy Corp.

4707 Dey Road, Liverpool, New York 13088

Phone (315) 701-6751

FAX (315) 701-6752

www.mskennedy.com

The information contained herein is believed to be accurate at the time of printing. MSK reserves the right to make changes to its products or specifications without notice, however, and assumes no liability for the use of its products.

5 Rev. C 6/00