# MX·CDM, INC. MiXed Signal ICs

**DATA BULLETIN**

# **MX102**

# **Autocorrelating Signal Processor**

#### **Features**

- Low Signal Level Input of 10mVrms

- Wide Signal Frequency Range from 17Hz to 13kHz

- **On-Chip Gain Amplifier**

- Digital Output Signal (f<sub>IN</sub> x 4)

- **Divided-Down Clock Output**

- Low Supply Voltage Operation of 2.5 V

- **Low Current Drain**

## **Applications**

- Medical Instruments

- **Sonar Detection**

- Remote Signaling

- **Pagers**

- **Mobile Radio**

- **Slow Data Rate Communication**

- **Tone Detection**

The MX102 is a single-chip device to extract single periodic signals from very high random-noise environments.

Using patented autocorrelation techniques the MX102 will enhance the input signal's signal-to-noise ratio by as much as 8.5dB and provide a digital output signal centered at four times (x4) the input frequency.

The amplitude of non-periodic components of the signal is substantially reduced. The patented autocorrelator compares the incoming signal to itself; the more elements of the waveform that are seen as periodic, the higher the energy at the microcircuit output.

The MX102 cascades two autocorrelators, each one improving the signal-to-noise ratio

With a random noise input the output will swing rail-to-rail at random (peak-limited). The input/output signal delay is fixed by the choice of clock frequency and the length of the internal register. The MX102 will operate at supply voltages of between 2.5 volts and 5.5 volts and with Xtal/clock frequencies from 20kHz to 2.5MHz. Using various Xtal/clock inputs the device can be set to accept input signal frequencies, in bands, from 17.0Hz to 13.0kHz.

Two uncommitted clock outputs are available: one to supply a 'divided-down' Xtal/clock frequencies and the second is a buffered output for use in external and peripheral functions.

This MX102 is available in the following package styles: 16-pin SOIC (MX102DW) and 16-pin CDIP (MX102J).

# **CONTENTS**

| Section                      | Page |

|------------------------------|------|

| 1. Block Diagram             | 3    |

| 2. Signal List               | 4    |

| 3. External Components       | 5    |

| 4. General Description       | 6    |

| 4.1 Signal                   | 6    |

| 4.2 Input Frequency Range    | 6    |

| 5. Performance Specification | 8    |

| 5.1 Electrical Performance   | 8    |

| 5.2 Packaging                | 10   |

MX•COM, Inc. reserves the right to change specifications at any time and without notice.

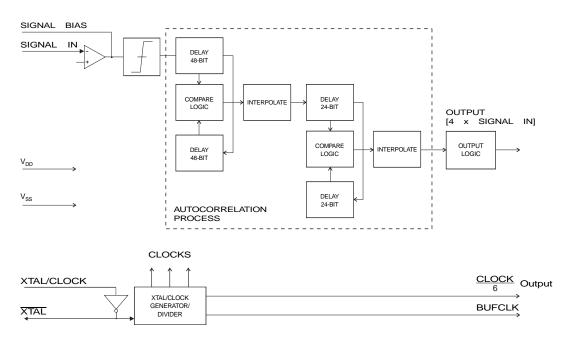

# 1. Block Diagram

Figure 1: Device Block Diagram

# 2. Signal List

| DW/J   Name   Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Packages             | Signal     |        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Signal Bias pin; external coupling components are required. See Figure 2  3 Signal Bias pin; external coupling components are required. See Figure 2  4 V <sub>DD</sub> power Positive supply rail. A single, stable power supply is required. Note that this device has two V <sub>DD</sub> pins; this input is positioned to prevent cross-talk, either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either V <sub>DD</sub> pin.  5 BUFCLK output Buffered inverter oscillator digital output. May be used as test point to allign clock frequency or to drive other circuitry.  6 XTAL output The output of the on-chip clock oscillator inverter.  8 Xtal/Clock input The input to the on-chip clock oscillator inverter; this may be a Xtal, resonator or clock pulse input. The selection of this frequency will affect the operational input signal bandwidth (and output frequency) of this device; refer to Table 4. Note that the choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and hence the maximum useable signal input frequency. Operation of this microcircuit without an active Xtal or clock input may cause device damage. A clock pulse input is fed directly into this pin; Xtal/Clock components are not required. See Table 2.  9 V <sub>SS</sub> power Negative Supply  11 CLK ÷ 6 output Output Output (FUT)  OUTPUT Ou | DW/J                 | Name       | Туре   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Peripheral circuitry; there is no drive capacity for off-chip signaling. The feedback resistor should be not less than 200kΩ. See Figure 2.  4 VDD power Positive supply rail. A single, stable power supply is required. Note that this device has two VDD pins; this input is positioned to prevent cross-talk, either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either VDD pin.  5 BUFCLK output Buffered inverter oscillator digital output. May be used as test point to align clock frequency or to drive other circuitry.  6 XTAL output The output of the on-chip clock oscillator inverter.  8 Xtal/Clock input The input to the on-chip clock oscillator inverter; this may be a Xtal, resonator or clock pulse input. The selection of this frequency will affect the operational input signal bandwidth (and output frequency) of this device; refer to Table 4. Note that the choice of VDD will determine the maximum Xtal/clock frequency and hence the maximum useable signal input frequency. Operation of this microcircitic without an active Xtal or clock input may cause device damage. A clock pulse input is fed directly into this pin; Xtal/clock components are not required. See Table 2.  9 Vss power Negative Supply  11 CLK ÷ 6 output A squarewave output clock signal at the rate of Clock/6; provided for peripheral and test purposes.  13 OUTPUT output ((OUT = 4 x fSIGNAL IN). The auto-correlated output signal at four times (x 4) the input signal (see Figure 3). There is a time delay between input and output signals (see Specifications).  16 VDD Power Positive supply rail. A single, stable power supply is required. Note that this device has two VDD pins; either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either VDD pin.  The choice of VDD will determine the maximum Xtal/clock frequency and                                                                                                                                                                                                              | 1                    | Signal In  | input  | Signal Bias pin; external coupling components are required.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| this device has two V <sub>DD</sub> pins; this input is positioned to prevent cross-talk, either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either V <sub>DD</sub> pin.  BUFCLK  output  Buffered inverter oscillator digital output. May be used as test point to align clock frequency or to drive other circuitry.  The output of the on-chip clock oscillator inverter.  Xtal/Clock  input  The input to the on-chip clock oscillator inverter; this may be a Xtal, resonator or clock pulse input. The selection of this frequency will affect the operational input signal bandwidth (and output frequency) of this device; refer to Table 4. Note that the choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and hence the maximum useable signal input frequency. Operation of this microcircuit without an active Xtal or clock input may cause device damage. A clock pulse input is fed directly into this pin; Xtal/clock components are not required.  See Table 2.  Power  Negative Supply  CLK ÷ 6 output  A squarewave output clock signal at the rate of Clock/6; provided for peripheral and test purposes.  OUTPUT  Output  (fOUT = 4 x fSIGNAL IN). The auto-correlated output signal at four times (x 4) the input signal (see Figure 3).  There is a time delay between input and output signals (see Specifications).  Power  Positive supply rail. A single, stable power supply is required.  Note that this device has two V <sub>DD</sub> pins; either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either V <sub>DD</sub> pin.  The choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and                                                                                                                                                                                                                                                                                                                                                                                                    | 3                    | _          | output | peripheral circuitry; there is no drive capacity for off-chip signaling. The                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| align clock frequency or to drive other circuitry.  6 XTAL output The output of the on-chip clock oscillator inverter.  8 Xtal/Clock input input to the on-chip clock oscillator inverter; this may be a Xtal, resonator or clock pulse input. The selection of this frequency will affect the operational input signal bandwidth (and output frequency) of this device; refer to Table 4. Note that the choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and hence the maximum useable signal input frequency. Operation of this microcircuit without an active Xtal or clock input may cause device damage. A clock pulse input is fed directly into this pin; Xtal/clock components are not required. See Table 2.  9 V <sub>SS</sub> power Negative Supply  11 CLK ÷ 6 output A squarewave output clock signal at the rate of Clock/6; provided for peripheral and test purposes.  13 OUTPUT output (fOUT = 4 x fSIGNAL IN). The auto-correlated output signal at four times (x 4) the input signal (see Figure 3).  There is a time delay between input and output signals (see Specifications).  16 V <sub>DD</sub> power Positive supply rail. A single, stable power supply is required.  Note that this device has two V <sub>DD</sub> pins; either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either V <sub>DD</sub> pin.  The choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                    | $V_{DD}$   | power  | this device has two V <sub>DD</sub> pins; this input is positioned to prevent cross-talk, either or both may be connected to the host circuit's supply line. Do not                                                                                                                                                                                                                                                                                                                                                |  |  |

| 8 Xtal/Clock input input to the on-chip clock oscillator inverter; this may be a Xtal, resonator or clock pulse input. The selection of this frequency will affect the operational input signal bandwidth (and output frequency) of this device; refer to Table 4. Note that the choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and hence the maximum useable signal input frequency. Operation of this microcircuit without an active Xtal or clock input may cause device damage. A clock pulse input is fed directly into this pin; Xtal/clock components are not required.  9 V <sub>SS</sub> power Negative Supply  11 CLK ÷ 6 output A squarewave output clock signal at the rate of Clock/6; provided for peripheral and test purposes.  13 OUTPUT output (fOUT = 4 x fSIGNAL IN). The auto-correlated output signal at four times (x 4) the input signal (see Figure 3).  There is a time delay between input and output signals (see Specifications).  Power Positive supply rail. A single, stable power supply is required.  Note that this device has two V <sub>DD</sub> pins; either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either V <sub>DD</sub> pin.  The choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5                    | BUFCLK     | output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| resonator or clock pulse input. The selection of this frequency will affect the operational input signal bandwidth (and output frequency) of this device; refer to Table 4. Note that the choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and hence the maximum useable signal input frequency. Operation of this microcircuit without an active Xtal or clock input may cause device damage. A clock pulse input is fed directly into this pin; Xtal/clock components are not required.  See Table 2.  9 V <sub>SS</sub> power Negative Supply  11 CLK ÷ 6 output A squarewave output clock signal at the rate of Clock/6; provided for peripheral and test purposes.  13 OUTPUT output (fOUT = 4 x fSIGNAL IN). The auto-correlated output signal at four times (x 4) the input signal (see Figure 3).  There is a time delay between input and output signals (see Specifications).  Positive supply rail. A single, stable power supply is required.  Note that this device has two V <sub>DD</sub> pins; either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either V <sub>DD</sub> pin.  The choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                    | XTAL       | output | The output of the on-chip clock oscillator inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 11 CLK ÷ 6 output A squarewave output clock signal at the rate of Clock/6; provided for peripheral and test purposes.  13 OUTPUT output (fOUT = 4 x fSIGNAL IN). The auto-correlated output signal at four times (x 4) the input signal (see Figure 3).  There is a time delay between input and output signals (see Specifications).  Power Positive supply rail. A single, stable power supply is required.  Note that this device has two V <sub>DD</sub> pins; either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either V <sub>DD</sub> pin.  The choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                    | Xtal/Clock | input  | resonator or clock pulse input. The selection of this frequency will affect the operational input signal bandwidth (and output frequency) of this device; refer to Table 4. Note that the choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and hence the maximum useable signal input frequency. Operation of this microcircuit without an active Xtal or clock input may cause device damage. A clock pulse input is fed directly into this pin; Xtal/clock components are not required. |  |  |

| DUTPUT  Output  (fOUT = 4 x fSIGNAL IN). The auto-correlated output signal at four times (x 4) the input signal (see Figure 3).  There is a time delay between input and output signals (see Specifications).  VDD  Power  Positive supply rail. A single, stable power supply is required.  Note that this device has two VDD pins; either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either VDD pin.  The choice of VDD will determine the maximum Xtal/clock frequency and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9                    | $V_{SS}$   | power  | Negative Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| (x 4) the input signal (see Figure 3).  There is a time delay between input and output signals (see Specifications).  VDD  Power  Positive supply rail. A single, stable power supply is required.  Note that this device has two VDD pins; either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either VDD pin.  The choice of VDD will determine the maximum Xtal/clock frequency and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11                   | CLK ÷ 6    | output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Note that this device has two V <sub>DD</sub> pins; either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either V <sub>DD</sub> pin.  The choice of V <sub>DD</sub> will determine the maximum Xtal/clock frequency and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13                   | OUTPUT     | output | (x 4) the input signal (see Figure 3). There is a time delay between input and output signals (see                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| to the host circuit's supply line. Do not attempt to draw current from either $V_{DD}$ pin. The choice of $V_{DD}$ will determine the maximum Xtal/clock frequency and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16                   | $V_{DD}$   | power  | Positive supply rail. A single, stable power supply is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |            |        | Note that this device has two $V_{DD}$ pins; either or both may be connected to the host circuit's supply line. Do not attempt to draw current from either $V_{DD}$ pin.  The choice of $V_{DD}$ will determine the maximum Xtal/clock frequency and                                                                                                                                                                                                                                                               |  |  |

| 2, 7, 10, 12, 14, 15 N/C No internal connection. Leave open circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2, 7, 10, 12, 14, 15 |            | N/C    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

Table 1: Signal List

| V <sub>DD</sub> (V) | Max. Xtal/Clock Freq. (MHz) |

|---------------------|-----------------------------|

| 2.5                 | 0.625                       |

| 3.0                 | 1.0                         |

| 5.0                 | 2.5                         |

Table 2: Maximum Usable Xtal/Clock Frequencies

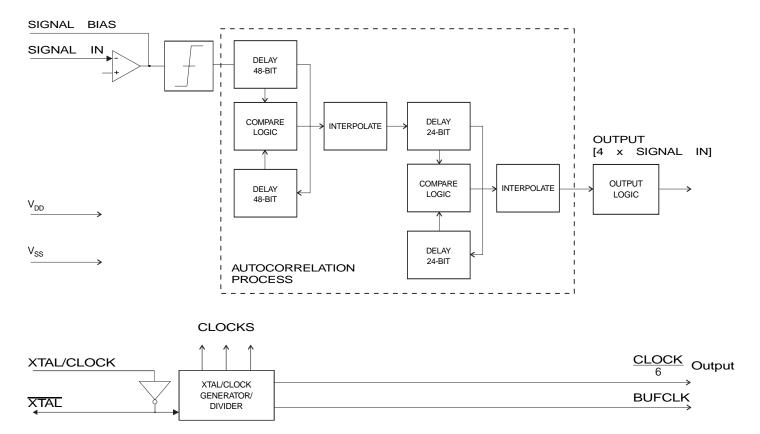

# 3. External Components

Figure 2: Recommended External Components

| R1       |        | 2.2ΜΩ                  |

|----------|--------|------------------------|

| R2       |        | $1.0 \mathrm{M}\Omega$ |

| C1       |        | 0.01µF                 |

| C2       | Note 1 | 47.0pF -see below      |

| C3       | Note 1 | 47.0pF -see below      |

| C4       | Note 2 | 5 - 65pF -see below    |

| C5       |        | 1.0µF                  |

| X1       |        | 560kHz resonator       |

| X1 range |        | 20kHz to 2.5MHz        |

**Table 3: Recommended External Components**

#### **Recommended External Component Notes:**

- 1. Values of capacitors C2 and C3 should be reduced for higher Xtal frequencies and/or lower supply voltages (V<sub>DD</sub>).

- C4 is suggested for frequency setting when using a resonator; when a Xtal is used C4 is omitted.

# 4. General Description

### 4.1 Signal

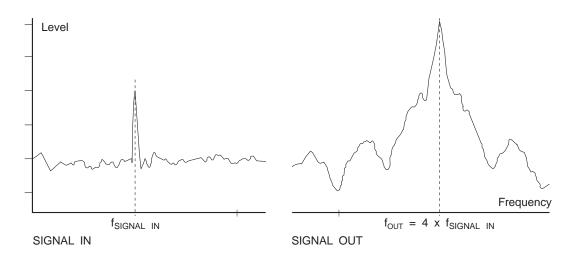

Figure 3: MX102 Input/Output Relationships

#### Note:

1. The frequency of the output signal is four times (x4) that of the input signal.

### 4.2 Input Frequency Range

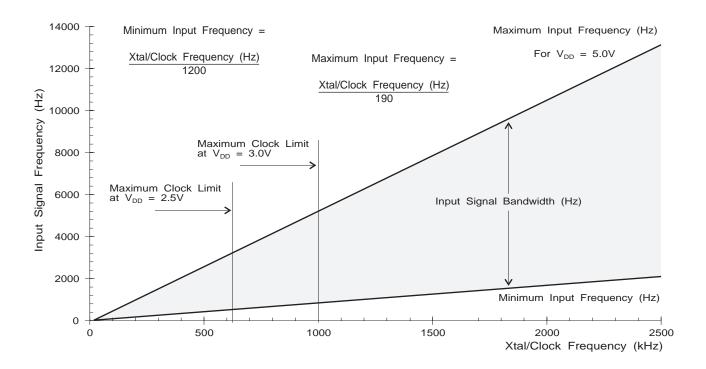

The MX102 has a wide frequency range, but care must be taken to choose the Xtal frequency appropriate for your application.

| Xtal/Clock Frequency<br>(kHz) | Input Fi | BW (Hz) |       |

|-------------------------------|----------|---------|-------|

|                               | Min.     | Max.    |       |

| 20                            | 17       | 105     | 88    |

| 100                           | 88       | 526     | 443   |

| 200                           | 166      | 1052    | 886   |

| 300                           | 250      | 1579    | 1329  |

| 400                           | 333      | 2105    | 1772  |

| 500                           | 416      | 2632    | 2216  |

| 560                           | 467      | 2947    | 2480  |

| 600                           | 500      | 3158    | 2658  |

| 700                           | 583      | 3684    | 3101  |

| 800                           | 667      | 4210    | 3543  |

| 900                           | 750      | 4737    | 3987  |

| 1000                          | 833      | 5263    | 4430  |

| 2000                          | 1667     | 10526   | 8859  |

| 2500                          | 2083     | 13157   | 11074 |

Table 4: Input Signal Ranges vs Xtal/Clock Frequency

Figure 4: Input Signal Ranges vs Xtal/Clock Frequency

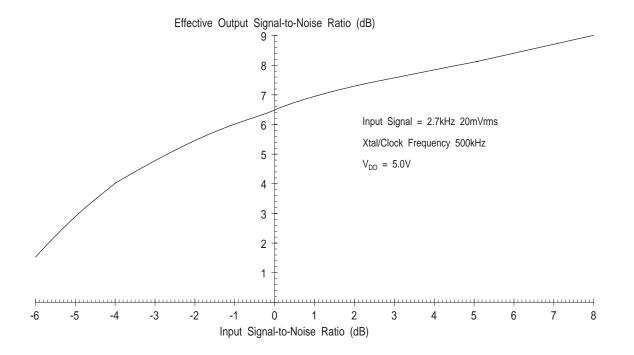

Figure 5: Enhancement of Signal-To-Noise Ratio

#### Note:

1. The graph shown in Figure 5 illustrates the signal-to-noise enhancement that can be obtained, under varying input conditions, from the MX102.

# 5. Performance Specification

#### **5.1 Electrical Performance**

#### **Absolute Maximum Ratings**

Exceeding these maximum ratings can result in damage to the device.

| General                    | Min. | Max.                         | Units |

|----------------------------|------|------------------------------|-------|

| Supply Voltage             | -0.3 | 7.0 volts                    | V     |

| Input Voltage at any pin   | -0.3 | (V <sub>DD</sub> +0.3 volts) | V     |

| Current                    |      |                              |       |

| $V_{DD}$                   | -30  | 30                           | mA    |

| V <sub>SS</sub>            | -30  | 30                           | mA    |

| Any other pins             | -20  | 20                           | mA    |

| Maximum Device Dissipation | 100  |                              | mW    |

| Operating Temperature      | -40° | 85                           | °C    |

| Storage Temperature        | -40° | 125                          | °C    |

#### **Operating Limits**

Correct operation of the device outside these limits is not implied.

|                       | Min. | Тур.    | Max. | Units |

|-----------------------|------|---------|------|-------|

| $V_{DD}$              | 2.5  | 3.3/5.0 | 5.5  | V     |

| Xtal/Clock            | 20   |         | 2500 | kHz   |

| Operating Temperature | -40  |         | 85   | °C    |

#### **Operating Characteristics**

For the following conditions unless otherwise specified:

$V_{DD} = 5.0V$ ,  $T_{AMB} = 25$ °C

Xtal/Clock = 560kHz, Input Test Signal = 200mV<sub>RMS</sub>

|                                           | Notes | Min.   | Тур. | Max   | Units             |

|-------------------------------------------|-------|--------|------|-------|-------------------|

| Static Values                             |       |        |      |       |                   |

| Supply Current                            |       | -      | 1.0  | 2.5   | mA                |

|                                           | 2     | -      | 4.0  | -     | mA                |

| Logic '1' Level                           |       | 80%    | -    | -     | V                 |

| Logic '0' Level                           |       | -      | -    | 20%   | V                 |

| Digital Output Impedance                  |       | -      | 4.0  | 10.0  | kΩ                |

| Dynamic Values                            |       |        |      |       |                   |

| Signal Input                              | 3     | 20.0   | -    | 1000  | mV <sub>RMS</sub> |

| Analog (Input) Amplifier Gain             | 4     | 20.0   | -    | -     | dB                |

|                                           | 5     | 9.0    | -    | -     | dB                |

|                                           | 6     | 10.0   | -    | -     | dB                |

| Recommended Input Signal Duty Cycle Ratio |       | 35     | 50   | -     | %                 |

| Frequency Out/Frequency In Ratio          |       | 4.0    | -    | 4.0   | %                 |

| Maximum Xtal/Clock Frequency              | 1     | 2.5    | -    | -     | MHz               |

| Minimum Xtal/Clock Frequency              |       |        |      | 20.0  | kHz               |

| Frequency Input Range                     |       |        |      |       |                   |

| Xtal/Clock = 560kHz                       | 7     | 500    | -    | 3000  | Hz                |

| Table 4                                   |       | 1/1200 |      | 1/190 | Xtal/Clock        |

| Input to Output Delay                     | 8     | -      | 1.4  |       | ms                |

| Output resolution                         |       | -      | 1/6  | -     | Xtal/Clock        |

#### **Operating Characteristics Notes:**

- 1. Maximum Xtal/clock frquency allowed varies with applied supply voltage (V<sub>DD</sub>).

- 2. I<sub>DD</sub> requirement for Xtal/clock frequency of 2.24MHz.

- 3. Signal input level required to provide a constant autocorrelated output.

- 4. Measured with a 6.0kHz sinewave at the signal input.

- 5. Measured with  $V_{DD} = 2.5$  volts.

- 6. Measured with a 12kHz input signal.

- 7. Recommended input signal frequency range to correlation circuits.

- 8. Input (Signal In) to output (Output) time with a 2.24MHz Xtal/clock input.

© 1997 MX•COM,INC.

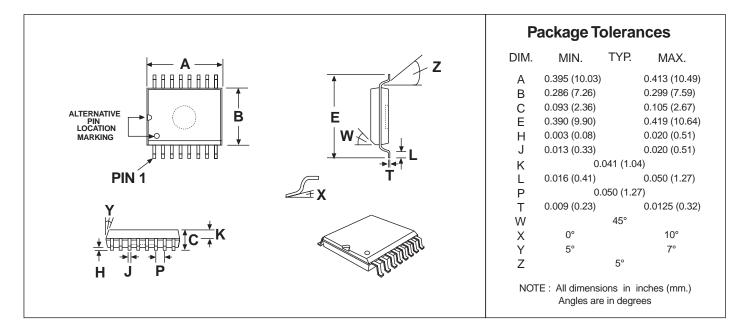

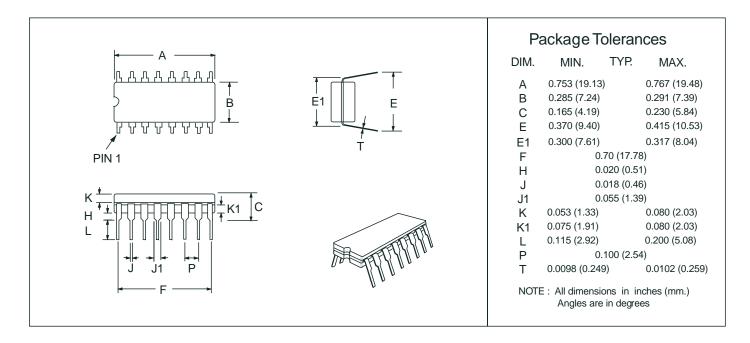

#### 5.2 Packaging

Figure 6: 16-pin SOIC Mechanical Outline: Order as part no. MX102DW

Figure 7: 16-pin CDIP Mechanical Outline: Order as part no. MX102J