# mos integrated circuit $\mu$ **PD77016**

# 16 bits, Fixed-point Digital Signal Processor

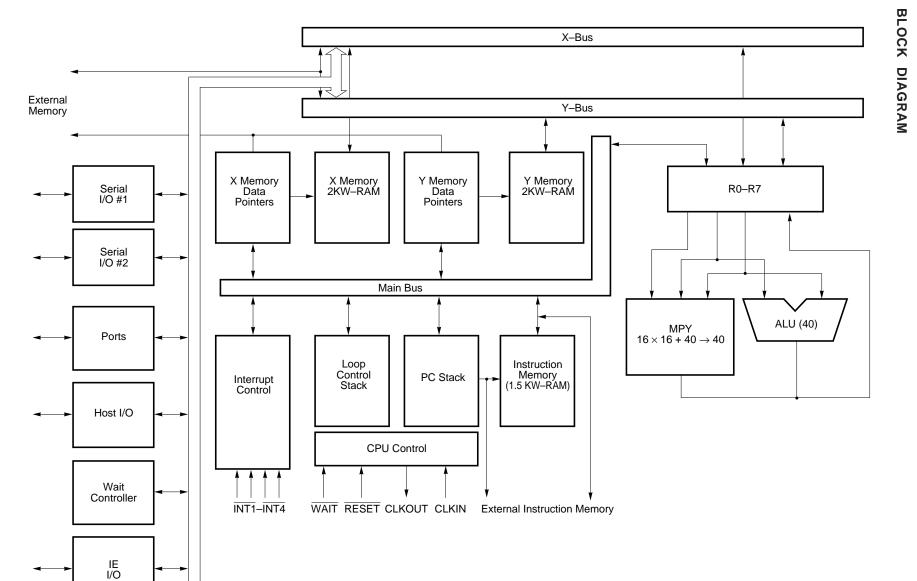

$\mu$ PD77016 is a 16 bits fixed-point DSP (Digital Signal Processor) developed for digital signal processing with its demand for high speed and precision.

#### FEATURES

NEC

- FUNCTIONS

- Instruction cycle: 30 ns (MIN.) with 33 MHz clock

- Dual load/store

- Hardware loop function

- Conditional execution

- Executes product-sum operation in one instruction cycle

- PROGRAMMING

- + 16 bits  $\times$  16 bits + 40 bits  $\rightarrow$  40 bits multiply accumulator

- 8 general registers (40 bits each)

- 8 ROM/RAM data pointer: each data memory area has 4 registers

- 10 source interrupts (external: 4, internal: 6)

- 3 operand instructions (example: R0 = R0 +R1L\*R2L)

- Nonpipeline on execution stage

- MEMORY AREAS

- Program memory area: 64K words  $\times$  32 bits

- Two independent data memory areas: 64K words × 16 bits (X/Y memory)

- ON-CHIP PERIPHERAL

- I/O port: 4 bits

- Serial I/O (16 bits): 2 channels

- CMOS

- +5 V single power supply

#### ORDERING INFORMATION

Part Number

Package

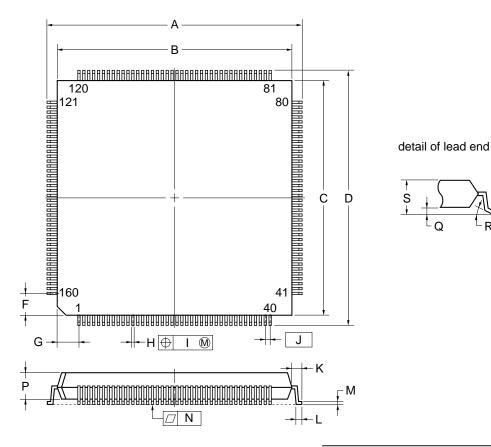

$\mu \text{PD77016GM-KMD}$  160-pin plastic QFP (FINE PITCH) (24  $\times$  24 mm)

The information in this document is subject to change without notice.

N Z

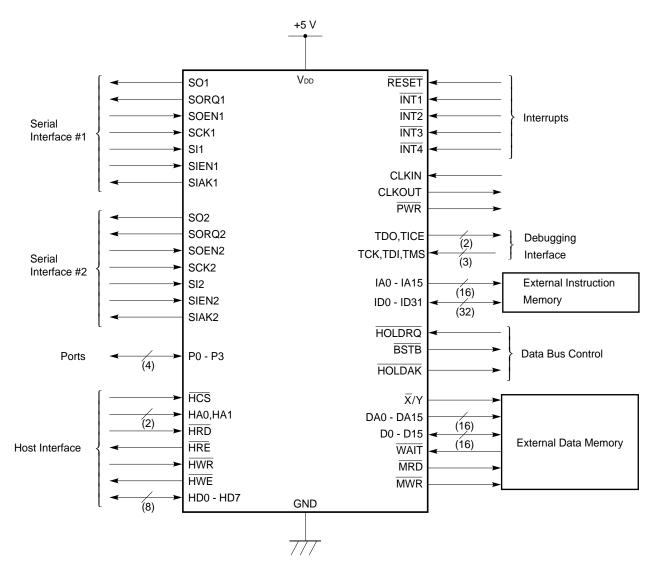

#### FUNCTIONAL PIN GROUPS

# **\star** Functional Differences among the $\mu$ PD7701× Family

| Item                                           | μPD77016                                       | μPD77015                                                                                                                                        | μPD77017                                                                       | μPD77018    | μPD77018A                                   | μPD77019                                                                          | μPD77019-013 |

|------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------|---------------------------------------------|-----------------------------------------------------------------------------------|--------------|

| Internal instruction RAM                       | 1.5K words                                     |                                                                                                                                                 | 256 words                                                                      |             |                                             | 4K word                                                                           |              |

| Internal instruction ROM                       | None                                           | 4K words                                                                                                                                        | 4K words 12K words                                                             |             |                                             | 24K words                                                                         |              |

| External instruction memory                    | 48K words                                      |                                                                                                                                                 |                                                                                | N           | one                                         |                                                                                   |              |

| Data RAM (X/Y memory)                          | 2K words each                                  | 1K words each                                                                                                                                   | 2K words each                                                                  |             | 3K wor                                      | ds each                                                                           |              |

| Data ROM (X/Y memory)                          | None                                           | 2K words each                                                                                                                                   | 4K words each                                                                  |             | 12K words each                              |                                                                                   | None         |

| External data memory                           | 48K words each                                 |                                                                                                                                                 |                                                                                | 16K woi     | rds each                                    |                                                                                   |              |

| Instruction cycle<br>(Maximum operation speed) |                                                | 30 ns (33 MHz)                                                                                                                                  |                                                                                |             |                                             |                                                                                   |              |

| External clock<br>(at maximum operation speed) | 66 MHz                                         |                                                                                                                                                 | 33/16.5/8.25/4.125 MHz<br>Variable multiple rate (1, 2, 4, 8 ) by mask option. |             |                                             | 60/30/20/15/7.5 MHz<br>Variable multiple rate (1, 2, 3, 4, 8 ) by<br>mask option. |              |

| Crystal<br>(at maximum operation speed)        | -                                              |                                                                                                                                                 | 33 MHz                                                                         |             | 60                                          | MHz                                                                               | _            |

| Instruction                                    | -                                              |                                                                                                                                                 |                                                                                | STOP instru | ction is added.                             |                                                                                   |              |

| Serial interface (2 Channels)                  | Channel 1 has the same functions as channel 2. | Channel 1 has the same functions as that of the $\mu$ PD77016.<br>Channel 2 has no SORQ2 or SIAK2 pin (Channel 2 is used for CODEC connection). |                                                                                |             |                                             |                                                                                   |              |

| Power supply                                   | 5V                                             | 3 V                                                                                                                                             |                                                                                |             |                                             |                                                                                   |              |

| Package                                        | 160-pin plastic QFP                            | 100-pin plastic TQFP                                                                                                                            |                                                                                |             | 100-pin plastic TQFP<br>116-pin plastic BGA | 100-pin pl                                                                        | astic TQFP   |

**Remark** The µPD77019-013 internal ROM area is masked already by the void code to use as RAM based DSP without mask code ordering process.

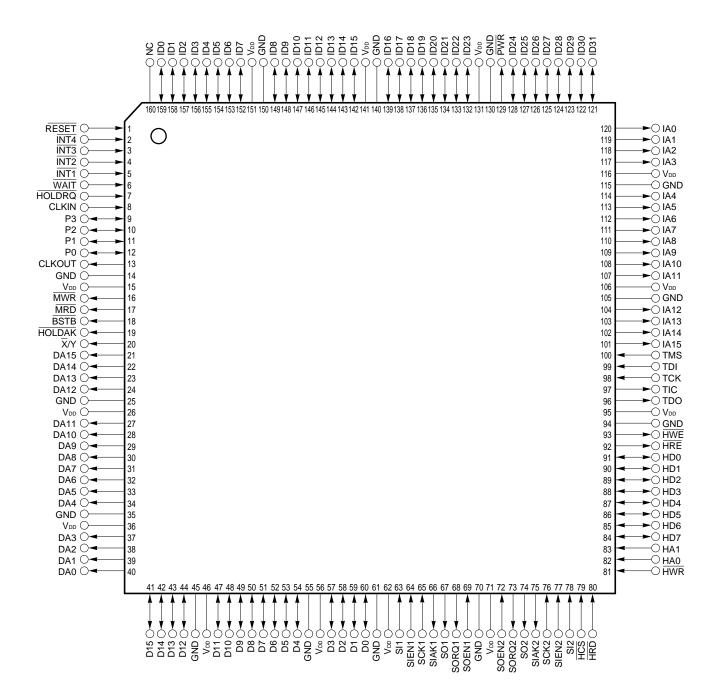

#### PIN CONFIGURATION

$\mu$ PD77016GM-KMD

160-pin plastic QFP (FINE PITCH) (24  $\times$  24 mm) (Top View)

# PIN IDENTIFICATION

| BSTB:        | Bus Strobe                        |

|--------------|-----------------------------------|

| CLKIN:       | Clock Input                       |

| CLKOUT:      | Clock Output                      |

| D0-D15:      | 16 Bits Data Bus                  |

| DA0-DA15:    | External Data Memory Address Bus  |

| GND:         | Ground                            |

| HA0,HA1:     | Host Data Access                  |

| HCS:         | Host Chip Select                  |

| HD0-HD7:     | Host Data Bus                     |

| HOLDAK:      | Hold Acknowledge                  |

| HOLDRQ:      | Hold Request                      |

| HRD:         | Host Read                         |

| HRE:         | Host Read Enable                  |

| HWE:         | Host Write Enable                 |

| HWR:         | Host Write                        |

| IA0-IA15:    | Instruction Memory Address Output |

| ID0-ID31:    | Instruction Data Input            |

| INT1-INT4:   | Interrupt                         |

| MRD:         | Memory Read Output                |

| MWR:         | Memory Write Output               |

| N.C:         | No Connection                     |

| P0-P3:       | Port                              |

| PWR:         | Program Memory Write Strobe       |

| RESET:       | Reset                             |

| SCK1,SCK2:   | Serial Clock Input                |

| SI1,SI2:     | Serial Data Input                 |

| SIAK1,SIAK2: | Serial Input Acknowledge          |

| SIEN1,SIEN2: | Serial Input Enable               |

| SO1,SO2:     | Serial Data Output                |

| SOEN1,SOEN2: | Serial Output Enable              |

| SORQ1,SORQ2  | Serial Output Request             |

| TCK:         | Test Clock Input                  |

| TDI:         | Test Data Input                   |

| TDO:         | Test Data Output                  |

| TICE:        | Test In-Circuit Emulator          |

| TMS:         | Test Mode Select                  |

| Vdd:         | Power Supply                      |

| WAIT:        | Wait Input                        |

| X/Y:         | X/Y Memory Select                 |

|              |                                   |

| Pin No. | Symbol |

|---------|--------|---------|--------|---------|--------|---------|--------|

| 1       | RESET  | 41      | D15    | 81      | HWR    | 121     | ID31   |

| 2       | INT4   | 42      | D14    | 82      | HA0    | 122     | ID30   |

| 3       | INT3   | 43      | D13    | 83      | HA1    | 123     | ID29   |

| 4       | INT2   | 44      | D12    | 84      | HD7    | 124     | ID28   |

| 5       | INT1   | 45      | GND    | 85      | HD6    | 125     | ID27   |

| 6       | WAIT   | 46      | Vdd    | 86      | HD5    | 126     | ID26   |

| 7       | HOLDRQ | 47      | D11    | 87      | HD4    | 127     | ID25   |

| 8       | CLKIN  | 48      | D10    | 88      | HD3    | 128     | ID24   |

| 9       | P3     | 49      | D9     | 89      | HD2    | 129     | PWR    |

| 10      | P2     | 50      | D8     | 90      | HD1    | 130     | GND    |

| 11      | P1     | 51      | D7     | 91      | HD0    | 131     | Vdd    |

| 12      | P0     | 52      | D6     | 92      | HRE    | 132     | ID23   |

| 13      | CLKOUT | 53      | D5     | 93      | HWE    | 133     | ID22   |

| 14      | GND    | 54      | D4     | 94      | GND    | 134     | ID21   |

| 15      | Vdd    | 55      | GND    | 95      | Vdd    | 135     | ID20   |

| 16      | MWR    | 56      | Vdd    | 96      | TDO    | 136     | ID19   |

| 17      | MRD    | 57      | D3     | 97      | TICE   | 137     | ID18   |

| 18      | BSTB   | 58      | D2     | 98      | ТСК    | 138     | ID17   |

| 19      | HOLDAK | 59      | D1     | 99      | TDI    | 139     | ID16   |

| 20      | X/Y    | 60      | D0     | 100     | TMS    | 140     | GND    |

| 21      | DA15   | 61      | GND    | 101     | IA15   | 141     | Vdd    |

| 22      | DA14   | 62      | Vdd    | 102     | IA14   | 142     | ID15   |

| 23      | DA13   | 63      | SI1    | 103     | IA13   | 143     | ID14   |

| 24      | DA12   | 64      | SIEN1  | 104     | IA12   | 144     | ID13   |

| 25      | GND    | 65      | SCK1   | 105     | GND    | 145     | ID12   |

| 26      | Vdd    | 66      | SIAK1  | 106     | Vdd    | 146     | ID11   |

| 27      | DA11   | 67      | SO1    | 107     | IA11   | 147     | ID10   |

| 28      | DA10   | 68      | SORQ1  | 108     | IA10   | 148     | ID9    |

| 29      | DA9    | 69      | SOEN1  | 109     | IA9    | 149     | ID8    |

| 30      | DA8    | 70      | GND    | 110     | IA8    | 150     | GND    |

| 31      | DA7    | 71      | Vdd    | 111     | IA7    | 151     | Vdd    |

| 32      | DA6    | 72      | SOEN2  | 112     | IA6    | 152     | ID7    |

| 33      | DA5    | 73      | SORQ2  | 113     | IA5    | 153     | ID6    |

| 34      | DA4    | 74      | SO2    | 114     | IA4    | 154     | ID5    |

| 35      | GND    | 75      | SIAK2  | 115     | GND    | 155     | ID4    |

| 36      | Vdd    | 76      | SCK2   | 116     | Vdd    | 156     | ID3    |

| 37      | DA3    | 77      | SIEN2  | 117     | IA3    | 157     | ID2    |

| 38      | DA2    | 78      | SI2    | 118     | IA2    | 158     | ID1    |

| 39      | DA1    | 79      | HCS    | 119     | IA1    | 159     | ID0    |

| 40      | DA0    | 80      | HRD    | 120     | IA0    | 160     | NC     |

NEC

# CONTENTS

| 1. | PIN                              | PIN FUNCTIONS |                                    |    |  |  |  |

|----|----------------------------------|---------------|------------------------------------|----|--|--|--|

|    | 1.1                              | Pin Fu        | unctions                           | 9  |  |  |  |

|    | 1.2                              | Recor         | nmended Connection for Unused Pins | 14 |  |  |  |

| 2. | FUN                              |               | IS                                 | 15 |  |  |  |

|    | 2.1                              | Pipeli        | ne Processing                      | 15 |  |  |  |

|    |                                  | 2.1.1         | Outline                            | 15 |  |  |  |

|    |                                  | 2.1.2         | Instructions with Delay            | 15 |  |  |  |

|    | 2.2                              | Progr         | am Control Unit                    | 16 |  |  |  |

|    | 2.3                              | Opera         | tion Unit                          | 16 |  |  |  |

|    |                                  | 2.3.1         | General register (R0 to R7)        | 16 |  |  |  |

|    |                                  | 2.3.2         | MAC: Multiply ACcumulator          | 17 |  |  |  |

|    |                                  | 2.3.3         | ALU: Arithmetic Logic Unit         | 17 |  |  |  |

|    |                                  | 2.3.4         | BSFT: Barrel ShiFTer               | 17 |  |  |  |

|    |                                  | 2.3.5         | SAC: Shifter And Count Circuit     | 17 |  |  |  |

|    |                                  | 2.3.6         | CJC: Condition Judge Circuit       | 17 |  |  |  |

|    | 2.4                              | Memo          | ory                                | 18 |  |  |  |

|    |                                  | 2.4.1         | Instruction RAM Outline            | 19 |  |  |  |

|    |                                  | 2.4.2         | Data Memory Outline                | 19 |  |  |  |

|    |                                  | 2.4.3         | Data Memory Addressing             | 19 |  |  |  |

|    | 2.5                              | On-ch         | ip Peripheral Circuit              | 20 |  |  |  |

|    |                                  | 2.5.1         | Serial Interface Outline           | 20 |  |  |  |

|    |                                  | 2.5.2         | Host Interface Outline             | 20 |  |  |  |

|    |                                  | 2.5.3         | General Input/output Ports Outline | 20 |  |  |  |

|    |                                  | 2.5.4         | Wait Cycle Register                | 20 |  |  |  |

| 3. | INS                              | TRUCT         | IONS                               | 21 |  |  |  |

|    | 3.1                              |               | ie                                 |    |  |  |  |

|    | 3.2                              |               | ction Set and Operation            |    |  |  |  |

| 4. | ELE                              | CTRIC         | AL SPECIFICATIONS                  | 29 |  |  |  |

| 5. | PAC                              | KAGE          | DRAWING                            | 50 |  |  |  |

| 6. | RECOMMENDED SOLDERING CONDITIONS |               |                                    |    |  |  |  |

# 1. PIN FUNCTIONS

## 1.1 Pin Functions

# • Power supply

| Symbol | Pin No.                                                    | I/O | Function         |

|--------|------------------------------------------------------------|-----|------------------|

| Vdd    | 15, 26, 36, 46, 56, 62, 71,<br>95, 106, 116, 131, 141, 151 | -   | +5V power supply |

| GND    | 14, 25, 35, 45, 55, 61, 70,<br>94, 105, 115, 130, 140, 150 | -   | Ground           |

# • System control

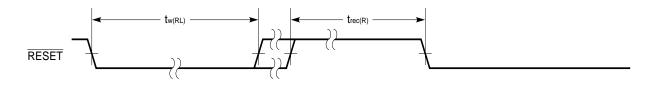

| Symbol | Pin No. | I/O | Function                           |

|--------|---------|-----|------------------------------------|

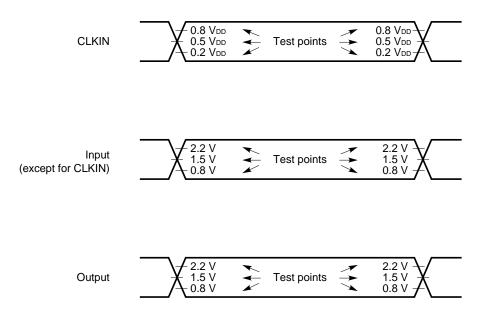

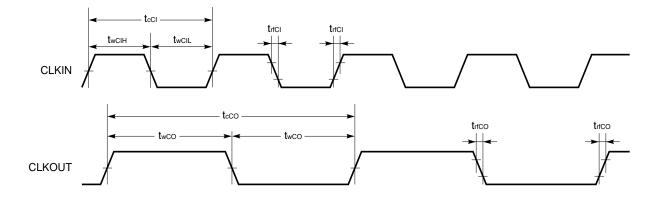

| CLKIN  | 8       | I   | External clock input               |

| CLKOUT | 13      | 0   | Internal system clock output       |

| RESET  | 1       | I   | Internal system reset signal input |

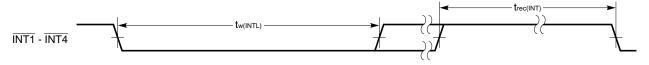

#### • Interrupt

| Symbol      | Pin No.    | I/O | Function                                                                     |

|-------------|------------|-----|------------------------------------------------------------------------------|

| INT4 - INT1 | 2, 3, 4, 5 | I   | Maskable external interrupt input <ul> <li>Falling edge detection</li> </ul> |

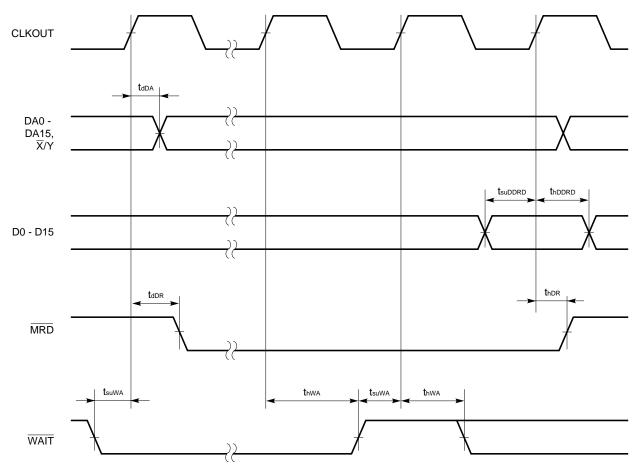

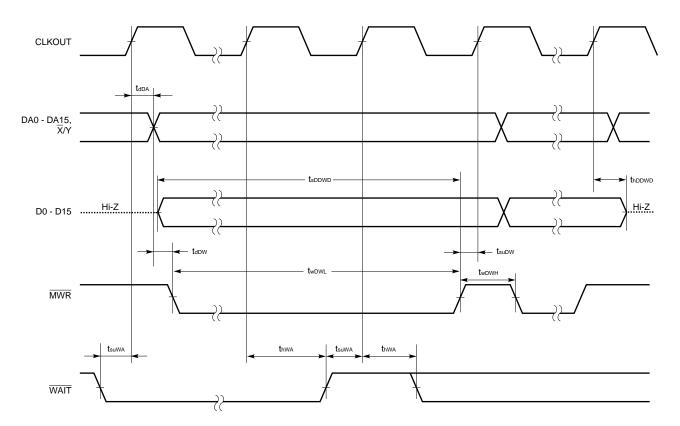

#### • External data memory interface

| Symbol     | Pin No. | I/O         | Function                                                                                                                                                                                                                                                                                                                                    |

|------------|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ху         | 20      | O<br>(3S)   | <ul><li>Memory select signal output</li><li>0: X memory is used.</li><li>1: Y memory is used.</li></ul>                                                                                                                                                                                                                                     |

| DA15 - DA0 | Note 1. | O<br>(3S)   | <ul> <li>Address bus to external data memory</li> <li>External data memory is accessed.</li> <li>During the external memory is not accessed, these pins keep the previous level.</li> <li>These pins are set to low level; 0x0000, by reset.</li> <li>They continue outputting low level until the first external memory access.</li> </ul> |

| D15 - D0   | Note 2. | I/O<br>(3S) | <ul><li>16 bits data bus to external data memory</li><li>External data memory is accessed.</li></ul>                                                                                                                                                                                                                                        |

| MRD        | 17      | O<br>(3S)   | Read output <ul> <li>Reads external memory</li> </ul>                                                                                                                                                                                                                                                                                       |

| MWR        | 16      | 0<br>(3S)   | Write output <ul> <li>Writes external memory</li> </ul>                                                                                                                                                                                                                                                                                     |

| WAIT       | 6       | I           | Wait signal input <ul> <li>Wait cycle is input when external memory is read.</li> <li>1: No wait</li> <li>0: Wait</li> </ul>                                                                                                                                                                                                                |

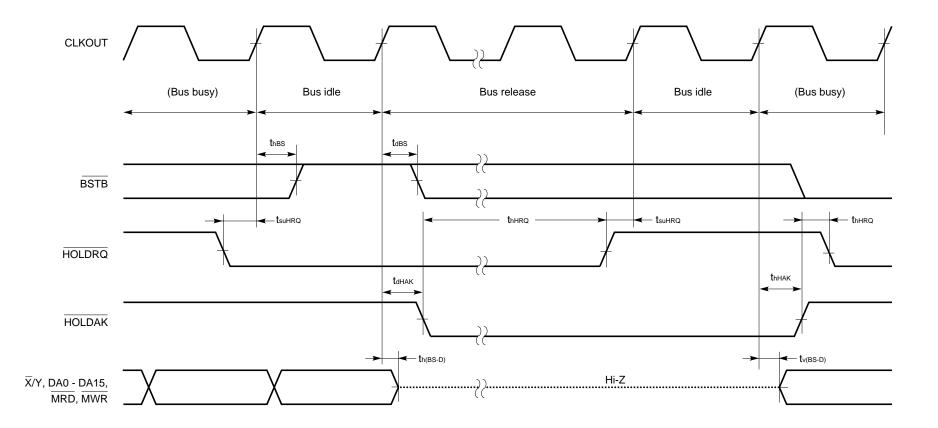

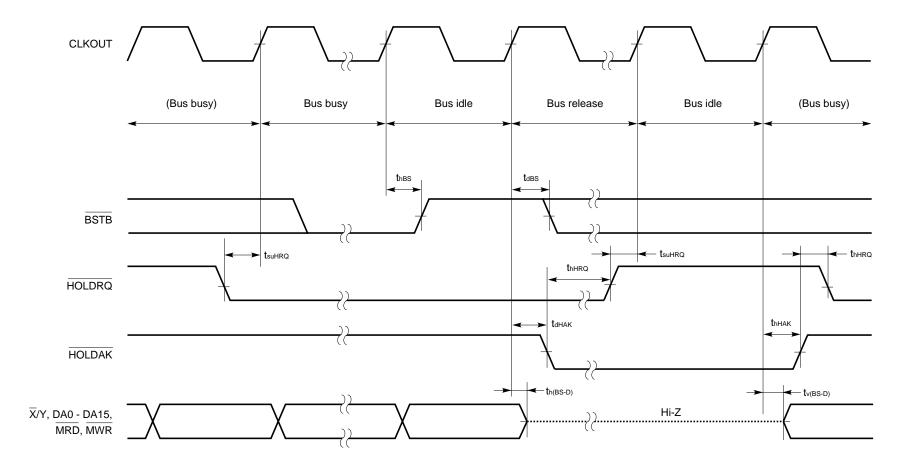

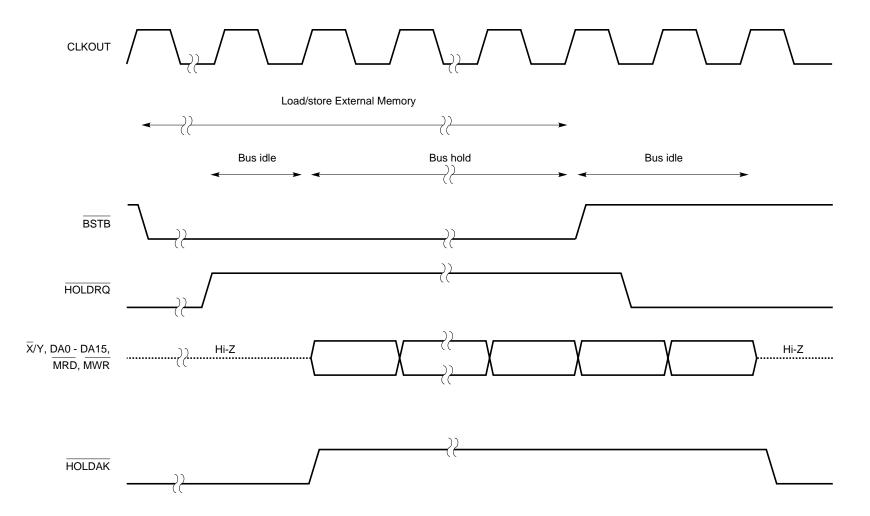

| HOLDRQ     | 7       | I           | <ul><li>Hold request signal input</li><li>Input low level when external data memory bus is expected to use.</li></ul>                                                                                                                                                                                                                       |

| BSTB       | 18      | 0           | <ul> <li>Bus strobe signal output</li> <li>Outputs low level while the μPD77016 is occupying external memory bus.</li> </ul>                                                                                                                                                                                                                |

| HOLDAK     | 19      | 0           | <ul> <li>Hold acknowledge signal output</li> <li>Outputs low level when the μPD77016 permits external device to use external data memory bus.</li> </ul>                                                                                                                                                                                    |

Note 1. DA15 to DA0 pins are located on Pin No. 21 - 24, 27 - 34, 37 - 40.

2. D15 to D0 pins are located on Pin No. 41 - 44, 47 - 54, 57 - 60.

★ Remark The state of the pins added 3S becomes high impedance when the external memory is not accessed or bus release signal (HOLDAK = 0) is output.

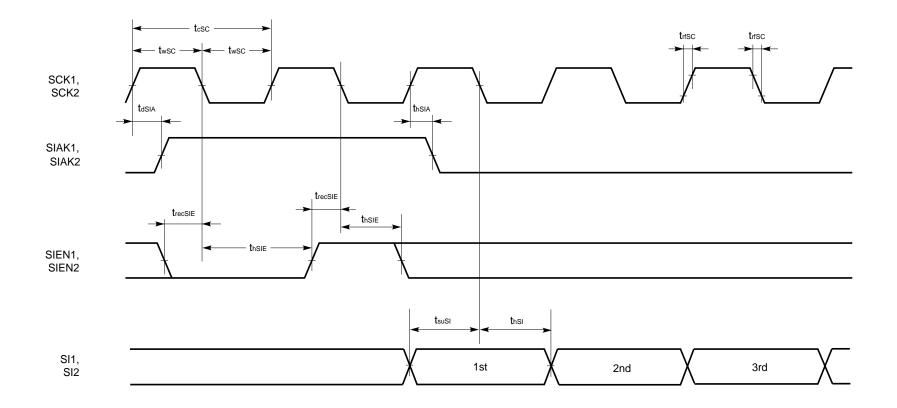

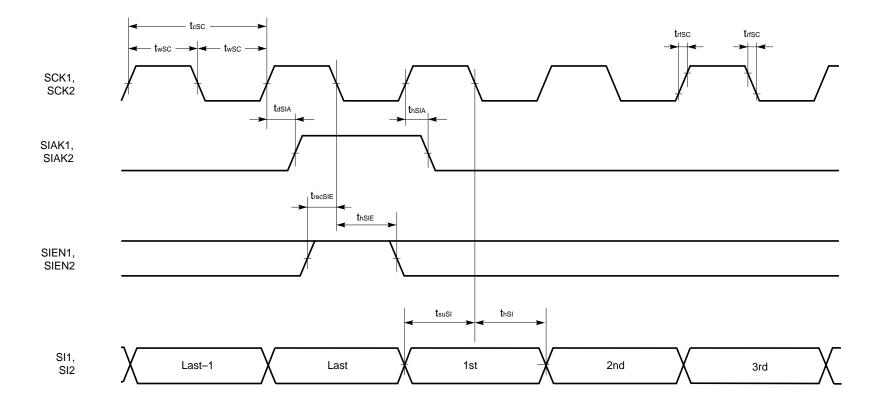

#### Serial interface

| Symbol | Pin No. | I/O    | Function                   |

|--------|---------|--------|----------------------------|

| SCK1   | 65      | I      | Clock input for serial 1   |

| SORQ1  | 68      | 0      | Serial output 1 request    |

| SOEN1  | 69      | I      | Serial output 1 enable     |

| SO1    | 67      | O (3S) | Serial data output 1       |

| SIEN1  | 64      | I      | Serial input 1 enable      |

| SI1    | 63      | I      | Serial data input 1        |

| SCK2   | 76      | I      | Clock input for serial 2   |

| SORQ2  | 73      | Ο      | Serial output 2 request    |

| SOEN2  | 72      | I      | Serial output 2 enable     |

| SO2    | 74      | O (3S) | Serial data output 2       |

| SIEN2  | 77      | I      | Serial input 2 enable      |

| SI2    | 78      | I      | Serial data input 2        |

| SIAK1  | 66      | 0      | Serial input 1 acknowledge |

| SIAK2  | 75      | 0      | Serial input 2 acknowledge |

**Remark** The state of the pins added 3S becomes high impedance, when data output have been finished or **RESET** is input.

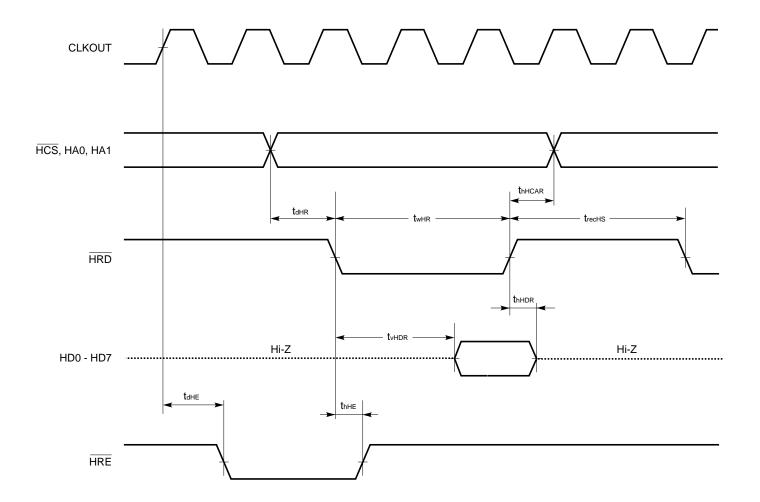

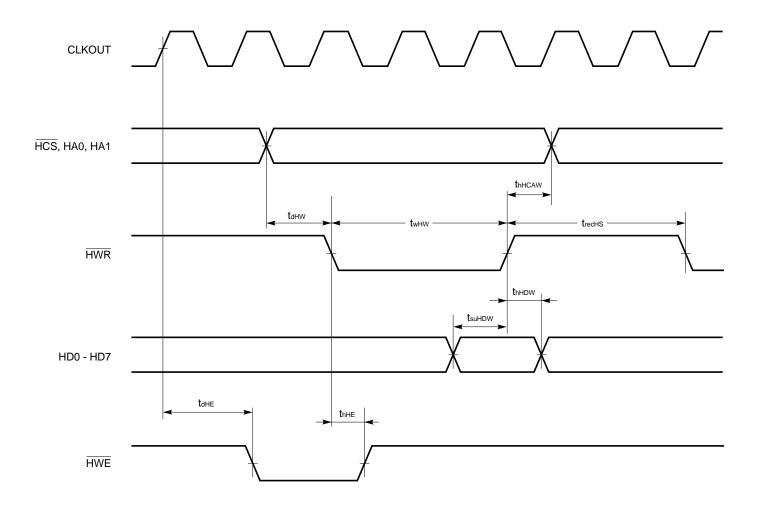

#### • Host interface

| Symbol    | Pin No. | I/O      | Function                                                                                                                                                                                                                                                                                                  |

|-----------|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HA1       | 83      | 1        | Specifies register which HD7 to HD0 access<br>1: Accesses HST: Host interface status register<br>when HA1 = 0<br>0: Accesses HDT <sub>(out)</sub> : Host transmit data register when<br>$\overline{HRD} = 0$<br>0: Accesses HDT <sub>(in)</sub> : Host receive data register when<br>$\overline{HWR} = 0$ |

| HAO       | 82      | I        | <ul> <li>Specifies bits of registers which HD7 to HD0 access</li> <li>1: Accesses bits 15-8 of HST, HDT (out), HDT (in)</li> <li>0: Accesses bits 7-0 of HST, HDT (out), HDT (in)</li> </ul>                                                                                                              |

| HCS       | 79      | I        | Chip select input                                                                                                                                                                                                                                                                                         |

| HRD       | 80      | I        | Host read input                                                                                                                                                                                                                                                                                           |

| HWR       | 81      | I        | Host write input                                                                                                                                                                                                                                                                                          |

| HRE       | 92      | 0        | Host read enable output                                                                                                                                                                                                                                                                                   |

| HWE       | 93      | 0        | Host write enable output                                                                                                                                                                                                                                                                                  |

| HD7 - HD0 | 84 - 91 | I/O (3S) | 8 bits host data bus                                                                                                                                                                                                                                                                                      |

Remark The state of the pins added 3S becomes high impedance when the host does not access host interface.

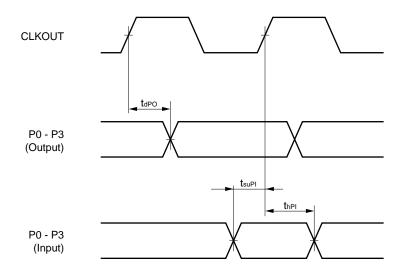

# • I/O port

| Symbol  | Pin No. | I/O | Function |

|---------|---------|-----|----------|

| P3 - P0 | 9 - 12  | I/O | I/O port |

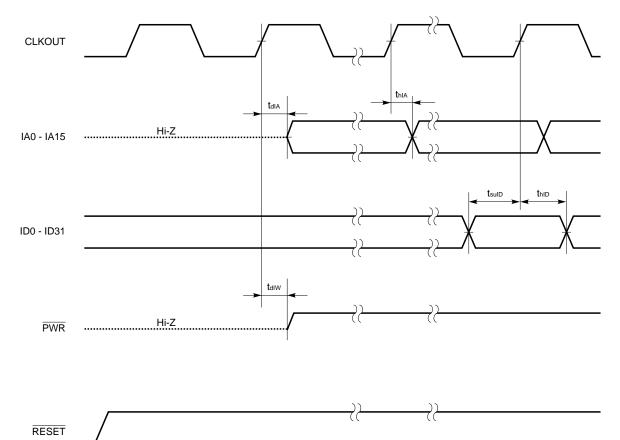

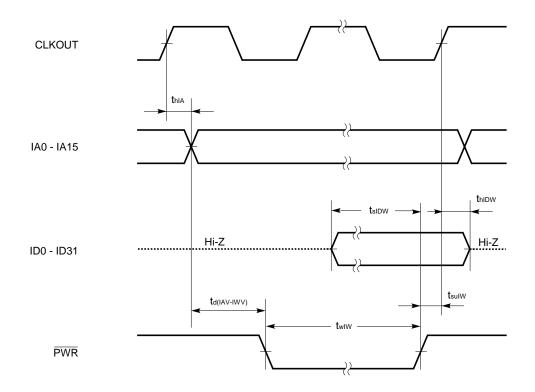

#### • External instructions memory interface

| Symbol     | Pin No. | I/O      | Function                                                                                                                                                                                                                                                           |

|------------|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IA15 - IA0 | Note 1. | O (3S)   | <ul> <li>Address bus to external instruction memory</li> <li>Even the internal instruction memory is accessed, the address is output to the external instruction memory. In this case, the μPD77016 ignores data of external instruction memory output.</li> </ul> |

| ID31 - ID0 | Note 2. | I/O (3S) | 32 bits instruction input                                                                                                                                                                                                                                          |

| PWR        | 129     | O (3S)   | <ul> <li>Program memory write strobe</li> <li>Write strobe for external instruction memory. This pin loads program to external instruction memory (not internal memory) while μPD77016 is in boot operation.</li> </ul>                                            |

Note 1. IA15 to IA0 pins are located on these pins: 101 to 104, 107 to 114, 117 to 120

2. ID31 to ID0 pins are located on these pins: 121 to 128, 132 to 139, 142 to 149, 152 to 159

Remark The state of the pins added 3S becomes high impedance when RESET is input.

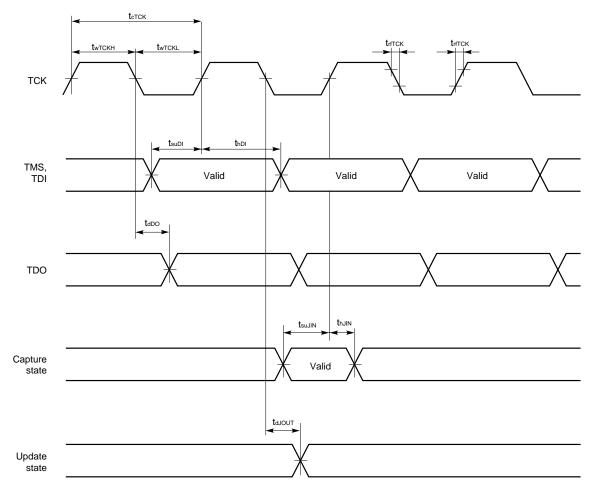

#### • Debugging interface

| Symbol | Pin No. | I/O | Function      |

|--------|---------|-----|---------------|

| TDO    | 96      | 0   | For debugging |

| TICE   | 97      | 0   | For debugging |

| тск    | 98      | I   | For debugging |

| TDI    | 99      | I   | For debugging |

| TMS    | 100     | I   | For debugging |

#### 1.2 Recommended Connection for Unused Pins

| Pin              | I/O | Recommended connection                |

|------------------|-----|---------------------------------------|

| INT1 - INT4      | I   | connect to VDD                        |

| X/Y              | 0   | open                                  |

| DA0 - DA15       | 0   |                                       |

| D0 - D15 Note 1  | I/O | connect to VDD or GND, via a resistor |

| MRD, MWR         | 0   | open                                  |

| WAIT             | I   | connect to VDD                        |

| HOLDRQ           | I   |                                       |

| BSTB             | 0   | open                                  |

| HOLDAK           | 0   |                                       |

| SCK1, SCK2       | I   | connect to VDD or GND                 |

| SI1, SI2         | I   |                                       |

| SOEN1, SOEN2     | I   | connect to GND                        |

| SIEN1, SIEN2     | I   |                                       |

| SORQ1, SORQ2     | 0   | open                                  |

| SO1, SO2         | 0   |                                       |

| SIAK1, SIAK2     | 0   |                                       |

| HA0, HA1         | I   | connect to VDD or GND                 |

| HCS              | I   | connect to VDD                        |

| HRD, HWR         | I   |                                       |

| HRE, HWE         | 0   | open                                  |

| HD0 - HD7 Note 2 | I/O | connect to VDD or GND, via a resistor |

| P0 - P3          | I/O |                                       |

| ID0 - ID31       | I/O |                                       |

| IA0 - IA15       | 0   | open                                  |

| PWR              | 0   |                                       |

| тск              | I   | connect to GND, via a resistor        |

| TDO, TICE        | 0   | open                                  |

| TMS, TDI         | I   | open(pull-up internally)              |

| CLKOUT           | 0   | open                                  |

Notes 1. Can leave open, if no access to external data memory is executed in the whole of program.But in the HALT mode when the current consumption is reduced, connect a pin as recommended connection.

Can leave open, if HCS, HRD, HWR are fixed to high level. But in the HALT mode when the current consumption is reduced, connect a pin as recommended connection.

Remark I: Input pin, O: Output pin, I/O: Input/Output pin

★

# 2. FUNCTIONS

#### 2.1 Pipeline Processing

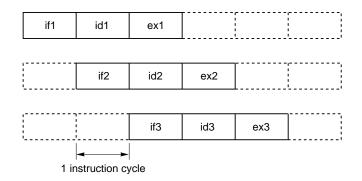

This section describes the  $\mu$ PD77016 pipeline processing.

#### 2.1.1 Outline

The  $\mu$ PD77016 basic operations are executed in following 3-stage pipeline.

- (1) instruction fetch; if

- (2) Instruction decoding; id

- (3) execution; ex

When the  $\mu$ PD77016 operates a result of a instruction just executed before, the data is input to ALU in parallel with written back to general registers. Pipeline processing actualizes programming without delay time to execute instructions and write back data. Three successive instructions and their processing timing are shown below.

#### **Pipeline Processing Timing**

#### 2.1.2 Instructions with Delay

The following instructions have delay time in execution.

(1) Instructions to control interrupt

2 instruction cycles have been taken between instruction fetch and execution.

(2) Inter-register transfer instructions and immediate data set instructions When data is set in data pointer, it needs 2 instruction cycles before the data is valid.

#### 2.2 Program Control Unit

Program control unit controls not only count up of program counter in normal operation, but loop, repeat, branch, halt and interrupt.

In addition to loop stack of loop 4 level and program stack of 15 level, software stack can be used for multiloop and multi-interrupt/subroutine call.

The  $\mu$ PD77016 has external 4 interruptions and internal 6 interruptions from peripheral, and specifies interrupt enable or disable independently.

The HALT instruction causes the µPD77016 to place in low power standby mode.

When the HALT instruction is executed, power consumption decreases. HALT mode is released by interrupt input or hardware reset input. It takes several system clock to recover.

#### 2.3 Operation Unit

Operation unit consists of the following five parts.

- 40 bits general register  $\times$  8 for data load/store and input/output of operation data

- 16 bits  $\times$  16 bits + 40 bits  $\rightarrow$  40 bits multiply accumulator

- 40 bits Data ALU

- 40 bits barrel shifter

- SAC: shifter and count circuit.

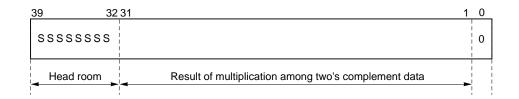

Standard word length is 40 bits to make overflow check and adjustment easy, and to accumulate the result of 16 bits  $\times$  16 bits multiplication correctly.

#### 2.3.1 General register (R0 to R7)

The  $\mu$ PD77016 has eight 40 bits registers for operation input/output and load/store with memory. General register consists of the following three parts.

- R0L to R7L (bit 15 to bit 0)

- R0H to R7H (bit 31 to bit 16)

- R0E to R7E (bit 39 to bit 32)

But each of RnL, RnH and RnE are treated as a register in the following conditions.

#### (1) General register used as 40 bits register

General registers are treated as 40 bits register, when they are used for the following aims.

- (a) Operand for triminal operation (except for multiplier input)

- (b) Operand for dyadic operation (except for multiplier and shift value)

- (c) Operand for monadic operation (except for exponent instructions)

- (d) Operand for operation

- (e) Operand for conditional judge

- (f) Destination for load instruction (with sign extension and 0 clear)

#### (2) General register used as 32 bits register

Bit 31 to bit 0 of general register are treated as 32 bits register, when it is used for a operand of exponent instruction.

#### (3) General register used as 24 bits register

Bit 39 to bit 16 of general register are treated as 24 bits register, when it is used for destination with extended sign for a load/store instruction.

#### (4) General register used as 16 bits register

Bit 31 to bit 16 of general register are treated as 16 bits register, when it is used for the following aims.

- (a) Signed operand for multiplier

- (b) Source/destination for load/store instruction

Bit 15 to bit 0 of general register are treated as 16 bits register, when it is used for the following aims.

- (c) Unsigned operand for multiplier

- (d) Shift value for shift instruction

- (e) Source/destination for load/store instruction

- (f) Source/destination for inter-register transfer instruction

- (g) Destination for immediate data set instruction

- (f) Hardware loop times

#### (5) General register used as 8 bits register

Bit 39 to bit 32 of general register are treated as 8 bits register, when it is used for source/destination of load/ store instruction.

#### 2.3.2 MAC: Multiply ACcumulator

MAC multiplies a pair of 16 bits data, and adds or subtract the result and 40 bits data. MAC outputs 40 bits data.

MAC operates three types of multiplication: signed data  $\times$  signed data, signed data  $\times$  unsigned data and unsigned data.

Result of multiplication and 40 bits data for addition can be added after 1 or 16 bits arithmetic shift right.

#### 2.3.3 ALU: Arithmetic Logic Unit

ALU performs arithmetic operation and logic operation. Both input/output data are 40 bits.

#### 2.3.4 BSFT: Barrel ShiFTer

BSFT performs shift right/left operation. Both input/output data are 40 bits. There are two types of shift right operations; arithmetic shift right which sign is extended, and logic shift right which is input 0 in MSB first.

#### 2.3.5 SAC: Shifter And Count Circuit

SAC calculates and outputs shift value for normalization. SAC is input 32 bits data and outputs the 40 bits data. Then, bit 39 to bit 5 of output data is always 0.

#### 2.3.6 CJC: Condition Judge Circuit

CJC judges whether condition is true or false with 40 bits input data. A conditional instruction is executed when the result is true, and not executed when the result is false.

#### 2.4 Memory

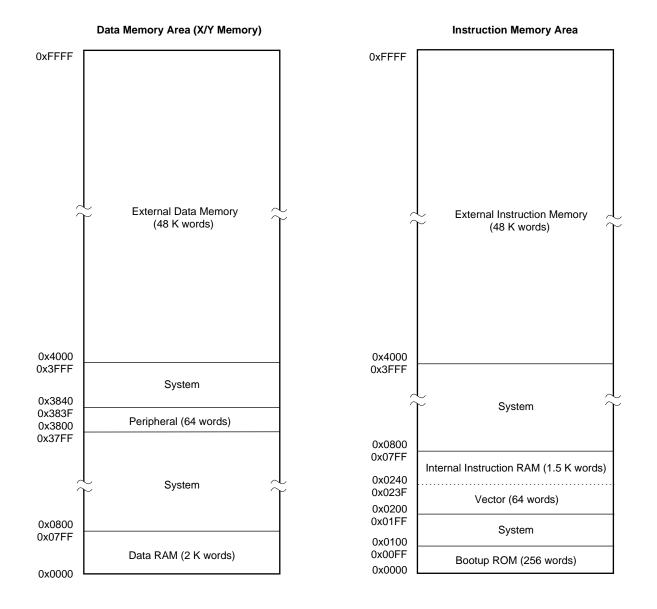

The  $\mu$ PD77016 has one instruction memory area (64K words  $\times$  32 bits) and two data memory areas (64K words  $\times$  16 bits each). It adopts Harvard-type architecture, with instruction memory area and data memory areas separated.

The  $\mu$ PD77016 has 2 sets of data addressing units, which are dedicated for addressing data memory area. Each addressing unit consists of four data pointers, four index registers, a modulo register and addressing ALU. Memory areas are shown below.

X memory area addresses are specified by DP0 to DP3, and Y memory area addresses are specified by DP4 to DP7. After memory access, DPn (with the same subscript), can be modified by DNn value. Modulo operation is performed with DMX for DP0 to DP3, with DMY for DP4 to DP7.

Caution When any data is accessed or stored to system address, normal operation of the  $\mu$ PD77016 is not assured.

#### 2.4.1 Instruction RAM Outline

The  $\mu$ PD77016 has an instruction RAM (1.5 words × 32 bits). A system vector area is assigned to 64 words of the instruction RAM. Internal RAM is initialized and rewritten by boot program.

Additionally external memory expansion is available as the  $\mu$ PD77016 has interface with the external instruction memory. When RAM is used as the external memory, it can be initialized and rewritten by boot program.

Boot up ROM contains the program loading instruction code to internal and external instruction RAM. When the external instruction memory area is accessed, instruction cycle can be 2 or more by wait function.

#### 2.4.2 Data Memory Outline

The  $\mu$ PD77016 has two data memory areas (64 words  $\times$  16 bits each) in X and Y memory areas.

Each memory areas consists of 2K words  $\times$  16 bits data RAM. Additionally, data memory expansion is available as the  $\mu$ PD77016 has interface with the external data memory.

Each data memory area includes on-chip peripheral area which consists of 64 words.

When the external data memory area is accessed, instruction cycle can be 2 or more by wait function.

#### 2.4.3 Data Memory Addressing

There are following two types of data memory addressing.

• Direct addressing

The address is specified in the instruction field.

Indirect addressing

The address is specified by the data pointer (DP). DP can get a bit reverse before addressing. It can update the DP value after accessing data memory.

#### 2.5 On-chip Peripheral Circuit

The  $\mu$ PD77016 includes serial interface, host interface, general input/output ports and wait cycle registers. They are mapped in both X and Y memory areas, and are accessed as memory mapped I/O by the  $\mu$ PD77016 CPU.

#### 2.5.1 Serial Interface Outline

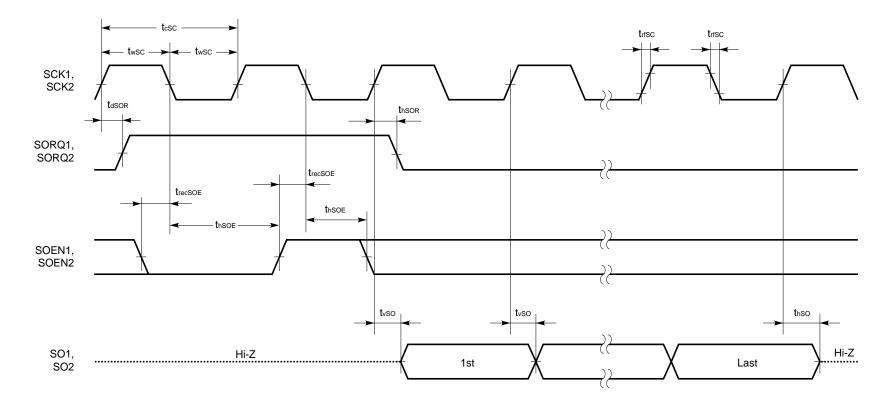

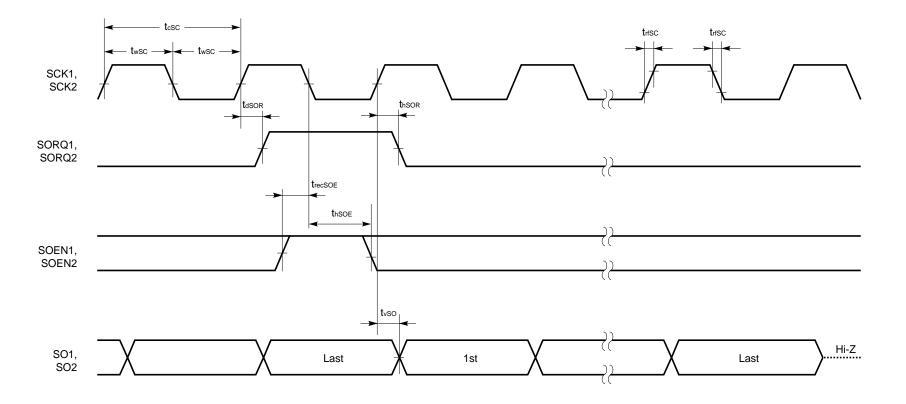

The  $\mu$ PD77016 has 2 channel serial interfaces. Serial I/O clock must be provided from external. Frame length can be programmed independently to be 8 bits or 16 bits. MSB first or LSB first can also be selected. Data is input/output by hand shaking for an external device, and by interrupts, polling or wait function in internal.

#### 2.5.2 Host Interface Outline

The  $\mu$ PD77016 has 8 bits parallel ports as host interface to input/output data to and from host CPU and DMA controller. When an external device accesses host interface, HA0 and HA1 pins; which are host address input pins; specifies bit 15 to bit 8 and bit 7 to bit 0. The  $\mu$ PD77016 includes 3 registers consisting of 16 bits, which are dedicated for input data, output data and status. The  $\mu$ PD77016 has three types of interface method for internal and external data; interrupts, polling and wait function.

#### 2.5.3 General Input/output Ports Outline

General input/output ports consist of 4 bits. User can set each port as input or output. The  $\mu$ PD77016 includes two registers. One is 4 bits register for input/output data, and the other is 16 bits for control.

#### 2.5.4 Wait Cycle Register

The wait cycle registers consist of 16 bits. It is used to set wait cycle number when external memory is accessed. 0, 1, 3, or 7 wait cycle can be set in every data area which is divided into 8, and in every X and Y memory area which is divided into 4.

When data area is accessed, wait cycle can be also set by  $\overline{\text{WAIT}}$  pin.

## 3. INSTRUCTIONS

#### 3.1 Outline

All  $\mu$ PD77016 instructions are one-word instructions, consisting of 32 bits. And they are executed in 30 ns (min.) per instruction. There are following 9 instruction types.

#### (1) Trinomial instructions

: specify the Acc operation. 3 of general registers are specified optionally as the operation object.

#### (2) Dyadic operation instructions

: specify the Acc, ALU or shifter operation. 2 of general registers are specified optionally as the operation object. Some instructions can specify a general register and immediate data.

#### (3) Monadic operation instructions

: specify operations by ALU. 1 general register is specified optionally as the operation object.

#### (4) Load/store instructions

: transfer 16 bits data from memory to general registers, from general registers to memory and between general registers.

#### (5) Inter-register transfer instructions

: transfer data between general register and other registers.

#### (6) Immediate data set instructions

: set immediate data at general registers or each registers of address operation unit.

#### (7) Branch instructions

: specify the direction of the program flow.

#### (8) Hardware loop instructions

: specify times of instruction repeating.

#### (9) Control Instructions

: specify the control program.

#### 3.2 Instruction Set and Operation

An operation is written according to the rules for expressing. An expression of instructions having two or more descriptions can have only one selected.

#### (a) Expressions and selectable registers

Expression and selectable registers are shown as follows.

| Expression   | Selectable registers                                                                                    |

|--------------|---------------------------------------------------------------------------------------------------------|

| ro, ro', ro" | R0 - R7                                                                                                 |

| rl, rl'      | R0L - R7L                                                                                               |

| rh, rh'      | R0H - R7H                                                                                               |

| re           | R0E - R7E                                                                                               |

| reh          | R0EH - R7EH                                                                                             |

| dp           | DP0 - DP7                                                                                               |

| dn           | DN0 - DN7                                                                                               |

| dm           | DMX, DMY                                                                                                |

| dpx          | DP0 - DP3                                                                                               |

| dpy          | DP4 - DP7                                                                                               |

| dpx_mod      | DPn, DPn++, DPn, DPn##, DPn%%, !DPn## (n = 0 - 3)                                                       |

| dpy_mod      | DPn, DPn++, DPn, DPn##, DPn%%, !DPn## (n = 4 - 7)                                                       |

| dp_imm       | DPn##imm (n = 0 - 7)                                                                                    |

| ***          | content of memory address ×××                                                                           |

|              | <b>Example</b> When the content of DP0 register is 1000, *DP0 shows the content of memory address 1000. |

#### (b) Modifying data pointers

Data pointers are modified after memory access. The results are valid immediately after instruction execution. It is impossible to modify without memory access.

| Description | Operation                                                                                |

|-------------|------------------------------------------------------------------------------------------|

| DPn         | No operation: DPn value does not change.                                                 |

| DPn++       | $DPn \leftarrow DPn+1$                                                                   |

| DPn         | $DPn \leftarrow DPn-1$                                                                   |

| DPn##       | DPn ← DPn + DNn: Adds DN0-DN7 corresponding to DP0-DP7<br><b>Example</b> DP0 ← DP0 + DN0 |

| DPn%%       | $(n = 0 - 3)$ DPn = $((DP_L + DNn) \mod (DMX + 1)) + DP_H$                               |

|             | (n = 4 - 7) DPn = ((DPL + DNn ) mod (DMY + 1)) + DPH                                     |

| !DPn##      | Access memory after DPn value is bit-reversed<br>After memory access, DPn ← DPn + DNn    |

| DPn##imm    | $DPn \leftarrow DPn + imm$                                                               |

#### (c) Concurrent processing instructions

$\bigcirc$  shows concurrent processing instruction.

Instruction names are shown in abbreviation.

| TRI   | : | Trinomial               |

|-------|---|-------------------------|

| DYAD  | : | Dyadic                  |

| MONAD | : | Monadic                 |

| TRANS | : | Inter-register transfer |

| IMM   | : | Immediate data set      |

| BR    | : | Branch                  |

| LOOP  | : | Hardware loop           |

| CTR   | : | Control                 |

|       |   |                         |

#### (d) State of Overflow flag (OV)

The following marks show the  $\mu$ PD77016 overflow flag state.

- •: Not affected

- $\updownarrow$ : 1 is set when the result of operation is overflow.

Caution If overflow does not occur after operation, OV is not reset, and keeps the state before operation.

NEC

# $\mu$ PD77016 INSTRUCTION SET

|           |                                  |                                                                   |                                              |      |       | Cor    | ncurrent V | Vriting Pro | cessing |      |    |  | Flag |

|-----------|----------------------------------|-------------------------------------------------------------------|----------------------------------------------|------|-------|--------|------------|-------------|---------|------|----|--|------|

|           | Name                             | Mnemonic                                                          | Operation                                    | TRI. | DYAD. | MONAD. | store      | BR.         | LOOP.   | CTL. | ov |  |      |

|           | Multiply add                     | ro = ro + rh*rh'                                                  | ro ← ro+rh∗rh'                               |      |       |        | 0          |             |         |      |    |  | \$   |

|           | Multiply sub                     | ro = ro-rh*rh'                                                    | ro ← ro–rh∗rh'                               |      |       |        | 0          |             |         |      |    |  | \$   |

| Trinomial | Sign unsign<br>Multiply add      | ro = ro + rh*rl<br>(rl should be a plus<br>integral number.)      | ro ← ro+rh*rl                                |      |       |        | 0          |             |         |      |    |  | \$   |

|           | Unsign unsign<br>Multiply add    | ro=ro+rl*rl'<br>(rl and rl' should be a plus<br>integral number.) | ro ← ro+rl*rl'                               |      |       |        | 0          |             |         |      |    |  | \$   |

|           | 1 bit shift Multiply add         | ro=(ro>>1)+rh*rh'                                                 | $ro \leftarrow \frac{ro}{2} + rh * rh'$      |      |       |        | 0          |             |         |      |    |  | \$   |

|           | 16 bits shift Multiply add       | ro = (ro>>16)+rh*rh'                                              | $ro \leftarrow \frac{ro}{2^{16}} + rh * rh'$ |      |       |        | 0          |             |         |      |    |  |      |

|           | Multiply                         | ro=rh*rh'                                                         | $ro \leftarrow rh*rh'$                       |      |       |        | 0          |             |         |      |    |  |      |

|           | Add                              | ro"=ro+ro'                                                        | ro" ← ro+ro'                                 |      |       |        | 0          |             |         |      |    |  | \$   |

|           | Immediate add                    | ro'=ro+imm                                                        | $ro' \leftarrow ro+imm (imm 1)$              |      |       |        |            |             |         |      |    |  | \$   |

|           | Sub                              | ro"=ro-ro'                                                        | ro" ← ro−ro'                                 |      |       |        | 0          |             |         |      |    |  | \$   |

|           | Immediate sub                    | ro'=ro-imm                                                        | $ro' \leftarrow ro-imm (imm 1)$              |      |       |        |            |             |         |      |    |  | \$   |

| Dyadic    | Arithmetic right shift           | ro'=ro SRA rl                                                     | $ro' \leftarrow ro >> rl$                    |      |       |        | 0          |             |         |      |    |  |      |

|           | Immediate arithmetic right shift | ro'=ro SRA imm                                                    | $ro' \leftarrow ro >> imm$                   |      |       |        |            |             |         |      |    |  | •    |

|           | Logic right shift                | ro'=ro SRL rl                                                     | $ro' \leftarrow ro >> rl$                    |      |       |        | 0          |             |         |      |    |  |      |

|           | Immediate Logic right shift      | ro'=ro SRL imm                                                    | $ro' \leftarrow ro >> imm$                   |      |       |        |            |             |         |      |    |  |      |

|           | Logic left shift                 | ro'=ro SLL rl                                                     | ro' ← ro << rl                               |      |       |        | 0          |             |         |      |    |  |      |

|           | Immediate logic left shift       | ro'=ro SLL imm                                                    | $ro' \leftarrow ro << imm$                   |      |       |        |            |             |         |      |    |  |      |

μ**PD77016**

24

| μP |

|----|

|    |

| N  |

| 2  |

| 2  |

| 6  |

|         |                        |                   |                                                                                                                                                                                                                                                                                                                          |      | store        O     I       O     I       O     I       O     I       O     I       O     I       O     I       O     I       O     I       O     I       O     I       O     I       O     I       O     I       O     I |        |   |        |      |     |       | Flag |            |

|---------|------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---|--------|------|-----|-------|------|------------|

|         | Name                   | Mnemonic          | Operation                                                                                                                                                                                                                                                                                                                | TRI. | DYAD.                                                                                                                                                                                                                    | MONAD. |   | TRANS. | IMM. | BR. | LOOP. | CTL. | OV         |

|         | And                    | ro" = ro & ro'    | ro" ← ro & ro'                                                                                                                                                                                                                                                                                                           |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       |      |            |

|         | Immediate and          | ro' = ro & imm    | ro' ← ro & imm                                                                                                                                                                                                                                                                                                           |      |                                                                                                                                                                                                                          |        |   |        |      |     |       |      |            |

|         | Or                     | ro" = ro   ro'    | $ro" \leftarrow ro \mid ro'$                                                                                                                                                                                                                                                                                             |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       |      |            |

| Dyadic  | Immediate or           | ro' = ro   imm    | $ro' \leftarrow ro \mid imm$                                                                                                                                                                                                                                                                                             |      |                                                                                                                                                                                                                          |        |   |        |      |     |       |      |            |

| Dyadic  | Exclusive or           | ro" = ro ^ ro'    | ro" ← ro ^ ro'                                                                                                                                                                                                                                                                                                           |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       |      |            |

|         | Immediate exclusive or | ro = ro ^ imm     | $ro \leftarrow ro \land imm$                                                                                                                                                                                                                                                                                             |      |                                                                                                                                                                                                                          |        |   |        |      |     |       |      |            |

|         | Less than              | ro" = LT(ro, ro') | $\label{eq:ro} \begin{array}{l} \mbox{if}(ro\mbox{ro}') \\ \mbox{fro}'' \leftarrow 0 x 0 0 0 0 0 0 0 0 1 \} \\ \mbox{else} \mbox{fro}'' \leftarrow 0 x 0 0 0 0 0 0 0 0 0 0 0 0 \\ \end{array}$                                                                                                                           |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       |      | •          |

|         | Clear                  | CLR(ro)           | ro ← 0x000000000                                                                                                                                                                                                                                                                                                         |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       | 0    |            |

|         | Increment              | ro' = ro + 1      | ro' ← ro + 1                                                                                                                                                                                                                                                                                                             |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       | 0    | $\uparrow$ |

|         | Decrement              | ro' = ro - 1      | ro' ← ro − 1                                                                                                                                                                                                                                                                                                             |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       | 0    | \$         |

|         | Absolute               | ro' = ABS (ro)    | $ \begin{array}{l} \text{if } (\text{ro}{<}0) \\ \{\text{ro}' \leftarrow -\text{ro}\} \\ \text{else } \{\text{ro}' \leftarrow \text{ro}\} \end{array} $                                                                                                                                                                  |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       | 0    | \$         |

|         | One's complement       | ro' = ~ro         | ro' ← ~ro                                                                                                                                                                                                                                                                                                                |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       | 0    |            |

|         | Two's complement       | ro' = -ro         | ro' ← −ro                                                                                                                                                                                                                                                                                                                |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       | 0    | \$         |

| Monadic | Clip                   | ro' = CLIP (ro)   | $\label{eq:constraints} \begin{array}{l} \text{if } (\text{ro} > 0 x 007 \text{FFFFFF}) \\ \{\text{ro}' \leftarrow 0 x 007 \text{FFFFFF}\} \\ \text{else if, } (\text{ro} < 0 x \text{FF8} 0000000) \\ \{\text{ro}' \leftarrow 0 x \text{FF8} 0000000\} \\ \text{else } \{\text{ro}' \leftarrow \text{ro}\} \end{array}$ |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       | 0    | \$         |

|         | Round                  | ro' = ROUND (ro)  | $ \begin{array}{l} \text{if } (\text{ro>0x007FFF0000}) \\ \{\text{ro'} \leftarrow 0x007FF0000\} \\ \text{else if, } (\text{ro>0xFF8000000}) \\  \{\text{ro'} \leftarrow 0xFF80000000\} \\ \text{else } \{\text{ro'} \leftarrow \\ (\text{ro + 0x8000}) \& 0xFFFFF0000\} \end{array} $                                    |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       | 0    | \$         |

|         | Exponent               | ro' = EXP (ro)    | $ro' \leftarrow log_2  (\frac{1}{ro})$                                                                                                                                                                                                                                                                                   |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       | 0    |            |

|         | Substitution           | ro' = ro          | ro' ← ro                                                                                                                                                                                                                                                                                                                 |      |                                                                                                                                                                                                                          |        | 0 |        |      |     |       | 0    |            |

|            |                                             |                                  |                                                                                                                                                                                                                                                                                                                            |      |       | Cor    | ncurrent V     | Vriting Pro | cessing |     |       |      | Flag           |

|------------|---------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------|----------------|-------------|---------|-----|-------|------|----------------|

|            | Name                                        | Mnemonic                         | Operation                                                                                                                                                                                                                                                                                                                  | TRI. | DYAD. | MONAD. | Load/<br>store | TRANS.      | IMM.    | BR. | LOOP. | CTL. | OV             |

|            | Cumulation                                  | ro'+ = ro                        | ro' ← ro'+ro                                                                                                                                                                                                                                                                                                               |      |       |        | 0              |             |         |     |       | 0    | $\updownarrow$ |

|            | Degression                                  | ro'- = ro                        | ro' ← ro'−ro                                                                                                                                                                                                                                                                                                               |      |       |        | 0              |             |         |     |       | 0    | $\uparrow$     |

| Monadic    | Division                                    | ro'/ = ro                        | $\begin{array}{l} \text{if } (\text{sign}(\text{ro'}) == \text{sign}(\text{ro})) \\ \{\text{ro'} \leftarrow (\text{ro'} - \text{ro}) << 1\} \\ \text{else} \\ \{\text{ro'} \leftarrow (\text{ro'} + \text{ro}) << 1\} \\ \text{if } (\text{sign}(\text{ro'}) == 0 \\ \{\text{ro'} \leftarrow \text{ro'} + 1\} \end{array}$ |      |       |        | 0              |             |         |     |       | 0    | \$             |

|            | Parallel load/store                         | ro=*dpx_mod ro'=*dpy_mod         | $ro \leftarrow *dpx, ro' \leftarrow *dpy$                                                                                                                                                                                                                                                                                  |      |       |        |                |             |         |     |       |      |                |

|            | Note1, Note2.                               | ro=*dpx_mod *dpy_mod=rh          | $ro \gets *dpx, *dpy \gets rh$                                                                                                                                                                                                                                                                                             |      |       |        |                |             |         |     |       |      |                |

|            |                                             | *dpx_mod=rh ro=*dpy_mod          | $*dpx \leftarrow rh, ro \leftarrow *dpy$                                                                                                                                                                                                                                                                                   | 0    | 0     | 0      |                |             |         |     |       |      |                |

| Load/store |                                             | *dpx_mod=rh *dpy_mod=rh'         | $*dpx \leftarrow rh, *dpy \leftarrow rh'$                                                                                                                                                                                                                                                                                  |      |       |        |                |             |         |     |       |      |                |

|            | Section load/store<br>Note1, Note2, Note 3. | dest=*dpx_mod dest'=*dpy_mod     | $dest \gets *dpx,  dest' \gets *dpy$                                                                                                                                                                                                                                                                                       |      |       |        |                |             |         |     |       |      |                |

|            | Note I, Note 2, Note 3.                     | dest=*dpx_mod *dpy_mod=source    | $dest \gets *dpx, *dpy \gets source$                                                                                                                                                                                                                                                                                       |      |       |        |                |             |         |     |       |      |                |

|            |                                             | *dpx_mod=source dest=*dpy_mod    | $*dpx \leftarrow source, dest \leftarrow *dpy$                                                                                                                                                                                                                                                                             |      |       |        |                |             |         |     |       |      |                |

|            |                                             | *dpx_mod=source *dpy_mod=source' | $*dpx \leftarrow source, *dpy \leftarrow source'$                                                                                                                                                                                                                                                                          |      |       |        |                |             |         |     |       |      |                |

**Note 1.** One or both of a mnemonic pair can be written.

- 2. After execution of load/store, data is modified by mod.

- 3. One of following mnemonic should be selected: dest, dest' = {ro, reh, re, rh, rl}, source, source' = {re, rh, rl}.

|                |                                                |                                       |                        |      |       | Cor    | ncurrent V     | Vriting Pro | cessing |     |       |      | Flag |

|----------------|------------------------------------------------|---------------------------------------|------------------------|------|-------|--------|----------------|-------------|---------|-----|-------|------|------|

|                | Name                                           | Mnemonic                              | Operation              | TRI. | DYAD. | MONAD. | Load/<br>store | TRANS.      | IMM.    | BR. | LOOP. | CTL. | OV   |

|                | Direct addressing<br>load/store <b>Note 1.</b> | dest = *addr                          | dest ← ∗addr           |      |       |        |                |             |         |     |       |      |      |

| Load/store     |                                                | *addr = source                        | ∗addr ← source         |      |       |        |                |             |         |     |       |      |      |

|                | Immediate index<br>load/store <b>Note 2.</b>   | dest = *dp_imm                        | $dest \gets *dp$       |      |       |        |                |             |         |     |       |      |      |

|                | load/store Note 2.                             | *dp_imm = source                      | ∗dp ← source           |      |       |        |                |             |         |     |       |      |      |

| Inter-register | Inter-register transfer<br>Note 3.             | dest = rl                             | $dest \gets rl$        |      |       |        |                |             |         |     |       | 0    |      |

| transfer       | Note 3.                                        | rl = source                           | $rl \leftarrow source$ |      |       |        |                |             |         |     |       | 0    |      |

|                | Immediate data set                             | rl = imm<br>(provided imm = 0-0xFFFF) | rl ← imm               |      |       |        |                |             |         |     |       |      |      |

| Immediate      |                                                | dp = imm<br>(provided imm = 0-0xFFFF) | $dp \leftarrow imm$    |      |       |        |                |             |         |     |       |      |      |

| data set       |                                                | dn = imm<br>(provided imm = 0-0xFFFF) | $dn \leftarrow imm$    |      |       |        |                |             |         |     |       |      |      |

|                |                                                | dm = imm<br>(provided imm = 1-0xFFFF) | dm ← imm               |      |       |        |                |             |         |     |       |      |      |