# MOS INTEGRATED CIRCUIT μ**PD784915B, 784916B**

## **16-BIT SINGLE-CHIP MICROCONTROLLERS**

#### DESCRIPTION

E

The  $\mu$ PD784915B, 784916B are members of the NEC 78K/IV Series of microcontrollers equipped with a highspeed 16-bit CPU and are versions with improved electrical characteristics of the  $\mu$ PD784915A, 784916A of the  $\mu$ PD784915 Subseries.

This series contains many peripheral hardware units ideal for VCR control, such as a multi-function timer unit (super timer unit) suitable for software servo control and VCR analog circuits.

A one-time PROM version of the  $\mu$ PD784916B, the  $\mu$ PD78P4916, is also available.

Detailed function descriptions are provided in the following user's manuals. Be sure to read them before designing.

# $\mu \text{PD784915}$ Subseries User's Manual - Hardware: U10444E 78K/IV Series User's Manual - Instruction: U10905E

#### FEATURES

- High instruction execution speed realized by 16-bit CPU core

- Minimum instruction execution time: 250 ns (with 8-MHz internal clock)

- High internal memory capacity

| Part Number | ROM         | RAM        |

|-------------|-------------|------------|

| μPD784915B  | 49152 bytes | 1280 bytes |

| μPD784916B  | 63488 bytes |            |

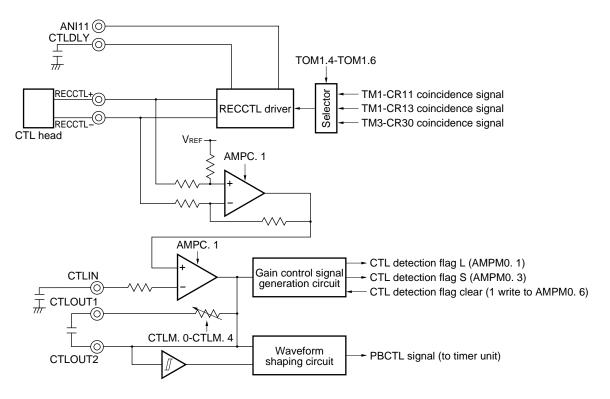

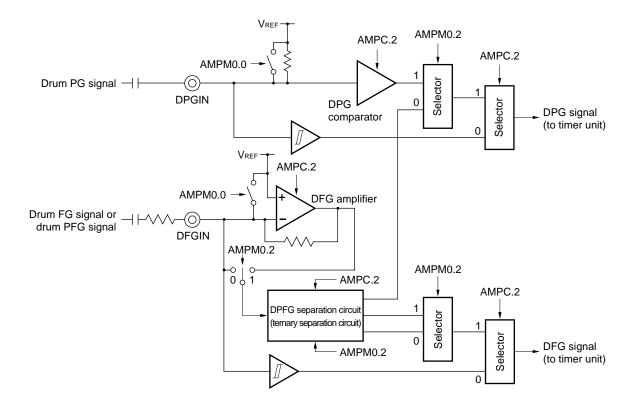

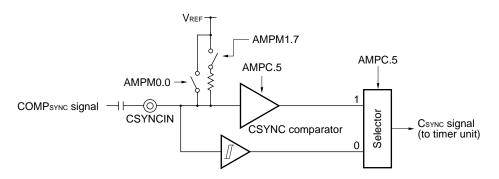

- · VCR analog circuits conforming to VHS Standard

- CTL amplifier

- RECCTL driver (rewritable)

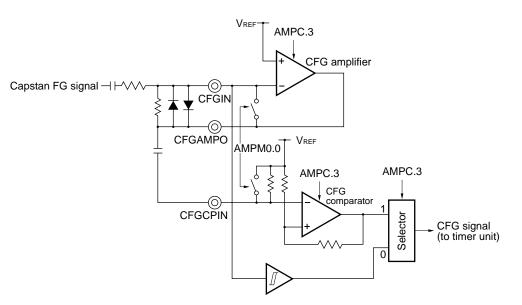

- CFG amplifier

- DFG amplifier

- DPG comparator

- DPFG separation circuit (ternary separation circuit)

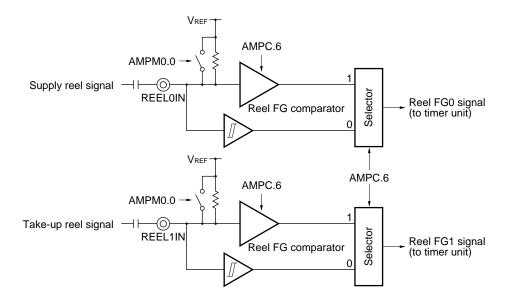

- Reel FG comparator (2 channels)

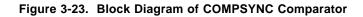

- CSYNC comparator

- Timer unit (super timer unit) for servo control

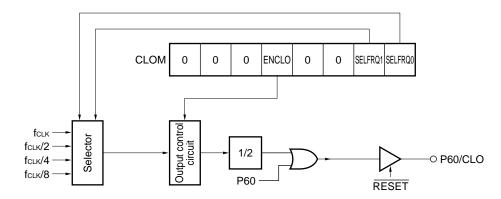

- Serial interface: 2 channels (3-wire serial I/O)

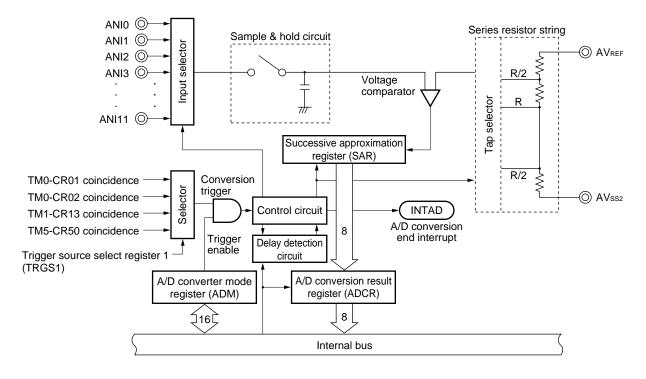

- A/D converter: 12 channels (conversion time: 10 μs)

- Low-frequency oscillation mode: main system clock frequency = internal clock frequency

- · Low-power dissipation mode: CPU can operate with a subsystem clock.

- Supply voltage range: VDD = 2.7 to 5.5 V

- Hardware watch function: watch operation at low voltage (VDD = 2.7 V (MIN.)) and low current

#### APPLICATIONS

Control system/servo/timer of VCR

Unless mentioned otherwise, the  $\mu$ PD784916B is described as the representative product. The information in this document is subject to change without notice

#### ORDERING INFORMATION

### Function List (1/2)

|                       | Item             | μPD784915B                                                 |                         |                        | μPD784916B                    |  |

|-----------------------|------------------|------------------------------------------------------------|-------------------------|------------------------|-------------------------------|--|

| Internal ROM capacity |                  | 49152 bytes                                                |                         | 63488 bytes            | 63488 bytes                   |  |

| Internal              | RAM capacity     | 1280 bytes                                                 |                         |                        |                               |  |

| Operatin              | ng clock         | 16 MHz (internal c                                         | lock: 8 MHz)            |                        |                               |  |

|                       |                  | Low frequency osc                                          | cillation mode: 8 MHz   | (internal clock: 8 MH  | z)                            |  |

|                       |                  | Low power dissipa                                          | tion mode: 32.768 kH    | z (subsystem clock)    |                               |  |

| Minimun               | n instruction    | 250 ns (with 8-MH                                          | z internal system cloc  | k)                     |                               |  |

| executio              | n time           |                                                            |                         |                        |                               |  |

| I/O ports             | 6                | input:8                                                    |                         |                        |                               |  |

|                       |                  | <sup>54</sup> I/O : 46                                     |                         |                        |                               |  |

| Real-tim              | e output port    | 11 (including one                                          | each for pseudo Vsync   | , head amplifier swite | ch, and chrominance rotation) |  |

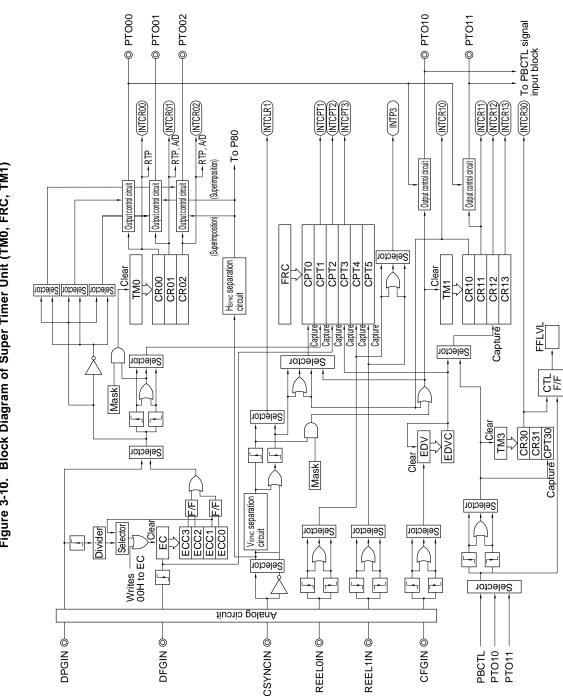

| Super                 | Timer/counter    | Timer/counter                                              | Compare register        | Capture register       | Remark                        |  |

| timer                 |                  | TM0 (16 bits)                                              | 3                       | -                      |                               |  |

| unit                  |                  | TM1 (16 bits)                                              | 3                       | 1                      |                               |  |

|                       |                  | FRC (22 bits)                                              | -                       | 6                      |                               |  |

|                       |                  | TM3 (16 bits)                                              | 2                       | 1                      |                               |  |

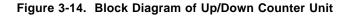

|                       |                  | UDC (5 bits)                                               | 1                       | -                      |                               |  |

|                       |                  | EC (8 bits)                                                | 4                       | -                      | For HSW signal generation     |  |

|                       |                  | EDV (8 bits)                                               | 1                       | -                      | For CFG signal division       |  |

|                       | Capture register | Input signal                                               | Number of bits          | Measurable cycle       | Operating edge                |  |

|                       |                  | CFG                                                        | 22                      | 125 ns to 524 ms       | $\uparrow \qquad \downarrow$  |  |

|                       |                  | DFG                                                        | 22                      | 125 ns to 524 ms       | $\uparrow$                    |  |

|                       |                  | HSW                                                        | 16                      | 1 $\mu$ s to 65.5 ms   | $\uparrow \qquad \downarrow$  |  |

|                       |                  | Vsync                                                      | 22                      | 125 ns to 524 ms       | $\uparrow$                    |  |

|                       |                  | CTL                                                        | 16                      | 1 $\mu$ s to 65.5 ms   | $\uparrow \qquad \downarrow$  |  |

|                       |                  | TREEL                                                      | 22                      | 125 ns to 524 ms       | $\uparrow$ $\downarrow$       |  |

|                       |                  | SREEL                                                      | 22                      | 125 ns to 524 ms       | $\uparrow  \downarrow$        |  |

|                       | VCR special      | • VSYNC separation                                         | n circuit, Hsync separa | tion circuit           |                               |  |

|                       | circuit          | VISS detection,                                            | wide aspect detection   | circuits               |                               |  |

|                       |                  | Field identification                                       |                         |                        |                               |  |

|                       |                  | Head amplifier s                                           | witch/chroma rotation   | output circuit         |                               |  |

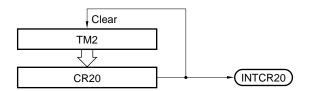

|                       | General-purpose  | Timer                                                      | Compare re              | gister C               | Capture register              |  |

|                       | timer            | TM2 (16 bits)                                              | 1                       |                        | _                             |  |

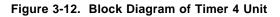

|                       |                  | TM4 (16 bits)                                              | 1 (capture/co           | mpare)                 | 1                             |  |

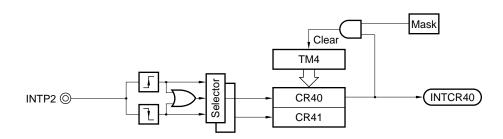

|                       |                  | TM5 (16 bits)                                              | 1                       |                        | —                             |  |

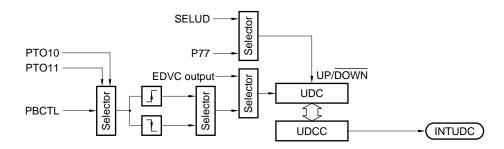

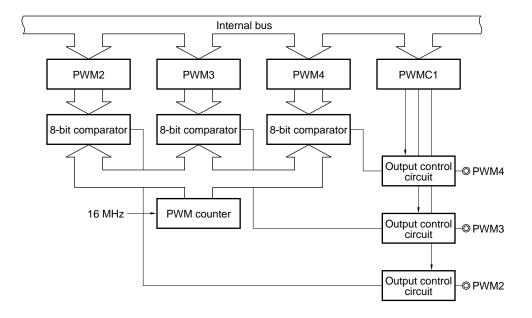

|                       | PWM output       | 16-bit accuracy : 3 channels (carrier frequency: 62.5 kHz) |                         |                        |                               |  |

|                       |                  | 8-bit accuracy                                             | : 3 channels (carrie    | r frequency: 62.5 kH   | z)                            |  |

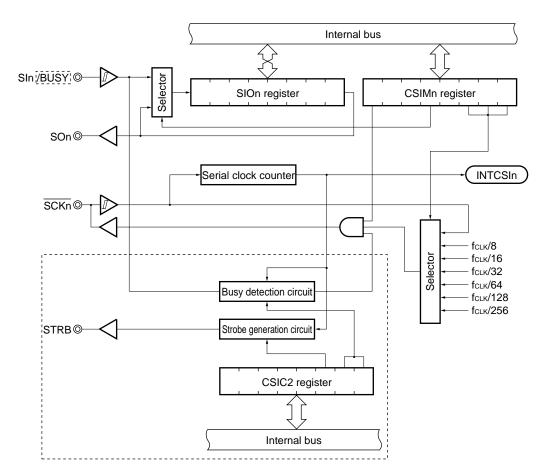

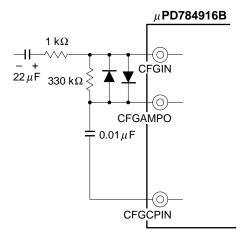

| Serial in             | terface          | 3-wire serial I/O: 2                                       | channels                |                        |                               |  |

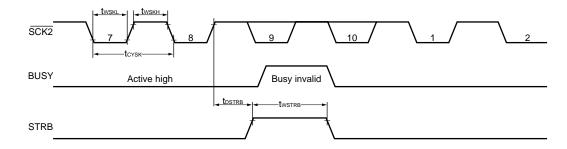

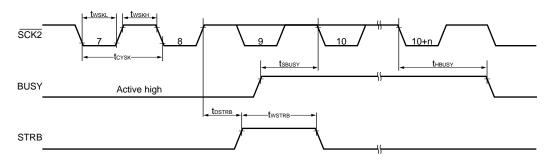

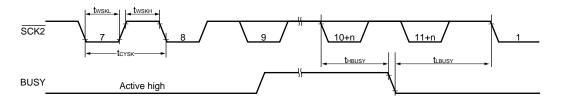

|                       |                  | BUSY/STRB cor                                              | ntrol (1 channel only)  |                        |                               |  |

|                       | verter           | 9 bit recolution v 1                                       | 2 channels, conversion  | n time: 10 up          |                               |  |

### Function List (2/2)

| Item             | μPD784915B                                                                                                                                                                                                                                                   | μPD784916B                        |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|

| Analog circuit   | <ul> <li>CTL amplifier</li> <li>RECCTL driver (rewritable)</li> <li>DFG amplifier, DPG comparator, CFG amplifier</li> <li>DPFG separation circuit (ternary separation circuit)</li> <li>Reel FG comparator (2 channels)</li> <li>CSYNC comparator</li> </ul> |                                   |  |  |

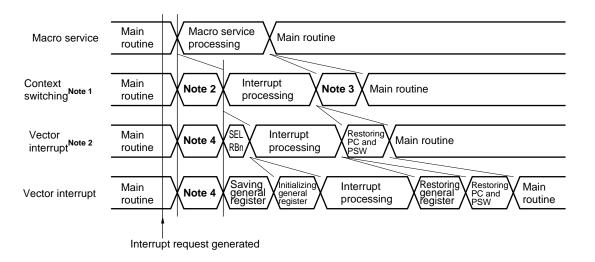

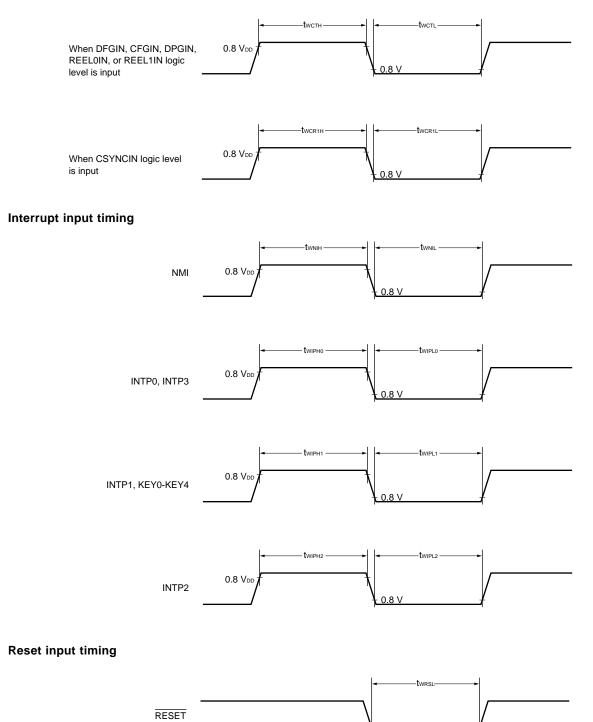

| Interrupt        | 4 levels (programmable), vector interrupt, macro service, context switching                                                                                                                                                                                  |                                   |  |  |

| External         | 9 (including NMI)                                                                                                                                                                                                                                            | 9 (including NMI)                 |  |  |

| Internal         | 19 (including software interrupt)                                                                                                                                                                                                                            |                                   |  |  |

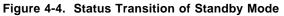

| Standby function | HALT/STOP mode/low power dissipation mode                                                                                                                                                                                                                    | e/low power dissipation HALT mode |  |  |

|                  | STOP mode can be released by input of valid edge of NMI pin, watch interrupt (INTW), or INTP1/INTP2/KEY0-KEY4 pins                                                                                                                                           |                                   |  |  |

| Watch function   | 0.5-second measurement, low-voltage operation (VDD = 2.7 V)                                                                                                                                                                                                  |                                   |  |  |

| Supply voltage   | V <sub>DD</sub> = 2.7 to 5.5 V                                                                                                                                                                                                                               |                                   |  |  |

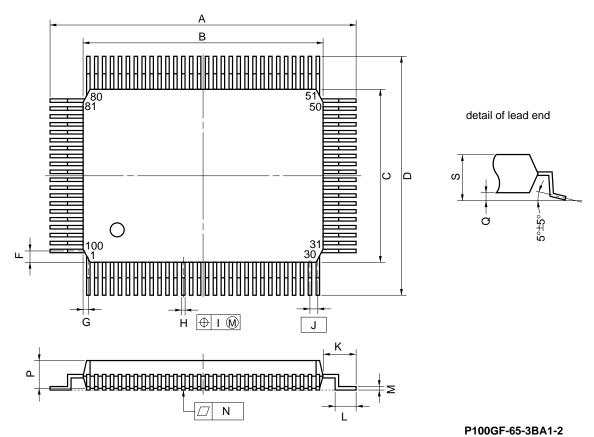

| Package          | 100-pin plastic QFP (14 $\times$ 20 mm)                                                                                                                                                                                                                      |                                   |  |  |

## NEC

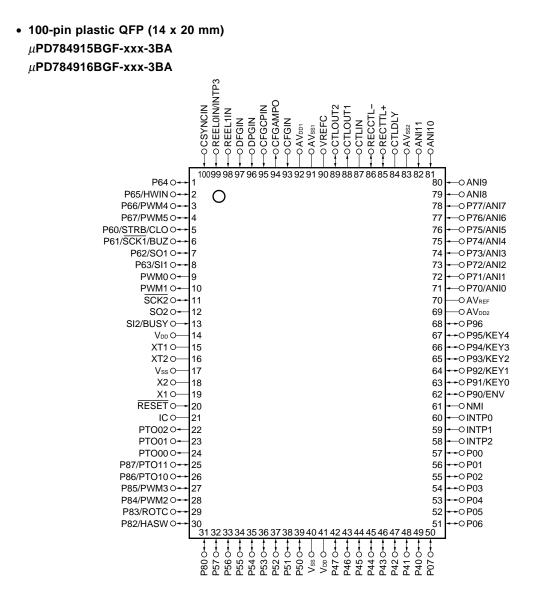

#### **PIN CONFIGURATION (Top View)**

Caution Directly connect the IC (Internally Connected) pin to Vss.

|                  |                                 |                  | . Dorto                         |

|------------------|---------------------------------|------------------|---------------------------------|

| ANIO-ANI11       | : Analog Input                  | P00-P07          | : Port0                         |

| AVdd1, AVdd2     | : Analog Power Supply           | P40-P47          | : Port4                         |

| AVss1, AVss2     | : Analog Ground                 | P50-P57          | : Port5                         |

| AVref            | : Analog Reference Voltage      | P60-P67          | : Port6                         |

| BUSY             | : Serial Busy                   | P70-P77          | : Port7                         |

| BUZ              | : Buzzer Output                 | P80, P82-P87     | : Port8                         |

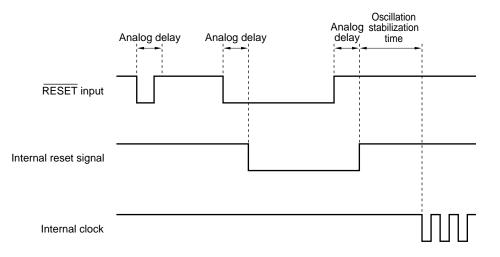

| CFGAMPO          | : Capstan FG Amplifier Output   | P90-P96          | : Port9                         |

| CFGCPIN          | : Capstan FG Capacitor Input    | PTO00-PTO02      | : Programmable Timer Output     |

| CFGIN            | : Analog Unit Input             | PTO10, PTO11     |                                 |

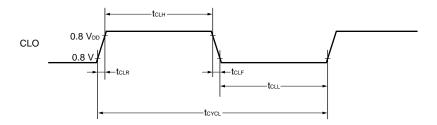

| CLO              | : Clock Output                  | PWM0-PWM5        | : Pulse Width Modulation Output |

| CSYNCIN          | : Analog Unit Input             | RECCTL+, RECCTL- | : RECCTL Output/PBCLT Input     |

| CTLDLY           | : Control Delay Input           | REEL0IN, REEL1IN | : Analog Unit Input             |

| CTLIN            | : CTL Amplifier Input Capacitor | RESET            | : Reset                         |

| CTLOUT1, CTLOUT2 | 2 : CTL Amplifier Output        | ROTC             | : Chrominance Rotate Output     |

| DFGIN            | : Analog Unit Input             | SCK1, SCK2       | : Serial Clock                  |

| DPGIN            | : Analog Unit Input             | SI1, SI2         | : Serial Input                  |

| ENV              | : Envelope Input                | SO1, SO2         | : Serial Output                 |

| HASW             | : Head Amplifier Switch Output  | STRB             | : Serial Strobe                 |

| HWIN             | : Hardware Timer External Input | Vdd              | : Power Supply                  |

| IC               | : Internally Connected          | VREFC            | : Reference Amplifier Capacitor |

| INTP0-INTP3      | : Interrupt From Peripherals    | Vss              | : Ground                        |

| KEY0-KEY4        | : Key Return                    | X1, X2           | : Crystal (Main System Clock)   |

| NMI              | : Nonmaskable Interrupt         | XT1, XT2         | : Crystal (Subsystem Clock)     |

|                  |                                 |                  |                                 |

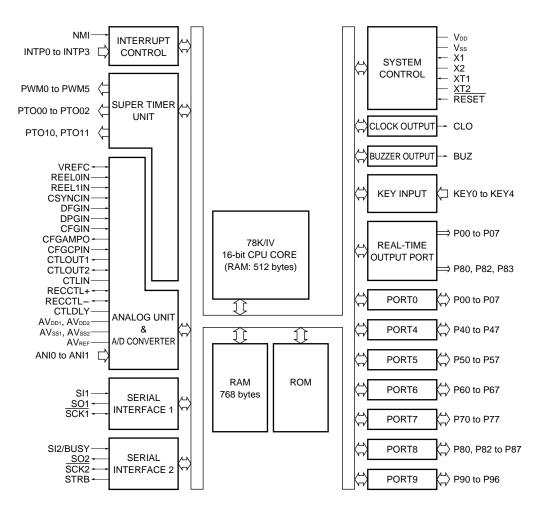

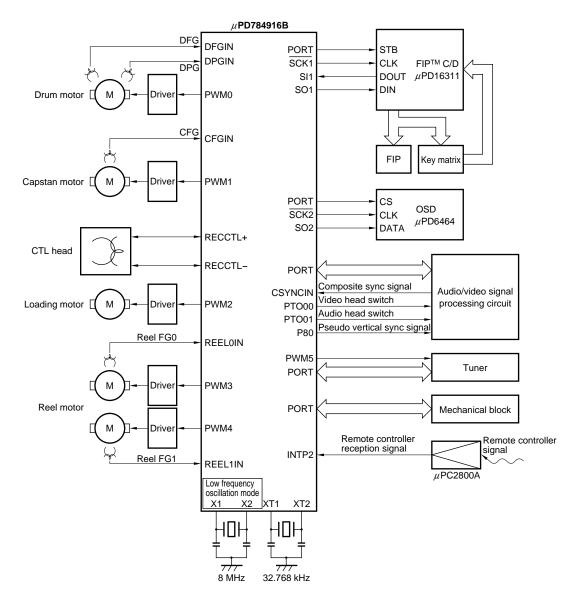

#### INTERNAL BLOCK DIAGRAM

**Remark** Internal ROM capacity depends on the product.

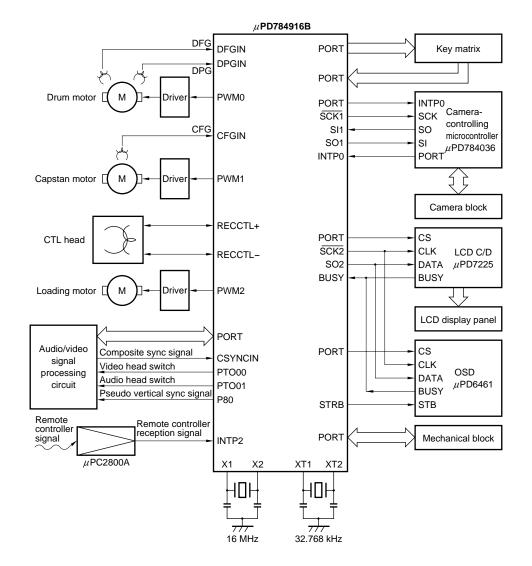

#### SYSTEM CONFIGURATION EXAMPLE

• Camera-contained VCR

• Stationary VCR

## CONTENTS

| 1. | 1. DIFFERENCES AMONG $\mu$ PD784915 SUBSERIES PRODUCTS | 11 |

|----|--------------------------------------------------------|----|

| 2. | 2. PIN FUNCTIONS                                       |    |

|    | 2.1 Port Pins                                          |    |

|    | 2.2 Non-Port Pins                                      |    |

|    | 2.3 I/O Circuits and Connection of Unused Pins         |    |

|    |                                                        |    |

| 3. | 3. INTERNAL BLOCK FUNCTIONS                            |    |

|    | 3.1 CPU Registers                                      |    |

|    | 3.1.1 General-purpose registers                        |    |

|    | 3.1.2 Other CPU registers                              | 20 |

|    | 3.2 Memory Space                                       |    |

|    | 3.3 Special Function Registers (SFRs)                  | 23 |

|    | 3.4 Ports                                              |    |

|    | 3.5 Real-time Output Port                              |    |

|    | 3.6 Super Timer Unit                                   |    |

|    | 3.7 Serial Interface                                   |    |

|    | 3.8 A/D Converter                                      |    |

|    | 3.9 VCR Analog Circuits                                | 41 |

|    | 3.10 Watch Function                                    |    |

|    | 3.11 Clock Output Function                             |    |

|    |                                                        |    |

| 4. |                                                        | -  |

|    | 4.1 Interrupt Function                                 |    |

|    | 4.1.1 Vector interrupt                                 |    |

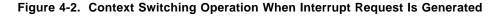

|    | 4.1.2 Context switching                                |    |

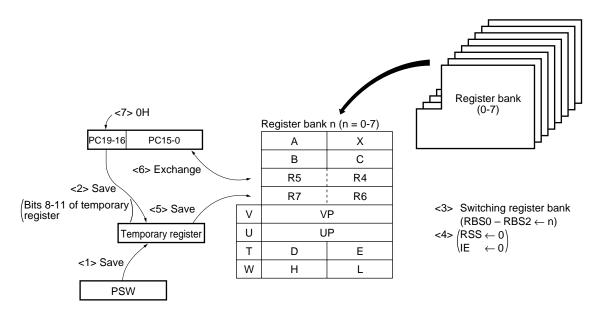

|    | 4.1.3 Macro service                                    |    |

|    | 4.1.4 Application example of macro service             |    |

|    | 4.2 Standby Function                                   | 57 |

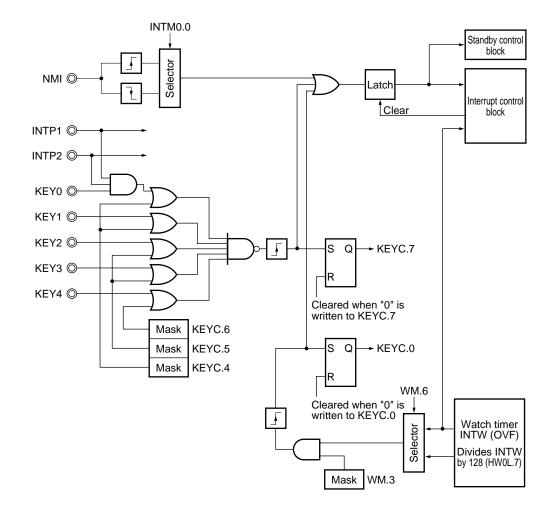

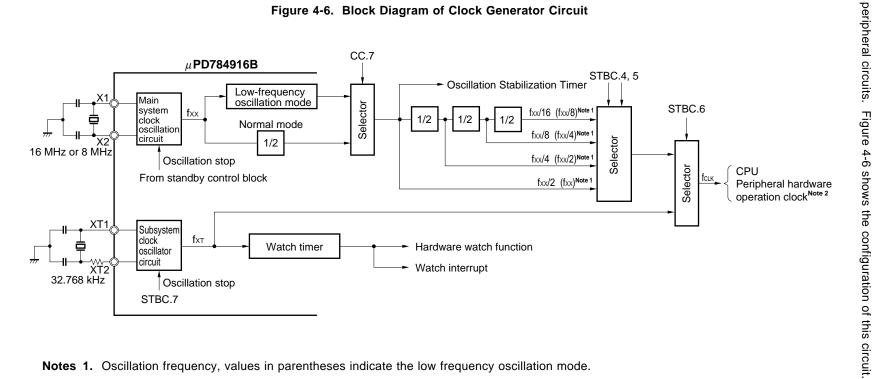

|    | 4.3 Clock Generator Circuit                            | 59 |

|    | 4.4 Reset Function                                     | 60 |

| 5. | 5. INSTRUCTION SETS                                    | 61 |

| 6. | 6. ELECTRICAL CHARACTERISTICS                          |    |

| 7. | 7. PACKAGE DRAWING                                     |    |

| 8. | 8. RECOMMENDED SOLDERING CONDITIONS                    |    |

| AP | APPENDIX A. DEVELOPMENT TOOLS                          |    |

| AP | APPENDIX B. RELATED DOCUMENTS                          |    |

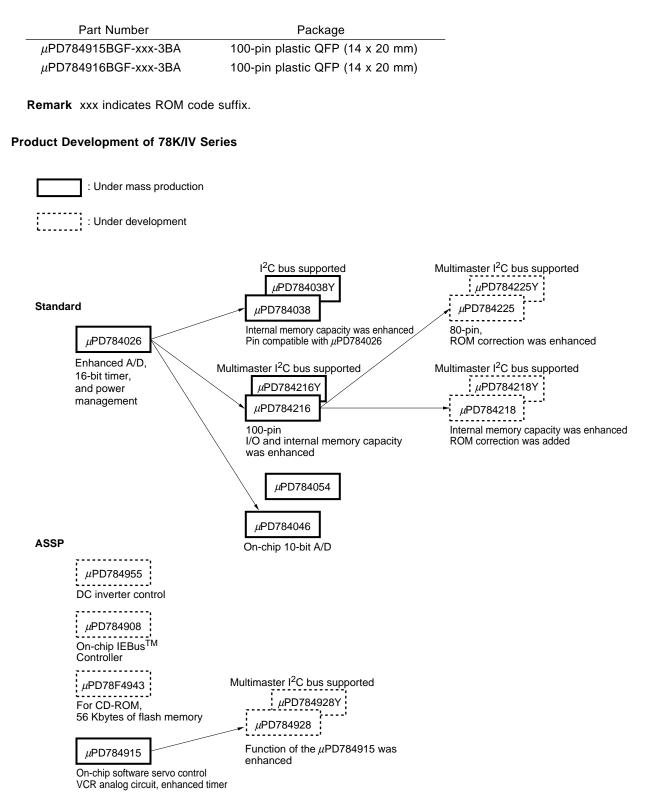

#### 1. DIFFERENCES AMONG $\mu$ PD784915 SUBSERIES PRODUCTS

The  $\mu$ PD784915 Subseries consists of the six products listed in Table 1-1. The  $\mu$ PD784915A is a low-cost processshrinked version of the  $\mu$ PD784915. The  $\mu$ PD784916A expands the internal ROM capacity of the  $\mu$ PD784915 to 62 Kbytes. The  $\mu$ PD784915B and 784916B feature improved electrical characteristics compared to the  $\mu$ PD784915A and 784916A.

The  $\mu$ PD78P4916 features writable one-time PROM instead of the mask ROM of the  $\mu$ PD784915, 784915A, 784916A, 784915B, and 784916B. Except for this substitution of PROM for ROM and the fact that PROM capacity differs from the ROM capacities offered in the other products, the  $\mu$ PD78P4916 has the same functions as those products.

In switching from the PROM product, used for debugging and testing application systems, to the mask ROM products for mass production, be careful to check the differences among these products.

For details on the CPU functions and the internal hardware, refer to  $\mu$ PD784915 Subseries User's Manual — Hardware (U10444E).

| Item                                              | μPD784915,<br>784915A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | μPD784916A                            | μPD784915B  | μPD784916B  | μPD78P4916       |  |  |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------|-------------|------------------|--|--|

| Internal ROM                                      | Mask ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |             |             |                  |  |  |

|                                                   | 49152 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63488 bytes                           | 49152 bytes | 63488 bytes | 63232 bytes Note |  |  |

| Internal RAM                                      | 1280 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1280 bytes 2048 bytes <sup>Note</sup> |             |             |                  |  |  |

| Internal memory capacity selection register (IMS) | Not provided                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Not provided Provided                 |             |             |                  |  |  |

| Electrical characteristics                        | The electrical characteristics of the μPD784915A/784916A, the μPD784915B/784916B, and the μPD78P4916 differ with respect to the items listed below.         • P40 to P47, P50 to P57: Low-level input voltage         • Vob supply current         • Data hold current         • CTL amplifier: Phase signal elimination ratio         • CFG amplifier: CFGAMPO low-level output current         For details, refer to the data sheet of each product.         • μPD784915A/784916A       Data Sheet (U11022J)         • μPD784915B/784916B       Data Sheet (This document)         • μPD78P4916       Data Sheet (U11045J) |                                       |             |             |                  |  |  |

| Pin connections                                   | In the $\mu$ PD78P4916, pin function for PROM read/write has been added.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |             |             |                  |  |  |

Table 1-1. Differences among µPD784915 Subseries Products

**Note** The internal PROM and internal RAM capacities can be changed using the internal memory selection register (IMS).

Caution The PROM version and mask ROM version differ in noise immunity and noise radiation, etc. When considering replacing a PROM version with a mask ROM version when switching from preproduction to volume production, perform sufficient evaluation using a CS version (not ES version) of the mask ROM version.

## 2. PIN FUNCTIONS

### 2.1 Port Pins

| Pin Name   | I/O   | Alternate Function |                           | Function                              |

|------------|-------|--------------------|---------------------------|---------------------------------------|

| P00 to P07 | I/O   | Real-time          | 8-bit I/O port (port 0).  |                                       |

|            |       | output port        | Can be set in input or    | output mode in 1-bit units.           |

|            |       |                    | Can be connected wit      | th software pull-up resistors.        |

| P40 to P47 | I/O   | -                  | 8-bit I/O port (port 4).  |                                       |

|            |       |                    | Can be set in input or    | output mode in 1-bit units.           |

|            |       |                    | Can be connected wit      | th software pull-up resistors.        |

| P50 to P57 | I/O   | -                  | 8-bit I/O port (port 5).  |                                       |

|            |       |                    | Can be set in input or    | output mode in 1-bit units.           |

|            |       |                    | Can be connected wit      | th software pull-up resistors.        |

| P60        | I/O   | STRB/CLO           | 8-bit I/O port (port 6).  |                                       |

| P61        |       | SCK1/BUZ           | Can be set in input or    | output mode in 1-bit units.           |

| P62        |       | SO1                | Can be connected wit      | th software pull-up resistors.        |

| P63        |       | SI1                |                           |                                       |

| P64        |       | -                  |                           |                                       |

| P65        |       | HWIN               |                           |                                       |

| P66        |       | PWM4               |                           |                                       |

| P67        |       | PWM5               |                           |                                       |

| P70 to P77 | Input | ANI0 to ANI7       | 8-bit input port (port 7) |                                       |

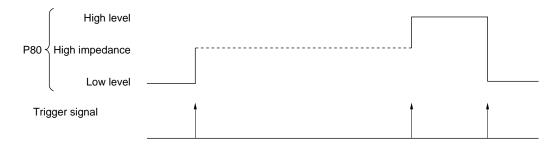

| P80        | I/O   | Real-time          | Pseudo Vsync output       | 7-bit I/O port (port 8).              |

| P82        |       | output port        | HASW output               | Can be set in input or output mode in |

|            |       |                    |                           | 1-bit units.                          |

| P83        |       |                    | ROTC output               | Can be connected with software pull-  |

|            |       |                    |                           | up resistors.                         |

| P84        |       | PWM2               |                           |                                       |

| P85        |       | PWM3               |                           |                                       |

| P86        |       | PTO10              |                           |                                       |

| P87        |       | PTO11              |                           |                                       |

| P90        | I/O   | ENV                | 7-bit I/O port (port 9).  |                                       |

| P91 to P95 |       | KEY0 to KEY4       | Can be set in input or    | output mode in 1-bit units.           |

| P96        | 7     | _                  | Can be connected wit      | th software pull-up resistors.        |

## 2.2 Non-Port Pins (1/2)

| Pin Name         | I/O          | Alternate Function | Function                                                 |

|------------------|--------------|--------------------|----------------------------------------------------------|

| REELOIN          | Input        | INTP3              | Reel FG input                                            |

| REEL1IN          |              | _                  |                                                          |

| DFGIN            |              | _                  | Drum FG, PFG input (ternary)                             |

| DPGIN            |              | -                  | Drum PG input                                            |

| CFGIN            |              | _                  | Capstan FG input                                         |

| CSYNCIN          |              | _                  | Composite SYNC input                                     |

| CFGCPIN          |              | _                  | CFG comparator input                                     |

| CFGAMPO          | Output       | _                  | CFG amplifier output                                     |

| PTO00            | Output       | _                  | Programmable timer output of super timer unit            |

| PTO01            |              | -                  |                                                          |

| PTO02            |              | _                  |                                                          |

| PTO10            |              | P86                |                                                          |

| PTO11            |              | P87                |                                                          |

| PWM0             | Output       | _                  | PWM output of super timer unit                           |

| PWM1             | -            | -                  |                                                          |

| PWM2             |              | P84                |                                                          |

| PWM3             |              | P85                |                                                          |

| PWM4             |              | P66                |                                                          |

| PWM5             |              | P67                |                                                          |

| HASW             | Output       | P82                | Head amplifier switch signal output                      |

| ROTC             | Output       | P83                | Chroma rotation signal output                            |

| ENV              | Input        | P90                | Envelope signal input                                    |

| SI1              | Input        | P63                | Serial data input (serial interface channel 1)           |

| SO1              | Output       | P62                | Serial data output (serial interface channel 1)          |

| SCK1             | I/O          | P61/BUZ            | Serial clock I/O (serial interface channel 1)            |

| SI2              | Input        | BUSY               | Serial data input (serial interface channel 2)           |

| SO2              | Output       | -                  | Serial data output (serial interface channel 2)          |

| SCK2             | I/O          | _                  | Serial clock I/O (serial interface channel 2)            |

| BUSY             | Input        | SI2                | Serial busy signal input (serial interface channel 2)    |

| STRB             | Output       | P60/CLO            | Serial strobe signal output (serial interface channel 2) |

| ANI0 to ANI7     | Analog input | P70 to P77         | Analog signal input of A/D converter                     |

| ANI8 to ANI11    |              | -                  |                                                          |

| CTLIN            | -            | -                  | CTL amplifier input capacitor connection                 |

| CTLOUT1          | Output       | -                  | CTL amplifier output                                     |

| CTLOUT2          | I/O          | -                  | Logic signal input/CTL amplifier output                  |

| RECCTL+, RECCTL- | I/O          | -                  | RECCTL signal output/PBCTL signal input                  |

| CTLDLY           | _            | _                  | External time constant connection (for RECCTL rewriting) |

| VREFC            | _            | -                  | VREF amplifier AC connection                             |

| NMI              | Input        | -                  | Non-maskable interrupt request input                     |

| INTP0 to INTP2   | Input        | -                  | External interrupt request input                         |

| INTP3            | Input        | REELOIN            |                                                          |

| KEY0 to KEY4     | Input        | P91 to P95         | Key input signal input                                   |

| CLO              | Output       | P60/STRB           | Clock output                                             |

| BUZ              | Output       | P61/SCK1           | Buzzer output                                            |

## 2.2 Non-Port Pins (2/2)

| Pin Name     | I/O   | Alternate Function | Function                                             |

|--------------|-------|--------------------|------------------------------------------------------|

| HWIN         | Input | P65                | External input of hardware watch counter             |

| RESET        | Input | -                  | Reset input                                          |

| X1           | Input | -                  | Crystal connection for main system clock oscillation |

| X2           | -     |                    |                                                      |

| XT1          | Input | -                  | Crystal connection for subsystem clock oscillation.  |

| XT2          | -     |                    | Crystal connection for watch clock oscillation       |

| AVdd1, AVdd2 | -     | -                  | Positive power supply to analog circuits             |

| AVss1, AVss2 | -     | -                  | GND of analog circuits                               |

| AVREF        | -     | -                  | Reference voltage input to A/D converter             |

| Vdd          | -     | -                  | Positive power supply to digital circuits            |

| Vss          | -     | -                  | GND of digital circuits                              |

| IC           | -     | -                  | Internally connected. Directly connect to Vss.       |

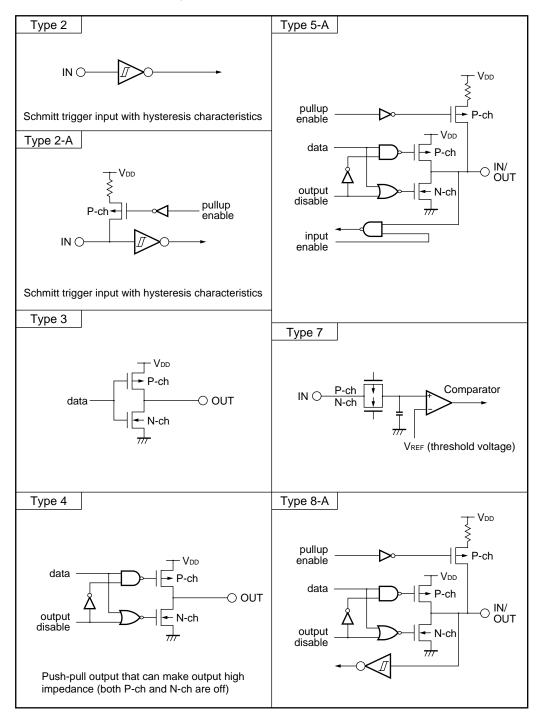

#### 2.3 I/O Circuits and Connection of Unused Pins

Table 2-1 shows the I/O circuit type of each pin and the recommended connection of unused pins. For the configuration of each type of I/O circuit, refer to Figure 2-1.

| Table 2-1. I/O Circuit Type of each Pin and Recommende | d Connection of Unused Pins (1/2) |

|--------------------------------------------------------|-----------------------------------|

|--------------------------------------------------------|-----------------------------------|

| Pin                  | I/O Circuit Type | I/O    | Recommended Connection of Unused Pins                               |

|----------------------|------------------|--------|---------------------------------------------------------------------|

| P00 to P07           | 5-A              | I/O    | Input: Connect to VDD                                               |

| P40 to P47           |                  |        | Output: Leave open                                                  |

| P50 to P57           |                  |        |                                                                     |

| P60/STRB/CLO         |                  |        |                                                                     |

| P61/SCK1/BUZ         | 8-A              | ]      |                                                                     |

| P62/SO1              | 5-A              | ]      |                                                                     |

| P63/SI1              | 8-A              | 1      |                                                                     |

| P64                  | 5-A              | 1      |                                                                     |

| P65/HWIN             | 8-A              | ]      |                                                                     |

| P66/PWM4             | 5-A              | ]      |                                                                     |

| P67/PWM5             |                  |        |                                                                     |

| P70/ANI0 to P77/ANI7 | 9                | Input  | Connect to Vss                                                      |

| P80                  | 5-A              | I/O    | Input: Connect to VDD                                               |

| P82/HASW             |                  |        | Output: Leave open                                                  |

| P83/ROTC             |                  |        |                                                                     |

| P84/PWM2             |                  |        |                                                                     |

| P85/PWM3             |                  |        |                                                                     |

| P86/PTO10            |                  |        |                                                                     |

| P87/PTO11            |                  |        |                                                                     |

| P90/ENV              |                  |        |                                                                     |

| P91/KEY0 to P95/KEY4 | 8-A              | ]      |                                                                     |

| P96                  | 5-A              |        |                                                                     |

| SI2/BUSY             | 2-A              | Input  | Connect to VDD                                                      |

| SO2                  | 4                | Output | Hi-Z: Connect to Vss via a pull-down resistor<br>Others: Leave open |

| SCK2                 | 8-A              | I/O    | Input: Connect to VDD<br>Output: Leave open                         |

| ANI8 to ANI11        | 7                | Input  | Connect to Vss                                                      |

| RECCTL+, RECCTL-     | _                | I/O    | When ENCTL = 0 and ENREC = 0: Connect to Vss                        |

Remark ENCTL : bit 1 of amplifier control register (AMPC)

ENREC: bit 7 of amplifier mode register 0 (AMPM0)

#### Table 2-1. I/O Circuit Type of each Pin and Recommended Connection of Unused Pins (2/2)

| Pin                    | I/O Circuit Type | I/O    | Recommended Connection of Unused Pins                                       |

|------------------------|------------------|--------|-----------------------------------------------------------------------------|

| DFGIN                  | —                | Input  | When ENDRUM = 0: Connect to Vss                                             |

| DPGIN                  |                  |        | When ENDRUM = 0 or ENDRUM = 1 and SELPGSEPA<br>= 0: Connect to Vss          |

| CFGIN, CFGCPIN         |                  |        | When ENCAP = 0: Connect to Vss                                              |

| CSYNCIN                |                  |        | When ENCSYN = 0: Connect to Vss                                             |

| REEL0IN/INTP3, REEL1IN |                  |        | When ENREEL = 0: Connect to Vss                                             |

| CTLOUT1                | -                | Output | Leave open                                                                  |

| CTLOUT2                | _                | I/O    | When ENCTL = 0 and ENCOMP = 0: Connect to Vss<br>When ENCTL = 1: Leave open |

| CFGAMPO                | —                | Output | Leave open                                                                  |

| CTLIN                  |                  | _      | When ENCTL = 0: Leave open                                                  |

| VREFC                  |                  |        | When ENCTL = 0 and ENCAP = 0 and ENCOMP = 0:<br>Leave open                  |

| CTLDLY                 |                  |        | Leave open                                                                  |

| PWM0, PWM1             | 3                | Output | Leave open                                                                  |

| PTO00 to PTO02         |                  |        |                                                                             |

| NMI                    | 2                | Input  | Connect to VDD                                                              |

| INTP0                  |                  |        | Connect to VDD or Vss                                                       |

| INTP1, INTP2           | 2-A              | Input  | Connect to VDD                                                              |

| AVdd1, AVdd2           | —                | _      | Connect to VDD                                                              |

| AVREF, AVSS1, AVSS2    |                  |        | Connect to Vss                                                              |

| RESET                  | 2                |        |                                                                             |

| XT1                    | _                |        | Connect to Vss                                                              |

| XT2                    |                  |        | Leave open                                                                  |

| IC                     |                  |        | Directly connect to Vss                                                     |

RemarkENDRUM: bit 2 of amplifier control register (AMPC)SELPGSEPA:bit 2 of amplifier mode register 0 (AMPM0)ENCAP: bit 3 of amplifier control register (AMPC)ENCSYN: bit 5 of amplifier control register (AMPC)ENREEL: bit 6 of amplifier control register (AMPC)ENCTL: bit 1 of amplifier control register (AMPC)ENCOMP: bit 4 of amplifier control register (AMPC)

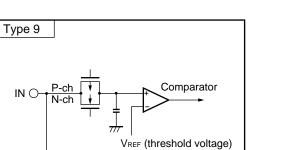

#### Figure 2-1. I/O Circuits of Pins (1/2)

- input enable

Figure 2-1. I/O Circuits of Pins (2/2)

#### 3. INTERNAL BLOCK FUNCTIONS

#### 3.1 CPU Registers

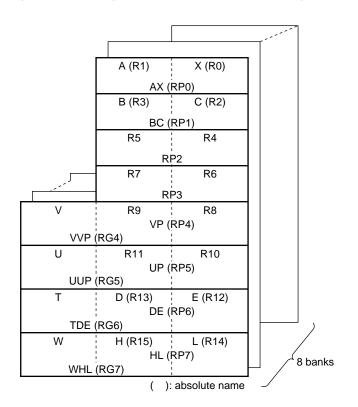

#### 3.1.1 General-purpose registers

The  $\mu$ PD784916B has eight banks of general-purpose registers. One bank consists of sixteen 8-bit generalpurpose registers. Two of these 8-bit registers can be used in pairs as a 16-bit register. Four of the 16-bit generalpurpose registers can be used to specify a 24-bit address in combination with an 8-bit address expansion register.

These eight banks of general-purpose registers can be selected by software or context switching function.

The general-purpose registers, except for the address expansion registers V, U, T, and W, are mapped to the internal RAM.

Figure 3-1. Configuration of General-Purpose Registers

Caution Although R4, R5, R6, R7, RP2, and RP3 can be used as X, A, C, B, AX, and BC registers, respectively, by setting the RSS bit of PSW to 1, do not use this function. The function of the RSS bit is planned to be deleted from the future models in the 78K/IV Series.

#### 3.1.2 Other CPU registers

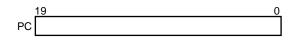

#### (1) Program counter

The program counter of the  $\mu$ PD784916B is 20 bits wide. The value of the program counter is automatically updated as the program is executed.

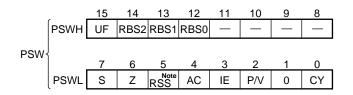

#### (2) Program status word

This is a register that holds the various statuses of the CPU. Its contents are automatically updated as the program is executed.

**Note** The RSS flag is provided to maintain compatibility with the microcontrollers in the 78K/III Series. Always set this flag to 0 except when the software of the 78K/III Series is used.

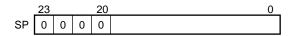

#### (3) Stack pointer

This is a 24-bit pointer that holds the first address of the stack. Be sure to write 0 to the high-order 4 bits.

#### 3.2 Memory Space

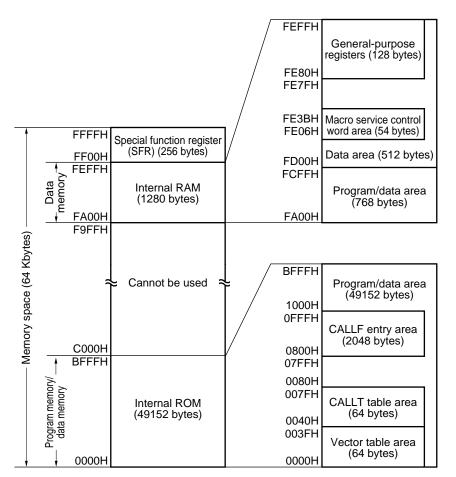

The  $\mu$ PD784916B can access a 64 Kbyte memory space.

Table 3-1 shows the addresses of the internal ROM and internal data areas.

| Table 3-1. | Memory | Space |

|------------|--------|-------|

|------------|--------|-------|

| Part Number | Internal ROM Area | Internal Data Area |

|-------------|-------------------|--------------------|

| μPD784915B  | 0000H-BFFFH       | FA00H-FFFFH        |

| μPD784916B  | 0000H-F7FFH       |                    |

Caution Some products in the 78K/IV Series can access up to 1 Mbyte of memory space in an address expansion mode which is set by the LOCATION instruction. However, the memory space of the  $\mu$ PD784916B is 64 Kbytes (0000H to FFFFH). Therefore, be sure to execute the LOCATION 0 instruction immediately after reset to set the memory space to 64 Kbytes (the LOCATION instruction cannot be used more than twice).

FEFFH General-purpose registers (128 bytes) FE80H FE7FH Macro service control word area (54 bytes) FE3BH FE06H FFFFH Special function register (SFR) (256 bytes) Data area (512 bytes) FF00H FD00H \_\_\_\_\_\_ \_\_\_\_\_\_\_\_\_\_\_ FEFFH FCFFH Internal RAM Program/data area (768 bytes) (1280 bytes) FA00H FA00H F9FFH Memory space (64 Kbytes) Cannot be used F800H F7FFH F7FFH Program/data area (63488 bytes) 1000H **OFFFH** Program memory/ data memory CALLF entry area (2048 bytes) Internal ROM 0800H (63488 bytes) 07FFH 0080H 007FH CALLT table area (64 bytes) 0040H 003FH Vector table area (64 bytes) 0000H 0000H

Figure 3-3. Memory Map of  $\mu \text{PD784916B}$

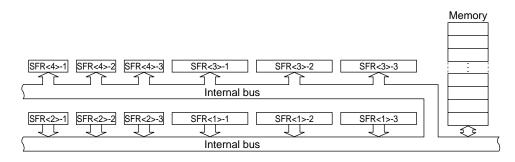

#### 3.3 Special Function Registers (SFRs)

Special function registers are assigned special functions and mapped to a 256-byte space from addresses FF00H through FFFFH. These registers include mode registers and control registers that control the internal peripheral hardware units.

# Caution Do not access an address to which no SFR is assigned. If such an address is accessed by mistake, the $\mu$ PD784916B may be deadlocked. This deadlock can be cleared only by reset input.

Table 3-2 lists the special function registers (SFRs). The meanings of the symbols in this table are as follows:

- R/W ...... Indicates whether the SFR in question can be read or written.

- R/W: Read/write

- R : Read only

- W : Write only

- Bit length ...... Indicates the bit length (word length) of the SFR.

- Bit units for manipulation ...... Indicates bit units in which the SFR in question can be manipulated. An SFR that can be manipulated in 16-bit units can be described as the operand sfrp of an instruction. Specify an even address to manipulate this SFR.

An SFR that can be manipulated in 1-bit units can be described for a bit manipulation instruction.

- After reset ...... Indicates the status of each register after the RESET signal has been input.

|         |                                          |        |     | Bit    | В            | Bit Units for |              | After        |

|---------|------------------------------------------|--------|-----|--------|--------------|---------------|--------------|--------------|

| Address | Special Function Register (SFR) Name     | Symbol | R/W | Length | Manipulation |               | on           | Releasing    |

|         |                                          |        |     |        | 1 bit        | 8 bits        | 16 bits      | Reset        |

| FF00H   | Port 0                                   | P0     | R/W | 8      |              | $\checkmark$  | -            | Undefined    |

| FF04H   | Port 4                                   | P4     |     | 8      | $\checkmark$ | $\checkmark$  | -            |              |

| FF05H   | Port 5                                   | P5     |     | 8      |              | $\checkmark$  | -            |              |

| FF06H   | Port 6                                   | P6     |     | 8      | $\checkmark$ | $\checkmark$  | -            |              |

| FF07H   | Port 7                                   | P7     | R   | 8      | $\checkmark$ | $\checkmark$  | -            |              |

| FF08H   | Port 8                                   | P8     | R/W | 8      | $\checkmark$ | $\checkmark$  | -            |              |

| FF09H   | Port 9                                   | P9     |     | 8      | $\checkmark$ | $\checkmark$  | -            |              |

| FF0EH   | Port 0 buffer register L                 | POL    |     | 8      |              | $\checkmark$  | -            |              |

| FF0FH   | Port 0 buffer register H                 | P0H    |     | 8      | V            |               | -            |              |

| FF10H   | Timer 0 compare register 0               | CR00   |     | 16     | -            | -             | V            | Cleared to 0 |

| FF11H   | Event counter compare register 0         | ECC0   | W   | 8      | -            |               | -            |              |

| FF12H   | Timer 0 compare register 1               | CR01   | R/W | 16     | -            | -             | $\checkmark$ |              |

| FF13H   | Event counter compare register 1         | ECC1   | W   | 8      | -            |               | -            |              |

| FF14H   | Timer 0 compare register 2               | CR02   | R/W | 16     | -            | -             | $\checkmark$ |              |

| FF15H   | Event counter compare register 2         | ECC2   | W   | 8      | -            |               | -            |              |

| FF16H   | Timer 1 compare register 0               | CR10   | R/W | 16     | -            | -             | $\checkmark$ |              |

| FF17H   | Event counter compare register 3         | ECC3   | W   | 8      | -            |               | -            |              |

| FF18H   | Timer 1 compare register 1               | CR11   | R/W | 16     | -            | -             | V            |              |

| FF1AH   | Timer 1 compare register 2               | CR12   | R   | 16     | -            | -             | $\checkmark$ |              |

| FF1CH   | Timer 1 compare register 3               | CR13   | R/W | 16     | -            | -             | $\checkmark$ |              |

| FF1EH   | Timer 2 compare register 0               | CR20   |     | 16     | -            | -             | $\checkmark$ |              |

| FF20H   | Port 0 mode register                     | PM0    | W   | 8      | -            | $\checkmark$  | -            | FFH          |

| FF24H   | Port 4 mode register                     | PM4    |     | 8      | -            |               | -            |              |

| FF25H   | Port 5 mode register                     | PM5    |     | 8      | -            | $\checkmark$  | -            |              |

| FF26H   | Port 6 mode register                     | PM6    |     | 8      | -            | $\checkmark$  | -            |              |

| FF28H   | Port 8 mode register                     | PM8    |     | 8      | -            |               | -            | FDH          |

| FF29H   | Port 9 mode register                     | PM9    |     | 8      | -            | $\checkmark$  | -            | 7FH          |

| FF2EH   | Real-time output port 0 control register | RTPC   | R/W | 8      | $\checkmark$ | $\checkmark$  | -            | 00H          |

| FF30H   | Timer register 0                         | TM0    | R   | 16     | -            | -             | $\checkmark$ | Cleared to 0 |

| FF31H   | Event counter                            | EC     | R/W | 8      | -            | $\checkmark$  | -            |              |

| FF32H   | Timer register 1                         | TM1    | R   | 16     | -            | -             | V            |              |

| FF34H   | Free running counter (bits 0 to 15)      | FRCL   |     | 16     | _            | -             | $\checkmark$ | 0000H        |

| FF35H   | Free running counter (bits 16 to 21)     | FRCH   |     | 8      | _            | $\checkmark$  | -            | 00H          |

| FF36H   | Timer register 2                         | TM2    |     | 16     | -            | -             | $\checkmark$ | Cleared to 0 |

| FF38H   | Timer control register 0                 | TMC0   | R/W | 8      | $\checkmark$ | $\checkmark$  | -            | 00H          |

| FF39H   | Timer control register 1                 | TMC1   |     | 8      | $\checkmark$ |               | _            |              |

| FF3AH   | Timer control register 2                 | TMC2   |     | 8      | $\checkmark$ | $\checkmark$  | -            |              |

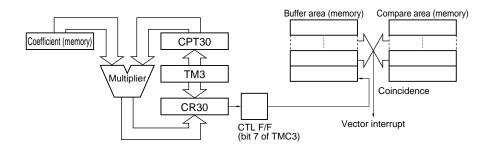

| FF3BH   | Timer control register 3                 | TMC3   |     | 8      | $\checkmark$ | $\checkmark$  | -            | 00×00000     |

| Table 3-2. Special | Function | Registers | (1/4) |

|--------------------|----------|-----------|-------|

|--------------------|----------|-----------|-------|

**Remark** Cleared to 0: Counter is initialized to 0 within 16 clocks after the reset signal has been deasserted (the contents before initialization are undefined).

|         |                                      |                        |     | Bit    | В            | it Units f   | or           | After        |

|---------|--------------------------------------|------------------------|-----|--------|--------------|--------------|--------------|--------------|

| Address | Special Function Register (SFR) Name | Symbol                 | R/W | Length | М            | anipulati    | on           | Releasing    |

|         |                                      |                        |     |        | 1 bit        | 8 bits       | 16 bits      | Reset        |

| FF3CH   | Timer register 3                     | TM3                    | R   | 16     | -            | -            | $\checkmark$ | Cleared to 0 |

| FF3DH   | Timer control register 4             | TMC4                   | R/W | 8      | $\checkmark$ | $\checkmark$ | -            | ××000000     |

| FF3EH   | Timer register 4                     | TM4                    | R   | 16     | -            | -            | $\checkmark$ | Cleared to 0 |

| FF48H   | Port 8 mode control register         | PMC8                   | R/W | 8      | $\checkmark$ | $\checkmark$ | -            | 00H          |

| FF4DH   | Trigger source select register       | TRGS0                  |     | 8      | $\checkmark$ | $\checkmark$ | -            |              |

| FF4EH   | Pull-up resistor option register L   | PUOL                   | ]   | 8      | $\checkmark$ | $\checkmark$ | -            |              |

| FF4FH   | Pull-up resistor option register H   | PUOH                   |     | 8      | $\checkmark$ | $\checkmark$ | -            |              |

| FF50H   | Input control register               | ICR                    |     | 8      | $\checkmark$ | $\checkmark$ | -            | 10H          |

| FF51H   | Up/down counter count register       | UDC                    | 1   | 8      | -            | $\checkmark$ | -            | Undefined    |

| FF52H   | Event divider counter                | EDV                    | R   | 8      | -            | $\checkmark$ | -            | Cleared to 0 |

| FF53H   | Capture mode register                | CPTM                   | R/W | 8      | $\checkmark$ | $\checkmark$ | -            | 00H          |

| FF54H   | Timer register 5                     | TM5                    | R   | 16     | -            | -            | $\checkmark$ | Cleared to 0 |

| FF56H   | Timer 3 capture register 0           | CPT30                  |     | 16     | -            | -            | $\checkmark$ |              |

| FF58H   | Timer 0 output mode register         | TOM0                   | W   | 8      | -            | $\checkmark$ | -            | ××000000     |

| FF59H   | Timer 0 output control register      | TOC0                   |     | 8      | -            | $\checkmark$ | -            | 00H          |

| FF5AH   | Timer 1 output mode register         | TOM1 <sup>Note 1</sup> | R/W | 8      | -            | $\checkmark$ | -            | 80H          |

| FF5BH   | Timer 1 output control register      | TOC1                   | W   | 8      | -            | $\checkmark$ | -            | 00H          |

| FF5CH   | Timer 3 compare register 0           | CR30                   | R/W | 16     | -            | -            | $\checkmark$ | Cleared to 0 |

| FF5EH   | Timer 3 compare register 1           | CR31                   | 1   | 16     | -            | -            | $\checkmark$ |              |

| FF60H   | Port 8 buffer register L             | P8L                    |     | 8      | $\checkmark$ | $\checkmark$ | -            | 000×0×0×     |

| FF63H   | Up/down counter compare register     | UDCC                   | W   | 8      | -            | $\checkmark$ | -            | Undefined    |

| FF65H   | Trigger source select register 1     | TRGS1                  | R/W | 8      | $\checkmark$ | $\checkmark$ | -            | 00H          |

| FF66H   | Port 6 mode control register         | PMC6                   |     | 8      | $\checkmark$ | $\checkmark$ | -            |              |

| FF68H   | A/D converter mode register          | ADM                    | ]   | 16     | -            | -            | $\checkmark$ | 0000H        |

|         |                                      | ADMLNote 2             |     | 8      | $\checkmark$ | $\checkmark$ | -            |              |

| FF6AH   | A/D conversion result register       | ADCR                   | R   | 8      | -            | $\checkmark$ | -            | Undefined    |

| FF6CH   | Hardware watch counter 0             | HW0                    | R/W | 16     | -            | -            | $\checkmark$ | Not affected |

| FF6EH   | Hardware watch counter 1             | HW1                    | R   | 16     | -            | -            | $\checkmark$ | by reset     |

| FF6FH   | Watch mode register                  | WM                     | R/W | 8      | $\checkmark$ | $\checkmark$ | -            | 00××0×00     |

| FF70H   | PWM control register 0               | PWMC0                  | R/W | 8      | $\checkmark$ | $\checkmark$ | -            | 05H          |

| FF71H   | PWM control register 1               | PWMC1                  |     | 8      | $\checkmark$ | $\checkmark$ | -            | 15H          |

| FF72H   | PWM0 modulo register                 | PWM0                   |     | 16     | -            | -            | $\checkmark$ | 0000H        |

| FF73H   | PWM2 modulo register                 | PWM2                   | ]   | 8      | I            | $\checkmark$ | -            | 00H          |

| FF74H   | PWM1 modulo register                 | PWM1                   |     | 16     | -            | -            | $\checkmark$ | 0000H        |

| FF75H   | PWM3 modulo register                 | PWM3                   |     | 8      | I            | $\checkmark$ | -            | 00H          |

| Table 3-2. | Special | Function | Registers | (2/4) |

|------------|---------|----------|-----------|-------|

|------------|---------|----------|-----------|-------|

- **Notes 1.** When the timer 1 output mode register (TOM1) is read, the write sequence of the REC driver is read (bits 0 and 1).

- **2.** ADML is the low-order 8 bits of the A/D converter mode register (ADM) and can be manipulated in 1or 8-bit units.

- **Remark** Cleared to 0: Counter is initialized to 0 within 16 clocks after the reset signal has been deasserted (the contents before initialization are undefined).

|         |                                               |       |         |     | Bit    | В            | it Units f   | or           | After        |

|---------|-----------------------------------------------|-------|---------|-----|--------|--------------|--------------|--------------|--------------|

| Address | Special Function Register (SFR) Name          | Sym   | bol     | R/W | Length | Μ            | anipulati    | on           | Releasing    |

|         |                                               |       |         |     |        | 1 bit        | 8 bits       | 16 bits      | Reset        |

| FF76H   | PWM5 modulo register                          | PW    | M5      | R/W | 16     | -            | -            | $\checkmark$ | 0000H        |

| FF77H   | PWM4 modulo register                          | PW    | M4      |     | 8      | -            | $\checkmark$ | -            | 00H          |

| FF78H   | Event divider control register                | ED    | /C      | W   | 8      | -            | $\checkmark$ | -            | 00H          |

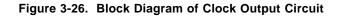

| FF79H   | Clock output mode register                    | CLO   | DM      | R/W | 8      | $\checkmark$ | $\checkmark$ | -            | 00H          |

| FF7AH   | Timer 4 capture/compare register 0            | CR    | 40      |     | 16     | -            | -            | $\checkmark$ | Cleared to 0 |

| FF7BH   | Clock control register                        | C     | C       |     | 8      | $\checkmark$ | $\checkmark$ | -            | 00H          |

| FF7CH   | Timer 4 capture register 1                    | CR    | 41      | R   | 16     | -            | -            | $\checkmark$ | Cleared to 0 |

| FF7DH   | Capture/compare control register              | CR    | С       | W   | 8      | -            | $\checkmark$ | -            | 00H          |

| FF7EH   | Timer 5 compare register                      | CR    | 50      | R/W | 16     | -            | -            | $\checkmark$ | Cleared to 0 |

| FF84H   | Serial mode register 1                        | CSI   | M1      |     | 8      |              | V            | -            | 00H          |

| FF85H   | Serial shift register 1                       | SIC   | D1      |     | 8      | -            | V            | -            | Undefined    |

| FF88H   | Serial mode register 2                        | CSI   | M2      |     | 8      | $\checkmark$ | $\checkmark$ | -            | 00H          |

| FF89H   | Serial shift register 2                       | SIC   | )2      |     | 8      | -            | $\checkmark$ | -            | Undefined    |

| FF8AH   | Serial control register 2                     | CSI   | C2      |     | 8      | -            | $\checkmark$ | -            | 00H          |

| FF91H   | Head amplifier switch output control register | HA    | PC      |     | 8      | $\checkmark$ | $\checkmark$ | -            |              |

| FF94H   | Amplifier control register                    | AM    | PC      |     | 8      | $\checkmark$ | $\checkmark$ | -            |              |

| FF95H   | Amplifier mode register 0                     | AMPM0 |         |     | 8      | $\checkmark$ | $\checkmark$ | -            |              |

| FF96H   | Amplifier mode register 1                     | AMF   | M1      |     | 8      | $\checkmark$ | $\checkmark$ | -            |              |

| FF97H   | Gain control register                         | СТІ   | M       |     | 8      | $\checkmark$ | V            | -            |              |

| FFA0H   | External interrupt mode register              | INT   | M0      |     | 8      | $\checkmark$ | V            | -            | 000000×0     |

| FFA1H   | External capture mode register 1              | INT   | M1      |     | 8      |              | V            | -            | 00H          |

| FFA2H   | External capture mode register 2              | INT   | M2      |     | 8      | $\checkmark$ | V            | -            |              |

| FFA6H   | Key interrupt control register                | KE    | (C      |     | 8      | $\checkmark$ | $\checkmark$ | -            | 70H          |

| FFA8H   | In-service priority register                  | ISF   | ۲R      | R   | 8      | $\checkmark$ | V            | -            | 00H          |

| FFAAH   | Interrupt mode control register               | IM    | С       | R/W | 8      | $\checkmark$ | V            | -            | 80H          |

| FFACH   | Interrupt mask flag register                  | MK0L  | MKO     |     | 8      | $\checkmark$ | V            | $\checkmark$ | FFH          |

| FFADH   |                                               | МКОН  | MK0     |     | 8      |              | V            |              |              |

| FFAEH   |                                               | MK1L  | MK1     |     | 8      | $\checkmark$ | V            | $\checkmark$ |              |

| FFAFH   |                                               | MK1H  | IVITX I |     | 8      | $\checkmark$ | $\checkmark$ |              |              |

| FFB0H   | FRC capture register 0L                       | CP1   | 0L      | R   | 16     | -            | -            | $\checkmark$ | Cleared to 0 |

| FFB1H   | FRC capture register 0H                       | СРТОН |         |     | 8      | -            | V            | -            |              |

| FFB2H   | FRC capture register 1L                       | CPT1L |         |     | 16     | -            | -            | $\checkmark$ |              |

| FFB3H   | FRC capture register 1H                       | CPT1H |         |     | 8      | -            | $\checkmark$ | -            |              |

| FFB4H   | FRC capture register 2L                       | CP1   | 2L      |     | 16     | -            | _            | $\checkmark$ |              |

| FFB5H   | FRC capture register 2H                       | CPT   | 2H      |     | 8      | -            | $\checkmark$ | -            |              |

| FFB6H   | FRC capture register 3L                       | CP1   | '3L     | 1   | 16     | -            | -            | $\checkmark$ |              |

| FFB7H   | FRC capture register 3H                       | CPT   | ЗH      |     | 8      | -            | $\checkmark$ | -            |              |

| FFB8H   | FRC capture register 4L                       | CP1   | 4L      |     | 16     | -            | -            | $\checkmark$ |              |

Table 3-2. Special Function Registers (3/4)

**Remark** Cleared to 0: Counter is initialized to 0 within 16 clocks after the reset signal has been deasserted (the contents before initialization are undefined).

|         |                                                       |        |     | Bit    | Bit Units for |              | or           | After        |

|---------|-------------------------------------------------------|--------|-----|--------|---------------|--------------|--------------|--------------|

| Address | Special Function Register (SFR) Name                  | Symbol | R/W | Length | Manipulation  |              | Releasing    |              |

|         |                                                       |        |     |        | 1 bit         | 8 bits       | 16 bits      | Reset        |

| FFB9H   | FRC capture register 4H                               | CPT4H  | R   | 8      | -             | $\checkmark$ | -            | Cleared to 0 |

| FFBAH   | FRC capture register 5L                               | CPT5L  |     | 16     | -             | -            | $\checkmark$ |              |

| FFBBH   | FRC capture register 5H                               | CPT5H  |     | 8      | -             | $\checkmark$ | -            |              |

| FFC0H   | Standby control register                              | STBC   | R/W | 8      | -             | $\checkmark$ | -            | 0000×0000    |

| FFC4H   | Execution speed select register                       | MM     | W   | 8      | -             | $\checkmark$ | -            | 20H          |

| FFCEH   | CPU clock status register                             | PCS    | R   | 8      | $\checkmark$  | $\checkmark$ | -            | 00H          |

| FFCFH   | Oscillation stabilization time specification register | OSTS   | W   | 8      | -             | $\checkmark$ | -            |              |

| FFE0H   | Interrupt control register (INTP0)                    | PIC0   | R/W | 8      | $\checkmark$  | $\checkmark$ | -            | 43H          |

| FFE1H   | Interrupt control register (INTCPT3)                  | CPTIC3 |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFE2H   | Interrupt control register (INTCPT2)                  | CPTIC2 |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFE3H   | Interrupt control register (INTCR12)                  | CRIC12 |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFE4H   | Interrupt control register (INTCR00)                  | CRIC00 | ]   | 8      |               | $\checkmark$ | -            |              |

| FFE5H   | Interrupt control register (INTCLR1)                  | CLRIC1 | ]   | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFE6H   | Interrupt control register (INTCR10)                  | CRIC10 |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFE7H   | Interrupt control register (INTCR01)                  | CRIC01 |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFE8H   | Interrupt control register (INTCR02)                  | CRIC02 |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFE9H   | Interrupt control register (INTCR11)                  | CRIC11 |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFEAH   | Interrupt control register (INTCPT1)                  | CPTIC1 |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFEBH   | Interrupt control register (INTCR20)                  | CRIC20 |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFEDH   | Interrupt control register (INTTB)                    | TBIC   |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFEEH   | Interrupt control register (INTAD)                    | ADIC   | ]   | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFEFH   | Interrupt control register (INTP2) <sup>Note</sup>    | PIC2   |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

|         | Interrupt control register (INTCR40) <sup>Note</sup>  | CRIC40 | ]   |        |               |              |              |              |

| FFF0H   | Interrupt control register (INTUDC)                   | UDCIC  |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFF1H   | Interrupt control register (INTCR30)                  | CRIC30 |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFF2H   | Interrupt control register (INTCR50)                  | CRIC50 |     | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFF3H   | Interrupt control register (INTCR13)                  | CRIC13 | ]   | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFF4H   | Interrupt control register (INTCSI1)                  | CSIIC1 | 1   | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFF5H   | Interrupt control register (INTW)                     | WIC    | 1   | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFF7H   | Interrupt control register (INTP1)                    | PIC1   | 1   | 8      |               | $\checkmark$ | -            |              |

| FFF8H   | Interrupt control register (INTP3)                    | PIC3   | 1   | 8      | $\checkmark$  | $\checkmark$ | -            |              |

| FFFAH   | Interrupt control register (INTCSI2)                  | CSIIC2 | 1   | 8      |               | $\checkmark$ | -            |              |

#### Table 3-2. Special Function Registers (4/4)

Note PIC2 and CRIC40 are at the same address (register).

**Remark** Cleared to 0: Counter is initialized to 0 within 16 clocks after the reset signal has been deasserted (the contents before initialization are undefined).

#### 3.4 PORTS

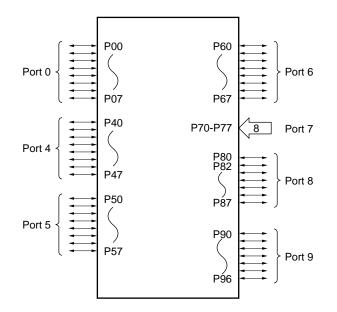

The  $\mu$ PD784916B is provided with the ports shown in Figure 3-4. Table 3-3 shows the function of each port.

| Table | 3-3. | Port | Function |

|-------|------|------|----------|

|-------|------|------|----------|

| Name   | Pin Name        | Function                                 | Specification of Pull-up Resistor      |

|--------|-----------------|------------------------------------------|----------------------------------------|

| Port 0 | P00 to P07      | Can be set in input or output mode in 1- | Pull-up resistors are connected to all |

| Port 4 | P40 to P47      | bit units.                               | pins in input mode.                    |

| Port 5 | P50 to P57      |                                          |                                        |

| Port 6 | P60 to P67      |                                          |                                        |

| Port 7 | P70 to P77      | Input port                               | Pull-up resistor is not provided.      |

| Port 8 | P80, P82 to P87 | Can be set in input or output mode in 1- | Pull-up resistors are connected to all |

| Port 9 | P90 to P96      | bit units.                               | pins in input mode.                    |

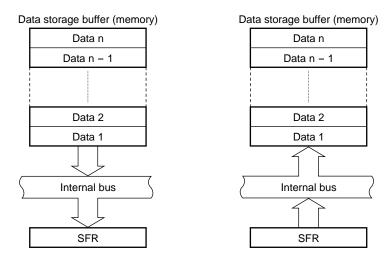

#### 3.5 Real-time Output Port

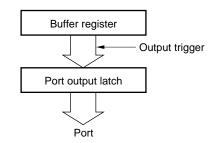

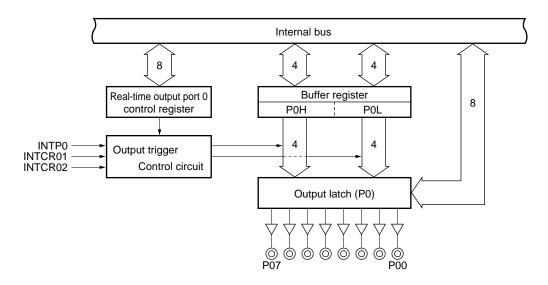

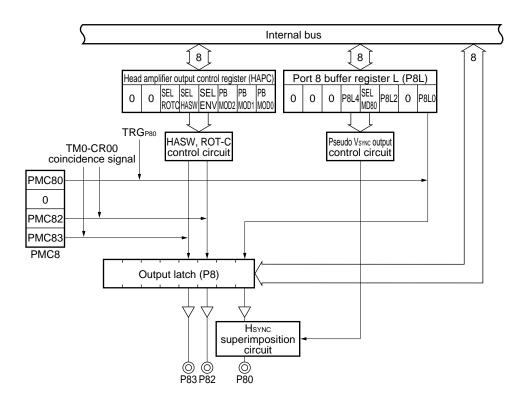

A real-time output port consists of a port output latch and a buffer register (refer to Figure 3-5).

The function to transfer the data prepared in advance in the buffer register to the output latch when a trigger such as a timer interrupt occurs, and output the data to an external device is called a real-time output function. A port used in this way is called a real-time output port (RTP).

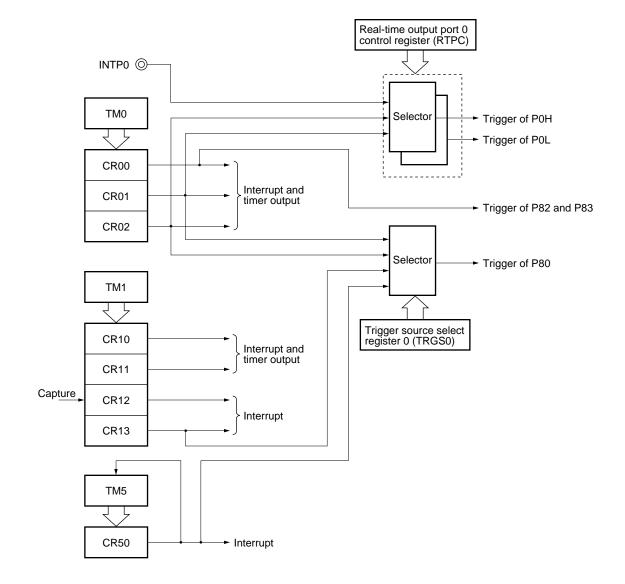

Table 3-4 shows the real-time output ports of the  $\mu$ PD784916B.

Table 3-5 shows the trigger sources of RTPs.

#### Figure 3-5. Configuration of RTP

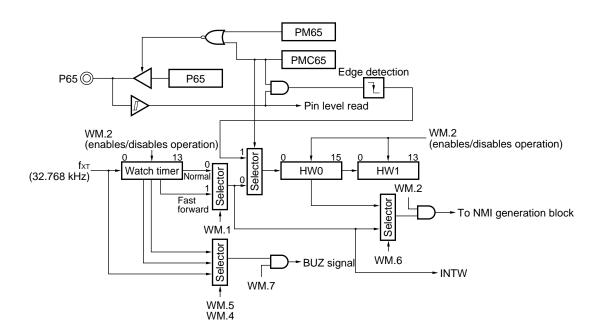

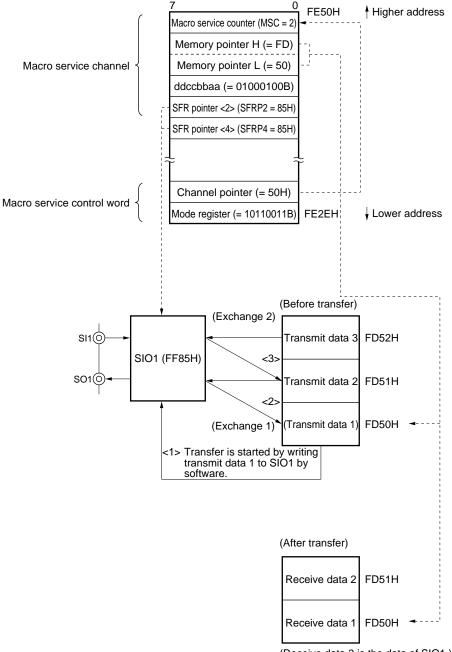

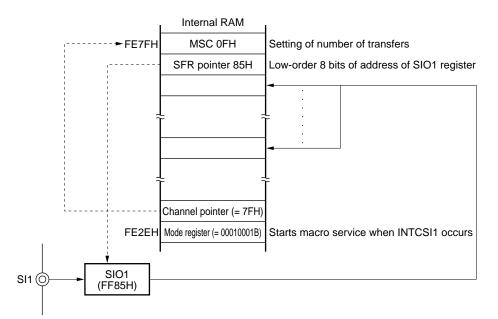

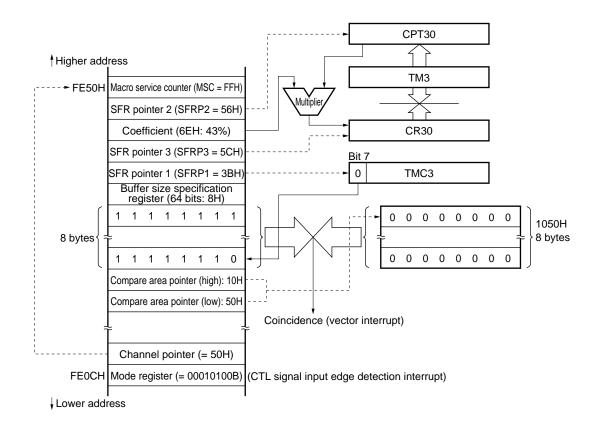

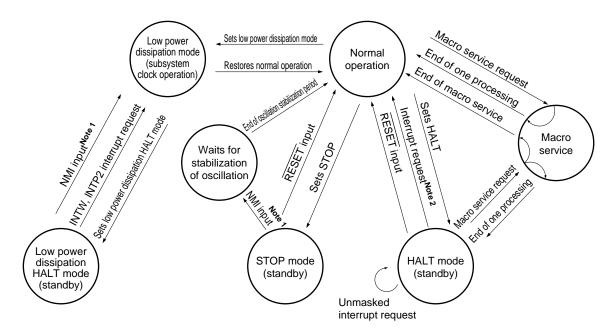

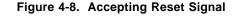

Table 3-4. Bit Configuration of RTP