## **DATA SHEET**

# MOS INTEGRATED CIRCUIT $\mu PD78CP14$

### **8-BIT SINGLE-CHIP MICROCOMPUTER**

The  $\mu PD78CP14$  is a product provided by replacing  $\mu PD78C14$  internal mask ROM with PROM.

$\mu\text{PD78CP14DW/KB/R}$  (for evaluation of  $\mu\text{PD78C11A}$ , 78C12A, 78C14) which is reprogrammable and  $\mu\text{PD78CP14CW/G/GF/L}$  of one time ROM version which is programmable only once (for small production) are provided.

#### Features:

- o Compatible with  $\mu$ PD78C11A, 78C12A, 78C14 (87AD series)

- o PROM programming characteristics:  $\mu$ PD27C256A compatible.

- o Single power supply: 5 V ±10 % (one-time PROM product)

5 V ±5 % (EPROM product)

- o Compatible with  $\mathtt{QTOP}^{TM}$  microcomputer

Remarks The QTOP Microcomputer is the general term for "One-time single-chip microcomputer with on-chip PROM totally supported from program writing to seating, screening, and verification" offered by NEC.

#### Ordering Information

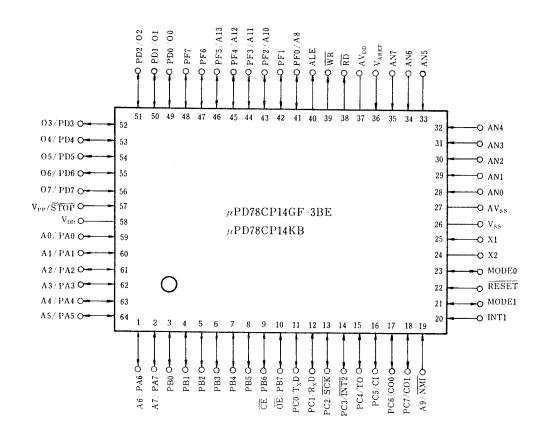

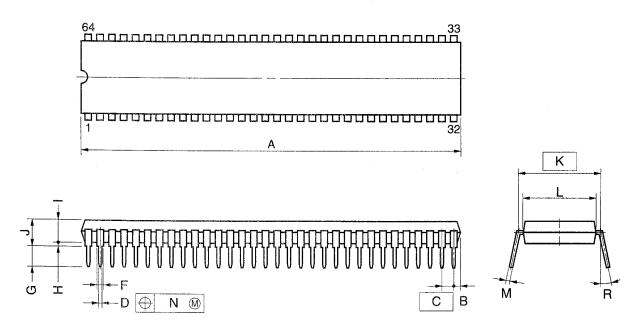

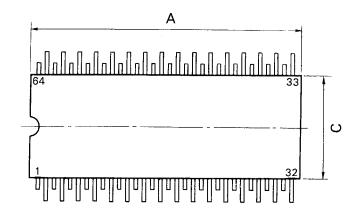

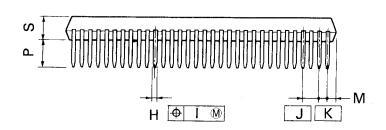

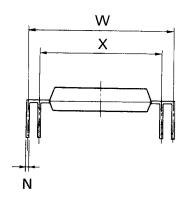

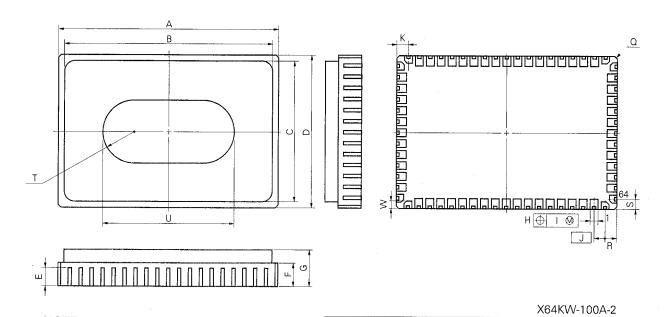

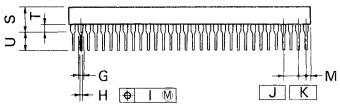

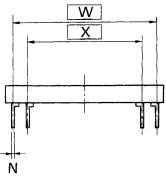

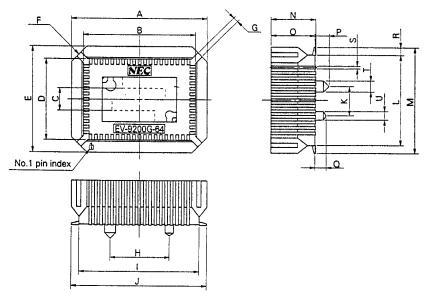

| Part number          | Package                                           | Program memory |

|----------------------|---------------------------------------------------|----------------|

| μPD78CP14CW          | 64-pin plastic shrink DIP (750 mil)               | One-time PROM  |

| $\mu$ PD78CP14G-36   | 64-pin plastic QUIP                               | One-time PROM  |

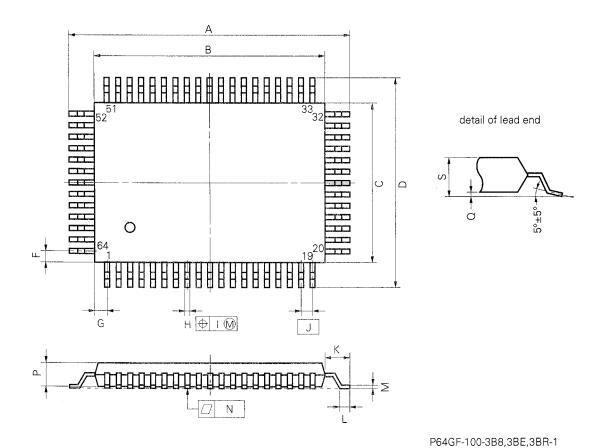

| $\mu$ PD78CP14GF-3BE | 64-pin plastic flat-pack (14 x 20 mm)             | One-time PROM  |

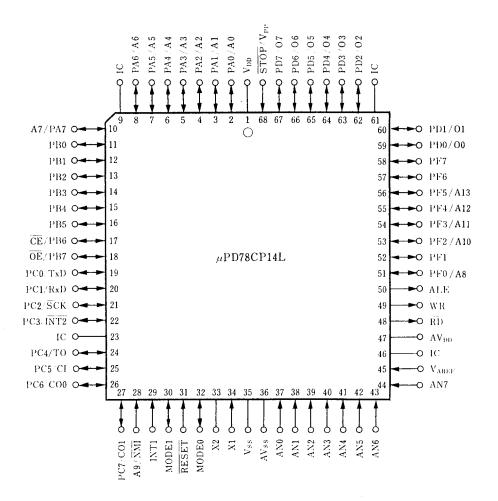

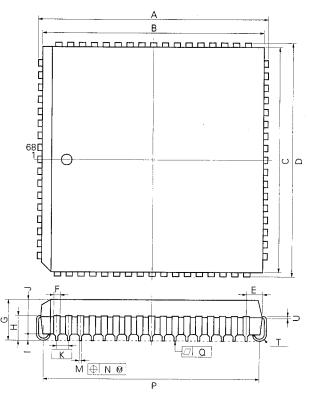

| $\mu$ PD78CP14L      | 68-pin plastic QFJ ( 950 mil)                     | One-time PROM  |

| μPD78CP14DW          | 64-pin ceramic shrink DIP with a window (750 mil) | EPROM          |

| $\mu$ PD78CP14KB     | 64-pin ceramic WQFN                               | EPROM          |

| $\mu$ PD78CP14R      | 64-pin ceramic QUIP with a window                 | EPROM          |

## Quality grade

#### Standard

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

This document represents the portion common to the one-time PROM and EPROM products as PROM.

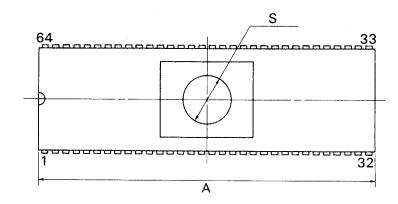

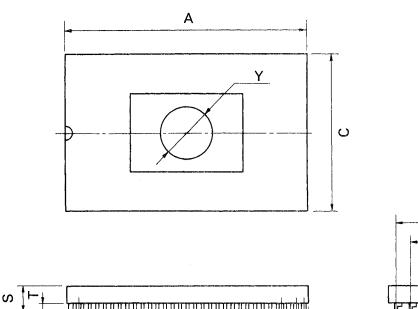

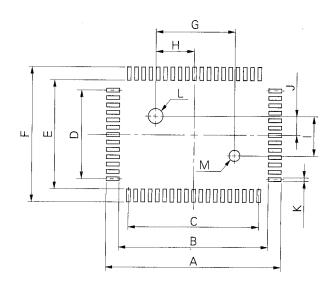

#### Pin Configuration (Top View)

IC .....Internally Connected

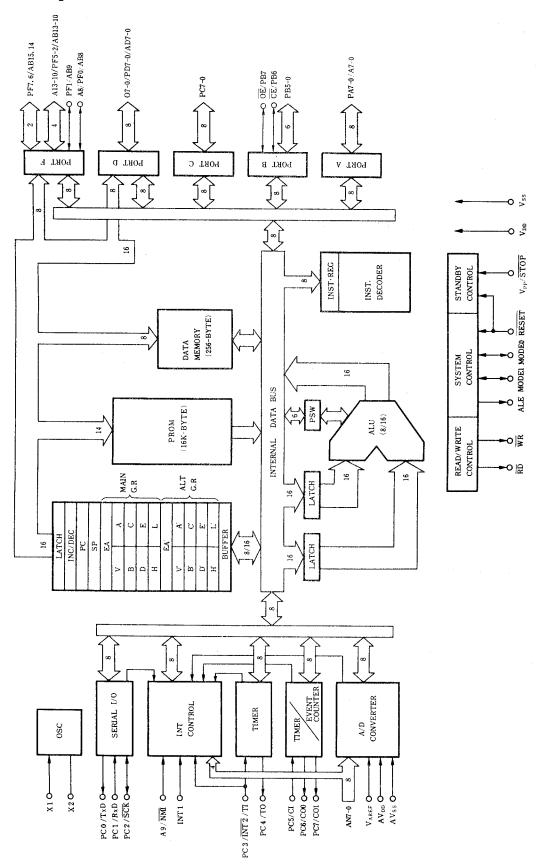

## Block Diagram

#### Contents

|     |                                |                                      |                                       |             | <u>Paqe</u> |

|-----|--------------------------------|--------------------------------------|---------------------------------------|-------------|-------------|

| 1.  | PIN FUNCTION .                 |                                      |                                       |             | 9           |

|     | 1.1 Port Funct                 | ons                                  |                                       |             | 9           |

|     |                                | Other Than Ports<br>rmal Operation)  | · · · · · · · · · · · · · · · · · · · | • • • • • • | 10          |

|     | · -                            | Other Than Ports<br>OM Write, Verify | r, Read)                              | • • • • •   | 12          |

|     | 1.4 Recommende                 | l Conditions for                     | Unused Pin                            | • • • • •   | 13          |

| 2.  | MEMORY CONFIGU                 | RATION                               |                                       | • • • • • • | 14          |

| 3.  | MEMORY EXTENSI                 | ON                                   |                                       | • • • • •   | 18          |

|     | 3.1 MODE Pins                  |                                      |                                       |             | 18          |

|     | 3.2 MEMORY MAP                 | 'ING Register (M                     | M)                                    |             | 19          |

| 4.  | PROM PROGRAMMI                 | ıg                                   |                                       | • • • • •   | 23          |

|     | 4.1 PROM Progra                | umming Operation                     | Mode                                  | • • • • •   | 25          |

|     | 4.2 PROM Write                 | Procedure                            |                                       | • • • • •   | 26          |

|     | 4.3 PROM Read                  | rocedure                             |                                       |             | 27          |

| 5.  | EPROM ERASE (O                 | ILY PACKAGE PROD                     | UCTS WITH CERAMIC WI                  | NDOW).      | 29          |

| 5.  | WINDOW SEAL<br>(ONLY FOR PACK) | GE PRODUCTS WIT                      | H CERAMIC WINDOW)                     | • • • • • • | 30          |

| 7.  | ONE-TIME PROM                  | PRODUCT SCREENIN                     | G                                     |             | 31          |

| 8.  | ELECTRICAL SPE                 | CIFICATIONS                          |                                       |             | 32          |

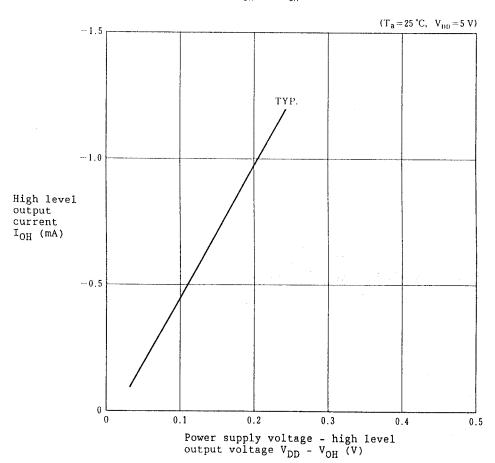

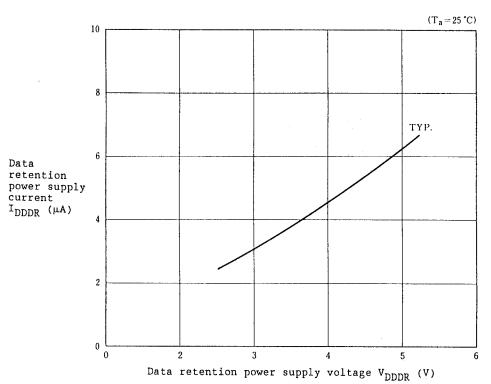

| 9.  | CHARACTERISTIC                 | CURVES (REFEREN                      | CE VALUE)                             | • • • • •   | 51          |

| . ^ | DICENCE INFORM                 | TT ON                                |                                       |             | 54          |

|   |                                                                                                | Page  |

|---|------------------------------------------------------------------------------------------------|-------|

|   | 11. RECOMMENDED CONDITIONS FOR SOLDERING                                                       | 61    |

|   | 12. DIFFERENCES BETWEEN µPD78CP14 AND MASK ROM PRODUCTS                                        | 63    |

|   | APPENDIX A DEVELOPMENT TOOLS                                                                   | 64    |

| * | APPENDIX B PACKAGE INFORMATION OF CONVERSION SOCKETS AND RECOMMENDED PATTERNS FOR BOARD FIXING | • 66° |

#### 1. PIN FUNCTIONS

#### 1.1 Port Functions

| Pin name          | I/O | Function                                                                 |

|-------------------|-----|--------------------------------------------------------------------------|

| PA7-0<br>(Port A) | I/O | 8-bit input/output port. Input or output can be specified for each bit.  |

| PB7-0<br>(Port B) |     |                                                                          |

| PC7-0<br>(Port C) |     |                                                                          |

| PD7-0<br>(Port D) |     | 8-bit input/output port. Input or output can be specified for each byte. |

| PF7-0<br>(Port F) |     | 8-bit input/output port. Input or output can be specified for each bit.  |

Remarks In these port pins, there are dual function pins described in 1.2 (at normal operation) and 1.3 (at PROM writing/verify/reading)

# 1.2 Functions Other Than Ports (During Normal Operation)

| Pin name                           | I/O | Other<br>uses | Function                                                                                                                                                                                                                                        |

|------------------------------------|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxD<br>(Transmit data)             | 0   | PC0           | Serial data output pin.                                                                                                                                                                                                                         |

| RxD<br>(Receive data)              | I   | PC1           | Serial data input pin.                                                                                                                                                                                                                          |

| SCK<br>(serial clock)              | I/O | PC2           | Serial clock input/output pin. When the internal clock is used, this line functions as an output and when an external clock source is used, this line functions as an input.                                                                    |

| INT2<br>(Interrupt<br>request)     | I   | PC3           | Maskable interrupt input (rising-edge triggered.)                                                                                                                                                                                               |

| TI<br>(Timer input)                | I   |               | Timer external clock input pin.                                                                                                                                                                                                                 |

| Zero-cross                         | I   |               | Zero cross detection pin of AC input.                                                                                                                                                                                                           |

| TO (Timer output)                  | 0   | PC4           | Square wave with pulse width of one internal clock cycle for timer count reference used as a half-cycle output.                                                                                                                                 |

| CI<br>(Counter input)              | I   | PC5           | External pulse input pin to timer/event counter.                                                                                                                                                                                                |

| COO, 1<br>(Counter output<br>0, 1  | 0   | PC6,7         | Programmable square wave output according to timer/event counter.                                                                                                                                                                               |

| AD7-0<br>(Address/data<br>bus 7-0) | I/O | PD7-0         | These lines are used as a multiplexed address/data bus with external memory.                                                                                                                                                                    |

| AB15-8<br>(Address bus<br>15-8     | 0   | PF7-0         | These lines are used as an address bus with external memory.                                                                                                                                                                                    |

| WR<br>(Write strobe)               | 0   |               | Store signal output for external memory write operation. This signal is HIGH except during external memory data write cycles. When the RESET signal is LOW or the hardware STOP mode is engaged, this line is placed in a high-impedance state. |

| Pin name                                   | 1/0        | Other<br>uses | Function                                                                                                                                                                                                                                                                   |

|--------------------------------------------|------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD<br>(Read strobe)                        | 0          |               | Strobe signal output for external memory read operation. This signal is HIGH except during external memory read cycles. When the RESET signal is LOW or the hardware STOP mode is engaged, this line is placed in a high-impedance state.                                  |

| ALE (Address latch enable)                 | 0          |               | This line is used for the strobe signal to externally latch the lower-order address on the PD7-PD0 lines for external memory access. When the $\overline{\text{RESET}}$ signal is LOW or the hardware STOP mode is engaged, this line is placed in a high-impedance state. |

| MODEO<br>MODE1<br>(Mode)                   | I/0<br>I/0 |               | Set the MODEO pin to 0 (low level) and the MODE1 pin to 1 (high level) (Note 1.)                                                                                                                                                                                           |

| NMI<br>(Non-maskable<br>interrupt)         | I          |               | Nonmaskable interrupt input (falling-edge triggered).                                                                                                                                                                                                                      |

| INT1<br>(Interrupt<br>request)             | I          |               | Maskable interrupt input (rising-edge triggered.) This line can also be used for AC input zero cross detection.                                                                                                                                                            |

| AN7-0<br>(Analog input)                    | I          |               | 8-line analog input to A/D converter. Lines AN7-AN4 provide edge falling-edge detection input.                                                                                                                                                                             |

| V <sub>AREF</sub> (Reference voltage)      | I          |               | For use as both A/D converter reference voltage and A/D converter operation control.                                                                                                                                                                                       |

| AV <sub>DD</sub> (Analog V <sub>DD</sub> ) |            |               | Power supply line for A/D converter.                                                                                                                                                                                                                                       |

| AV <sub>SS</sub> (Analog V <sub>SS</sub> ) |            |               | GND potential for A/D converter.                                                                                                                                                                                                                                           |

| X1, X2<br>(Crystal)                        |            |               | Crystal-oscillator input for system clock timing. When an external clock source is used, the timing pulses are input on X1. The X1 inversion signal is input to X2.                                                                                                        |

Note Pull up. Pull-up resistance R is 4  $\leq$  R  $\leq$  0.4  $t_{CYC}$  [k\Omega] (t\_{CYC}: ns units)

| Pin name        | I/O | Other<br>uses | Function                                                                                                                         |

|-----------------|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------|

| RESET (Reset)   | I   |               | System reset (active-low) input. Input line for hardware STOP mode control signal. When a low level is input, oscillation stops. |

| STOP<br>(Stop)  | I   |               | Input line for hardware STOP mode control signal. When a low level is input, oscillation stops.                                  |

| V <sub>DD</sub> |     |               | +5 V power supply line.                                                                                                          |

| V <sub>SS</sub> |     |               | GND potential line.                                                                                                              |

## 1.3 Functions Other Than Ports (During PROM Write, Verify, Read)

| Pin name        | I/O | Other<br>uses | Function                                                                |

|-----------------|-----|---------------|-------------------------------------------------------------------------|

| A7-0            | I   | PA7-0         | Low-order eight-bit input pins of address.                              |

| CE              | I   | PB6           | Chip enable signal input pin.                                           |

| ŌĒ              | I   | PB7           | Output enable signal input pin.                                         |

| 07-0            | I/O | PD7-0         | Data input/output pins.                                                 |

| A13-10<br>A8    | I   | PF5-2<br>PF0  | High-order 6-bit input pins address.                                    |

| A9              | I   | NMI           |                                                                         |

| MODEO<br>MODE1  | I   |               | Set the MODEO pin to 1 (high) and the MODE1 pin to 0 (low).             |

| RESET           | I   |               | Set the RESET pin to 0 (low).                                           |

| V <sub>PP</sub> |     | STOP          | High voltage apply pin.<br>When EPROM is read, high level (1) is input. |

## $\star$ Caution Input low level for PF6 during PROM write, verify, read.

## 1.4 Recommended Conditions for Unused Pin

| Pin                                     | Recommended connection                                                |

|-----------------------------------------|-----------------------------------------------------------------------|

| PA7-0<br>B7-0<br>C7-0<br>PD7-0<br>PF7-0 | Connect to $V_{ m DD}$ or $V_{ m SS}$ via resistor.                   |

| RD<br>WR<br>ALE                         | Open                                                                  |

| STOP                                    | Connect to V <sub>DD</sub>                                            |

| INT1, NMI                               | Connect to ${ m V_{DD}}$ or ${ m V_{SS}}$                             |

| av <sub>dd</sub>                        | Connect to V <sub>DD</sub>                                            |

| V <sub>AREF</sub><br>AV <sub>SS</sub>   | Connect to V <sub>SS</sub>                                            |

| AN7-0                                   | Connect to $\mathtt{AV}_{\mathtt{SS}}$ or $\mathtt{AV}_{\mathtt{DD}}$ |

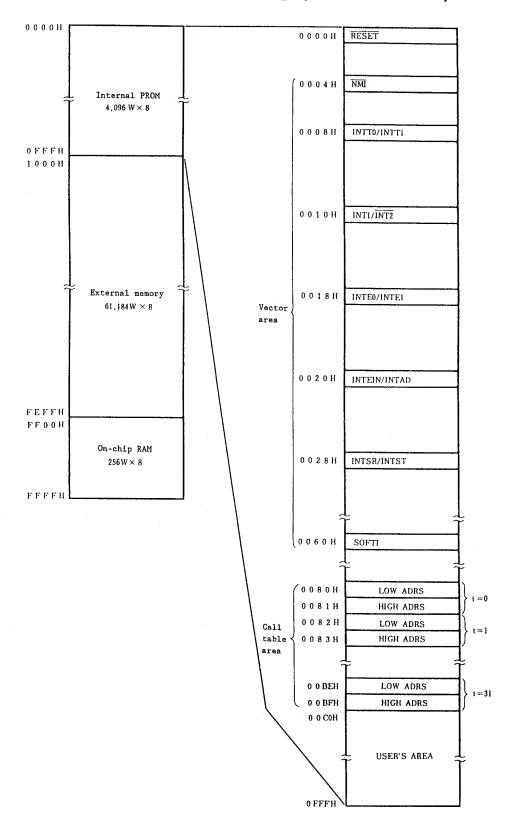

#### 2. MEMORY CONFIGURATION

$\mu PD78CP14$  memory can be operated in any of the following three modes as specified:

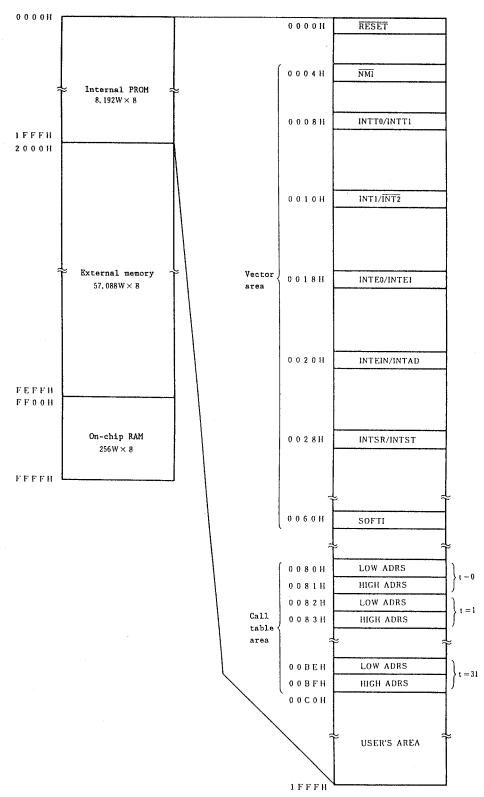

- o  $\mu$ PD78C11A mode (see Figure 2-1)

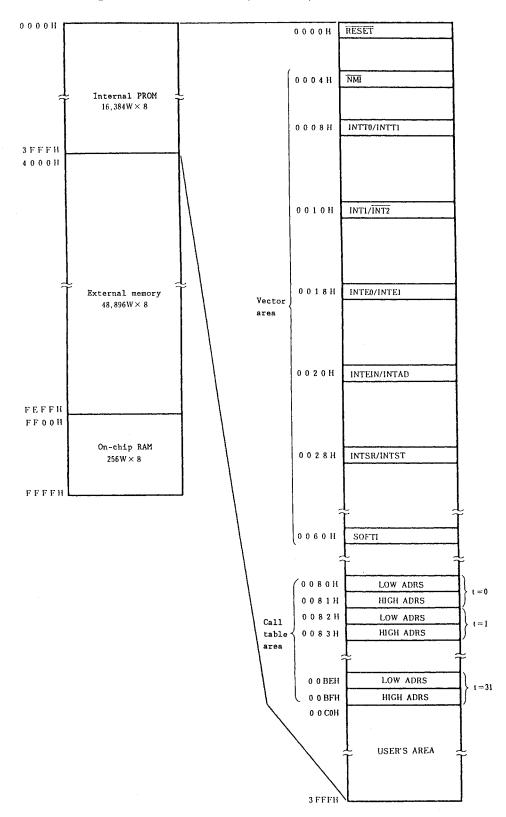

- o  $\mu$ PD78C12A mode (see Figure 2-2)

- o  $\mu PD78C14$  mode (see Figure 2-3)

In addition, the internal PROM address range can be specified to map external memory (except PROM) efficiently (See 3.2).

The vector area, call table area, and internal RAM are common to all the modes.

Internal RAM data can be retained with low consumption current by setting the hardware or software STOP mode or the HALT mode.

Figure 2-1. Memory Map ( $\mu$ PD78C11A Mode)

Figure 2-2. Memory Map ( $\mu$ PD78C12A Mode)

Figure 2-3. Memory Map ( $\mu$ PD78C14 Mode)

#### 3. MEMORY EXTENSION

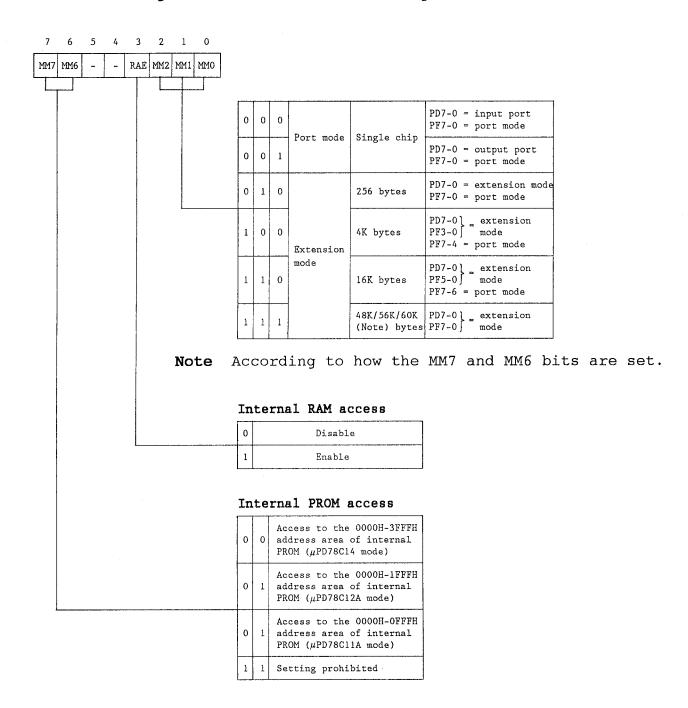

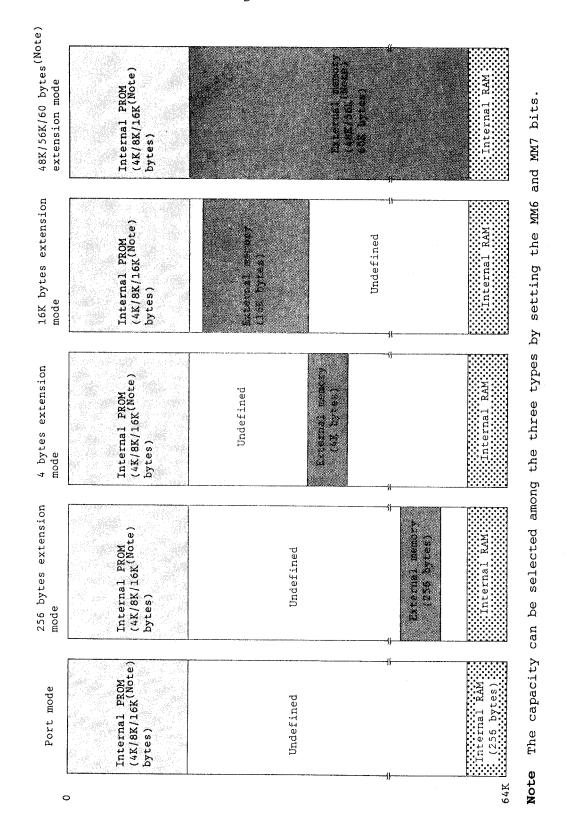

The  $\mu$ PD78CP14 enables external memory extension by using the MEMORY MAPPING register (MM) or the MODE0 and MODE1 pins. The internal PROM access range can be specified by using MEMORY MAPPING register bits 7 and 6.

#### 3.1 MODE Pins

The  $\mu$ PD78CP14 enables the user to change the programming mode and normal operation mode by setting the MODE0 and MODE1 pins.

Table 3-1 lists mode setting by using the MODE pins.

Table 3-1 Mode Setting by Using MODE Pins

| MODE1 | MODE0 | Operation mode          |

|-------|-------|-------------------------|

| L     | L     | Setting prohibted       |

| L     | Н     | Programming mode (Note) |

| Н     | L     | Normal operation mode   |

| Н     | Н     | Setting prohibited      |

Note See 4.

To make the MODE0 and MODE1 pins high, use pull-up registor of  $4 \le R \le 0.4 t_{\rm CYC}[k \text{ ohms}]$  (t<sub>CYC</sub>: ns units).

#### 3.2 MEMORY MAPPING Register (MM)

The MEMORY MAPPING register is an 8-bit register used for the following control:

- PD7-PD0, PF7-PF0 port/extension mode specification.

- Control as to whether or not internal RAM access is enabled.

- Internal PROM access range specification

Figure 3-1 shows the MEMORY MAPPING register format.

#### (1) MMO-MM2 bits

The MM0-MM2 bits are used to PD7-PD0 port/extension mode, input/output, PF7-PF0 address output specification.

As shown in Figure 3-1, the capacity of external memory that can be connected to the  $\mu PD78CP14$  can be selected among the following four types:

- 256 bytes

- 4K bytes

- 16K bytes

- 48K, 56K, or 60K bytes (according to how MM6 and MM7 bits are set)

The PF7-PF0 port pins not used for address output car be used as general purpose port pins.

When  $\overline{\text{RESET}}$  is input or the hardware STOP mode is entered, the bits are cleared and the PD7-PD0 pins are used as an input port (output high impedance).

#### (2) MM3 bit (RAE)

The MM3 bit is used to specify whether internal RAM access is enabled (RAE=1) or not (RAE=0).

When standby operation is performed or external RAM connected is used without using internal RAM, set the MM3 bit to "0".

Even if RESET is input during normal operation, the bit contents are held. However, the RAE bit becomes undefined at power on reset, thus the bit must be initialized by using an instruction.

#### (3) MM6 and MM7 bits

The MM6 and MM7 bits are used to specify the internal PROM access range.

When  $\overline{\text{STOP}}$  or  $\overline{\text{RESET}}$  is input, the MM6 and MM7 bits are cleared and the 16K-byte mode ( $\mu\text{PD78C14}$  mode) is selected.

The bits are effective only for the  $\mu\text{PD78CP14}$  and 78CG14. When data is written into the bits on the  $\mu\text{PD78C11A}$ , 78C12A/14, or 78C14 the CPU ignores it. Therefore, the programs developed on the  $\mu\text{PD78CP14}$  can be moved to mask ROM as they are.

Figure 3-1. MEMORY MAPPING Register Format

Figure 3-2. External Extension Mode Set by Using MEMORY MAPPING Register

#### 4. PROM PROGRAMMING

The  $\mu$ PD78CP14 contains 16384 x 8 bit PROM for internal program memory. Table 4-1 lists the pins used to write and verify the PROM.

The  $\mu\,\text{PD78CP14}$  programming timing is compatible with the  $\mu\,\text{PD27C256A}$  programming timing.

Also refer to the  $\mu PD27C256A$  documents.

Table 4-1. Pin Functions in PROM Programming

|                      | <u> </u>                                                                 |

|----------------------|--------------------------------------------------------------------------|

| Pin name             | Function                                                                 |

| RESET                | Low level input (during write/verify, read)                              |

| MODE0                | High level input (during write/verify, read)                             |

| MODE1                | Low level input (during write/verify, read)                              |

| PF6                  | Low level input (during write/verify, read)                              |

| V <sub>PP</sub> Note | High voltage input (during write/verify), high level input (during read) |

| CENote               | Chip enable input                                                        |

| <u> </u>             | Output enable input                                                      |

|                      | Address input                                                            |

| Note                 | Data input (during write, data output (during verify/read)               |

| V <sub>DD</sub> Note | Supply voltage input                                                     |

Note These pins are compatible with the  $\mu$ PD27C256A pins.

Cautions 1. Cover the  $\mu PD78CP14$  containing an erasion window with shading cover film except in EPROM erasion.

- 2. The  $\mu\text{PD78CP14}$  of one time PROM product which does not contain an erasion window cannot be erased with ultraviolet rays.

- 3. The  $\mu PD78CP14$  does not contain memory at 4000H-7FFFH.

If read operation is performed, FFH is always read.

To program in the  $\mu$ PD27C256A,

- (1) set PROM programmer 4000H-7FFFH buffer to all FFH; or

- (2) program the ROM 0000H-3FFFH area only.

#### 4.1 PROM Programming Operation Mode

The PROM programming operation mode is set as listed in Table 4-2. At the time, treat every pin not used for programming as listed in Table 4-3.

Table 4-2. EPROM Programming Mode

| Operation mode  | (N <u>ot</u> e)<br>CE | (N <u>ot</u> e)<br>OE | (Note)<br>V <sub>PP</sub> | (Note)<br>V <sub>DD</sub> | RESET | MODEO | MODE1 | PF6 |

|-----------------|-----------------------|-----------------------|---------------------------|---------------------------|-------|-------|-------|-----|

| Program         | Ļ                     | Н                     |                           |                           |       |       |       |     |

| Program verify  | Н                     | L                     | +12.5 V                   | +6 V                      | L     | Н     | L     | L   |

| Program inhibit | Н                     | Н                     |                           |                           |       |       |       |     |

| Read            | L                     | L                     |                           |                           |       |       |       |     |

| Output disable  | L                     | Н                     | +5 V                      | +5 V                      |       |       |       |     |

| Standby         | Н                     | L/H                   |                           |                           |       |       |       |     |

Note These pins are compatible with the  $\mu$ PD27C256A pins.

Caution When  $V_{PP}$  is set to +12.5 V and  $V_{DD}$  is set to +6 V, both  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  must not be set L simultaneously.

Table 4-3. Recommended Conditions for Unused Pins (in PROM programming mode)

| Pin               | Recommended connection method                       |  |  |  |

|-------------------|-----------------------------------------------------|--|--|--|

| INT1              |                                                     |  |  |  |

| X1                |                                                     |  |  |  |

| AN0-7             | Connect to V <sub>SS</sub>                          |  |  |  |

| VA <sub>REF</sub> | Connect to VSS                                      |  |  |  |

| AV <sub>DD</sub>  |                                                     |  |  |  |

| AV <sub>SS</sub>  |                                                     |  |  |  |

| Pins except above | Connect each pin via a resistor to ${ m V}_{ m SS}$ |  |  |  |

| X2                | Open                                                |  |  |  |

#### 4.2 PROM Write Procedure

Data is written into PROM according to the following procedure: (High speed write is enabled.)

- (1) Pull down unused pins to  $V_{\rm SS}$  via a resistor and supply +6 V to  $V_{\rm DD}$  and +12.5 V to  $V_{\rm pp}$ .

- (2) Supply initial address.

- (3) Supply write data.

- (4) Supply 1 ms program pulse (active low) to the CE pin.

- (5) Verify mode. If data is written, proceed to (7). If data is not written, repeat (3) to (5). If data cannot be written after the steps are repeated 25 times, proceed to (6).

- (6) Judge that the EPROM is a faulty device. Stop write operation.

- (7) Supply write data. Supply X (number of (3)-(5) repetitions) x 3 ms program pulse (additional write).

- (8) Increment the address.

- (9) Repeat (3) to (8) until the last address is reached.

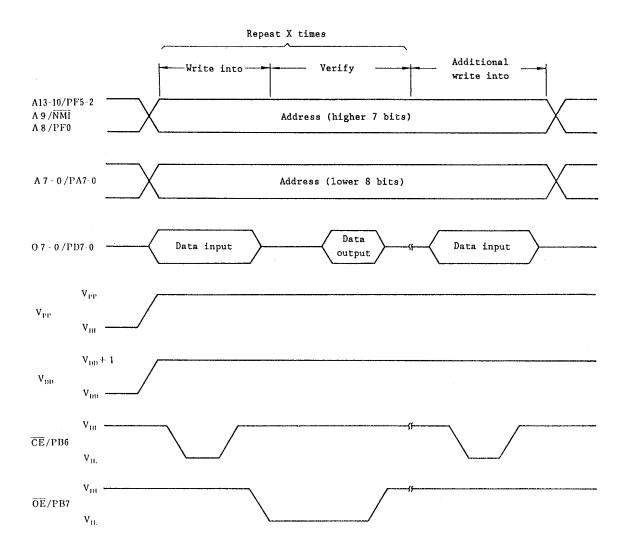

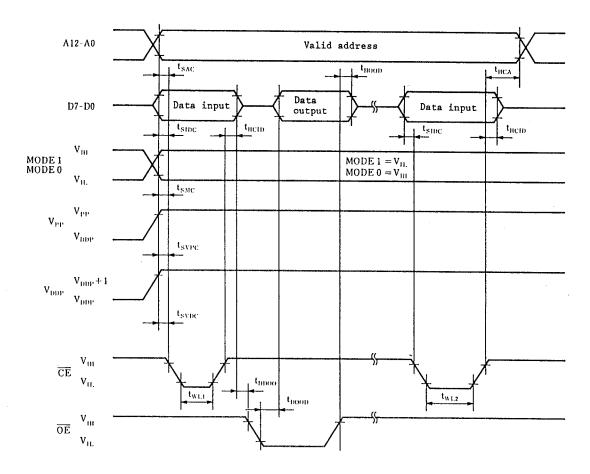

Figure 4-1. PROM Write/Verify Timing

#### 4.3 PROM Read Procedure

The PROM contents can be read onto the external data bus (07-00) according to the following procedure:

- (1) Pull down THE unused pins to GND via a resistor.

- (2) Supply 5 V to the  $V_{\mbox{\scriptsize DD}}$  and  $V_{\mbox{\scriptsize PP}}$  pins.

- (3) Input the address of the data to be read to the Al3-A0 pins.

- (4) Read mode

- (5) Output data to the 07-00 pins.

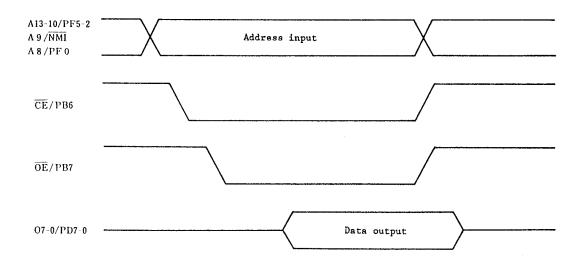

Figure 4-2 shows the (2) to (5) timing.

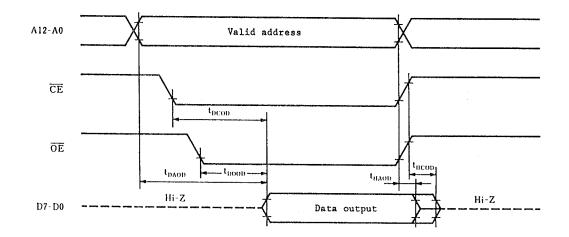

Figure 4-2. PROM Read Timing

#### 5. EPROM ERASE (ONLY PACKAGE PRODUCTS WITH CERAMIC WINDOW)

The  $\mu\text{PD78CP14}$  enables the programmed EPROM data contents to be erased by light rays whose wavelength is shorter than about 400 nm. The programmed EPROM data contents may also be erased if the uncovered window is exposure to direct sunlight or a fluorescent light for several hours. Thus, to protect the data contents, cover the  $\mu\text{PD78CP14}$  with an opaque film so as to prevent ultraviolet rays from entering it through the top window. Shading cover film whose quality is guaranteed is attached to the package product with a window containing EPROM by NEC for shipping.

For normal EPROM erase, place the  $\mu$ PD78CP14 under an ultraviolet light source (254 nm). The minimum amount of radiation exposure required to erase the  $\mu$ PD78CP14 completely is 15 W.s/cm² (ultraviolet ray strength x erase time). This corresponds to about 15 to 20 minutes when using a ultraviolet ray lamp of 12000 uW/cm². However, note that the erase time may be prolonged by aging of the ultraviolet lamp, dirty package window, etc. The distance between the ultraviolet lamp and the  $\mu$ PD78CP14 should be within 2.5 cm.

## 6. WINDOW SEAL (ONLY FOR PACKAGE PRODUCTS WITH CERAMIC WINDOW)

To prevent light other than EPROM erasion lamps from causing an error or light from causing the internal circuitry other than EPROM to malfunction, put a protective seal on the window except when the EPROM contents are erased.

#### 7. ONE-TIME PROM PRODUCT SCREENING

The one-time PROM products ( $\mu$ PD78CP14CW, 78CP14G-36, 78CP14GF-3BE, and 78CP14L) cannot be completely tested by NEC prior to shipment because of the structures. For screening, it is recommended to verify PROM after storing the necessary data under a storage temperature of 125 and a storage time of 24 hours after writing the data.

NEC has a service of one-time PROM write to scaling to screening to verification for pay under the name of QTOP MICON. For details, ask the salesperson.

#### 8. ELECTRICAL SPECIFICATIONS

The  $\mu\text{PD78CP14}$  has a few differences as follows in electric between one-time PROM product and EPROM product. There is no different electric specifications other than the parameters listed in Table 8-1.

Table 8-1. Differences in Electric Specifications between

One-time PROM Product and EPROM Product

| Products<br>Parameter                                   | One-time PROM Product          |       |       | EPROM product                 |      |        |  |

|---------------------------------------------------------|--------------------------------|-------|-------|-------------------------------|------|--------|--|

| Operation power supply voltage range (V <sub>DD</sub> ) | 5 V ±10 %                      |       |       | 5 V ±5 %                      |      |        |  |

| Data retention                                          | Conditions                     | TYP.  | MAX.  | Conditions                    | TYP. | MAX.   |  |

| current (I <sub>DDDR</sub> )                            | $V_{DDDR} = 2.5 V$             | 1 μΑ  | 15 μΑ | $V_{DDDR} = 2.5 V$            |      | 300 μA |  |

|                                                         | V <sub>DDDR</sub> = 5 V ± 10 % | 10 μΑ | 50 μΑ | V <sub>DDDR</sub> = 5 V ± 5 % |      | 1 m/   |  |

# Absolute Maximum Ratings (Ta = 25°C)

| Parameter                             | Symbol            | Test condition        | Ratings                                  | Unit |

|---------------------------------------|-------------------|-----------------------|------------------------------------------|------|

|                                       | V <sub>DD</sub>   |                       | -0.5 to +7.0                             | V    |

| Power supply voltage                  | AV <sub>DD</sub>  |                       | AV <sub>SS</sub> to V <sub>DD</sub> +0.5 | V    |

|                                       | AVSS              |                       | -0.5 to +0.5                             | V    |

|                                       | V <sub>PP</sub>   |                       | -0.5 to +13.5                            | V    |

| Input voltage                         | T.                | Except for NMI/A9 pin | -0.5 to V <sub>DD</sub> +0.5             | V    |

| Imput voltage                         | VI                | NMI/A9 pin            | -0.5 to +13.5                            | V    |

| Output voltage                        | v <sub>o</sub>    |                       | -0.5 to V <sub>DD</sub> +0.5             | V    |

| Output low current                    | I <sub>OL</sub>   | All outputs           | 4.0                                      | mA   |

| output fow cuffere                    |                   | Total, all outputs    | 100                                      | mA   |

| Output high current                   | ІОН               | All outputs           | -2.0                                     | mA   |

| output high carrent                   |                   | Total, all outputs    | -50                                      | mA   |

| A/D converter reference input voltage | V <sub>AREF</sub> |                       | -0.5 to AV <sub>DD</sub> +0.3            | V    |

| Operation<br>temperature              | Topt              |                       | -40 to +85                               | °C   |

| Storage temperature                   | T <sub>stg</sub>  |                       | -65 to +150                              | °C   |

#### ★ Oscillator Characteristics

(One time PROM product): (Ta = -40°C to +85°C,

$$V_{DD}$$

= 5.0 V  $\pm$  10%,  $V_{SS}$  = AV $_{SS}$  = 0 V,  $V_{DD}$  -0.8 V  $\leq$  AV $_{DD}$   $\leq$  V $_{DD}$ , 3.4 V  $\leq$  V $_{AREF}$   $\leq$  AV $_{DD}$ )

(EPROM product): Ta = -40 to +85°C,  $V_{DD}$  = +5.0 V  $\pm$ 5%,  $V_{SS}$  = AV $_{SS}$  = 0 V,  $V_{DD}$  -0.8V  $\leq$  AV $_{DD}$   $\leq$  V $_{DD}$ , 3.4 V  $\leq$  V $_{AREF}$   $\leq$  AV $_{DD}$ )

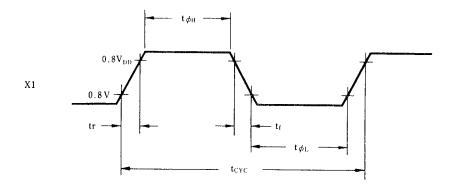

| Resonator                          | Recommended circuit                                         | Parameter                                                   | Test<br>condition | MIN. | MAX. | Unit |

|------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|-------------------|------|------|------|

| Ceramic or<br>crystal<br>resonator | $\begin{bmatrix} X1 & X2 \\ \hline -C1 & -C2 \end{bmatrix}$ | Oscillation<br>frequency (f <sub>xx</sub> )                 |                   | 6    | 15   | MHz  |

| External<br>clock                  | X 1 X 2  HCMOS inverter                                     | X1 input<br>frequency (f <sub>x</sub> )                     |                   | 6    | 15   | MHz  |

|                                    |                                                             | X1 input rise, fall time (t <sub>r</sub> , t <sub>f</sub> ) | ·                 | . 0  | 20   | ns   |

|                                    |                                                             | X1 input high, low level width $(t_{\phi H}, t_{\phi L})$   |                   | 20   | 167  | ns   |

Caution 1. Put the oscillator close to the X1 and X2 pins as much as possible.

2. Do not pass any other signal line through the shaded region.

# Capacitance (Ta = 25°C, $V_{DD}$ = $V_{SS}$ = 0 V)

| Parameter                | Symbol          | Test condition         | MIN. | TYP. | MAX. | Unit |

|--------------------------|-----------------|------------------------|------|------|------|------|

| Input capacitance        | CI              | f <sub>C</sub> = 1 MHz |      |      | 10   | pF   |

| Output capacitance       | c <sub>o</sub>  | Unmeasured pins        |      |      | 20   | pF   |

| Input/output capacitance | c <sub>IO</sub> | returned to 0 V        |      |      | 20   | pF   |

#### DC Characteristics

(One time PROM product): (Ta = -40 to +85°C,

$$V_{DD}$$

=  $AV_{DD}$  =  $+5.0 \text{ V } \pm 10\%$ ,  $V_{SS}$  =  $AV_{SS}$  = 0 V)

(EPROM product) : (Ta = -40 to +85°C,  $V_{DD}$  =  $AV_{DD}$  =  $+5.0 \text{ V } \pm 5\%$ ,  $V_{SS}$  =  $AV_{SS}$  = 0 V)

| Parameter                             | Symbol            | Test condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MIN.                 | TYP. | MAX.               | Unit |

|---------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|--------------------|------|

| T                                     | V <sub>IL1</sub>  | Except for RESET, STOP, NMI, SCK INT1, TI, or AN4-AN7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                    |      | 0.8                | V    |

| Input low voltage                     | V <sub>IL2</sub>  | RESET, STOP, NMI, SCK, INT1, TI, or AN4-AN7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                    |      | 0.2V <sub>DD</sub> | V    |

| T                                     | v <sub>IH1</sub>  | Except for RESET, STOP, NMI, SCK INT1, TI, AN4-AN7, X1, or X2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.2                  |      | V <sub>DD</sub>    | V    |

| Input high voltage                    | v <sub>IH2</sub>  | RESET, STOP, NMI, SCK, INT1, TI, AN4-AN7, X1, or X2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.8V <sub>DD</sub>   |      | v <sub>DD</sub>    | V    |

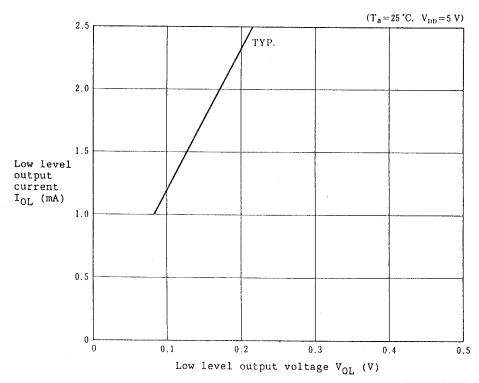

| Output low voltage                    | v <sub>OL</sub>   | I <sub>OL</sub> = 2.0 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |      | 0.45               | v    |

| Output high voltage                   | v                 | I <sub>OH</sub> = -1.0 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>DD</sub> -1.0 |      |                    | V    |

| Output high voltage                   | V <sub>ОН</sub>   | I <sub>OH</sub> = -100 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>DD</sub> -0.5 |      |                    | V    |

| Input current                         | I                 | INT1 (Note 1), TI(PC3) (Note 2);<br>0 V ≤ V <sub>I</sub> ≤ V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |      | ±200               | μΑ   |

| Input leakage current                 | I <sub>LI</sub>   | Except for INT1, TI(PC3);<br>0 V   V  DD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |      | ±10                | μΑ   |

| Output leakage                        | ILO               | 0 V \( \times \t |                      |      | ±10                | μΑ   |

| AV <sub>DD</sub> power supply current | AI <sub>DD1</sub> | Operating mode f <sub>XX</sub> = 15 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | 0.5  | 1.3                | mA   |

| current                               | AI <sub>DD2</sub> | STOP mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      | 10   | 20                 | μА   |

(to be continued)

(Cont'd)

| Parameter                            | Symbol                  | Test cond                     | Test condition                       |                               |  |    | MAX. | Unit           |

|--------------------------------------|-------------------------|-------------------------------|--------------------------------------|-------------------------------|--|----|------|----------------|

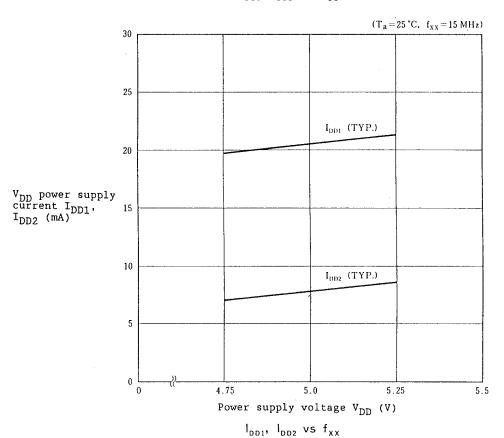

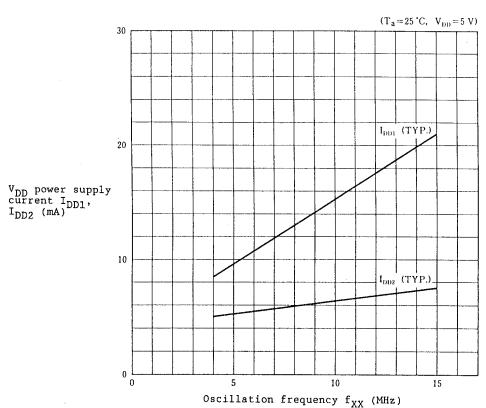

| V <sub>DD</sub> power supply current | I <sub>DD1</sub>        | Operating mode f              | x = 15 MHz                           |                               |  | 16 | 32   | mA             |

| current                              | I <sub>DD2</sub>        | HALT mode f <sub>XX</sub> = 1 | 5 MHz                                |                               |  | 8  | 15   | mA             |

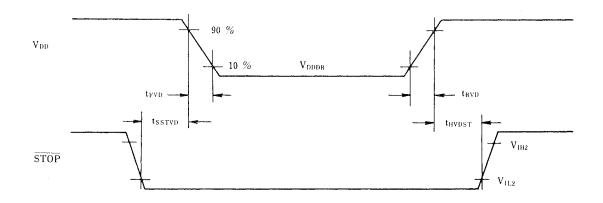

| Data retention voltage               | V <sub>DDDR</sub>       | Hardware or softw             | ardware or software STOP mode        |                               |  |    |      | v              |

| Data retention                       | т                       | Hardware/                     | One-time<br>PROM                     | V <sub>DDDR</sub> = 2.5 V     |  | 1  | 15   | μΑ             |

|                                      | IDDDR Software (Note 3) | STOP mode                     | OP mode   Product   VDDDR = 5 V ± 10 | V <sub>DDDR</sub> = 5 V ± 10% |  | 10 | - 50 | $\mu$ <b>A</b> |

|                                      |                         |                               | EPROM                                | V <sub>DDDR</sub> = 2.5 V     |  |    | 300  | μA             |

|                                      |                         |                               | product                              | V <sub>DDDR</sub> = 5 V ± 10% |  |    | 1    | mA.            |

- Note 1. Assume that self-bias is generated by setting the  ${\tt ZCM}$  register.

- 2. Assume that self-bias is generated by setting the ZCM register when the control mode is set in the MCC register.

- 3. When self-bias is not generated.

#### AC Characteristics

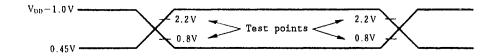

(One-time PROM product:  $(Ta = -40\,^{\circ}\text{C to } +85\,^{\circ}\text{C}, \ V_{DD} = \text{AV}_{DD} = +5.0 \ \text{V} \ \pm 10\,^{\circ}\text{K}, \ V_{SS} = \text{AV}_{SS} = 0 \ \text{V})$  (EPROM product :  $(Ta = -40\,^{\circ}\text{C to } +85\,^{\circ}\text{C}, \ V_{DD} = \text{AV}_{DD} = +5.0 \ \text{V} \ \pm 5\,^{\circ}\text{K}, \ V_{SS} = \text{AV}_{SS} = 0 \ \text{V})$

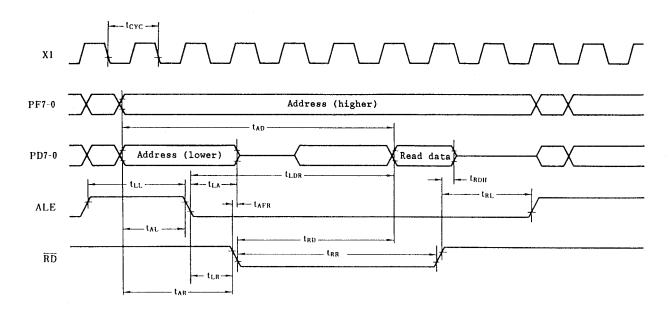

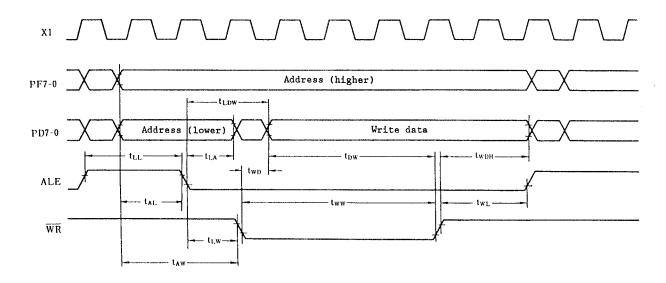

## Read/write Operation:

| Parameter                  | Symbol           | Test condition                                          | MIN. | MAX. | Unit |

|----------------------------|------------------|---------------------------------------------------------|------|------|------|

| X1 input cycle time        | tCYC             |                                                         | 66   | 167  | ns   |

| Address setup time to ALE  | t <sub>AL</sub>  |                                                         | 30   |      | ns   |

| Address hold time from ALE | t <sub>LA</sub>  | f <sub>XX</sub> =15 MHz, CL=150 pF                      | 35   |      | ns   |

| Address RD   delay time    | t <sub>AR</sub>  |                                                         | 100  |      | ns   |

| RD   address float time    | tAFR             | C <sub>L</sub> =150 pF                                  |      | 20   | ns   |

| Address data input time    | t <sub>AD</sub>  |                                                         |      | 250  | ns   |

| ALE - data input time      | t <sub>LDR</sub> | f -15 MU2 01-150 pF                                     |      | 135  | ns   |

| RD   data input time       | t <sub>RD</sub>  | f <sub>XX</sub> =15 MHz, CL=150 pF                      |      | 120  | ns   |

| ALE   RD   delay time      | t <sub>LR</sub>  |                                                         | 15   |      | ns   |

| Data hold time from RD     | t <sub>RDH</sub> | CL=150 pF                                               | 0    |      | ns   |

| RD   ALE   delay time      | t <sub>RL</sub>  | f <sub>XX</sub> =15 MHz, CL=150 pF                      | 80   |      | ns   |

|                            | +                | When data is read f <sub>XX</sub> =15 MHz, CL=150 pF    | 215  |      | ns   |

| RD low level width         | t <sub>RR</sub>  | When OP code is fetched $f_{\rm XX}$ =15 MHz, CL=150 pF | 415  |      | ns   |

| ALE high level width       | tLL              | f <sub>XX</sub> =15 MHz, CL=150 pF                      | 90   |      | ns   |

| Address — WR ∤ delay time  | t <sub>AW</sub>  | f <sub>XX</sub> =15 MHz, CL=150 pF                      | 100  |      | ns   |

| ALE ↓ → data output time   | t <sub>LDW</sub> | TXX 13 IMB, OB 130 pr                                   |      | 180  | ns   |

| WR ↓ data output time      | t <sub>WD</sub>  | CL=150 pF                                               |      | 100  | ns   |

| ALE ↓ → WR ↓ delay time    | t <sub>LW</sub>  |                                                         | 15   |      | ns   |

| Data setup time to WR      | t <sub>DW</sub>  |                                                         | 165  |      | ns   |

| Data hold time from WR     | t <sub>WDH</sub> | f <sub>XX</sub> =15 MHz, CL=150 pF                      | 60   |      | ns   |

| WR   ALE   delay time      | t <sub>WL</sub>  |                                                         | 80   |      | ns   |

| WR low level width         | t <sub>WW</sub>  |                                                         | 215  |      | ns   |

#### Zero-cross Characteristics:

| Parameter                            | Symbol          | Test condition  | MIN. | MAX. | Unit               |

|--------------------------------------|-----------------|-----------------|------|------|--------------------|

| Zero-cross detection input           | v <sub>zx</sub> | AC coupling     | 1    | 1.8  | VAC <sub>P-P</sub> |

| Zero-cross accuracy                  | AZX             | 60-Hz sine wave |      | ±135 | mV                 |

| Zero-cross detection input frequency | fZX             |                 | 0.05 | 1    | kHz                |

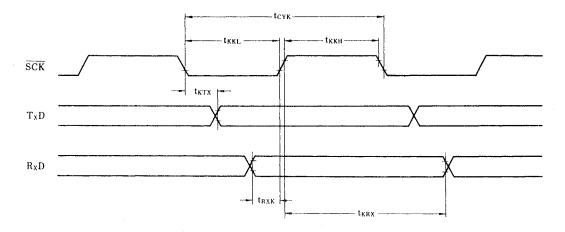

## Serial Operation:

| Parameter               | Symbol           | Test       | condition | MIN. | MAX. | Unit |

|-------------------------|------------------|------------|-----------|------|------|------|

| ·                       |                  | SCK input  | (Note 1)  | 800  |      | ns   |

| SCK cycle time          | <sup>t</sup> CYK | SCK Input  | (Note 2)  | 400  |      | ns   |

|                         |                  | SCK output |           | 1.6  |      | μs   |

|                         |                  | SCK input  | (Note 1)  | 335  |      | ns   |

| SCK low level width     | <sup>t</sup> KKL | Sok Input  | (Note 2)  | 160  |      | ns   |

|                         |                  | SCK output |           | 700  |      | ns   |

|                         |                  | SCK input  | (Note 1)  | 335  |      | ns   |

| SCK high level width    | tKKH             | SOK Input  | (Note 2)  | 160  |      | ns   |

|                         |                  | SCK output |           | 700  |      | ns   |

| RxD setup time to SCK † | t <sub>RXK</sub> | (Note 1)   |           | 80   | ·    | ns   |

| RxD hold time from SCK  | t <sub>KRX</sub> | (Note 1)   |           | 80   |      | ns   |

| SCK ↓ TxD delay time    | t <sub>KTX</sub> | (Note 1)   |           |      | 210  | ns   |

- Notes 1. When the clock rate is x1 in the asynchronous mode or the synchronous mode or I/O interface mode is set

- 2. When the clock rate is x16 or x64 in the asynchronous mode

- Remark The numeric values in the table apply when  $f_{\rm XX}$  = 15 MHz,  $C_{\rm L}$  = 150pF.

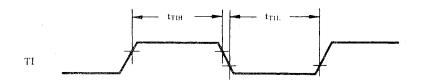

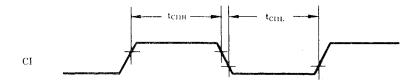

# Other Operations:

| Parameter                               | Symbol                                | Test condition                                                                       | MIN. | MAX. | Unit             |

|-----------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------|------|------|------------------|

| TI high, low level width                | t <sub>TIH</sub> , t <sub>TIL</sub>   |                                                                                      | 6    |      | t <sub>CYC</sub> |

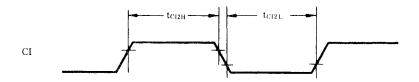

| CI high, low level width                | t <sub>CI1H</sub> , t <sub>CI1L</sub> | o Event count mode<br>o Frequency measurement<br>mode                                | б    |      | tCYC             |

| or high, low level width                | t <sub>CI2H</sub> , t <sub>CI2L</sub> | o Pulse width measurement<br>mode<br>o ECNT latch, clear input<br>o INTEIN set input | 48   |      | tcYC             |

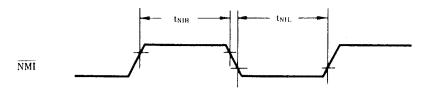

| NMI high, low level width               | t <sub>NIH</sub> , t <sub>NIL</sub>   |                                                                                      | 10   |      | us               |

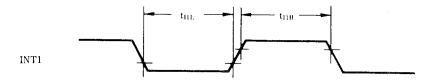

| INT1 high, low level width              | t <sub>I1H</sub> , t <sub>I1L</sub>   |                                                                                      | 36   |      | t <sub>CYC</sub> |

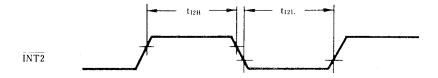

| $\overline{INT2}$ high, low level width | t <sub>I2H</sub> , t <sub>I2L</sub>   |                                                                                      | 36   |      | t <sub>CYC</sub> |

| AN4-7 high, low level width             | t <sub>ANH</sub> , t <sub>ANL</sub>   |                                                                                      | 36   |      | <sup>t</sup> CYC |

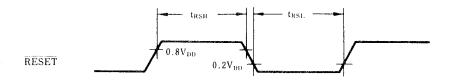

| RESET high, low level width             | t <sub>RSH</sub> , t <sub>RSL</sub>   |                                                                                      | 10   |      | us               |

#### A/D Converter Characteristics

(One-time PROM product:

$$(Ta = -40\,^{\circ}\text{C to } +85\,^{\circ}\text{C}, V_{DD} = 5.0\text{V})$$

$\pm 10\,^{\circ}$ ,  $V_{SS} = AV_{SS} = 0$  V,  $V_{DD} - 0.8$  V  $\leq AV_{DD} \leq V_{DD}$ ,  $3.4\text{V} \leq V_{AREF} \leq AV_{DD}$ ) (EPROM product :  $(Ta = -40\,^{\circ}\text{C to } +85\,^{\circ}\text{C}, V_{DD} = 5.0\text{V} \pm 5\,^{\circ}\text{K}, V_{SS} = AV_{SS} = 0$  V,  $V_{DD} - 0.8$  V  $\leq AV_{DD} \leq V_{DD}$ ,  $3.4$  V  $\leq V_{AREF} \leq AV_{DD}$ )

| Parameter                             | Symbol             | Test condition                                                                                | MIN. | TYP. | MAX.             | Unit             |

|---------------------------------------|--------------------|-----------------------------------------------------------------------------------------------|------|------|------------------|------------------|

| Resolution                            |                    |                                                                                               | 8    |      | -                | Bits             |

|                                       |                    | 3.4 V \( \times V_{AREF} \( \times AV_{DD} \), 66 ns \( \times t_{CYC} \) \( \times 167 ns \) |      |      | ±0.8%            | FSR              |

| Absolute accuracy (Note)              |                    | 4.0 ≤ V <sub>AREF</sub> ≤ AV <sub>DD</sub> ,<br>66 ns ≤ t <sub>CYC</sub> ≤ 167 ns             |      |      | ±0.6%            | FSR              |

|                                       |                    | Ta=-10 to +70°C,<br>4.0 \le V_{AREF} \le AV_{DD},<br>66 ns \le t_{CYC} \le 167 ns             |      |      | ±0.4%            | FSR              |

| 0                                     |                    | 66 ns ≤ t <sub>CYC</sub> ≤ 110 ns                                                             | 576  |      |                  | tCYC             |

| Conversion time                       | CONV               | 110 ns < t <sub>CYC</sub> < 167 ns                                                            | 432  |      |                  | <sup>t</sup> CYC |