#### **PRELIMINARY**

# SERIAL I/O REAL TIME CLOCK WITH WAKE-UP OUTPUT for EXTERNAL CLOCK

#### **■** GENERAL DESCRIPTION

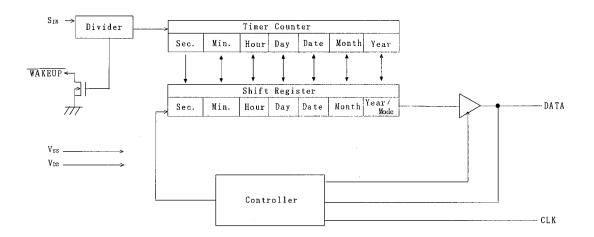

The NJU6359 series is serial I/O and external clock using Real Time Clock with wake-up function suitable for microprocessor.

It contains timer counter, shift register, and interface controller.

It is able to simplify of the external crystal because of the external clock signal using for 32kHz or 384kHz.

The operating voltage is as wide as 2.0V to 5.5V, consequently, the NJU6359 can count accurate time data even if the back up period. And also the wake-up signal outputs by fixed cycle of 720  $\mu$  S.

The data transfer with MPU operated by 2-wire serial transfer.

Furthermore, the long time back up is available as the current consumption during the back up period is a few.

#### **■ FEATURES**

Operating Voltage

: 3.0V ± 20%

2.0V to 5.5V(The clock operation)

• Low operating current :  $0.25 \mu$  A (Typ.) at 3.0V(NJU6359A)

1.0 μ A (Max.) at 3.0V(NJU6359A)

■ BCD Counts of Seconds, Minutes, Hours, Days of week,

Date, Month and Year

Required only 2-port for MCU interface (DATA and CLK)

Automatic Leap Year Compensation: Up to AD 2099

WAKE-UP function

:720  $\mu$  s cycle

Package Outline

: SSOP 8/Chip

C-MOS Technology

#### ■ PACKAGE OUTLINE

NJU6359V

NJU6359C

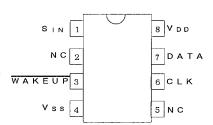

#### ■ PIN CONFIGURATION

#### ■ LINE UP

| Device Name | Input<br>frequency |

|-------------|--------------------|

| NJU6359A    | 3 2 k H z          |

| NJU6359B    | 3 8 4 k H z        |

#### BLOCK DIAGRAM

#### **■ TERMINAL DESCRIPTION**

| No. | SYMBOL  | 1/0   | FUNCTION                                                                                                                                                                                                                                                                           |

|-----|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SIN     | I     | 32kHz or 384kHz input terminal<br>It is different 32kHz and 384kHz by line up.<br>Note)If the accuracy clock is needed, 32.0kHz or 384.0kHz shuold input.<br>Because, It makes the 1Hz by the dividing clock input from this terminal.                                             |

| 3   | WAKE-UP | 0     | WAKE-UP Output terminal(N-channel open-drain.)<br>It Outputs the "L" level signal in 720μ S cycle.                                                                                                                                                                                 |

| 4   | Vss     | Power | GND                                                                                                                                                                                                                                                                                |

| 6   | CLK     | I     | Clock Input Terminal.(with a pull-down resistor.) The Data Input/Output is synchronized by this clock. When the no accessing, this terminal should be connected to Vss.                                                                                                            |

| 7   | DATA    | I/O   | Serial timer data input/output terminal. (with a pull-down resistor.) When the no accessing, this terminal should be connected to VSS. Because the pull-down resistor is valid at the input mode, and, this terminal is VSS. The pull-down resistor is invalid at the output mode. |

| 8   | VDD     | Power | Power supply                                                                                                                                                                                                                                                                       |

| 2,5 | NC      | -     | Non connection (Normally open)                                                                                                                                                                                                                                                     |

#### **■ FUNCTIONAL DESCRIPTION**

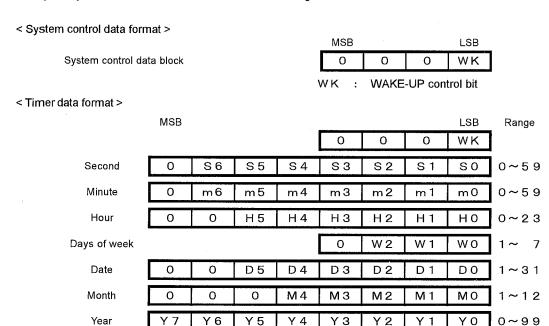

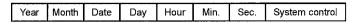

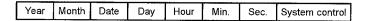

1.Timer and System control data format

The NJU6359 using BCD code which consisting of 4 bits per 1 digit.

The calendar function including the last data of each month and the leap year calculation is executed automatically. The system control data is operated wake-up control.

The unused bit for the Timer and System control data is "0".

Only the system control data can be set instead of setting whole timer data.

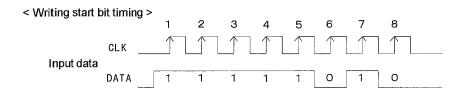

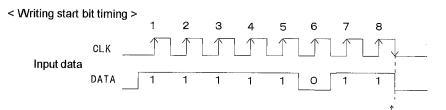

#### 2.Start bit, Stop bit

< Start bit format >

The NJU6359 is decided "Start bit, Stop bit" in order to recognize the start and stop of the Data Input/Output. The fix data needs to input about the timer data write/read, only the system control data write. But, in case of the Stop bit of the timer data read, The NJU6359 generated and outputs. The data is changed over from Output to Input by output of Stop bit. There "Start bit, Stop bit" is using the unused arrangement in BCD code.

#### 1 Timer data writing MSB 0 1 0 1 1 1

LSB 1 (5F) H

2 Timer data reading

MSB LSB 0 1 1 1 1 1 1 1 (DF) H

3 Only the system control data writing MSB LSB

1 0 0 (9F) H

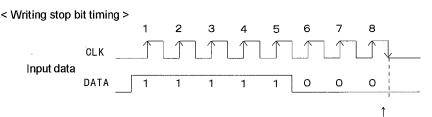

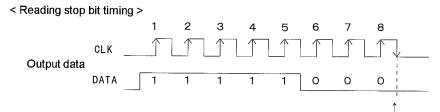

#### < Stop bit format >

1 Timer data writing/reading, Only the system control data writing

| MSB |   |   |   |   |   |   | LSB | _      |

|-----|---|---|---|---|---|---|-----|--------|

| 0   | 0 | 0 | 1 | 1 | 1 | 1 | 1   | (1F) H |

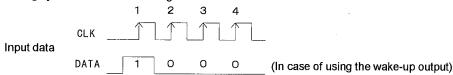

#### 3. Only the system control data writing

The data can be written into the shift register in the NJU6359 from the DATA terminal synchronized with the rising edge of the clock signal input from the CLK terminal.

At first, Start bit for writing of only the system control data is writing into NJU6359, Therefore into the writing mode. At second, System control data is writing into NJU6359, and the last 4 bits is effective.

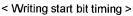

At last, Stop bit is writing, after the Writing system control data concluded. The system control data is written into the internal register with the falling edge of the clock signal, after the writing stop bit. The data writing is operated from LSB first.

### < Writing system control data timing >

#### < Writing stop bit timing >

(The system control data is written into the internal register with the falling edge of the 8th clock.)

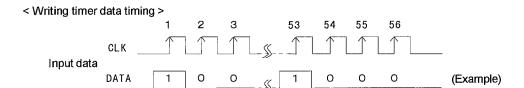

#### 4. Timer data writing

The timer data can be written into the shift register in the NJU6359 from the DATA terminal synchronized with the rising edge of the clock signal input from the CLK terminal.

At first, Start bit for writing of the timer data is writing into NJU6359, Therefore into the writing mode. And then, the divider is stop, and the contents of data is cleared.

At second, Timer data is writing into NJU6359, and the last 56 bits is effective.

At last, Stop bit is writing, after the Writing timer data concluded. The timer data is written into the internal register with the falling edge of the clock signal, after the writing stop bit. And the divider starts operation. The data writing is operated from LSB first. The writing timer data must execute from the beginning, after the power supply turn on.

Rise time of power supply should be less than 10mS when the power supply turn on. (at VDD=3V)

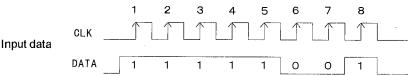

The input data strings are shown below:

(The timer data is written into the internal register with the falling edge of the 8th clock, and the divider starts operation.)

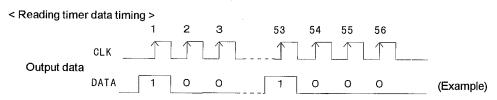

#### 5. Timer data reading

The timer data in the shift register shift by synchronized at the falling edge of the clock signal on CLK terminal and output from the DATA terminal.

At first, Start bit for reading of the timer data is writing into NJU6359. The timer data becomes reading mode by the falling edge of the CLK after the writing. And then, the data terminal is output.

When the timer data becomes reading mode, the timer data is read from the shift register. The timer data is 56 bits.

The stop bit is reading continuously, after the reading timer data concluded. The DATA terminal is changed over from output to input by the falling edge of the CLK after the stop bit writing. The data reading is operated from LSB first.

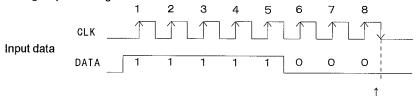

The input data strings are shown below:

(The DATA terminal is output by the falling edge of the 8th clock.)

(The DATA terminal is input by the falling edge of the 8th clock.)

#### 6.Data correction

The NJU6359 have the function of the data correction. This function prevent the error operation of the internal counter by wrong data.

When the in effective data is input, the data is corrected as show below table. However, the data correction is not executed for the system control data. Even if the data "1" is written into the unused bit, the data correction is executed to "0" automatically.

|        | The ineffective data                                                                                                                                                           | The object data of the correction | The corrected data |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------|

| Second | The data except 0 to 59                                                                                                                                                        | S0 to S6                          | 0                  |

| Minute | The data except 0 to 59                                                                                                                                                        | m0 to m6                          | 0                  |

| Hour   | The data except 0 to 23                                                                                                                                                        | H0 to H5                          | 0                  |

| Day    | The data except 1 to 7                                                                                                                                                         | W0 to W2                          | 1                  |

| Date   | Jan., Mar., May, Jul.,  Aug., Oct., Dec.  Apr., Jun., Sep., Nov.,  Feb.,  Feb. in the leap year  : The data except 1 to 30 : The data except 1 to 28 : The data except 1 to 29 | D0 to D5                          | 1                  |

| Month  | The data except 1 to 12                                                                                                                                                        | M0 to M4                          | 1                  |

| Year   | The data except 0 to 99                                                                                                                                                        | Y0 to Y7                          | 0                  |

Note ) The data correction is not executed for the "start bit, stop bit". Therefore, the wrong data is recognized as "start bit, stop bit".

#### ■ ABSOLUTE MAXIMUM RATINGS

| PARAMETER              |  | SYMBOL | RATING             | UNIT |

|------------------------|--|--------|--------------------|------|

| Supply Voltage         |  | VDD    | -0.3 <b>~</b> +6.0 | V    |

| Input Voltage          |  | Vı     | Vss-0.3 ∼ VDD+0.3  | V    |

| Operating Temperature  |  | Topr   | -30 ∼ +80          | °C   |

| Storage Temperature    |  | Tstg   | -40 ~ +125         | °C   |

| Power Dissipation SSOP |  | PD     | 250                | mW   |

Note 1) Decoupling capacitor should be connected between VDD and Vss due to the stabilized operation of the circuit.

#### ■ ELECTRICAL CHARACTERISTICS

#### DC Characteristics

(Unless Otherwise Specified VDD=3V±20%, Vss=0V, Ta=25°C)

| PARAMETER                     | SYMBOL |                                                         | NOLTION           | T MAINT | TVD  | T 144 V |      |      |

|-------------------------------|--------|---------------------------------------------------------|-------------------|---------|------|---------|------|------|

|                               |        | CONDITION                                               |                   | MIN.    | TYP. | MAX.    | UNIT | NOTE |

| Operating Voltage             | VDD    |                                                         |                   | 2.0     |      | 5,5     | V    |      |

| Operating Current             | IDD1   | Apply to the NJU6359A                                   |                   |         | 0.25 | 1.0     | μА   | 2    |

| operating outlent             | IDD2   | Apply to the                                            |                   | 0.85    | 2.0  | 3       |      |      |

| Output off Leakage<br>Current | lor    | WAKEUP Ter                                              | WAKEUP Terminal   |         |      | 2.0     | μΑ.  |      |

| Input Current                 | lin    | CLK, DATA At the Input mode Terminals VDD,CLK,DATA=3.6V |                   |         |      | 12.0    | μА   |      |

| In most 1/mltmm - 4           | VIH1   | SIN Terminal                                            |                   | VDDx0.8 |      | VDD     | .,   |      |

| Input Voltage 1               | VIL1   | SIN Terminal                                            |                   | 0       |      | 0.2     | V    |      |

| Input Voltage 2               | VIH2   | CLK,DATA Terminals                                      |                   | VDDx0.8 |      | VDD     | .,   |      |

| input voltage 2               | VIL2   | CLK,DATA Terminals                                      |                   | Vss     |      | VDDx0.2 | V    |      |

| Output Current                | Vон    | DATA<br>Terminal                                        | VDD=2.4V,VOH=1.8V | 0.4     |      |         |      |      |

|                               | Vol1   | DATA<br>Terminal                                        | VDD=2.4V,VOL=0.4V | 1.0     |      |         | mA   |      |

|                               | VOL2   | WAKEUP Terminal VDD=2.4V,VOL=0.4V                       |                   | 1.0     |      |         |      |      |

Note 2) SIN=32KHz, CLK/DATA=0V, The data is input mode, and the unused wake-up.

Note 3) SIN=384KHz, CLK/DATA=0V, The data is input mode, and the unused wake-up.

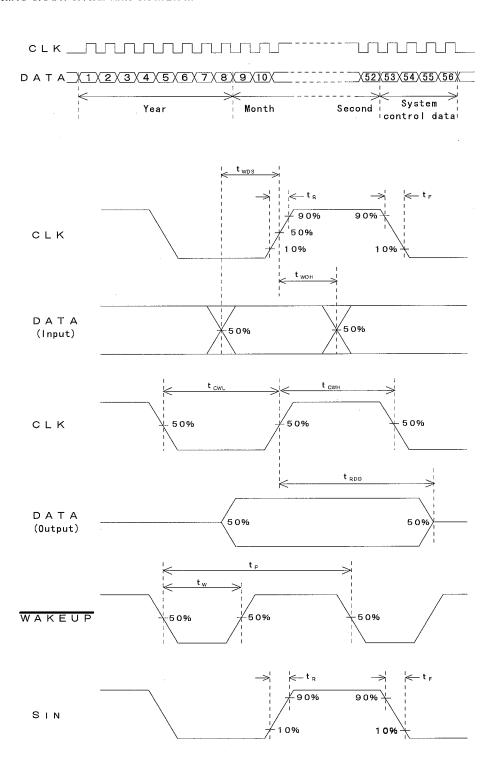

#### **AC Characteristics**

( Unless Otherwise Specified VDD=3V $\pm$ 20%, Vss=0V, Ta=25°C )

|                                    | •      | •          |      |      | •    | •     |      |

|------------------------------------|--------|------------|------|------|------|-------|------|

| PARAMETER                          | SYMBOL | CONDITIONS | MIN. | TYP. | MAX. | UNIT  | NOTE |

| Sin Input Frequency                | FR32   |            |      | 32   |      | 1211- | 4    |

| On input i requency                | FR384  |            |      | 384  |      | - KHz | 5    |

| Sin Input Operating Frequency      | FRD32  |            | 30   | 32   | 34   |       | 6    |

| On input Operating Frequency       | FRD384 |            | 382  | 384  | 386  | KHz   | 7    |

| Sın Input Signal Duty Ratio        | DUTY   |            | 40   | 50   | 60   | %     |      |

| CLK Pulse "H" Period               | tcwn   |            | 0.47 |      | 5000 | μS    |      |

| CLK Pulse "L" Period               | tcwL   |            | 0.47 |      | 5000 | μS    |      |

| DATA Set-up Time Before CLK Rising | twos   |            | 200  |      |      | nS    |      |

| DATA Hold Time After CLK Rising    | twoH   |            | 200  |      |      | nS    |      |

| DATA Delay Time After CLK Rising   | trdd   | CL=50pF    |      |      | 200  | nS    |      |

| Wake-up Cycle                      | tР     |            | 690  | 720  | 750  | μS    | 8    |

| Wake-up Pulse "L" Period           | tw     |            | 90   | 120  | 150  | μS    | 8    |

| Input Rise/Fall Time               | trF    |            |      |      | 40   | nS    |      |

| Power Supply Rising Time           | tvon   |            |      |      | 10   | mS    |      |

Note 4) Apply to the NJU6359A. If the accuracy clock is needed, 32.0kHz should input, because a second is made with the input signal is divided by 32,000.

Note 5) Apply to the NJU6359B. If the accuracy clock is needed, 384.0kHz should input, because a second is made with the input signal is divided by 384,000.

Note 6) Apply to the NJU6359A. The regulations guarantees operation, but the accuracy is not available.

Note 7) Apply to the NJU6359B. The regulations guarantees operation, but the accuracy is not available.

Note 8) Measurement conditions : The WAKEUP terminal is pulled-up to the VDD terminal connected by 470k Ω resister. The 32kHz (NJU6359A) or 384kHz (NJU6359B) inputs to the SIN terminal.

#### ■ TIMING CHART of Real Time Clock Block

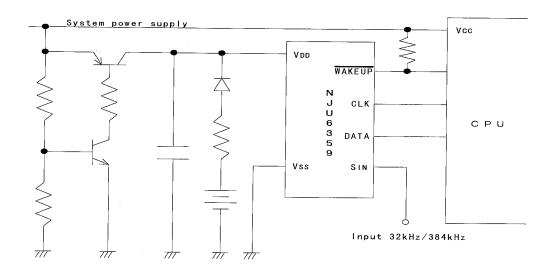

#### ■ APPLICATION CIRCUIT

## NJU6359

## **MEMO**

[CAUTION]

The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.