# 1/4 DUTY LCD DRIVER

#### GENERAL DESCRIPTION

The NJU6433 is a 1/4 duty LCD driver for segment type LCD panel.

The LCD driver consists of 4-common and 50-segment drives up to 200 segments.

The NJU6433 is useful for the digital tuning system or others segment type display driver.

#### PACKAGE OUTLINE

NJU6433F

#### **■** FEATURES

- 50 Segment Drivers

- Duty Ratio 1/4 (Up to 200-Segments)

- Serial Data Transmission (Shift Clock 2MHz max.)

- Oscillation Circuit On-chip (External Resistance Required)

- Display Off Function (INH Terminal)

- Operating Voltage --- 2.4~5.5V

- LCD Driving Voltage --- 6.5V Max.

- Package Outline --- QFP 64 ( D1, G1 )

- C-MOS Technology

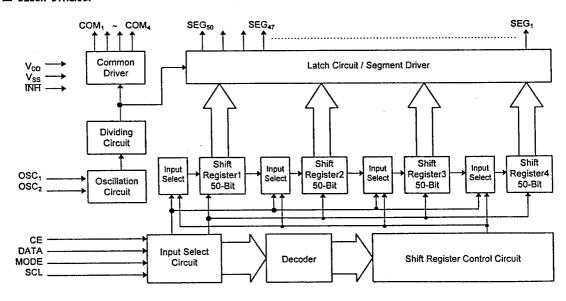

#### **BLOCK DIAGRAM**

5

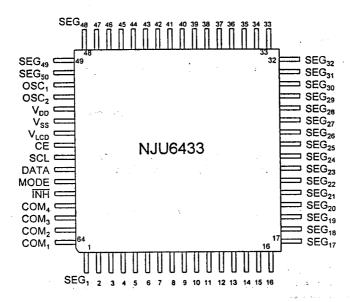

# PIN CONFIGURATION

# **TERMINAL DESCRIPTION**

| NO.      | SYMBOL                               | FUNCTION                                                                                                                                     |  |  |  |  |  |

|----------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1~50     | SEG <sub>1</sub> ~ SEG <sub>50</sub> | LCD Segment Output Terminals                                                                                                                 |  |  |  |  |  |

| 51<br>52 | OSC <sub>1</sub><br>OSC <sub>2</sub> | Oscillation Terminals : External resistance is connected to these terminals.                                                                 |  |  |  |  |  |

| 53       | V <sub>DD</sub>                      | Power Supply (+5V)                                                                                                                           |  |  |  |  |  |

| 54       | Vss                                  | Power Supply ( OV)                                                                                                                           |  |  |  |  |  |

| 55       | VLCD                                 | Power Supply for LCD Driving The relation: IVDD - VLCD I≦ 1.3VDD, VLCD VSS must be maintained.                                               |  |  |  |  |  |

| 56       | CE                                   | Chip Enable Signal Input Terminal: "H": LCD display data and mode setting data input "L": Disable Fall Edge: LCD display data latch          |  |  |  |  |  |

| 57       | SCL                                  | Serial Data Transmission Clock Input Terminal:<br>LCD display and Mode setting data are input synchronized<br>SCL clock signal rise edge.    |  |  |  |  |  |

| 58       | DATA                                 | Serial Data Input Terminal<br>Data input timing : SCL clock rise edge                                                                        |  |  |  |  |  |

| 59       | MODE                                 | Data or Mode Select Terminal "H": Data input mode "L": LCD display data input mode (refer the mode setting table for mode setting contents)  |  |  |  |  |  |

| 60       | TNH                                  | Display-Off Control Terminal: When display goes to off, the display data in the shift-register is retained. "H": Display-On "L": Display-Off |  |  |  |  |  |

| 61~64    | COM4~COM1                            | LCD Common Output Terminals                                                                                                                  |  |  |  |  |  |

#### ■ FUNCTIONAL DESCRIPTION

(1) Operation of each block

(1-1)Oscillation Circuit:

The oscillation circuit operate by connecting external resistance ( capacitance is incorporated ).

This circuit provides the clock signal to both common and segment drivers.

(1-2)Divider Circuit

This circuit divides the oscillating signal to generate the common and segment timing.

(1-3)Shift-Register

When the CE terminal is "H" (Enable mode), the display data is transferred to the shift-register synchronized by the shift clock on the SCL terminal.

(1-4)Latch Circuit and Segment Driver

When the CE signal falling, the display data is latched, and the data controls the segment signal of display-on/off.

(2) Data Input Format

(2-1) Input Data Correspond to Segment Status

The "H" input data correspond to segment "ON" and "L" correspond to "OFF".

| Data Dxxx | Segment Status |

|-----------|----------------|

| "H"       | ON             |

| "L"       | OFF            |

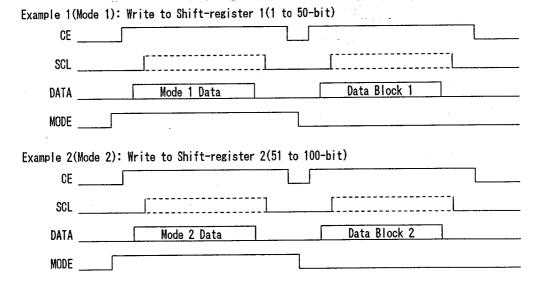

(2-2)Write to Shift-register

Write to shift-register performes Mode setting data writing and LCD display data writing.

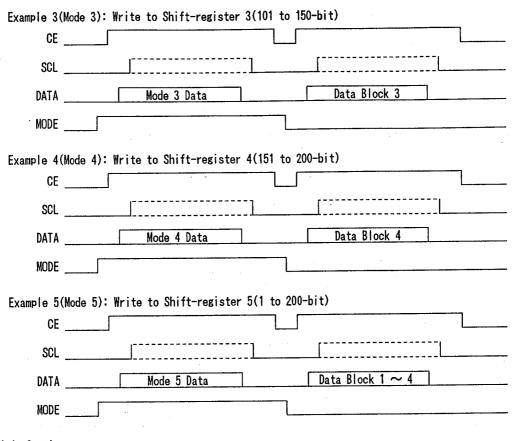

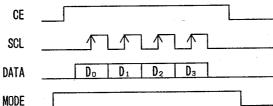

### (2-3)Mode Setting

Transferd register selection and all clear of the shift register are performed by writing 4-bit code shown below to the decoder in CE ="H" and MODE ="H" state.

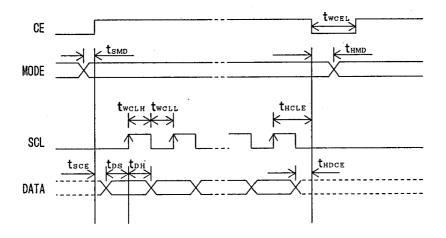

< Input Timing Chart >

< Mode Setting Table >

| CE<br>Terminal | MODE<br>Terminal | DATA Terminal MODE # Data<br>D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> (HEX) | Mode Set Up                            |

|----------------|------------------|------------------------------------------------------------------------------------------------|----------------------------------------|

|                | "H"              | 0 0 0 1 (01 <sub>H</sub> )                                                                     | Select the shift-register 1            |

|                |                  | 0 0 1 0 (02н)                                                                                  | Select the shift-register 2            |

|                |                  | 0 0 1 1 (03н)                                                                                  | Select the shift-register 3            |

| "H"            |                  | 0 1 0 0 (04 <sub>H</sub> )                                                                     | Select the shift-register 4            |

|                |                  | 0 1 0 1 (05 <sub>H</sub> )                                                                     | Select the all shift-register (1 to 4) |

|                |                  | 1 1 1 1 (0F <sub>H</sub> )                                                                     | All shift-register is "L"              |

Note) The internal decoder is data through type. Therefore, the 8 bits data also can write though only 4 bits data from the CE falling are validated.

—New Japan Radio Co.,Ltd.-

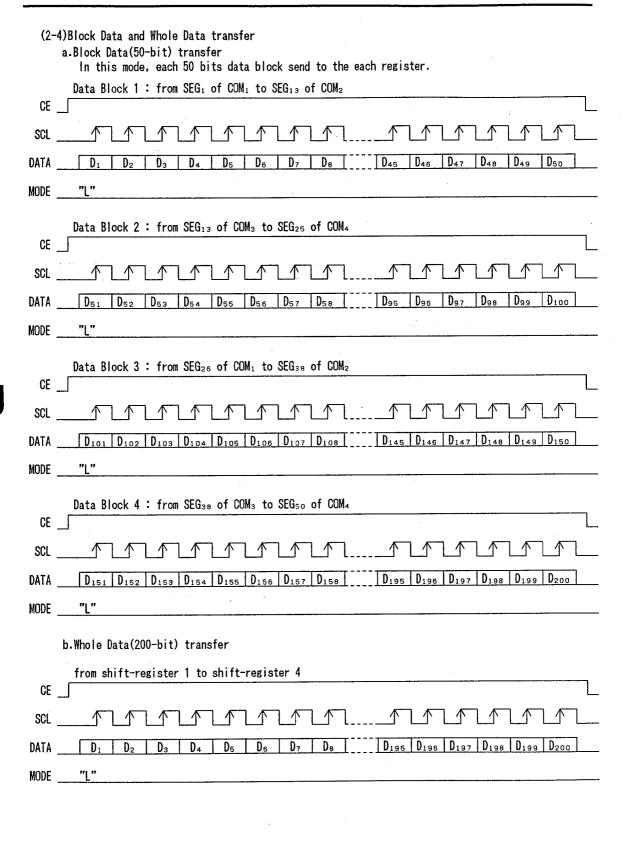

(2-5)Display Data Correspond to Segment and Common Terminals

|        | 2-5)Display Data Correspond to Segment and Common Terminals                  |                   |                  |                  |      |      |              |  |  |  |

|--------|------------------------------------------------------------------------------|-------------------|------------------|------------------|------|------|--------------|--|--|--|

| Mode   | Data                                                                         | Segment           | COM <sub>1</sub> | COM <sub>2</sub> | COM₃ | COM₄ | Data Block   |  |  |  |

| Mode 1 | D <sub>1</sub><br>D <sub>2</sub><br>D <sub>3</sub><br>D <sub>4</sub>         | SEG <sub>1</sub>  | 0                | 0                | 0    | 0    | Data Block 1 |  |  |  |

|        | D <sub>5</sub><br>D <sub>6</sub><br>D <sub>7</sub><br>D <sub>8</sub>         | SEG <sub>2</sub>  | 0                | 0                | 0    | 0    |              |  |  |  |

|        |                                                                              |                   |                  | :                |      |      | ·            |  |  |  |

|        | D45<br>D46<br>D47<br>D48                                                     | SEG <sub>12</sub> | 0                | 0                | 0    | 0    |              |  |  |  |

|        | D <sub>49</sub><br>D <sub>50</sub>                                           | SEG <sub>13</sub> | 0                | 0                |      |      |              |  |  |  |

| Mode 2 | D <sub>51</sub><br>D <sub>52</sub>                                           | SEG <sub>13</sub> |                  |                  | 0    | 0    | Data Block 2 |  |  |  |

|        | D <sub>53</sub><br>D <sub>54</sub><br>D <sub>55</sub><br>D <sub>56</sub>     | SEG <sub>14</sub> | 0                | 0                | 0    | 0_   |              |  |  |  |

|        |                                                                              |                   |                  |                  |      | :    |              |  |  |  |

| e e e  | D <sub>97</sub><br>D <sub>98</sub><br>D <sub>99</sub><br>D <sub>100</sub>    | SEG <sub>25</sub> | 0                | 0                | 0    | . 0  |              |  |  |  |

| Mode 3 | D <sub>101</sub><br>D <sub>102</sub><br>D <sub>103</sub><br>D <sub>104</sub> | SEG <sub>26</sub> | 0                | 0                | 0    | 0    | Data Block 3 |  |  |  |

| ·      | D <sub>105</sub><br>D <sub>106</sub><br>D <sub>107</sub><br>D <sub>108</sub> | SEG <sub>27</sub> | 0                | 0                | 0    | 0    |              |  |  |  |

|        |                                                                              | :                 | :                | :                | :    |      |              |  |  |  |

|        | D <sub>145</sub><br>D <sub>146</sub><br>D <sub>147</sub><br>D <sub>148</sub> | SEG <sub>37</sub> | 0                | 0                | 0    | 0    |              |  |  |  |

|        | D <sub>149</sub><br>D <sub>150</sub>                                         | SEG₃₃             | 0                | 0                |      |      |              |  |  |  |

| Mode 4 | D <sub>151</sub><br>D <sub>152</sub>                                         | SEG38             |                  |                  | 0    | 0    | Data Block 4 |  |  |  |

|        | D <sub>153</sub><br>D <sub>154</sub><br>D <sub>155</sub><br>D <sub>156</sub> | SEG39             | 0                | 0                | 0    | 0    |              |  |  |  |

|        | :                                                                            | •                 |                  | • • •            | :    | :    |              |  |  |  |

|        | D <sub>197</sub><br>D <sub>198</sub><br>D <sub>199</sub><br>D <sub>200</sub> | SEG <sub>50</sub> | 0                | 0                | 0    | 0    |              |  |  |  |

# MASOLUTE MAXIMUM RATINGS

| PARAMETE              | R       | SYMBOL             | RATINGS                                 | UNIT |

|-----------------------|---------|--------------------|-----------------------------------------|------|

| Operating Voltage (1) |         | V <sub>DD</sub>    | - 0.3 ~ + 7.0                           | V    |

| Operating Voltage (2) | Note 1) | Arcd               | V <sub>DD</sub> - 6.5 ~ V <sub>SS</sub> | ٧    |

| Input Voltage (1)     | Note 2) | V <sub>1 (1)</sub> | - 0.3 ~ + 7.0                           | V    |

| Input Voltage (2)     | Note 3) | V <sub>1 (2)</sub> | - 0.3 ~ V <sub>DD</sub> +0.3            | ٧    |

| Output Voltage        | Note 3) | Vo -               | - 0.3 ~ V <sub>DD</sub> +0.3            | ٧    |

| Output Current (1)    | Note 4) | 10(1)              | 100                                     | μA   |

| Output Current (2)    | Note 5) | lo(2)              | 1.0                                     | mA   |

| Power Dissipation     |         | PD                 | 300                                     | m₩   |

| Operating Temperature |         | Topr               | - 30 ~ + 85                             | ဗ    |

| Storage Temperature   |         | Tstg               | - 40 ~ + 125                            | r    |

Note 1) IV<sub>DD</sub> - V<sub>LCD</sub> I ≦ 1.3V<sub>DD</sub>, V<sub>LCD</sub> ≦ V<sub>SS</sub> Note 2) CE, SCL, DATA, MODE, TNH Terminals

Note 3) OSC1, OSC2 Terminals

Note 4) SEG<sub>1</sub>  $\sim$  SEG<sub>50</sub> Terminals

Note 5) COM<sub>1</sub>  $\sim$  COM<sub>4</sub> Terminals

# **ELECTRICAL CHARACTERISTICS**

· DC Characteristics

( Ta=25°C,  $V_{DD}=5.0V$ ,  $V_{ss}=0V$ ,  $V_{LCD}=V_{DD}-6.5V$  )

| (14.40-4) 100-411            |                        |                                               |                       |         |                      |                |                       |      |  |

|------------------------------|------------------------|-----------------------------------------------|-----------------------|---------|----------------------|----------------|-----------------------|------|--|

| PARAMETER                    | SYMBOL                 | CONDII                                        | 10                    | NS      | MIN                  | TYP            | MAX                   | UNIT |  |

| Operating Voltage (1)        | <b>V</b> <sub>DD</sub> | V <sub>DD</sub> Terminal                      |                       | 2.4     |                      | 5.5            | ٧                     |      |  |

| Operating Voltage (2)        | VLCD                   | VLCD Terminal                                 |                       | Note 6) | Vss                  |                | V <sub>DD</sub> -6.5  | V    |  |

| "H" Input Voltage            | VIH                    | CE,SCL,DATA,MO                                | DE,                   |         | 0.7V <sub>DD</sub>   |                | V <sub>DD</sub>       | V    |  |

| "L" Input Voltage            | VIL                    | TNH Terminals                                 |                       |         | Vss                  |                | 0.3V <sub>DD</sub>    | ٧    |  |

| "H" Input Current            | I <sub>IH</sub>        | CE,SCL,DATA,MO                                | DDE.                  | V1=VDD  |                      |                | 5.0                   | μA   |  |

| "L" Input Current            | 1 I E                  | INH Terminals                                 |                       | V1=Ass  |                      |                | 5.0                   | μA   |  |

| "H" Output Voltage (1)       | V <sub>OH(1)</sub>     | SEG1~SEG50                                    | 50 lo=-10μA           |         | V <sub>DD</sub> -1.0 |                |                       | ٧    |  |

| "L" Output Voltage (1)       | Vol(1)                 |                                               | 1o=+10μA              |         |                      |                | V <sub>LCD</sub> +1.0 | ٧    |  |

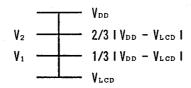

| Middle Level Voltage 1/3 (1) | V <sub>MS1/3</sub>     | SEG <sub>1</sub> ~SEG <sub>50</sub>           | I₀=±10µA              |         | V <sub>1</sub> -1.0  | V <sub>1</sub> | V1+1.0                | ٧    |  |

| Middle Level Voltage 2/3 (1) | V <sub>MS2/3</sub>     | Note 7)                                       | 1 <sub>0</sub> =±10μA |         | V <sub>2</sub> -1.0  | V <sub>2</sub> | V <sub>2</sub> +1.0   | ٧    |  |

| "H" Output Voltage (2)       | V <sub>OH(2)</sub>     | COM₁~COM₄                                     | Io=-100μA             |         | V <sub>DD</sub> -0.6 |                |                       | ٧    |  |

| "L" Output Voltage (2)       | Vol (2)                |                                               | 1o=+100 MA            |         |                      |                | VLCD-0.6              | ٧    |  |

| Middle Level Voltage 1/3 (2) | V <sub>мс1/3</sub>     | COM1~COM4                                     | Io=±100μA             |         | V <sub>1</sub> -0.6  | V <sub>1</sub> | V <sub>1</sub> +0.6   | ٧    |  |

| Middle Level Voltage 2/3 (2) | V <sub>MC2/3</sub>     | Note 7)                                       | Io=±100μA             |         | V <sub>2</sub> -0.6  | V <sub>2</sub> | V <sub>2</sub> +0.6   | ٧    |  |

| Oscillating Frequency Range  | fosc                   | OSC <sub>1</sub> , OSC <sub>2</sub> Terminals |                       | 25      |                      | 200            | kHz                   |      |  |

| Oscillating Frequency        | fosc                   |                                               | R=140kΩ               |         | 115                  | 130            | 145                   | kHz  |  |

| Operating Current (1)        | DD                     | V <sub>DD</sub> Terminal                      |                       |         | 50                   | 80             | μA                    |      |  |

| Operating Current (2)        | LCD                    | V <sub>LCD</sub> Terminal                     |                       |         | 15                   |                | μA                    |      |  |

| Hysteresis Voltage           | V <sub>H</sub>         | CE,SCL,DATA,MODE,<br>TNH Terminals            |                       | 0.3     |                      |                | V                     |      |  |

Note 6) The relation: I  $V_{\rm DD}$  -  $V_{\rm LCD}$  I  $\leq$  1.3 $V_{\rm DD}$ ,  $V_{\rm LCD}$   $\leq$   $V_{\rm SS}$  must be maintained. Note 7)  $V_{\rm 1}$ =1/3 I  $V_{\rm DD}$  -  $V_{\rm LCD}$  I,  $V_{\rm 2}$ =2/3 I  $V_{\rm DD}$  -  $V_{\rm LCD}$  I

# · AC Characteristics

( Ta=25°C,  $V_{DD}$ =5.0V,  $V_{SS}$ =0V,  $V_{LCD}$ = $V_{DD}$ -6.5V )

| PARAMETER                      | SYMBOL           | CONDITIONS          | MIN  | TYP | MAX | UNIT |

|--------------------------------|------------------|---------------------|------|-----|-----|------|

| "L" Clock Pulse Width          | twell            | COL Tauminal        | 0.25 |     |     | μs   |

| "H" Clock Pulse Width          | twclh            | SCL Terminal        | 0.25 |     |     | μs   |

| Data Set-up Time               | tos              | COL DATA Taumimala  | 0.25 |     |     | μs   |

| Data Hold Time                 | t <sub>DH</sub>  | SCL, DATA Terminals | 0.25 |     |     | μs   |

| CE Set-up Time                 | tsce             | OF DATA Touringle   | 1.0  |     |     | μs   |

| CE Hold Time (1)               | thoce            | CE, DATA Terminals  | 1.0  |     |     | μs   |

| CE Hold Time (2)               | thele            | CE, SCL Terminals   | 1.25 |     |     | μs   |

| Mode Set-up Time               | tsmD             | OF HODE T           | 0.25 |     |     | μs   |

| Mode Hold Time                 | t <sub>HMD</sub> | CE, MODE Terminals  | 0.25 |     |     | μs   |

| "L" Chip Enable<br>Pulse Width | twcel            | CE Terminal         | 4.0  |     |     | μs   |

#### · Input Timing Characteristics

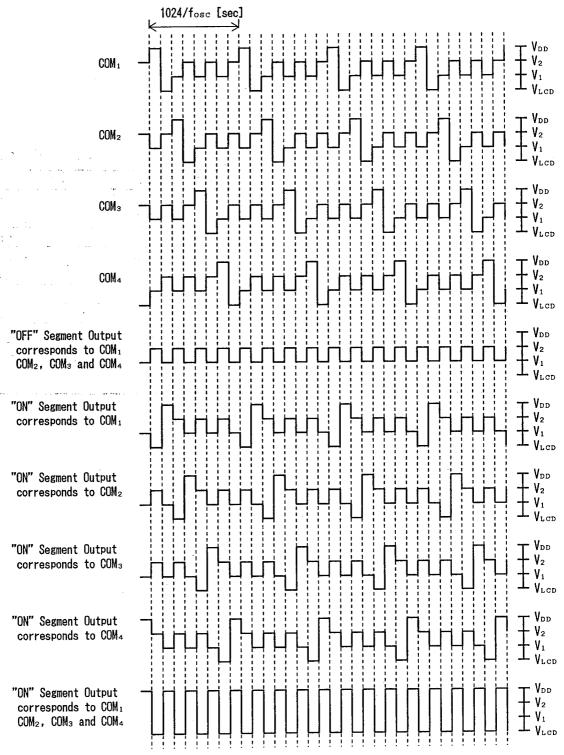

#### ■ LCD Driving Waveform(1/4DUTY • 1/3BIAS)

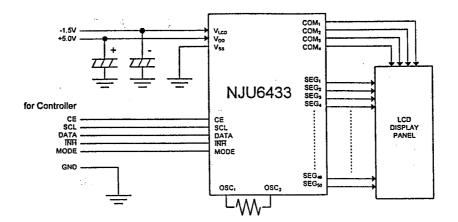

# **APPLICATION CIRCUIT**

(Note) The internal display data is undefined when  $V_{\text{DD}}$  is just turned on.

To avoid the meaningless display, please keep the INH terminal at "L" until proper display data has been transferred.

In order to set the initial condition, 200-bit blank data or the first 200-bit data to be displayed should be transferred.

# **NJU6433**

# **MEMO**

[CAUTION]

The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.