## PRELIMINARY

## 34COMMON X 101SEGMENT I<sup>2</sup>C-BUS BIT MAP LCD DRIVER

## GENERAL DESCRIPTION

NJU6576 is a bit map LCD driver to display graphics or characters. It contains 3,434-bit display data RAM, microprocessor interface circuits, instruction decoder, 101-segment and 34-common drivers.

NJU6576 is supported by the first-mode I<sup>2</sup>C-Bus, and the bit image display data are transferred to the display data RAM through SDA line. NJU6576 possesses two display modes selected by a command. It displays 33-common/101-segment graphics in the normal display mode. And it displays 101 Static-icons, keeping low power consumption, in the icon mode.

NJU6576 includes internal oscillator and realizes low operating current, wide operating voltage from 2.2V to 5.5V. Therefore it is useful for small size battery items.

## PACKAGE OUTLINE

NJU6576CH

| FEATURES                           |                                |                         |              | н.<br>На страна стр |

|------------------------------------|--------------------------------|-------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------|

| Display Data RAM                   | 3,434-bit                      |                         |              |                                                                                                                       |

| LCD Driving outputs                | 34-common X 10                 | 34-common X 101-segment |              | display mode: Bit Map Display                                                                                         |

|                                    | 1-common X 101                 | -segment                | (in icon mo  | de: Static-icon Display)                                                                                              |

| Oirect Interface to the first-mode | e l²C-bus                      |                         |              |                                                                                                                       |

| Programmable Display mode          | Normal display m               | ode, Icon mo            | de           |                                                                                                                       |

| Programmable Duty Ratio            | 1/34, 1/17 duty                | (in normal              | display mode | )                                                                                                                     |

| Programmable Bias Ratio            | 1/7, 1/5 bias                  | (in normal              | display mode | )                                                                                                                     |

| Command List                       |                                |                         |              |                                                                                                                       |

| Display On/Off, Power Save         | e On/Off, Icon-mode            | On/Off, Duty            | Select, Bias | Select, Increment Mode Sele                                                                                           |

| Page Address Set, Column           | Address Set                    |                         |              |                                                                                                                       |

| LCD Power Supply Circuit           | Bleeder resistor )             | < 5, Voltage            | follower X 4 | (in normal display mode)                                                                                              |

| Low Operating Current              | *** uA TYP.                    |                         |              |                                                                                                                       |

| Operating Voltage(VDD)             | 2.2V to 5.5V                   |                         |              |                                                                                                                       |

| LCD Driving Voltage(VLCD)          | 4V to 13.5V                    | (in normal              | display mode | )                                                                                                                     |

|                                    |                                |                         |              |                                                                                                                       |

|                                    | 2.5V to 13.5V                  | (in icon mo             | ode)         |                                                                                                                       |

| Package Outline                    | 2.5V to 13.5V<br>TCP/Bumped Ch |                         | ode)         |                                                                                                                       |

\* Purchase of I<sup>2</sup>C components of New Japan Radio Co., Ltd or one of its sublicensed Associated Companies conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

New Japan Radio Co., Ltd.

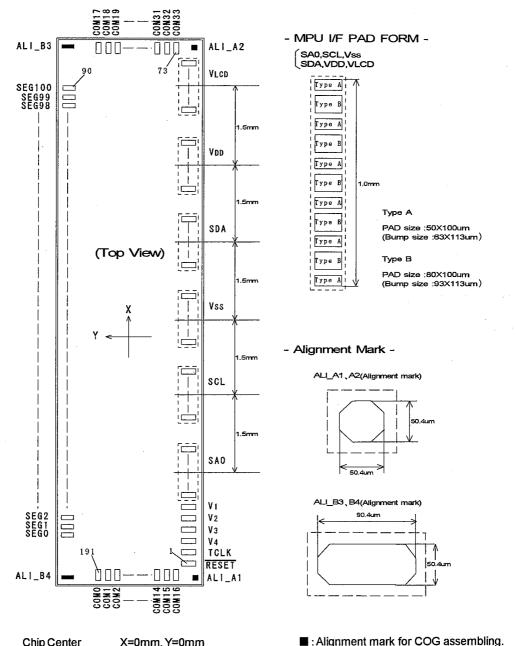

## PAD LOCATION

Chip Center Chip Size Chip Thickness PAD(Bump) Size

PAD Pitch Bump Height Bump Material X=0mm, Y=0mm X=9.58mm, Y=2.3mm 400um ±30um No.1 to No.6, No.73 to No.207 PAD size :50umX100um (Bump size :63um X 113um) 80um MIN. 25um TYP. Au

New Japan Radio Co., Ltd.

# JRC

# NJU6576

## PAD COORDINATES

## Chip size 9.58mm X 2.3mm (Chip center X= 0,Y=0)

| PAD No. | PAD Name | X = (um) | Y = (um) |  |

|---------|----------|----------|----------|--|

| 1       | RESET    | -4374    | -999     |  |

| 2       | TCLK     | -4294    | -999     |  |

| 3       | V4       | -4234    | -999     |  |

| 4       | V3       | -4214    | -999     |  |

|         |          |          |          |  |

|         | V2       | -4054    | -999     |  |

| 6       | V1       | -3974    | -999     |  |

|         | SAO      | -3893    | -999     |  |

| 8       | SAO      | -3798    | -999     |  |

| 9       | SAO      | -3703    | -999     |  |

| 10      | SAO      | -3608    | -999     |  |

| 11      | SAO      | -3513    | -999     |  |

| 12      | SAO      | -3418    | -999     |  |

| 13      | SA0      | -3323    | -999     |  |

| 14      | SAO      | -3228    | -999     |  |

| 15      | SAO      | -3133    | -999     |  |

| 16      | SAO      | -3038    | -999     |  |

| 17      | SAO      | -2943    | -999     |  |

| 18      | SCL      | -2393    | -999     |  |

| 19      | SCL      | -2298    | -999     |  |

| 20      | SCL      | -2203    | -999     |  |

| 21      | SCL      | -2108    | -999     |  |

| 22      | SCL      | -2013    | -999     |  |

| 23      | SCL      | -1918    | -999     |  |

| 24      | SCL      | -1823    | -999     |  |

| 25      | SCL      | -1728    | -999     |  |

| 26      | SCL      | -1633    | -999     |  |

| 27      | SCL      | -1538    | -999     |  |

| 28      | SCL      | -1443    | -999     |  |

| 29      | VSS      | -893     | -999     |  |

| 30      | VSS      | -798     | -999     |  |

| 31      | VSS      | -703     | -999     |  |

| 32      | VSS      | -608     | -999     |  |

| 33      | VSS      | -513     | -999     |  |

| 34      | vss      | -418     | -999     |  |

| 35      | VSS      | -323     | -999     |  |

| 36      | VSS      | -228     | -999     |  |

| 37      | VSS      | -133     | -999     |  |

| 38      | VSS      | -38      | -999     |  |

| 39      | VSS      | 57       | -999     |  |

| 40      | SDA      | 607      | -999     |  |

| 41      | SDA      | 702      | -999     |  |

| 42      | SDA      | 797      | -999     |  |

| 43      | SDA      | 892      | -999     |  |

| 44      | SDA      | 987      | -999     |  |

| 45      | SDA      | 1082     | -999     |  |

| 45      | SDA      | 1177     | -999     |  |

|         |          |          | -999     |  |

| 47      | SDA      | 1272     |          |  |

| 48      | SDA      | 1367     | -999     |  |

| 49      | SDA      | 1462     | -999     |  |

| 50      | SDA      | 1557     | -999     |  |

|         |                | (Chip center | <u> </u> |  |

|---------|----------------|--------------|----------|--|

| PAD No. | Pad Name       | X = (um)     | Y = (um) |  |

| 51      | VDD            | 2107         | -999     |  |

| 52      | VDD            | 2202         | -999     |  |

| 53      | VDD            | 2297         | -999     |  |

| 54      | VDD            | 2392         | -999     |  |

| 55      | VDD            | 2487         | -999     |  |

| 56      | VDD            | 2582         | -999     |  |

| 57      | VDD            | 2677         | -999     |  |

| 58      | VDD            | 2772         | -999     |  |

| 59      | VDD            | 2867         | -999     |  |

| 60      | VDD            | 2962         | -999     |  |

| 61      | VDD            | 3057         | -999     |  |

| 62      | VLCD           | 3607         | -999     |  |

| 63      | VLCD           | 3702         | -999     |  |

| 64      | VLCD           | 3797         | -999     |  |

| 65      | VLCD           | 3892         | -999     |  |

| 66      | VLCD           | 3987         | -999     |  |

| 67      | VLCD           | 4082         | -999     |  |

| 68      | VLCD           | 4177         | -999     |  |

| 69      | VLCD           | 4272         | -999     |  |

| 70      | VLCD           | 4367         | -999     |  |

| . 71    | VLCD           | 4452         | -999     |  |

| 72      | VLCD           | 4557         | -999     |  |

| 73      | COM 33         | 4638         | -705     |  |

| 74      | COM 32         | 4638         | -625     |  |

| 75      | COM31          | 4638         | -545     |  |

| 76      | COM30          | 4638         | -465     |  |

| 77      | COM29          | 4638         | -385     |  |

| 78      | COM28          | 4638         | -305     |  |

| 79      | COM27          | 4638         | -225     |  |

| 80      | COM26          | 4638         | -145     |  |

| 81      | COM25          | 4638         | -65      |  |

| 82      | COM24          | 4638         | 15       |  |

| 83      | COM23          | 4638         | 95       |  |

| 84      | COM 22         | 4638         | 175      |  |

| 85      | COM21          | 4638         | 255      |  |

| 86      | COM21          | 4638         | 335      |  |

| 87      | COM 19         | 4638         | 415      |  |

| 88      | COM18          | 4638         | 495      |  |

| 89      | COM18          | 4638         | 575      |  |

| 90      | SEG 100        | 4030         | 998      |  |

| 90      | SEG 99         | 3946         | 998      |  |

| 92      | SEG 98         | 3866         | 998      |  |

| 92      | SEG90<br>SEG97 | 3786         | 998      |  |

|         |                |              | 998      |  |

| 94      | SEG96          | 3706         |          |  |

| 95      | SEG95          | 3626         | 998      |  |

| 96      | SEG94          | 3546         | 998      |  |

| 97      | SEG93          | 3466         | 998      |  |

| 98      | SEG92          | 3386         | 998      |  |

| 99      | SEG91          | 3306         | 998      |  |

| 100     | SEG90          | 3226         | 998      |  |

New Japan Radio Co., Ltd.

| PAD No. | PAD Name | X = (um) | Y = (um) |

|---------|----------|----------|----------|

| 101     | SEG89    | 3146     | 998      |

| 102     | SEG88    | 3066     | 998      |

| 103     | SEG87    | 2986     | 998      |

| 104     | SEG86    | 2906     | 998      |

| 105     | SEG85    | 2826     | 998      |

| 106     | SEG84    | 2746     | 998      |

| 107     | SEG83    | 2666     | 998      |

| 108     | SEG82    | 2586     | 998      |

| 109     | SEG81    | 2506     | 998      |

| 110     | SEG80    | 2426     | 998      |

| 111     | SEG79    | 2346     | 998      |

| 112     | SEG78    | 2266     | 998      |

| 113     | SEG77    | 2186     | 998      |

| 114     | SEG76    | 2106     | 998      |

| 115     | SEG75    | 2026     | 998      |

| 116     | SEG74    | 1946     | 998      |

| 117     | SEG73    | 1866     | 998      |

| 118     | SEG72    | 1786     | 998      |

| 119     | SEG71    | 1706     | 998      |

| 120     | SEG70    | 1626     | 998      |

| 120     | SEG69    | 1546     | 99.8     |

| 122     | SEG68    | 1466     | 998      |

| 123     | SEG67    | 1386     | 998      |

| 124     | SEG66    | 1306     | 998      |

| 125     | SEG65    | 1226     | 998      |

| 125     | SEG64    | 1146     | 998      |

| 128     | SEG 63   | 1066     | 998      |

| 127     | SEG62    | 986      | 998      |

|         |          |          | 998      |

| 129     | SEG61    | 906      |          |

| 130     | SEG60    | 826      | 998      |

| 131     | SEG59    | 746      | 998      |

| 132     | SEG58    | 666      | 998      |

| 133     | SEG57    | 586      | 998      |

| 134     | SEG56    | 506      | 998      |

| 135     | SEG55    | 426      | 998      |

| 136     | SEG54    | 346      | 998      |

| 137     | SEG53    | 266      | 998      |

| 138     | SEG52    | 186      | 998      |

| 139     | SEG51    | 106      | 998      |

| 140     | SEG50    | 26       | 998      |

| 141     | SEG49    | -54      | 998      |

| 142     | SEG48    | -134     | 998      |

| 143     | SEG47    | -214     | 998      |

| 144     | SEG46    | -294     | 998      |

| 145     | SEG45    | -374     | 998      |

| 146     | SEG44    | -454     | 998      |

| 147     | SEG43    | -534     | 998      |

| 148     | SEG42    | -614     | 998      |

| 149     | SEG41    | -694     | 998      |

| 150     | SEG40    | -774     | 998      |

JRC

| PAD No. | PAD Name     | X = (um)       | Y=(um) |

|---------|--------------|----------------|--------|

| 151     | SEG39        | -854           | 99     |

| 152     | SEG38        | -934           | 99     |

| 153     | SEG37        | -1014          | 99     |

| 154     | SEG36        | -1094          | 99     |

| 155     | SEG35        | -1174          | 99     |

| 156     | SEG34        | -1254          | 99     |

| 157     | SEG33        | -1334          | 99     |

| 158     | SEG32        | -1414          | 99     |

| 159     | SEG31        | -1494          | 99     |

| 160     | SEG30        | -1574          | 99     |

| 161     | SEG29        | -1654          | 99     |

| 162     | SEG28        | -1734          | 99     |

| 163     | SEG27        | -1814          | 99     |

| 164     | SEG26        | -1894          | 99     |

| 165     | SEG25        | -1974          | 99     |

| 166     | SEG24        | -2054          | 99     |

| 167     | SEG23        | -2134          | 99     |

| 168     | SEG22        | -2214          | 99     |

| 169     | SEG21        | -2294          | 99     |

| 170     | SEG20        | -2374          | . 99   |

| 171     | SEG19        | -2454          | 99     |

| 172     | SEG18        | -2534          | 99     |

| 173     | SEG17        | -2614          | 99     |

| 174     | SEG16        | -2694          | 99     |

| 175     | SEG15        | -2774          | 99     |

| 176     | SEG14        | -2854          | 99     |

| 177     | SEG13        | -2934          | 99     |

| 178     | SEG12        | -3014          | 99     |

| 179     | SEG11        | -3094          | 99     |

| 180     | SEG10        | -3174          | 99     |

| 181     | SEG9         | -3254          | 99     |

| 182     |              | -3334          | 99     |

|         | SEG8<br>SEG7 | -3334          | 99     |

| 183     |              |                |        |

| 184     | SEG6         | -3494<br>-3574 | 99     |

| 185     | SEG5         |                | 99     |

| 186     | SEG4         | -3654          | 99     |

| 187     | SEG3         | -3734          | 99     |

| 188     | SEG2         | -3814          | 99     |

| 189     | SEG1         | -3894          | 99     |

| 190     | SEGO         | -3974          | 99     |

| 191     | сомо         | -4639          | 57     |

| 192     | COM1         | -4639          | 49     |

| 193     | COM2         | -4639          | 41     |

| 194     | COM3         | -4639          | 33     |

| 195     | COM4         | -4639          | 25     |

| 196     | COM5         | -4639          | 17     |

| 197     | СОМ6         | -4639          | 9      |

| 198     | COM7         | -4639          | . 1    |

| 199     | COM8         | -4639          | -6     |

| 200     | СОМ9         | -4639          | -14    |

New Japan Radio Co., Ltd.

# NJU6576

# NJU6576

| PAD No. | PAD Name | X=(um) | Y=(um) |

|---------|----------|--------|--------|

| 201     | COM10    | -4639  | -228   |

| 202     | COM11    | -4639  | -308   |

| 203     | COM12    | -4639  | -388   |

| 204     | COM13    | -4639  | -468   |

| 205     | COM14    | -4639  | -548   |

| 206     | COM15    | -4639  | -628   |

| PAD No.   | PAD Name | X=(um) | Y=(um) |

|-----------|----------|--------|--------|

| 207       | COM16    | -4639  | -708   |

| ALIGNMENT | ALI_A1   | -4663  | -1023  |

| ALIGNMENT | ALI_A2   | 4662   | -1023  |

| ALIGNMENT | ALI_B3   | 4662   | 1002   |

| ALIGNMENT | ALI_B4   | -4663  | 1002   |

|           |          |        |        |

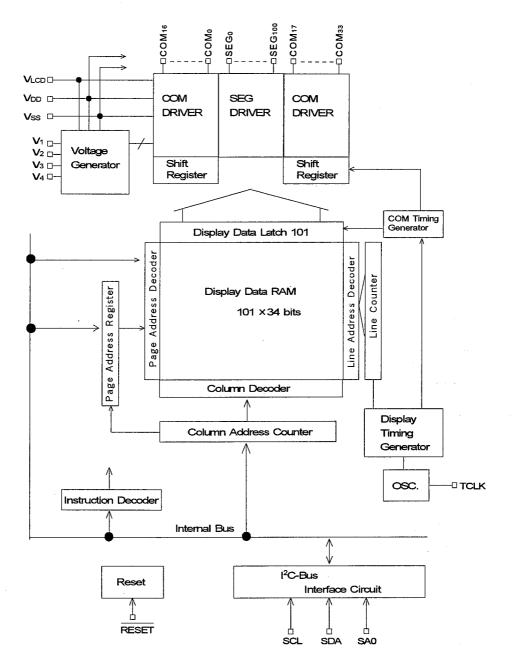

## BLOCK DIAGRAM

## TERMINAL DESCRIPTION

| PAD No.                 | Symbol                        | I/O   | Function                                                                                                                                                                          |

|-------------------------|-------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51 to 61                | VDD                           | POWER | Power supply                                                                                                                                                                      |

| 29 to 39                | Vss                           | POWER | GND                                                                                                                                                                               |

| 62 to 72                | VLCD                          | POWER | LCD driving voltage supply(VLco)                                                                                                                                                  |

| 6                       | V1                            |       | LCD driving voltage supply(V1 to V4)                                                                                                                                              |

| 5                       | V2                            |       |                                                                                                                                                                                   |

| 4                       | V3                            | POWER | In order to realize high quality display, the capacitors between V1, V2, V3, V4<br>and Vss are recommended. But if these capasitors are not needed, V1, V2, V3,                   |

| 3                       | V4                            |       | $V_4$ terminals should be open.                                                                                                                                                   |

| 1                       | RESET                         | Į     | Reset<br>When the reset signal "L" is input into this terminal, the reset operation is<br>performed.<br>In case this terminal is not used, it should be open or connected to Vod. |

| 18 to 28                | SCL                           | I     | Serial clock input                                                                                                                                                                |

| 40 to 50                | SDA                           | 1/0   | Serial data input                                                                                                                                                                 |

| 7 to 17                 | SA0                           | I     | External input address<br>SA0 terminal defines the slave address bit0 of NJU6576.<br>Fix SA0 terminal to Vod or Vss.                                                              |

| 73 to 89,<br>191 to 207 | COMo<br>to<br>COM33           |       | LCD driving outputs<br>- Common outputs<br>COM₀ to COM₃3 (Normal Display Mode: 1/34Duty)                                                                                          |

| 90 to 190               | O<br>SEG0<br>190 to<br>SEG100 |       | COMo to COM15, COM33(Normal Display Mode: 1/17Duty)<br>COM33 (Icon Mode : 1/1Duty)<br>- Segmnet outputs<br>SEGo to SEG100 (Normal Display/Icon Mode)                              |

| 2                       | TCLK                          | -     | Test terminal. Normaly open.                                                                                                                                                      |

New Japan Radio Co., Ltd.

## Functional Description

## (1-1) Line Counter

The Line Counter generates the line address of display data RAM by the count up operation synchronizing the common cycle after the reset operation at the status change of internal FR signal.

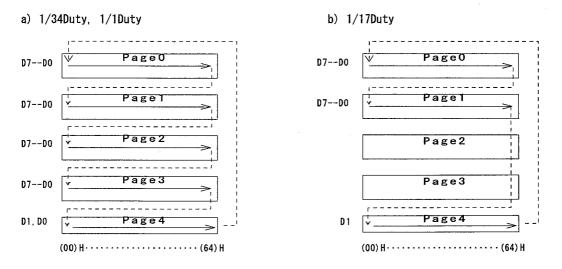

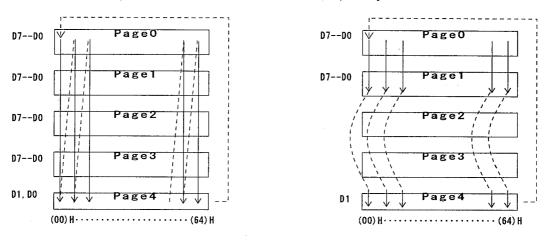

## (1-2) Column Address Counter/ Page Address Register

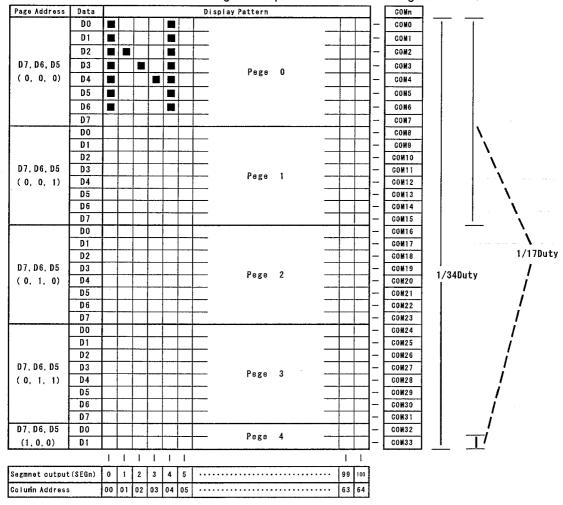

The column address counter is a pre-settable counter addressing the of display data RAM as shown in Fig. 2. The page register gives a page address of the display data RAM. "Increment mode select" command sets "column increment mode" or "page increment mode".

In the "column increment mode", the column address is auto-incremented (+1) whenever the display data byte is transferred, as shown in Fig.1-1. After the display data byte is written in the last column(64)H, the column address returns to(00)H and the page address is auto-incremented(+1).

In the "page increment mode", the page address is auto-incremented (+1) whenever the display data byte is transferred, as shown in Fig.1-2. After the display data byte is written in the page(4)H, the page address returns to page(0)H and the column address is auto-incremented(+1).

In both case of "column increment mode" and "page address mode", after the display data byte is written in the page (4)H and column(64)H, these addresses returns to the page(0)H and column (00)H.

The "page address set" and "column address set" command are required, when access by changing the page address and column address.

D7--D0 of page(2)H and page(3), and D0 of page(4) can not be accessed by MPU in 1/17Duty.

Fig.1-1 Auto-increment direction, in column increment mode.

a) 1/34Duty, 1/1Duty

b) 1/17duty

Fig.1-2 Auto-increment direction, in page increment mode.

New Japan Radio Co., Ltd.

## (1-3)Display Data RAM

Display Data RAM is the bit map RAM consisting of 3,434 bits to memorize the display data corresponding to each pixel of LCD panel. The each bit in the Display Data RAM corresponds to the each pixel of the LCD panel and controls the display by following bit data.

> When Normal Display : On="1", Off="0" When Inverse Display : On="0", Off="1"

The Display Data RAM outputs 101-bit parallel data in the area addressed by the line counter, and these data are set into the Display Data Latch.

The access operation from MPU to the display data RAM and the data output from the display data RAM are so controlled to operate independently that the data rewriting does not influence with any malfunctions to the display. The relation between column address and segment output terminals is shown in Fig. 2.

## Fig.2 Correspondence with Display data RAM and address

Note1) Correspondence with Duty and COM terminals

COM0 - COM33 COM0 - COM15, COM33 (Normal Display Mode COM33

(Normal Display Mode ( Icon Mode

: 1/34Duty) : 1/1Duty)

: 1/17Duty) \*1) D7--D0 of page(2)H, D7--D0 of page(3)H and D0 of page(4)H can not be accessed from MPU in 1/17Duty.

New Japan Radio Co., Ltd.

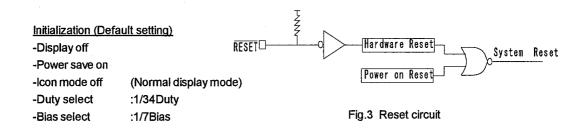

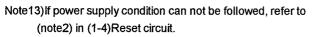

## (1-4)Reset Circuit

NJU6576 automatically executes the reset operation by the power on reset circuit when the external power supply is turned on. To work the power on reset circuit correctly, The "power supply condition" mentioned in the reset circuit characteristics should be kept.

To use the hardware reset operation after the external power supply is turned on, input the reset signal, which is "L" over than 10us, into the RESET terminal. And then the normal operation starts after 1us from the rise edge of reset signal.

Note2) If "power supply condition" mentioned in the reset characteristics can not be followed..... If "power supply condition" is not followed, the above-mentioned initialization functions might not be expected. For example, if "display on" and "power save off" are set by mistake, because of unstable COM/ SEG waveform output just after VLcD on, LCD display might be turned on for an instant. To avoid this phenomenon, set "display off" and "power save on" command before VLcD on.

## (1-5) LCD Driving

## (a)Oscillation Circuit

The Oscillation Circuit is a low power CR oscillator incorporating with Resistor and Capacitor. It generates clocks for display timing signal source.

## (b) LCD Driving Circuits

LCD driving circuits are consisted of 135 multiplexers which operate as 101-segment drivers and 34-common drivers. 34-common drivers with the shift register scan the common display signal. The combination of the Display data, COM scan signal and FR signal forms the LCD driving output voltage. The output wave form are shown in Fig.6 - Fig.9.

## (c) Display Data Latch Circuits

Display Data Latch stores 101-bit display data temporarily which is output to LCD driver circuits at a common cycle from the Display Data RAM addressed by Line Counter. The instructions of Display On/Off controls only the data in Display Data Latch, therefore, the data in the Display Data RAM is not changed.

## (d) Line Counter and Latch signal of Latch Circuits

The clock to Line Counter and latch signal to the Latch Circuits are generated from the internal display clock(CL). The line address of Display Data RAM is renewed synchronizing with display clock(CL). 101-bit display data are latched in display latch circuits synchronizing with display clock, and then output to the LCD driving circuits. The display data transfer to the LCD driving circuits is executed independently with RAM access by the MPU.

New Japan Radio Co., Ltd.

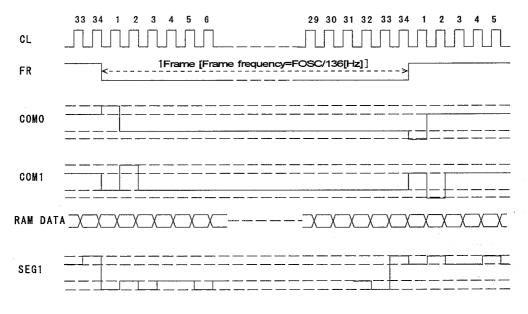

## (e) Display Timing Generator

Display Timing Generator generates the timing signal for the display system by combination of the master clock CL and Driving Signal FR (Refer to Fig.4). The Frame Signal FR and LCD alternative signal generate LCD driving waveform of the two frame alternative driving method.

## (f) Common Timing Generation

The common timing is generated by display clock CL. Refer to Fig.4.

Fig.4 Display Timing in 1/34Duty

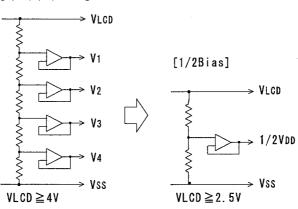

## (g) Power Supply Circuit

The internal Power Supply Circuit generates the bias voltage for the LCD driving waves. This circuit condition are changed by the NJU6576 state, such as the power save mode, normal display mode and icon mode, as shown in Table.1 and Fig.5.

This circuit is designed for small size LCD, not for large size LCD. In case of large size LCD, capacitors between V1, V2, V3, V4 and Vss should be connected in order to high quality display.

## Table.1

|             | Power supply circuit condition |

|-------------|--------------------------------|

| Power save  | All components stop            |

| Normal mode | 1/7(1/5) Bias                  |

| lcon·mode   | 1/2 Bias                       |

## \*1)

NJU6576 state, such as the power save mode, normal display mode and icon mode, is selected by the command.

## \*2)

Input each suitable VLCD voltage for the normal mode, for the icon mode. The following conditions should be maintained in each case.

-In normal display mode

-In icon mode

[1/7(1/5)Bias]

Fig.5 Power Supply Circuit

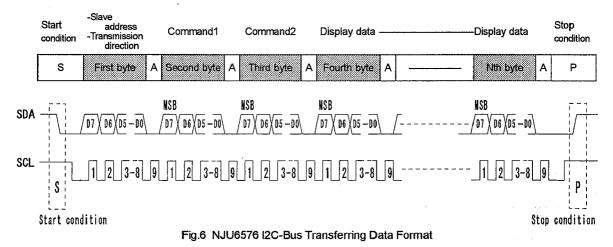

## Transferring data on the I<sup>2</sup>C-Bus

## 1)Transferring data format

NJU6576 transferring data can be supported by the first mode I<sup>2</sup>C-Bus. The serial data are transferred through SDA line and the serial clock is input through SCL line.

As the first byte, transfer the slave address of NJU6576 and the data direction . NJU6576 is only for slave LSI, and the data D0 in the first byte (at 8th bit timing) should be "0". As the second byte, transfer the command1 mentioned in (3-1), as the third byte, transfer the command2 in (3-2). After the fourth byte, transfer the display data.

NJU6576 outputs the acknowledge bit (A="0") after each byte, at 9th bit timing.

## 1-1)S:START condition

A rise edge of the SDA terminal while the SCL terminal is "H", which situation defines the START condition. After the START, NJU6576 starts reading the first byte.

## 1-2)P:STOP condition

A fall edge of the SDA terminal while the SCL terminal is "H", which situation defines the STOP condition. NJU6576 can read plural bytes continually until the STOP. After the STOP, it finishes reading data and holds previous state until the next START.

## 1-3)A:Acknowledge bit (A="0")

When NJU6576 acknowledges a coincidence its own address with the address information in the first byte, it outputs the Acknowledge just after the first byte(at 9th bit timing) through the SDA terminal.

After the second byte, whenever NJU6576 reads data correctly, it outputs the acknowledge at each 9th bit timing.

1-4)Definitions of each byte

- First byte :Slave address, Data direction

- Second byte :Command1

- Third byte :Command2

- Fourth byte :Display data

- Nth byte :Display data

New Japan Radio Co., Ltd.

2)Definition of the first byte :Slave address, Data direction

As the first byte, transfer the NJU6576 slave address and the data direction

The NJU6576 slave address is (D7--D1)=(0, 1, 1, 1, 0, 0, SA0). In this address, the data "D1(SA0)" is corresponded to the SA0 terminal state. NJU6576 is only for slave LSI, and the data D0(at 8th bit timing) in the first byte should be "0". If the data D0="1", NJU6576 does not output the acknowledge.

NJU6576 is not supported by the general call address. Therefore, if the data (D7--D1)=(0, 0, 0, 0, 0, 0, 0), NJU6576 does not output the acknowledge.

|   | MISB  |      |                                |     |     |     |     | LSB |  |

|---|-------|------|--------------------------------|-----|-----|-----|-----|-----|--|

|   | D 7   | D 6  | D 5                            | D 4 | D 3 | D 2 | D 1 | DO  |  |

|   | 0     | 1    | 1                              | 1   | 0   | 0   | SAO | 0   |  |

|   | Ļ     |      | Sla                            | +   | R/W |     |     |     |  |

|   | D7-D2 | : 0, | : 0,1,1,1,0,0                  |     |     |     |     |     |  |

|   | · D1  | : S/ | : SA0 (External input address) |     |     |     |     |     |  |

| - | D0    | : 0  |                                |     |     |     |     |     |  |

## 3)Explanation of Command1,2

3-1)Definition of the second byte :Command1

| MSB     |                                                                                      | -                 |          |     |            |        | LSB |                                  |  |

|---------|--------------------------------------------------------------------------------------|-------------------|----------|-----|------------|--------|-----|----------------------------------|--|

| D7      | D 6                                                                                  | D 5               | D 4      | D 3 | D 2        | D1     | DO  |                                  |  |

| - D7-D5 | : P                                                                                  | age add           | ress set |     |            |        |     |                                  |  |

| - D4    | : Bi                                                                                 | ias selec         | rt       |     |            |        |     |                                  |  |

| - D3    | : D                                                                                  | uty selec         | ct       | ٦,  | (loto1)    |        |     |                                  |  |

| - D2    | : Icon mode ON/OFF Note1)<br>The combination of the data, D3, D2 and D1, decides the |                   |          |     |            |        |     |                                  |  |

| - D1    | : P                                                                                  | ower sav          | /e ON/O  |     |            |        |     |                                  |  |

| - D0    | : D                                                                                  | isp <b>l</b> ay O | N/OFF    | l   | play state | and CO |     | nal condition. Refer to Table.2. |  |

## D0: Display ON/OFF

This command executes whole display ON/OFF, without relationship of the data in the Display Data RAM and internal condition.

D0=1:Display ON D0=0:Display OFF

The internal state of LSI in the display off is as follows;

- The oscillation circuit and internal power supply circuit are working.

- All COM/SEG terminals are fixed to Vss level.

- The display data and operation mode are kept as before the display off.

- The display data RAM can be accessed by MPU.

## D1: Power save ON/OFF

In the power save mode, the operating current can be reduced as same as the standby current.

## D1=1:Power save ON

D1=0:Power save OFF

The internal state of LSI in the power save mode is as follows;

- The oscillation circuit and internal power supply circuit stop.

- All COM/SEG terminals are fixed to Vss level.

- The display data and operation mode are kept as before the power save.

- The display data RAM can be accessed by MPU.

New Japan Radio Co., Ltd.

## D2: Icon mode ON/OFF

This command selects the normal display mode(bit map display) or icon mode. In the icon mode, NJU6576 can display 101 max static-icons.

| D2=1: Icon mode           | (Icon mode ON)  |

|---------------------------|-----------------|

| D2=0: Normal display mode | (Icon mode OFF) |

In the icon mode, the internal condition of LSI is as follows;

- All SEG and icon COM terminals are valid.

- Except the icon COM terminal, the other COM terminals output 1/2 VLcD level.

- The display data and operation mode are kept as before the power save.

- The display data RAM can be accessed from MPU.

## Note2)

To access the DDRAM efficiently during the icon mode, set "page address(4)H" by command1, "column increment mode" and "column address" by command2.

#### D3: Duty select

This command sets the duty ratio in the normal display mode, and in the icon mode.

| D3=1 :Norma<br>:lcon m  | I display mode<br>ode  | 1/34 duty<br>1/1 duty | (COM0COM33)<br>(COM33)        |            |  |

|-------------------------|------------------------|-----------------------|-------------------------------|------------|--|

| D3=0 :Norma<br>ilcon m: | ıl display mode<br>ode | 1/17 duty<br>1/1 duty | (COM0COM15, COM33)<br>(COM33) | da 10 - 11 |  |

Note3)Refer to table.2.

## D4: Bias select

This command sets the LCD bias ratio.

D4=1 :1/7 bias D4=0 :1/5 bias

#### Note4)

In the normal display mode, this command is valid.

In the icon mode, the ratio is fixed to 1/2 bias and 1/1Duty regardless of this command.

## D7-D5: Page address set

This command sets page address.

D7,D6,D5 = 0,0,0

:Page address(0)H

D7,D6,D5 = 0,0,1

:Page address(1)H

D7,D6,D5 = 0,1,0

:Page address(2)H

D7,D6,D5 = 0,1,1

:Page address(3)H

D7,D6,D5 = 1,0,0

:Page address(4)H

New Japan Radio Co., Ltd.

(Note1, 3)

The combination of the data, D3, D2 and D1, decides the display state and output terminals condition as shown in Table.2.

|  | -Table.2- | Display state and output terminals condition. |

|--|-----------|-----------------------------------------------|

|--|-----------|-----------------------------------------------|

|             | Command1            |                      |                 |                    |          |       |  |  |

|-------------|---------------------|----------------------|-----------------|--------------------|----------|-------|--|--|

| "D 3"       | "D2"                | "D1"                 | Display state   | COM/SEG termin     | rale     | Duty  |  |  |

| Duty Select | icon mode<br>ON/OFF | Power Save<br>ON/OFF |                 |                    |          | Buty  |  |  |

| *           | *                   | 1                    | Power save mode |                    |          |       |  |  |

| *           | 1                   |                      | lcon mode       | COM33 (*1)         | SEG0     | 1/1   |  |  |

| 1           | •                   | - O                  | Normal          | СОМ0 - СОМ33       | SEG100   | 1/34  |  |  |

| 0           | 0                   |                      | display mode    | COM0 - COM15,COM33 |          | 1/17  |  |  |

|             |                     |                      |                 |                    | *: Don't | care. |  |  |

\*1)Max.101 icons

\*2)Input each suitable VLCD voltage for the normal mode, for the icon mode. The following conditions should be maintained in each case.

-In normal display mode :VLCD ≧ 4V

-In icon mode :VLCD  $\geq 2.5V$

\*3)LCD driving waveform through the COM/SEG terminals are shown in Fig.12--Fig.14.

## 3-2)Definition of the third byte :command2

This byte sets the "increment mode select" and "column address" in the display data RAM.

MSB

|   | D7 | D6 | D 5 | D4 | D 3 | D 2 | D 1 | DO |  |

|---|----|----|-----|----|-----|-----|-----|----|--|

| • |    |    |     |    |     |     |     |    |  |

-D7: Increment mode select

D7=1 :Page increment mode

D7=0 :Column increment mode

Note5) Refer to functional description (1-2)

-D6-D0: Column address

D6,D5,D4,D3,D2,D1,D0 =0,0,0,0,0,0,0 D6,D5,D4,D3,D2,D1,D0 =0,0,0,0,0,0,1 :Column address (00)H :Column address (01)H

LSB

D6,D5,D4,D3,D2,D1,D0 =1,1,0,0,0,1,1 D6,D5,D4,D3,D2,D1,D0 =1,1,0,0,1,0,0 :Column address (63)H :Column address (64)H

4)Definition of the fourth byte :Display data

After the fourth byte, transfer the display data byte.

The column and page address auto-increment by the Display Data transfers. Therefore, NJU6576 can read plural bytes continually without these "address set" commands, until the STOP condition.

The correspondence with display data RAM and addresses are shown in Fig.2.

New Japan Radio Co., Ltd.

## Attention to "power supply on/off" and "power save off"

In case of connecting capacitors between V1, V2, V3, V4 and Vss, execute the following timing and wait-time at the power supply on/off and power save off. Unless these executions, LCD display might be turned on for an instant because of unstable COM/SEG waveform by charging(or discharging) these capacitors just after the power supply on/off and power save off. To avoid this phenomenon, these executions are required. In case of large size LCD panel, in spite of not connecting these capacitors, same phenomenon might be happened. In this case, execute them at the power supply on/off and power supply on

## 1)At the power supply on/off

VDD VDD VLCD VLCD Power save off Display on Display on (Command1) Power save off (Command1) Command (Command1) (Command1) Command Wait-time (note1) Wait-time (note1) Fig.7 Power supply on timing and Wait-time Fig.8 Power supply on timing and Wait-time Case1 Case2 VDD VLCD VLCD Power save or Display off (Cmmand1) (Command1) Command Command Fig.9 Power supply off timing Fig.10 Power supply off timing Case1 Case2

Execute Fig.7 or Fig.8 at power supply on, Fig.9 or Fig.10 at power supply off.

## Note1)

Wait-time is almost \*\*\*ms at capacitors C3=0.1uF, VDD=3V, VLcD=8V. Suitable wait-time depends on value of capacitor, VDD, VLcD. Therefore, practice a test with actual module.

Any commands except "display on" can be accepted during wait-time.

| 2)At the po | wer save off              |                              |                          |

|-------------|---------------------------|------------------------------|--------------------------|

| VDD         |                           |                              |                          |

| VLCD        |                           |                              |                          |

| Command     | Display off<br>(Command1) | Power save off<br>(Command1) | Display on<br>(Command1) |

Fig.11 Power save off timing

New Japan Radio Co., Ltd.

## ABSOLUTE MAXIMUM RATING

| PARAMETER             |      | SYMBOL | RATING       | UNIT |

|-----------------------|------|--------|--------------|------|

| Supply Voltage(1)     |      | VDD    | -0.3 ~ +7.0  | V    |

| Supply Voltage(2)     |      | VLCD   | -0.3 ~ +13.5 | V    |

| Input Voltage         |      | Vin    | -0.3 ~ +7.0  | V    |

| Oparating Temperature |      | Торя   | -30 ~ +80    | °C   |

| Storage               | ТСР  | T      | -55 ~ +100   | °C   |

| Temperature           | Chip | Тѕтс   | -55 ~ +125   | °C   |

Note 1) All voltage values are specified as Vss = 0 V.

Note 2) If the LSI are used on condition above the absolute maximum ratings, the LSI may be destroyed. Using the LSI within electrical characteristics is strongly recommended for normal operation. Use beyond the electric characteristics conditions will cause malfunction and poor reliability.

Note 3) The relation : VLCD  $\geq$  Vss must be maintained.

Note 4) Decoupling capacitor should be connected between VDD and Vss, VLcD and Vss due to the stabilized operation for the voltage converter.

| PARAN                       | IETER       | SYMBOL | CONDITIONS         |                     | MIN.       | TYP.     | MAX.     | UNIT | NOTE |

|-----------------------------|-------------|--------|--------------------|---------------------|------------|----------|----------|------|------|

| Operating                   | Recommend   | Vdd    |                    |                     |            | 3.0      | 3.3      | ٧    | 5    |

| Voltage(1)                  | Available   | VUU    |                    |                     | 2. 2       | -        | 5.5      | ٧    | 5    |

| Operating                   | Available   | VLCD   |                    | Normal display mode | 4.0        |          | 13. 5    | V    |      |

| Voltage(2)                  | Available   | VLOD   |                    | I con mode          | 2.5        |          | 13. 5    | ٧    |      |

| "H" input vo                | ltage       | Vih    | SCL, SDA termi     | nals                | O. 7Vdd    |          | Vdd      | V    |      |

| "L"input vo                 | ltage       | Vil    | SCL, SDA termi     | nals                | Vss        |          | O. 3VDD  | ٧    |      |

| Input leaka                 | to our ront | Пін    | SCL, SDA term.     | V1H=VDD             | -          | -        | 5        | uA   |      |

| Πρωτιθακαξ                  |             | l IL   | SCL, SDA term.     | Vil=Vss             | -          | -        | 5        | uA   |      |

| "L" output v                | oltage      | Vol    | SDA term. IO=3mA   |                     | -          | -        | Vss+0. 4 | ٧    |      |

| Hysteresis                  | voltage     | Vhys   | SCL terminal       |                     | 0. 05Vdd   | -        | -        | ٧    |      |

| Input capac                 | itance      | CIN    | SCL, SDA terminals |                     | -          | -        | 10       | pF   |      |

| Driver on-resistance        |             | Ron1   | COM/SEG term.      | 10=*uA, Vlcd=13. 5V | -          | 2.0      | 3.0      | kΩ   | 6    |

|                             | 5818Lance   | Ron2   | com/seu cerm.      | 10=*uA, VLCD=8V     | -          | 3.0      | 3.5      | kΩ   | U    |

| Standby curi                | rent        | l dda  | VDD term.          | Power save mode     |            | T. B. D. |          | uA   |      |

| Operating cu<br>logic(1)    | urrent for  | lod1   | VDD term.          | Normal display mode |            | T. B. D. |          | uA   |      |

| Operating cu<br>LCD driving |             | ILCD1  | VLCD term.         | VDD=3V, VLCD=8V     |            | T. B. D. |          | uA   | 7    |

| Operating cu<br>logic(2)    | urrent for  | l dd2  | VDD term.          | l con mode          | e T. B. D. |          |          | uA   |      |

| Operating cu<br>LCD driving |             | ILCD2  | VLCD term.         | VDD=3V, Vlcd=3V     | T. B. D.   |          |          | uA   |      |

| Oscillation                 | frequency   | Fosc   | Fosc term.         | VDD=3V, Ta=25°C     |            | T. B. D. |          | kHz  |      |

■ ELECTRICAL CHARACTERISTICS

VDD=3 ± 10%, Vss=0V, VLcD=8V, Ta=-20 ~ +75°C

Note5) NJU6576 operating voltage range is wide, but it is not guaranteed in immediate voltage change during access from MPU.

Note6) This characteristic is applied to resistances between VLcD terminal and each output terminal, and between VLcD terminal and each output terminal.

Note7) These characteristics are applied to operating current, in no access from MPU and SCL=SDA=Vss.

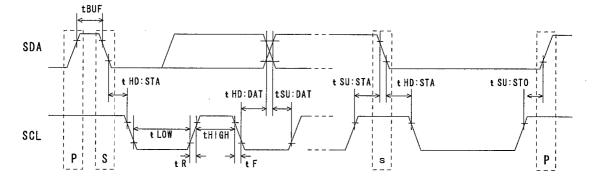

## I<sup>2</sup>C-BUS TIMING CHARACTERISTICS

VDD=3 ± 10%, Vss=0V, VLcD=8V, Ta=-20 ~ +75°C

| PARAMETER                    | SYMBOL  | MIN.         | MAX. | UNIT |

|------------------------------|---------|--------------|------|------|

| SCL clock frequency          | fscl    | 0            | 400  | kHz  |

| Bus free time                | tBUF    | 1.3          | _    | uS   |

| START condition hold time    | thd:STA | 0.6          |      | uS   |

| SCL"L" pulse width           | tlow    | 1.3          |      | uS   |

| SCL"H" pulse width           | thigh   | 0.6          | -    | uS   |

| START condition set -up time | tsu:STA | 0,6          | _    | uS   |

| Data hold time               | thd:DAT | 0            | 0.9  | uS   |

| Data set-up time             | tsu:DAT | 100          |      | nS   |

| Rise time                    | tr      | 20+0.1Cb(*1) | 300  | nS   |

| Fall time                    | tF      | 20+0.1Cb(*1) | 300  | nS   |

| STOP condition set-up time   | tsu:ST0 | 0.6          | _    | uS   |

Note8)Cb= total capacitance of one line bus(unit;pF).

Note9)Each timing is specified based on 0.3xVDD and 0.7xVDD.

## RESET CIRCUIT CHARACTERISTICS

-Input condition by hardware reset

| PARAMETER             | SYMBOL | CONDITIONS | MIN. | TYP. | MAX. | UNIT | NOTE |

|-----------------------|--------|------------|------|------|------|------|------|

| Resettime             | tr     | RESETterm. | 1.0  | -    | -    | uS   | 10   |

| Reset "L" pulse width | trw    | RESETterm. | 10   | -    | -    | uS   | 11   |

Note10) This characteristic specifies time from the rise edge of reset signal to the internal reset circuit operating finish.

Note11) This characteristic specifies minimum pulse width of reset signal "L" .

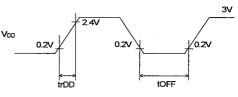

-Power supply condition by power on reset

| PARAMETER              | SYMBOL | CONDITIONS | MIN. | TYP. | MAX. | UNIT | NOTE |

|------------------------|--------|------------|------|------|------|------|------|

| Power supply rise time | trDD   |            | 0.5  | -    | 5    | mS   |      |

| Power supply off time  | t0FF   |            | 1    | -    | -    | mS   | 12   |

Note12)tOFF specifies the power off time in a shot period off or cycle on/off.

NJU6576

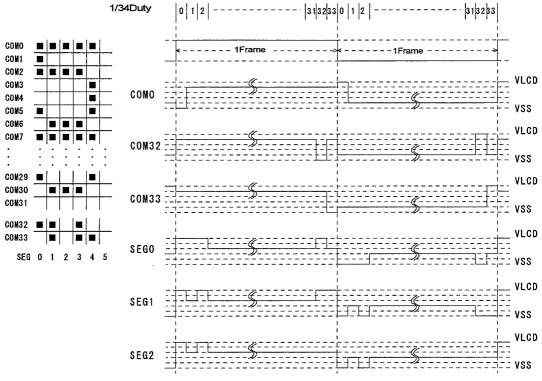

## LCD DRIVING WAVEFORM(1)

Frame frequency = Fosc / 136 [Hz]

Fig.12 COM/SEG waving forms in 1/34-duty, in the normal display mode.

New Japan Radio Co., Ltd.

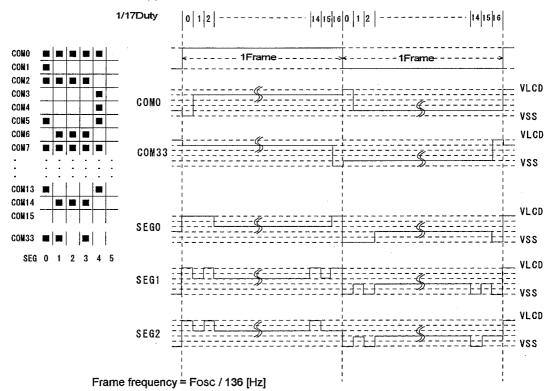

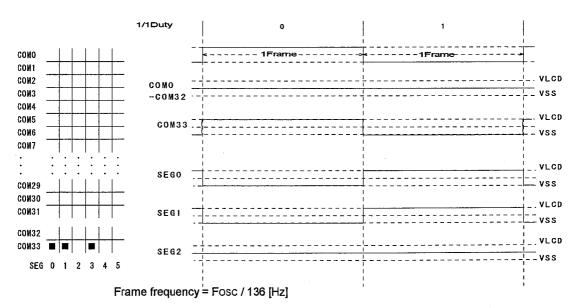

## LCD DRIVING WAVEFORM(2)

Fig.13 COM/SEG waving forms in 1/17duty, in the normal display mode.

Fig.14 COM/SEG waving forms in 1/1-duty, in the Icon mode.

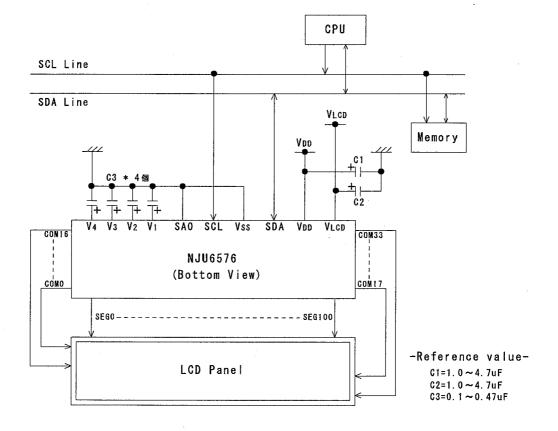

## ■APPLICATION CIRCUIT

Fig.15 Typical application circuit

Note1) In order to stabilize LSI operation, the capacitors between VDD-VSs and between VLcD-VSs are required. Note2) In order to realize high quality display, the capacitor between V1, V2, V3, V4 and Vss are recommended.

In case these capacitors are not needed, V1, V2, V3, V4 terminals are open.

Note3) SA0 terminal state decides NJU6576 slave address bit0. Fix this terminal to VDD or Vss.

## MEMO

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.