New Japan Radio Co., Ltd.

- 2.4V to 3.6V (Except For LCD Driving Voltage)

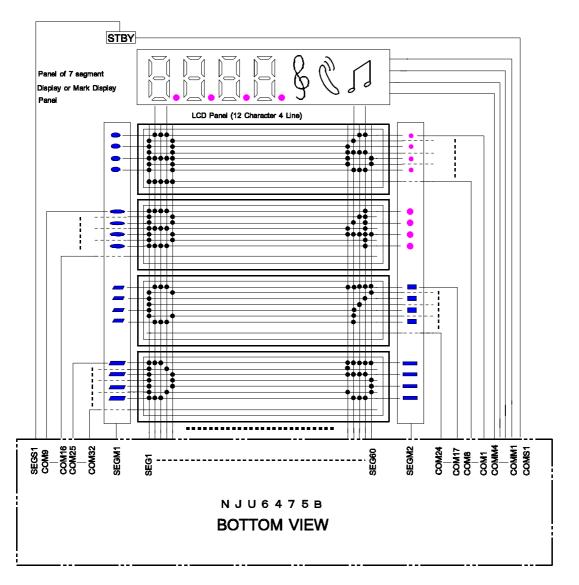

- 48 x 8 Bits :Maximum 12-Character 4-Line Display

- 10,080 Bits:252 Characters (5 x 8 Dots)

- 32 x 5 Bits :4 Patterns (5 x 8 Dots)

- 32 x 5 Bits :Maximum 128-Icon

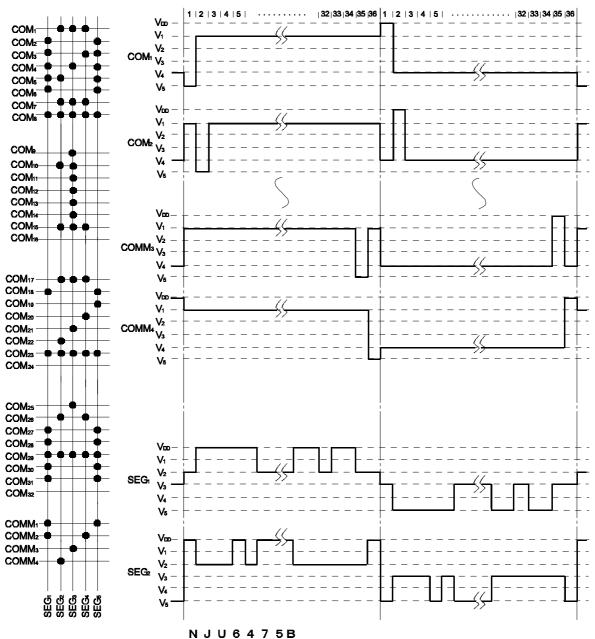

: 37-Common/63-Segment

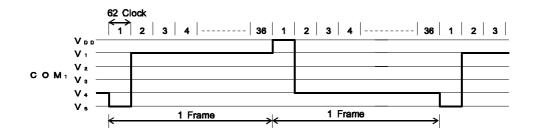

: 1/36 duty 1/7Bias

- Bumped-Chip / TCP

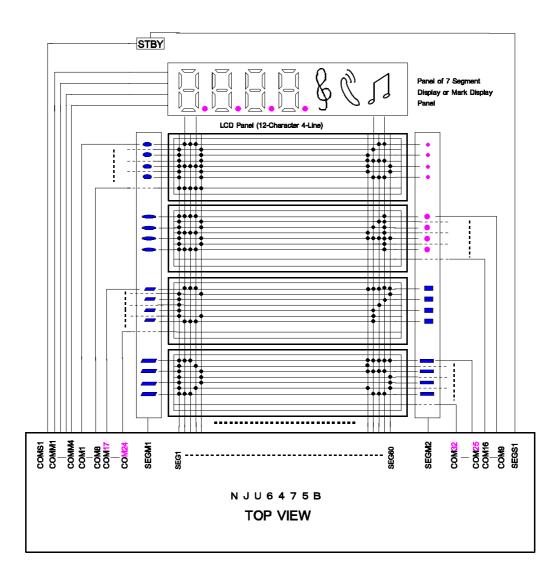

## 12-Character 4-Line Dot Matrix Low Power

LCD Controller Driver with key Scan Function

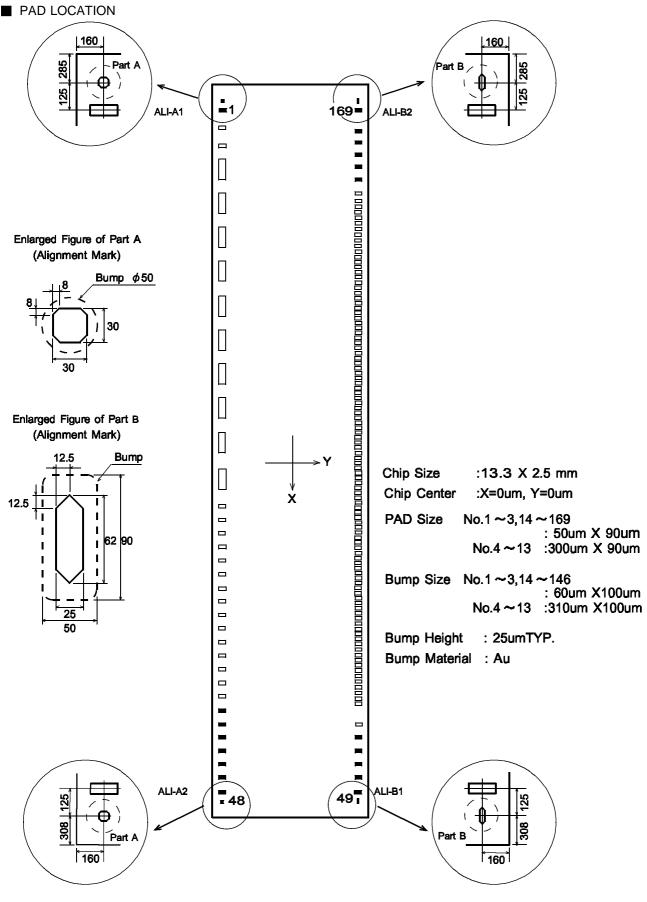

PACKAGE OUTLINE

## GENERAL DESCRIPTION

The NJU6475B is a Dot Matrix LCD Controller Driver for 12-character 4-line with Icon display in single chip. It contains voltage converter, voltage regulator, bleeder resistance, CR oscillator, instruction decoder, character generator ROM/RAM, high voltage operation controller/driver and key scan circuit.

The voltage converter generates (about 8V) from the supply voltage (3V) and regulated by the regulator. The bias level of LCD driving voltage is generated of high value bleeder resistance and the buffer amplifier matches the impedance. 16-step contrast control function is incorporated for its adjustment. Therefore, simple power supply circuit and easy contrast adjustment are available. The complete CR oscillator is incorporated without external components for oscillation circuit. The microprocessor interface circuit which operates by 1MHz, can be selected serial interface.

The character generator ROM consisting of 10,080bits stores 252 kinds of character Font.

Each 160bits CG RAM and Icon display RAM can story 4 kinds of special character to display on the dot matrix display area or 128 kinds of Icon on the display area.

## FEATURES

- •12-Character 4-Line Dot Matrix LCD Controller Driver

- Maximum 128-Icon Display

- •Serial CPU Interface

- Display Data RAM

- •Character Generator ROM

- •Character Generator RAM

- Icon Display RAM

- •High Voltage LCD Driver

- Duty & Bias Ratio

- •Useful Instruction Set

- : Clear Display, Return Home, Display On/Off Control Display Blink, Cursor Shift, Character Shift Common and Segment Driver location Order Select Function (Mode-A, Mode-B)

- Power On Reset Circuit On Chip

- Hardware Reset

- Voltage Regulator On Chip

- •Electrical Variable Resistance On Chip

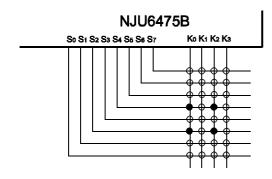

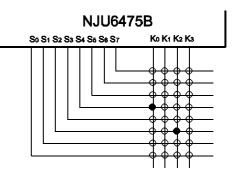

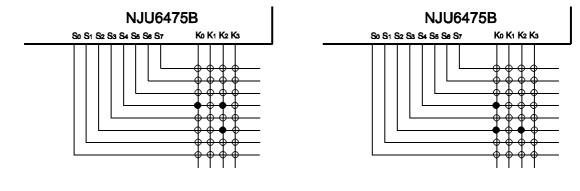

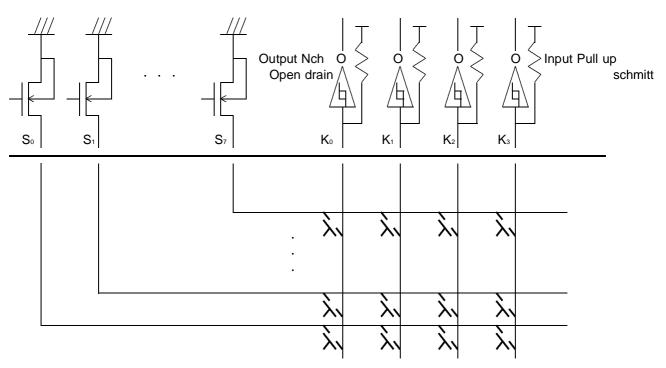

- 32-key scan function (8 x 4 Matrix)

- Oscillation circuit On Chip

- Voltage Converter (Doubler, Tripler) On Chip

- •Bleeder Resistance On Chip

- •Low Oprating Current

- Operating Voltage

- Package Outline

- C-MOS Technology

NJU6475B

# NJU6475B

New Japan Radio Co., Ltd.

## PAD COORDINATES

|                 | PAD                   | Name                  |            |        |          | PAD               | n (Chip Cent<br>Name |        |        |

|-----------------|-----------------------|-----------------------|------------|--------|----------|-------------------|----------------------|--------|--------|

| PAD No.         | Mode A                | Mode B                | X=(um)     | Y=(um) | PAD No.  | Mode A            | Mode B               | X=(um) | Y=(um) |

| 1               | ALI-A1                | ALI-A1                | -6240      | -1090  | 51       | NC                | NC                   | 5817   | 1090   |

| 2               | OSC1                  | OSC1                  | -6020      | -1090  | 52       | NC                | NC                   | 5617   | 1090   |

| 3               |                       |                       | -5775      | -1090  | 53       | NC                | NC                   | 5417   | 1090   |

| 4               | V <sub>5</sub>        | V <sub>5</sub>        | -5479      | -1090  | 54       | NC                | NC                   | 5217   | 1090   |

| 5               | Vss                   | Vss                   | -4979      | -1090  | 55       | NC                | NC                   | 5017   | 1090   |

| 6               | V 33                  | V <sub>50UT</sub>     | -4479      | -1090  | 56       | NC                | NC                   | 4817   | 1090   |

| 7               | C2                    | C2                    | -3979      | -1090  | 57       | NC                | NC                   | 4617   | 1090   |

| 8               | C2⁺                   | C2⁺                   | -3479      | -1090  | 58       | NC                | NC                   | 4417   | 1090   |

| 9               | C1 <sup>-</sup>       | C1 <sup>°</sup>       | -2979      | -1090  | 59       | NC                | NC                   | 4217   | 1090   |

| 10              | C1⁺                   | C1 <sup>+</sup>       | -2479      | -1090  | 60       | NC                | NC                   | 4017   | 1090   |

| 10              | VDD                   | VDD                   | -1979      | -1090  | 61       | NC                | NC                   | 3817   | 1090   |

| 12              | VR                    | VR                    | -1479      | -1090  | 62       | NC                | NC                   | 3617   | 1090   |

| 12              | VIX                   | VIX                   | - 979      | -1090  | 63       | NC                | NC                   | 3417   | 1090   |

| 13              | TEST                  |                       | - 531      | -1090  | 64       | SEGS1             | SEGS1                | 3160   | 1090   |

|                 | SEL                   | SEL                   | - 302      | -1090  |          |                   | COM9                 | 2780   | 1090   |

| 15              |                       |                       |            |        | 65       |                   |                      |        |        |

| <u>16</u><br>17 | RESET                 | RESET                 |            | -1090  | 66<br>67 |                   |                      | 2700   | 1090   |

|                 | P/S<br>RS             | P/S<br>RS             | 155<br>383 | -1090  |          |                   |                      | 2620   | 1090   |

| 18              |                       |                       |            | -1090  | 68       |                   |                      | 2540   | 1090   |

| 19              | R/W                   | R/W                   | 612        | -1090  | 69       |                   |                      | 2460   | 1090   |

| 20              | E/SCL                 | E/SCL                 | 840        | -1090  | 70       |                   |                      | 2380   | 1090   |

| 21              | LCD/KEY               | LCD/KEY               | 1069       | -1090  | 71       |                   |                      | 2300   | 1090   |

| 22              | REQ                   | REQ                   | 1298       | -1090  | 72       |                   |                      | 2220   | 1090   |

| 23              | DB7/CS                | DB7/CS                | 1536       | -1090  | 73       | COM <sub>25</sub> | COM <sub>25</sub>    | 2140   | 1090   |

| 24              | DB6/SIO               | DB6/SIO               | 1773       | -1090  | 74       |                   | COM <sub>26</sub>    | 2060   | 1090   |

| 25              | DB₅                   | DB₅                   | 2010       | -1090  | 75       | COM <sub>27</sub> | COM <sub>27</sub>    | 1980   | 1090   |

| 26              | DB4                   | DB4                   | 2247       | -1090  | 76       | COM <sub>28</sub> | COM <sub>28</sub>    | 1900   | 1090   |

| 27              | DB₃                   | DB <sub>3</sub>       | 2484       | -1090  | 77       | COM <sub>29</sub> | COM <sub>29</sub>    | 1820   | 1090   |

| 28              | DB <sub>2</sub>       | DB <sub>2</sub>       | 2721       | -1090  | 78       |                   |                      | 1740   | 1090   |

| 29              | DB <sub>1</sub>       | DB1                   | 2958       | -1090  | 79       |                   |                      | 1660   | 1090   |

| 30              | DB                    | DB₀                   | 3195       | -1090  | 80       | COM <sub>32</sub> | COM <sub>32</sub>    | 1580   | 1090   |

| 31              | K₀                    | K₀                    | 3466       | -1090  | 81       | SEGM1             | SEGM <sub>2</sub>    | 1500   | 1090   |

| 32              | K <sub>1</sub>        | K <sub>1</sub>        | 3632       | -1090  | 82       | SEG <sub>1</sub>  | SEG <sub>60</sub>    | 1420   | 1090   |

| 33              | K <sub>2</sub>        | <b>K</b> <sub>2</sub> | 3903       | -1090  | 83       | SEG <sub>2</sub>  | SEG <sub>59</sub>    | 1340   | 1090   |

| 34              | K₃                    | K₃                    | 4068       | -1090  | 84       | SEG₃              | SEG <sub>58</sub>    | 1260   | 1090   |

| 35              | S₀                    | S₀                    | 4244       | -1090  | 85       | SEG <sub>4</sub>  | SEG <sub>57</sub>    | 1180   | 1090   |

| 36              | S1                    | S1                    | 4352       | -1090  | 86       | SEG₅              | SEG <sub>56</sub>    | 1100   | 1090   |

| 37              | <b>S</b> <sub>2</sub> | <b>S</b> <sub>2</sub> | 4460       | -1090  | 87       | SEG <sub>6</sub>  | SEG <sub>55</sub>    | 1020   | 1090   |

| 38              | S₃                    | S₃                    | 4568       | -1090  | 88       | SEG7              | SEG <sub>54</sub>    | 940    | 1090   |

| 39              | <b>S</b> <sub>4</sub> | <b>S</b> <sub>4</sub> | 4676       | -1090  | 89       | SEG₃              | SEG <sub>53</sub>    | 860    | 1090   |

| 40              | S₅                    | S₅                    | 4784       | -1090  | 90       | SEG               | SEG <sub>52</sub>    | 780    | 1090   |

| 41              | S <sub>6</sub>        | S <sub>6</sub>        | 4892       | -1090  | 91       | SEG <sub>10</sub> | SEG <sub>51</sub>    | 700    | 1090   |

| 42              | <b>S</b> 7            | <b>S</b> 7            | 5000       | -1090  | 92       | SEG11             | SEG <sub>50</sub>    | 620    | 1090   |

| 43              | NC                    | NC                    | 5217       | -1090  | 93       | SEG <sub>12</sub> | SEG <sub>49</sub>    | 540    | 1090   |

| 44              | NC                    | NC                    | 5417       | -1090  | 94       | SEG <sub>13</sub> | SEG <sub>48</sub>    | 460    | 1090   |

| 45              | NC                    | NC                    | 5617       | -1090  | 95       | SEG <sub>14</sub> | SEG <sub>47</sub>    | 380    | 1090   |

| 46              | NC                    | NC                    | 5817       | -1090  | 96       | SEG <sub>15</sub> | SEG <sub>46</sub>    | 300    | 1090   |

| 47              | NC                    | NC                    | 6017       | -1090  | 97       | SEG <sub>16</sub> | SEG <sub>45</sub>    | 220    | 1090   |

| 48              | ALI-A2                | ALI-A2                | 6217       | -1090  | 98       | SEG <sub>17</sub> | SEG <sub>44</sub>    | 140    | 1090   |

| 49              | ALI-B2                | ALI-B2                | 6217       | 1090   | 99       | SEG <sub>18</sub> | SEG <sub>43</sub>    | 60     | 1090   |

| 50              | NC                    | NC                    | 6017       | 1090   | 100      | SEG <sub>19</sub> | SEG <sub>42</sub>    | - 20   | 1090   |

- New Japan Radio Co.,Ltd. -

## NJU6475B

| PAD No. | PAD               | Name              | V (um) | V (um) | PAD No. | PAD               | Name              | V (um) | V (um) |

|---------|-------------------|-------------------|--------|--------|---------|-------------------|-------------------|--------|--------|

| PAD NO. | Mode A            | Mode B            | X=(um) | Y=(um) | PAD NO. | Mode A            | Mode B            | X=(um) | Y=(um) |

| 101     | SEG <sub>20</sub> | SEG <sub>41</sub> | - 100  | 1090   | 135     | SEG <sub>54</sub> | SEG7              | -2820  | 1090   |

| 102     | SEG <sub>21</sub> | SEG <sub>40</sub> | - 180  | 1090   | 136     | SEG <sub>55</sub> | SEG <sub>6</sub>  | -2900  | 1090   |

| 103     | SEG <sub>22</sub> | SEG <sub>39</sub> | - 260  | 1090   | 137     | SEG <sub>56</sub> | SEG₅              | -2980  | 1090   |

| 104     | SEG <sub>23</sub> | SEG <sub>38</sub> | - 340  | 1090   | 138     | SEG <sub>57</sub> | SEG <sub>4</sub>  | -3060  | 1090   |

| 105     | SEG <sub>24</sub> | SEG <sub>37</sub> | - 420  | 1090   | 139     | SEG <sub>58</sub> | SEG₃              | -3140  | 1090   |

| 106     | SEG <sub>25</sub> | SEG <sub>36</sub> | - 500  | 1090   | 140     | SEG <sub>59</sub> | SEG <sub>2</sub>  | -3220  | 1090   |

| 107     | SEG <sub>26</sub> | SEG <sub>35</sub> | - 580  | 1090   | 141     | SEG <sub>60</sub> | SEG1              | -3300  | 1090   |

| 108     | SEG <sub>27</sub> | SEG <sub>34</sub> | - 660  | 1090   | 142     | SEGM <sub>2</sub> | SEGM1             | -3380  | 1090   |

| 109     | SEG <sub>28</sub> | SEG <sub>33</sub> | - 740  | 1090   | 143     | COM <sub>24</sub> | COM <sub>24</sub> | -3460  | 1090   |

| 110     | SEG <sub>29</sub> | SEG <sub>32</sub> | - 820  | 1090   | 144     | COM <sub>23</sub> | COM <sub>23</sub> | -3540  | 1090   |

| 111     | SEG <sub>30</sub> | SEG <sub>31</sub> | - 900  | 1090   | 145     | COM <sub>22</sub> | COM <sub>22</sub> | -3620  | 1090   |

| 112     | SEG <sub>31</sub> | SEG <sub>30</sub> | - 980  | 1090   | 146     | COM <sub>21</sub> | COM <sub>21</sub> | -3700  | 1090   |

| 113     | SEG <sub>32</sub> | SEG <sub>29</sub> | -1060  | 1090   | 147     | COM <sub>20</sub> | COM <sub>20</sub> | -3780  | 1090   |

| 114     | SEG <sub>33</sub> | SEG <sub>28</sub> | -1140  | 1090   | 148     | COM <sub>19</sub> | COM <sub>19</sub> | -3860  | 1090   |

| 115     | SEG <sub>34</sub> | SEG <sub>27</sub> | -1220  | 1090   | 149     | COM <sub>18</sub> | COM <sub>18</sub> | -3940  | 1090   |

| 116     | SEG <sub>35</sub> | SEG <sub>26</sub> | -1300  | 1090   | 150     | COM <sub>17</sub> | COM <sub>17</sub> | -4020  | 1090   |

| 117     | SEG <sub>36</sub> | SEG <sub>25</sub> | -1380  | 1090   | 151     | COM <sup>8</sup>  | COM <sup>8</sup>  | -4100  | 1090   |

| 118     | SEG <sub>37</sub> | SEG <sub>24</sub> | -1460  | 1090   | 152     | COM <sub>7</sub>  | COM <sub>7</sub>  | -4180  | 1090   |

| 119     | SEG <sub>38</sub> | SEG <sub>23</sub> | -1540  | 1090   | 153     |                   |                   | -4260  | 1090   |

| 120     | SEG <sub>39</sub> | SEG <sub>22</sub> | -1620  | 1090   | 154     | COM <sup>5</sup>  | COM <sub>5</sub>  | -4340  | 1090   |

| 121     | SEG <sub>40</sub> | SEG <sub>21</sub> | -1700  | 1090   | 155     | COM <sub>4</sub>  | COM <sub>4</sub>  | -4420  | 1090   |

| 122     | SEG <sub>41</sub> | SEG <sub>20</sub> | -1780  | 1090   | 156     | COM <sub>3</sub>  | COM <sub>3</sub>  | -4500  | 1090   |

| 123     | SEG <sub>42</sub> | SEG <sub>19</sub> | -1860  | 1090   | 157     | COM <sub>2</sub>  | COM <sub>2</sub>  | -4580  | 1090   |

| 124     | SEG <sub>43</sub> | SEG <sub>18</sub> | -1940  | 1090   | 158     |                   |                   | -4660  | 1090   |

| 125     | SEG <sub>44</sub> | SEG <sub>17</sub> | -2020  | 1090   | 159     | COMM <sub>4</sub> | COMM <sub>4</sub> | -4740  | 1090   |

| 126     | SEG <sub>45</sub> | SEG <sub>16</sub> | -2100  | 1090   | 160     | COMM <sub>3</sub> | COMM₃             | -4820  | 1090   |

| 127     | SEG <sub>46</sub> | SEG <sub>15</sub> | -2180  | 1090   | 161     | COMM <sub>2</sub> | COMM <sub>2</sub> | -4900  | 1090   |

| 128     | SEG <sub>47</sub> | SEG <sub>14</sub> | -2260  | 1090   | 162     | COMM <sub>1</sub> | COMM <sub>1</sub> | -4980  | 1090   |

| 129     | SEG <sub>48</sub> | SEG <sub>13</sub> | -2340  | 1090   | 163     | COMS <sub>1</sub> | COMS <sub>1</sub> | -5085  | 1090   |

| 130     | SEG <sub>49</sub> | SEG <sub>12</sub> | -2420  | 1090   | 164     | NC                | NC                | -5285  | 1090   |

| 131     | SEG <sub>50</sub> | SEG <sub>11</sub> | -2500  | 1090   | 165     | NC                | NC                | -5485  | 1090   |

| 132     | SEG <sub>51</sub> | SEG <sub>10</sub> | -2580  | 1090   | 167     | NC                | NC                | -5885  | 1090   |

| 133     | SEG <sub>52</sub> | SEG <sub>9</sub>  | -2660  | 1090   | 168     | NC                | NC                | -6085  | 1090   |

| 134     | SEG <sub>53</sub> | SEG <sub>8</sub>  | -2740  | 1090   | 169     | ALI-B2            | ALI-B2            | -6240  | 1090   |

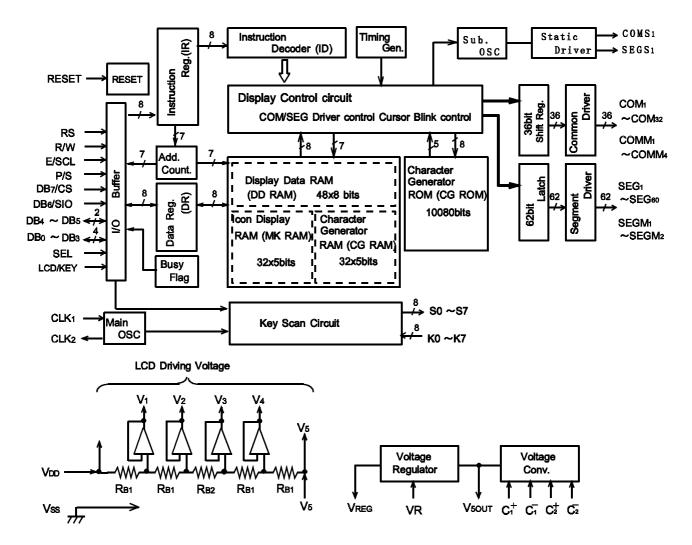

## BLOCK DIAGRAM

## ■ TERMINAL DESCRIPTION

| PAD No.                                      | Symbol           | I/O | Function                                                                                                                                                        |

|----------------------------------------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11,5                                         | Vdd,Vss          | -   | Power Source : VDD=+3V GND : VSS=0V                                                                                                                             |

| 4                                            | V <sub>5</sub>   | -   | LCD driving voltage                                                                                                                                             |

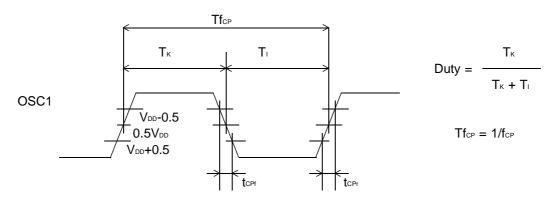

| 2,3                                          | OSC1,<br>OSC2    | I/O | System clock terminal<br>Oscillation C and R are incorporated. (Normally Open)<br>For external clock operation, the clock should be input on OSC <sub>1</sub> . |

| 17                                           | P/S              | I   | Serial input select terminal (fixed to "L")                                                                                                                     |

| 18                                           | RS               | I   | Register selection signal input terminal<br>"0" instruction register. (Writing)<br>"1" Data register. (Writing, Reading)                                        |

| 19                                           | R/W              | I   | Read(R) / Write(W) selection signal input terminal                                                                                                              |

| 20                                           | E/SCL            | Ι   | Serial clock input terminal                                                                                                                                     |

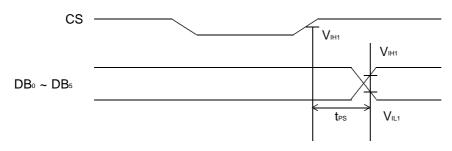

| 23                                           | DB7/CS           | I   | Chip select signal                                                                                                                                              |

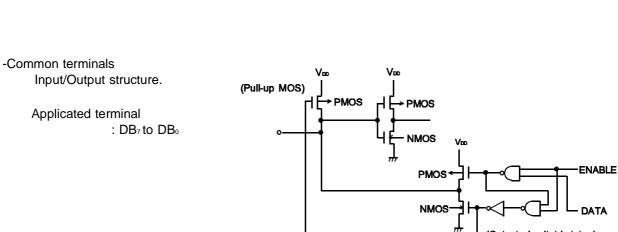

| 24                                           | DB6/SIO          | I/O | Data input terminal (3-state data bus.)                                                                                                                         |

| 25 - 30                                      | DB₀ - DB₅        | I   | I/O port output terminal                                                                                                                                        |

| 22                                           | REQ              | 0   | This terminal normally output "L".<br>When confirm a key action, REQ terminal output puls.                                                                      |

| 21                                           | LCD/KEY          | I   | Fix to "H" Level                                                                                                                                                |

| 35 - 42                                      | S₀-S7            | 0   | Key scan signal data output terminal<br>Open Drain Output                                                                                                       |

| 31 - 34                                      | K0 - K3          | I   | Key scan data input terminal<br>In case of non use, fix to "H".                                                                                                 |

| 158 - 151<br>65 - 72<br>150 - 143<br>73 - 80 | COM1 - COM32     | 0   | Common signal output terminal                                                                                                                                   |

| 162 - 159                                    | COMM1 -<br>COMM4 | 0   | Icon common display signal output terminal                                                                                                                      |

| 163                                          | COMS1            | 0   | Static driving common signal output terminal When power down mode $V_{\text{DD}}$ or $V_{\text{SS}}$ levels are output.                                         |

| 82 - 141                                     | SEG1 - SEG60     | 0   | Segment signal output terminal                                                                                                                                  |

| 81,142                                       | SEGM1,SEGM2      | 0   | Icon segment driving signal output terminal                                                                                                                     |

- New Japan Radio Co.,Ltd. -

| PAD No.                         | Symbol                                                              | I/O | Function                                                                                                                                            |

|---------------------------------|---------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 57                              | SEGS1                                                               | 0   | Static driving segment signal output terminal When power down mode $V_{\text{DD}}$ or $V_{\text{SS}}$ level are output.                             |

| 10,9<br>8,7                     | C1 <sup>+</sup> C1 <sup>-</sup><br>C2 <sup>+</sup> ,C2 <sup>-</sup> | I/O | Step up voltage capacitor connecting terminal                                                                                                       |

| 6                               | V50UT                                                               | 0   | Step up voltage output terminal                                                                                                                     |

| 13                              | Vreg                                                                | 0   | Voltage regulator output terminal<br>Connect the resistor between this terminal and VR terminal.                                                    |

| 12                              | VR                                                                  | I   | Reference voltage for voltage regulator input terminal Connect the resistor between this reference voltage and $V_{\text{DD}}$ terminal.            |

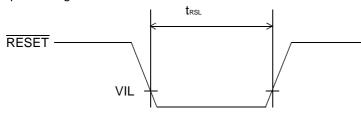

| 16                              | RESET                                                               | I   | Reset terminal When the "L" level input over than 1.2ms to this terminal, the system is reset (at $f_{osc}$ =180KHz).                               |

| 15                              | SEL                                                                 | I   | Common and Segment driver location order select terminal.<br>"0" Mode A location (See PAD COORDINATES)<br>"1" Mode B location (See PAD COORDINATES) |

| 14                              | TEST                                                                | I   | Maker test terminal This terminal should be connected to $V_{ss}$ (or open.)                                                                        |

| 43 - 47<br>50 - 63<br>164 - 168 | NC                                                                  | -   | Non connection terminal<br>These terminals are electrically open.                                                                                   |

| 169<br>49<br>1<br>48            | ALI-A1<br>ALI-A2<br>ALI-B1<br>ALI-B2                                | -   | Alignment mark<br>These terminals are electrically open.                                                                                            |

## ■ FUNCTIONAL DESCRIPTION

#### (1) Description for each blocks

#### (1-1) Register

The NJU6475B incorporates three 8-bit registers, an instruction register (IR), and a Data Register (DR), Key Register (KR). The register (IR) stores an instruction code such as "clear display" and "cursor shift" or address data for Display Data RAM (DD RAM), Character Generator RAM (CG RAM) and Icon Display RAM (MK RAM). The MPU can write the instruction code and address data to the register (IR), but it cannot read out from register (IR). The Register (DR) is a temporary register, the data stored in the Register (DR) is written into DD RAM, MK RAM. A register from these two registers is selected by the register select signal (RS). Register (KR) is an only temporary register for key scan data. This Register (KR) can read out the contents when selected Key signal at "H" signal. And non relation ship with signal of register select (RS).

The Relation ship with RS, R/W register as shown below.

| RS | R/W | Operation                                                                   |

|----|-----|-----------------------------------------------------------------------------|

| 0  | 0   | IR write & internal register operation mode<br>(Clear Display etc)          |

| 0  | 1   | Read out (KR)                                                               |

| 1  | 0   | Write (DR) & internal register operation mode<br>(DR→ DD RAM/CG RAM/MK RAM) |

| 1  | 1   | Read out (KR)                                                               |

#### <Table-1> Register selection

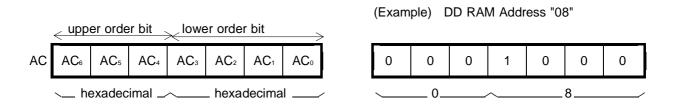

## (1-2) Address Counter (AC)

The address counter (AC) addresses the DD RAM, CG RAM or MK RAM. When the address setting instruction is written into register (IR), the address information is transferred from register (IR) to the address counter (AC). The selection of DD RAM, CG RAM or MK RAM is also determined by this instruction.

After writing (or reading) the display data to (or from) the DD RAM, CG RAM or MK RAM, the address counter (AC) increments (or decrements) automatically.

## (1-3) Display Data RAM (DD RAM)

The display data RAM (DD RAM) consisting of 48 x 8 bits stores up to 48-character display data represented in 8-bit code.

The DD RAM address data set in the address counter (AC) is represented in Hexadecimal code.

(1-3-1) The relation between DD RAM address and display position on the LCD

-12-Characters 4-Line Display

| _        | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | ← Display Position                |

|----------|----|----|----|----|----|----|----|----|----|----|----|----|-----------------------------------|

| 1st Line | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | ← DD RAM Address<br>(Hexadecimal) |

| 2nd Line | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1A | 1B | (nexadecimal)                     |

| 3rd Line | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 2A | 2B |                                   |

| 4th Line | 30 | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 3A | 3B |                                   |

When the display shift is performed, the DD RAM address changes as follows:

| (00) ← | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 00 |

|--------|----|----|----|----|----|----|----|----|----|----|----|----|

| (10)←  | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1A | 1B | 10 |

| (20)←  | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 2A | 2B | 20 |

| (30)←  | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | ЗA | 3B | 30 |

[Left shift display]

[Right shift display]

| 0B | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | →(0B) |

|----|----|----|----|----|----|----|----|----|----|----|----|-------|

| 1B | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 1A | →(1B) |

| 2B | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 2A | →(2B) |

| 3B | 30 | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 3A | →(3B) |

(1-4) Character Generator ROM (CG ROM)

The Character Generator ROM (CG ROM) stores  $5 \times 8$  dots character pattern represented in 8-bit character code. The capacity is up to 252 kinds of  $5 \times 8$  dots character pattern.

The correspondence between character code and standard character pattern of NJU6475B is shown in table 2. User defined character patterns (Custom Font) are also available by mask option. (in this case, the address (20)<sup>H</sup> are using for "Space Pattern".)

|                          |   |                   |          |              | _  |   |     | Uppe     | r 4bit ( | Hexad | ecimal         | )     |    |         |     |      |          |

|--------------------------|---|-------------------|----------|--------------|----|---|-----|----------|----------|-------|----------------|-------|----|---------|-----|------|----------|

| $\left  \right\rangle$   |   | 0                 | 1        | 2            | 3  | 4 | 5   | 6        | 7        | 8     | 9              | А     | В  | С       | D   | Е    | F        |

|                          | 0 | CG<br>RAM<br>(01) |          |              | 0  | 0 | P   | ÷        | p        | Ç     | ė              |       |    | 9       | Ξ.  | Ċ    | p        |

|                          | 1 | (02)              |          |              | -  | P | 0   | -8       | -4       | Ü     | 22             |       | ļ  | ÷       | ć., | ÷    | q        |

|                          | 2 | (03)              |          | ::           |    | 8 | R   | b        | ŀ        | ė     | Æ              | ľ     | ÷  | ų.      | .×' | e    | $\oplus$ |

|                          | 3 | (04)              |          |              |    | C | 5   | <u>.</u> | <u></u>  | ÷     | Ô              | .1    | ņ  | il.     | 1   |      |          |

|                          | 4 |                   | $\odot$  | \$           |    |   | -   | c        | ۰.       |       | Ö              | ۰.    |    |         | ÷   | ļ4   | 9        |

|                          | 5 |                   | Ú        |              |    |   |     | <b>e</b> | L.,      | ÷     | Ò              |       | 7  | <br>    |     | S    | ü        |

| 0e                       | 6 |                   | ñ        | 8            | 6  |   | Ų   | ÷        | ц.)      |       | Ô              | ņ     | 17 |         |     | p    | 2        |

| lexadecim                | 7 |                   | Ń        |              | 1  | 0 | ļ,  | 9        | Ļ.)      | ÷     | ù              |       | ÷  | 32      | ÷., | 9    | Л        |

| Lower 4bit (Hexadecimal) | 8 |                   |          | ÷.           | 8  |   | X   | h        | :::      | ê     | ÿ              | чį,   |    |         | Ņ   | .,1" | 33       |

| Law                      | 9 |                   | <u>_</u> | 2            | 9  |   | Ŷ   | 1        | ·!       | ë     | Ü              |       | Ţ  |         | 11, | :    | <u>ا</u> |

|                          | А |                   | ÷        | : <b>4</b> : | :: |   | 2   | Ĵ.       |          | è     | Ü              | ::::  |    | È       |     | .1   | ц:       |

|                          | В |                   | :        |              | ;; | K | Ľ   | k        | ÷.       | 1     | ¢.             | 7     |    | <u></u> |     | ×    | 39       |

|                          | С |                   |          | ::           | 4  | l | ÷   | 1        |          |       |                | †?    | :: |         | ņ   | ¢.   | PI       |

|                          | D |                   | i        |              |    | M |     | m        | 2        | 1     | ÷              | .::1. | 2  | ÷,      |     | ÷    | ÷        |

|                          | Е |                   | ×        |              | 2  | ŀ | ·^. | n        | <u> </u> | Ä     | P <sub>t</sub> |       | Ľ  |         | ÷   | ñ    |          |

|                          | F |                   | »        | /            |    | 0 |     | O        | ÷        | A     | ÷              | чų    | 9  | 7       | 13  | ö    |          |

<Table-2> The Correspondence Between Character Code and Standard Character Pattern (ROM Version -02)

New Japan Radio Co.,Ltd.

(1-5) Character Generator RAM (CG RAM)

The Character Generator RAM stores any kinds of character pattern in  $5 \times 8$  dots written by the user program to display user's original character pattern. The CG RAM can store 4 kinds of character in  $5 \times 8$  dots mode.

To display user's original character pattern stored in the CG RAM, the address data  $(00)_{H}$ - $(03)_{H}$  should be written to the DD RAM as shown in Table-3.

<Table-3> Correspondence of CG RAM address, DD RAM character code

and CG RAM character pattern (5 x 8 dots)

| Character 0<br>(DD RAM |              | CG RAM | Address                                              | Characte<br>(CG R                      | r Pattern<br>AM Data)                                                |                                                       |

|------------------------|--------------|--------|------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|

| 765432                 |              | 76543  | 210                                                  |                                        | 210                                                                  |                                                       |

| Upper L<br>Bits        | ower<br>Bits | Upper  | Lower                                                | Upper                                  | Lower                                                                |                                                       |

| 000000                 | 0 0          | 01000  | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>110 | 1 0<br>1 1<br>1 0<br>1 0<br>1 0        | 1 1 0<br>0 0 1<br>0 0 1<br>1 1 0<br>1 0 0<br>0 1 0<br>0 0 1<br>0 0 0 | Character Pattern<br>Example (1)<br>€ Cursor Position |

| 000000                 | 0 1          | 01001  | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>110 | 01<br>11<br>00<br>11<br>00<br>00<br>00 | 0 0 1<br>0 1 0<br>1 1 1<br>1 0 0<br>1 1 1<br>1 0 0<br>1 0 0<br>0 0 0 | Character Pattern<br>Example (2)<br>←—Cursor Position |

|                        |              |        | 000<br>001                                           |                                        |                                                                      |                                                       |

|                        |              |        |                                                      | i                                      |                                                                      |                                                       |

| 000000                 | 11           | 01011  |                                                      |                                        |                                                                      |                                                       |

|                        |              |        | 100<br>101<br>110<br>111                             |                                        |                                                                      |                                                       |

Notes : 1. Character code bit 0,1 correspond to the CG RAM address bit 3,4 (2bits ; 4patterns).

CG RAM address 0 to 2 designate character pattern line position. The 8th line should be "0". If there is "1" in the 8th line, but bit "1" is always displayed on the cursor position regardless of cursor existence.

- 3. Row position character pattern correspond to CG RAM data bits 0 to 4 are shown above.

- 4. CG RAM character patterns are selected when character code bits 2 to 7 are all "0" and these are addressed by character code bits "0" and "1".

- 5. "1" for CG RAM data corresponds to display on and "0" to display off.

(1-6) Icon display RAM (MK RAM)

The NJU6475B can display maximum 128 Icons.

The Icon display can be controlled by writing the data into MK RAM corresponding to the Icons. The relation between MK RAM address and Icon display position is shown in Table-4.

| <table-4> Correspondence among Icon Position, MK RAM Address and Data</table-4> |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

|             | dress                  | Bits f | or Icon        | Positi | on MK                 | RAM A | Addres                | s and [ | Data           |                                                                               |

|-------------|------------------------|--------|----------------|--------|-----------------------|-------|-----------------------|---------|----------------|-------------------------------------------------------------------------------|

| (60н - 7Fн) |                        | D7     | D <sub>6</sub> | D₅     | <b>D</b> <sub>4</sub> | D₃    | <b>D</b> <sub>2</sub> | D1      | D <sub>0</sub> |                                                                               |

| 0110 0000   | 60н                    | *      | *              | *      | 1                     | 2     | 3                     | 4       | 97             | $\mathbf{r}$                                                                  |

| 0110 0001   | 61н                    | *      | *              | *      | 5                     | 6     | 7                     | 8       | 98             | COMM <sub>1</sub> Line and                                                    |

|             | 1                      |        |                |        |                       |       |                       |         |                | Both besides of 1st Line                                                      |

| 0110 0101   | <b>65</b> ⊦            | *      | *              | *      | 21                    | 22    | 23                    | 24      | 102            |                                                                               |

| 0110 0110   | <b>66</b> н            | *      | *              | *      | *                     | *     | *                     | *       | 103            | (COM1,COM3,COM5,COM7)                                                         |

| 0110 0111   | 67н                    | *      | *              | *      | *                     | *     | *                     | *       | 104            | )                                                                             |

| 0110 1000   | <b>68</b> н            | *      | *              | *      | 25                    | 26    | 27                    | 28      | 105            | 7                                                                             |

| 0110 1001   | <b>69</b> н            | *      | *              | *      | 29                    | 30    | 31                    | 32      | 106            | COMM <sub>2</sub> Line and                                                    |

|             |                        |        |                |        |                       |       |                       |         | 1              | Both besides of 2nd Line                                                      |

| 0110 1101   | 6Dн                    | *      | *              | *      | 45                    | 46    | 47                    | 48      | 110            | Both Booldoo of Zha Eino                                                      |

| 0110 1110   | 6Eн                    | *      | *              | *      | *                     | *     | *                     | *       | 111            | (COM9,COM11,COM13,COM15)                                                      |

| 0110 1111   | 6F⊩                    | *      | *              | *      | *                     | *     | *                     | *       | 112            | )                                                                             |

| 0111 0000   | <b>70</b> н            | *      | *              | *      | 49                    | 50    | 51                    | 52      | 113            | 7                                                                             |

| 0111 0001   | 71н                    | *      | *              | *      | 53                    | 54    | 55                    | 56      | 114            | COMM₃ Line and                                                                |

|             |                        |        |                |        |                       |       |                       |         |                | Both besides of 3rd Line                                                      |

| 0111 0101   | 75н                    | *      | *              | *      | 69                    | 70    | 71                    | 72      | 118            | Doth besides of ord Line                                                      |

| 0111 0110   | <b>76</b> <sub>H</sub> | *      | *              | *      | *                     | *     | *                     | *       | 119            | (COM17,COM19,COM21,COM23)                                                     |

| 0111 0111   | 77н                    | *      | *              | *      | *                     | *     | *                     | *       | 120            | )                                                                             |

| 0111 1000   | <b>78</b> н            | *      | *              | *      | 73                    | 74    | 75                    | 76      | 121            | $\mathbf{r}$                                                                  |

| 0111 1001   | <b>79</b> н            | *      | *              | *      | 77                    | 78    | 79                    | 80      | 122            | COMM <sub>4</sub> Line and                                                    |

|             | :                      |        |                |        |                       |       |                       |         | 1              | Both besides of 4th Line                                                      |

| 0111 1101   | 7Dн                    | *      | *              | *      | 93                    | 94    | 95                    | 96      | 126            |                                                                               |

| 0111 1110   | 7E⊩                    | *      | *              | *      | *                     | *     | *                     | *       | 127            | (COM <sub>25</sub> ,COM <sub>27</sub> ,COM <sub>29</sub> ,COM <sub>31</sub> ) |

| 0111 1111   | 7F⊦                    | *      | *              | *      | *                     | *     | *                     | *       | 128            |                                                                               |

Notes : 1. When the Icon display function using, the system should be initialized by the software initialization Because the MK RAM is not initialized by the power on reset and hardware.

2. The cross-points between segments (SEGM<sub>1</sub> and SEGM<sub>2</sub>) and commons (COMM<sub>1</sub> to COMM<sub>4</sub> and COM<sub>2</sub> to COM<sub>32</sub>) are always set "OFF" level.

3. In the table 4, \* mark are invalid, therefore both of "0" or "1" can be written but these are no meaning.

New Japan Radio Co., Ltd.

## (1-7) Timing generator

The timing generator generates a timing signals for the DD RAM, CG RAM and MK RAM and other internal circuits. RAM and timing for the display and internal operation timing for MPU access are separately generated, so that may not interfere with each other.

Therefore, when the data write to the DD RAM for example, there will be undesirable influence, such as flickering, in areas other than display area.

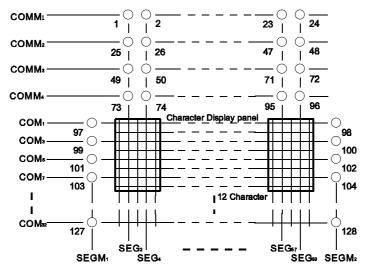

#### (1-8) LCD Driver

LCD Driver consists of 37-common driver and 63-segment driver. The character pattern data are latched to the addressed segment-register respectively.

This latched data controls display driver to output LCD driving waveform.

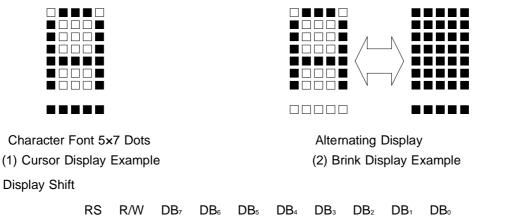

## (1-9) Cursor Blinking control circuit

This circuit controls cursor On / Off and cursor position character blinking. The cursor or blinking appear in the digit locating at the DD RAM address set in the address counter (AC). When the address counter is  $(08)_{H}$ , a cursor position is shown as bellow.

|              | AC <sub>6</sub> | А  | C₅ | AC <sub>4</sub> | AC | 3  | AC <sub>2</sub> | AC <sub>1</sub> | A         | C₀ |    |    |                   |

|--------------|-----------------|----|----|-----------------|----|----|-----------------|-----------------|-----------|----|----|----|-------------------|

| AC           | 0               | (  | C  | 0               | 1  |    | 0               | 0               | (         | )  |    |    |                   |

|              |                 |    |    |                 |    |    |                 |                 |           |    |    |    |                   |

| 4 Lino Dicol | 21              |    |    |                 |    |    |                 |                 |           |    |    |    |                   |

| 4-Line Displ | ау<br>1         | 2  | 3  | 4               | 5  | 6  | 7               | 8               | 9         | 10 | 11 | 12 | ←Display position |

| 1st Line     | 00              | 01 | 02 | 03              | 04 | 05 | 06              | 07              | <u>08</u> | 09 | 0A | 0B | ← DD RAM Address  |

| 2nd Line     | 10              | 11 | 12 | 13              | 14 | 15 | 16              | 17              | 18        | 19 | 1A | 1B | (Hexadecimal)     |

| 3rd Line     | 20              | 21 | 22 | 23              | 24 | 25 | 26              | 27              | 28        | 29 | 2A | 2B |                   |

| 4th Line     | 30              | 31 | 32 | 33              | 34 | 35 | 36              | 37              | 38        | 39 | ЗA | 3B |                   |

|              |                 |    | 1  |                 | /  | /  |                 |                 |           |    |    |    |                   |

Cursor position

Note : The cursor or blinking also appear when the address counter (AC) selects the CG RAM or the MK RAM. But the displayed cursor and blinking are meaningless.

If the AC stores the CG or MK RAM address data, the cursor and blinking are displayed in the meaningless position.

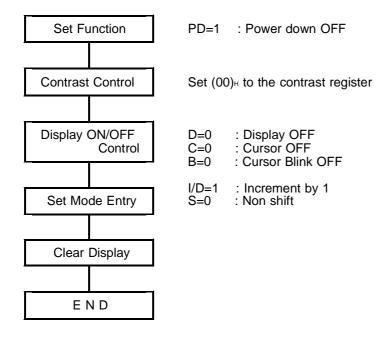

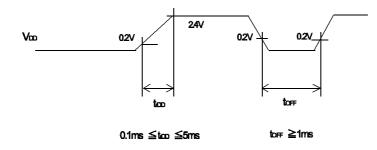

- (2) Power on Initialization by internal circuits

- (2-1) Internal Reset circuits Initialization

The NJU6475B is automatically initialized by internal power on initialization circuits when the power is turned on. In the internal power on initialization, following instructions are executed.

During the Internal power on initialization, the busy flag (BF) is "1" and this status is kept during 6ms ( $f_{OSC}$ =180KHz) after V<sub>DD</sub> rose to 2.4V.

Initialization sequence

Note : If the condition of power supply rise time described in the Electrical Characteristics is not satisfied, the internal Power On Initialization will not performed.

In this case, the software initialization by MPU is required.

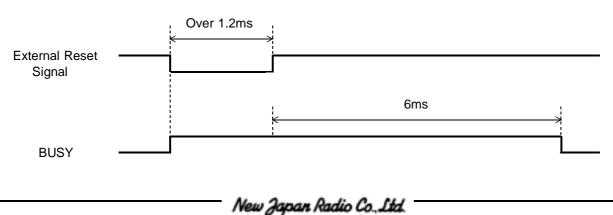

#### (2-2) Hardware Initialization

The NJU6475B prepares RESET terminal to initialize the all system.

When the "L" level is input over 1.2ms to the RESET terminal, reset sequence is executed. In this time, the busy signal is output during 6ms (fosc=180KHz) after RESET terminal went to "H".

-Timing Chart

## (3) Instruction

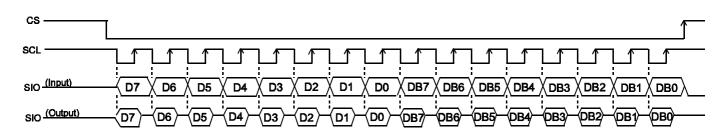

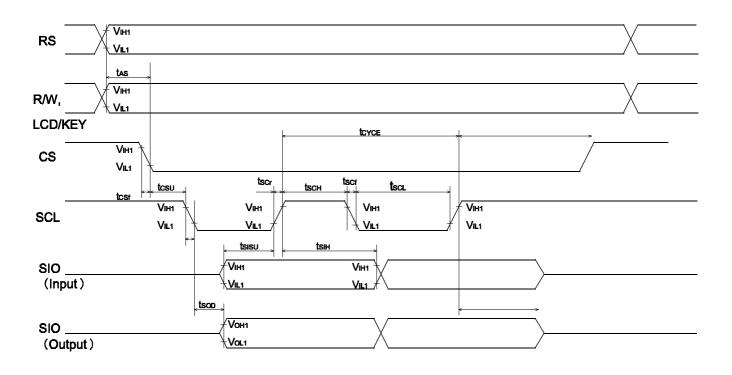

The NJU6475B incorporates two registers, an Instruction Register (IR) and a Data Register (DR). These two registers store control information temporarily to allow interface between NJU6475B and MPU or peripheral IC operating different cycles. The operation of NJU6475B is determined by this control signal from MPU. The control information includes resister selection signals (RS), Read / Write signals (R/W) and data signal (SIO).

| Instruction                         |                         |                                                                                                                                                                                                                         |     | С               | 0     | d   | е    |                 |             |                 | Description                                                                                                                                        | Execute Time<br>(MAX)<br>(fcp or fosc                           |

|-------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|-------|-----|------|-----------------|-------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                                     | RS                      | R/W                                                                                                                                                                                                                     | DB7 | DB <sub>6</sub> | DB₅   | DB4 | DB₃  | DB <sub>2</sub> | DB₁         | DB <sub>0</sub> |                                                                                                                                                    | =180kHz)                                                        |

| Maker Test                          | 0                       | 0                                                                                                                                                                                                                       | 0   | 0               | 0     | 0   | 0    | 0               | 0           | 0               | All "0" code is using for maker testing.                                                                                                           | -                                                               |

| Clear Display                       | 0                       | 0                                                                                                                                                                                                                       | 0   | 0               | 0     | 0   | 0    | 0               | 0           | 1               | Clears Display and sets RAM address (00) <sup>⊬</sup> in AC.                                                                                       | 5.42ms                                                          |

| Return Home                         | 0                       | 0                                                                                                                                                                                                                       | 0   | 0               | 0     | 0   | 0    | 0               | 1           | *               | Sets RAM address (00) <sub>H</sub> in AC<br>and returns shifted display to<br>original position. RAM contents<br>are not changed                   | 83.4us                                                          |

| Entry Mode Set                      | 0                       | 0                                                                                                                                                                                                                       | 0   | 0               | 0     | 0   | 0    | 1               | I/D         | S               | sets cursor move direction and display shift operation which are performed at data read/write.                                                     | Ous                                                             |

| Display ON/OFF<br>Control           | 0                       | 0                                                                                                                                                                                                                       | 0   | 0               | 0     | 0   | 1    | D               | с           | В               | Set Display Control<br>On /Off (D), cursor On /Off (C)<br>and character blinking (B) at<br>cursor position.                                        | Ous                                                             |

| Cursor or<br>Display Shift          | 0                       | 0                                                                                                                                                                                                                       | 0   | 0               | 0     | 1   | S/C  | R/L             | *           | *               | moves cursor and shifts dis-<br>play without changing RAM(DR) contents.                                                                            | Cursor :<br>83.4us<br>Display : 0us                             |

| Function Set                        | 0                       | 0                                                                                                                                                                                                                       | 0   | 0               | 1     | *   | *    | *               | *           | PD              | Sets Interface data length (DL) and power down mode (PD).                                                                                          | Ous                                                             |

| Electronic Volume<br>Register Set   | 0                       | 0                                                                                                                                                                                                                       | 0   | 1               | *     | *   | Ele  | ectro           | nic<br>volu | ıme             | Sets Vreg data to EVR control register.                                                                                                            | Ous                                                             |

| RAM Address Set                     | 0                       | 0                                                                                                                                                                                                                       | 1   |                 |       | A   | ddre | SS              |             |                 | Sets RAM Address. After this instruction, the data is transferred to/from RAM.                                                                     | 83.4us                                                          |

| Key Data Read                       | 0                       | 1                                                                                                                                                                                                                       |     | Rea             | id Da | ata | (KE) | / DA            | TA)         |                 | When LCD/Key= "1", reads key data out.                                                                                                             | Ous                                                             |

| Data Write to CG<br>or DD or MK RAM | 1                       | 0                                                                                                                                                                                                                       | *   | Writ<br>*       | e Da  | ata |      | G R/            | ÁM)         |                 | Writes data into DD or CG or MK RAM.                                                                                                               | 83.4us                                                          |

| * : Don't care                      | S=<br>S/0<br>shi<br>R/I | I/D=1:Increment, I/D=0:Decrement,      S=1:Include Display Shift,      S/C=1:Shift Display, S/C=0:Cursor      shift, R/L=1:Shift to Right,      R/L=1:Shift left, PD=0:Power Down Mode      PD=1:Cancel Power Down Mode |     |                 |       |     |      | ursoi<br>Dow    | ſ           | ode             | DD RAM : Display data RAM<br>CG RAM : Character generator<br>RAM<br>MK RAM : Icon display RAM<br>AC : Address counter use for<br>DD, CG and MK RAM | When FRQ is<br>changed, the<br>execute time is<br>also changed. |

<Table-5> shows each instruction and its operating time

Note : If the oscillation frequency is changed, the execution time is also changed.

New Japan Radio Co., Ltd. \_

- (3-1) Description of each instructions

- (a) Maker Test

| -    | RS | R/W | DB7 | DB <sub>6</sub> | DB₅ | DB <sub>4</sub> | DB₃ | $DB_2$ | DB₁ | DB₀ |

|------|----|-----|-----|-----------------|-----|-----------------|-----|--------|-----|-----|

| Code | 0  | 0   | 0   | 0               | 0   | 0               | 0   | 0      | 0   | 0   |

(b) Clear Display

|      | RS | R/W | DB7 | DB <sub>6</sub> | DB₅ | DB4 | DB₃ | $DB_2$ | DB₁ | DB₀ |

|------|----|-----|-----|-----------------|-----|-----|-----|--------|-----|-----|

| Code | 0  | 0   | 0   | 0               | 0   | 0   | 0   | 0      | 0   | 1   |

Clear Display Instruction is executed when the code "1" is written into DB<sub>0</sub>.

When this instruction is executed, the space code  $(20)_{H}$  is written into every DD RAM address, then the DD RAM  $(00)_{H}$  is set into address counter and I/D of entry mode is set as increment mode. If the cursor or blink are displayed, they are returned to the left end of the 1st line on the LCD panel.

In addition, S of entry mode is not changes and contents of MK RAM and CG RAM are also not changed.

Note : The character code (20)<sup>H</sup> must be blank code in the user defined character pattern (Custom font).

(c) Return Home

|      | RS | R/W | DB7 | DB6 | DB₅ | $DB_4$ | DB₃ | $DB_2$ | DB₁ | DB₀ | _             |

|------|----|-----|-----|-----|-----|--------|-----|--------|-----|-----|---------------|

| Code | 0  | 0   | 0   | 0   | 0   | 0      | 0   | 0      | 1   | *   | *= Don't Care |

Return Home instruction is executed when the code "1" is written into DB1.

When this instruction is executed, the DD RAM address  $(00)_{H}$  is set into the address counter. Display is returned to its original position if shifted, the cursor or blink are returned to the left end of the 1st line on the LCD if the cursor or blink are operating. The DD RAM contents do not change.

(d) Entry Mode Set

| _    | RS | R/W | DB7 | DB <sub>6</sub> | DB₅ | DB4 | DB₃ | $DB_2$ | DB₁ | DB₀ |

|------|----|-----|-----|-----------------|-----|-----|-----|--------|-----|-----|

| Code | 0  | 0   | 0   | 0               | 0   | 0   | 0   | 1      | I/D | S   |

Entry Mode Set instruction which sets the cursor moving direction and display shift On/Off, is executed when the code "1" is written into  $DB_2$  and codes of (I/D) and (S) are written into  $DB_1$  (I/D) and  $DB_0$  (S). (I/D) sets the address increment or decrement, and the (S) sets the entire display shift at the DD RAM writing.

| I/D | Function                                                                                                                   |

|-----|----------------------------------------------------------------------------------------------------------------------------|

| 1   | Address increment : The address of the DD RAM or CG RAM increment (+1) when the                                            |

|     | read/write operation, and the cursor or blink moves to the right.                                                          |

| 0   | Address decrement : The address of the DD RAM or CG RAM decrement (-1) when the                                            |

|     | read/write operation, and the cursor or blink moves to the left.                                                           |

| S   | Function                                                                                                                   |

|     | Entire display shift.                                                                                                      |

|     | The shift direction is determined by I/D. : shift to left at I/D=1 and shift to the right at                               |

| 1   |                                                                                                                            |

| 1   | the I/D=0. The shift is operated only for the character, so that it looks as if the cursor                                 |

| I   | the I/D=0. The shift is operated only for the character, so that it looks as if the cursor stands still and display moves. |

| I   | stands still and display moves.                                                                                            |

| I   | stands still and display moves.                                                                                            |

New Japan Radio Co.,Ltd.

(e) Display ON/OFF Control

| _    | RS | R/W | DB7 | DB6 | DB₅ | DB₄ | DB₃ | $DB_2$ | DB₁ | DB₀ |

|------|----|-----|-----|-----|-----|-----|-----|--------|-----|-----|

| Code | 0  | 0   | 0   | 0   | 0   | 0   | 1   | D      | С   | В   |

Display ON/OFF control instruction which controls the whole display ON/OFF, the cursor ON/OFF and the cursor position character blink, is executed when the code "1" is written into DB3 and codes of (D), (C) and (B) are written into  $DB_2(D)$ ,  $DB_1(C)$  and  $DB_0(B)$ , as shown below.

| D | Function                                                                                                                                          |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Display On                                                                                                                                        |

| 0 | Display Off. In this mode, the display data remains in the DD RAM so that it is retrieved immediately on the display when the D changes to 1.     |

| С | Function                                                                                                                                          |

| 1 | Cursor On. The cursor is displayed by 5 dots on the 8th line.                                                                                     |

| 0 | Cursor Off. Even if the display data write, the I/D etc does not change.                                                                          |

| В | Function                                                                                                                                          |

| 1 | The cursor position character is blinking.<br>Blinking rate is 480ms at fosc=180KHz.<br>The cursor and the blink can be displayed simultaneously. |

| 0 | The character does not blink.                                                                                                                     |

(f) Cursor Display Shift

|      | RS | R/W | DB7 | DB <sub>6</sub> | DB₅ | $DB_4$ | DB₃ | $DB_2$ | DB₁ | DB <sub>0</sub> | _             |

|------|----|-----|-----|-----------------|-----|--------|-----|--------|-----|-----------------|---------------|

| Code | 0  | 0   | 0   | 0               | 0   | 1      | S/C | R/L    | *   | *               | *= Don't Care |

The cursor /display shift instruction shifts the cursor display to the right or left without writing or reading display data. This function is used to correct or search the display. The cursor moves to the 2nd line after the 12nd digit of the 1st line. Notice that 1st to 3rd line displays shift at the same time. When the displayed data are shifted repeatedly, each display moves in only same line. The 2nd and 3rd line display do not shift into the 1st and 2nd line.

The contents of address counter (AC) does not change by operation of only the display shift.

This instruction is executed when the code "1" is written into DB4 and the codes of (S/C) and (R/L) are written into  $DB_3(S/C)$  and  $DB_2(R/L)$ , as shown below.

| S/C | R/L | Function                                                           |

|-----|-----|--------------------------------------------------------------------|

| 0   | 0   | Shift the cursor position to the left ((AC) is decremented by 1).  |

| 0   | 1   | Shift the cursor position to the right ((AC) is incremented by 1). |

| 1   | 0   | Shifts the entire display to the left and the cursor follows it.   |

| 1   | 1   | shifts the entire display to the right and the cursor follows it.  |

New Japan Radio Co., Ltd.

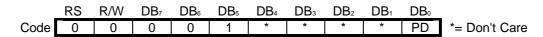

(g) Function Set

Function set instruction which sets the interface data length and power down is executed, when the code "1" is written into  $DB_5$  and (PD) is written into  $DB_0$ , as shown below.

When the power down mode is set, the display turns off automatically. Afterward, when the power down mode is reset, the display is off continuously.

The display appears by the display on instruction.

| PD | Function                                                    |

|----|-------------------------------------------------------------|

| 1  | Power down mode off (Normal operation)                      |

| 0  | Power down mode on (the display goes to off automatically.) |

(h) Set Electronic Volume Register

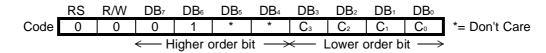

Contrast Control instruction which adjusts the contrast of LCD, is executed when the code "1" is written into DB<sub>6</sub> and the codes of C<sub>0</sub> to C<sub>3</sub> are written into DB<sub>0</sub> to DB<sub>3</sub> as shown below.

The contrast of LCD can be adjusted one of 16 voltage stage by setting 4 bit register. Set the binary code "0000" when contrast control unused.

| C₃ | $C_2$       | C <sub>1</sub> | Co | VLCD | $V_{LCD} = V_{DD} - V_5$ |

|----|-------------|----------------|----|------|--------------------------|

| 0  | 0           | 0              | 0  | low  |                          |

| 1  | :<br>:<br>1 | 1              | 1  | high |                          |

(i) Set RAM Address

| _    | RS | R/W | DB7 | DB <sub>6</sub> | DB₅      | $DB_4$ | DB₃ | $DB_2$  | DB₁     | DB₀                  |  |

|------|----|-----|-----|-----------------|----------|--------|-----|---------|---------|----------------------|--|

| Code | 0  | 0   | 1   | Α               | Α        | Α      | Α   | Α       | Α       | Α                    |  |

| -    |    |     | ← H | liaher a        | order bi | t>     | ← L | _ower o | order b | it $\longrightarrow$ |  |

The RAM address set instruction is executed when the code "1" is written into  $DB_7$  and the address is written into  $DB_6$  to  $DB_0$  as shown above.

The address data (DB<sub>6</sub> to DB<sub>0</sub>) is written into the address counter (AC) by this instruction.

After this instruction execution, the data writing/reading is performed into/from the addressed RAM.

The RAM includes DD RAM, CG RAM and MK RAM and these RAMs are shared by addressed as shown below.

#### RAM Address

| DD RAM | 1st Line     | : | <b>(00)</b> н     | to | (0B)⊦         |

|--------|--------------|---|-------------------|----|---------------|

| DD RAM | 2nd Line     | : | (10) <sub>H</sub> | to | <b>(1B)</b> н |

| DD RAM | 3rd Line     | : | <b>(20)</b> н     | to | (2B)н         |

| DD RAM | 4th Line     | : | <b>(30)</b> н     | to | <b>(3B)</b> н |

| CG RAM | 4 Characters | : | <b>(40)</b> ⊦     | to | (5F)⊦         |

| MK RAM | 128 Icons    | : | <b>(60)</b> ⊦     | to | (7F)⊦         |

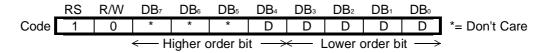

(j) Write Data to CG, DD or MK RAM

-Write Data to DD RAM

|                                                        | RS | R/W | DB7 | DB <sub>6</sub> | DB₅ | DB4              | DB₃ | $DB_2$ | DB₁ | DB <sub>0</sub> | _ |

|--------------------------------------------------------|----|-----|-----|-----------------|-----|------------------|-----|--------|-----|-----------------|---|

| Code                                                   | 1  | 0   | D   | D               | D   | D                | D   | D      | D   | D               |   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |    |     |     |                 |     | it $\rightarrow$ |     |        |     |                 |   |

-Write Data to CG or MK RAM

Write Data to RAM instruction is executed when the code "1" is written into (RS) and code "0" is written into (R/W).

By the execution of this instruction, the data is written into RAM. The selection of RAM is determined by the previous instruction.

After this instruction execution, the address increment (+1) or decrement (-1) is performed automatically according to the entry mode set.

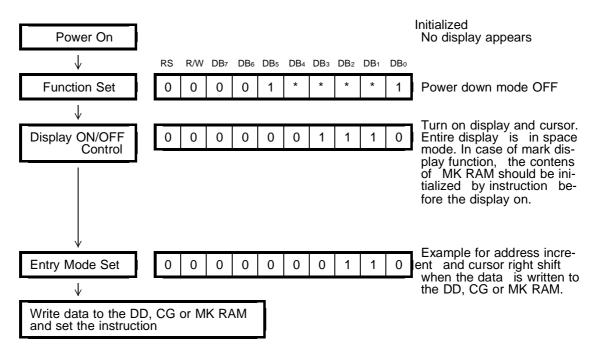

(3-2) Initialization using the internal reset circuit

When internal reset operates for initialization, the function set, Display ON/OFF Control and Entry Set instruction must be executed before the data input as shown below.

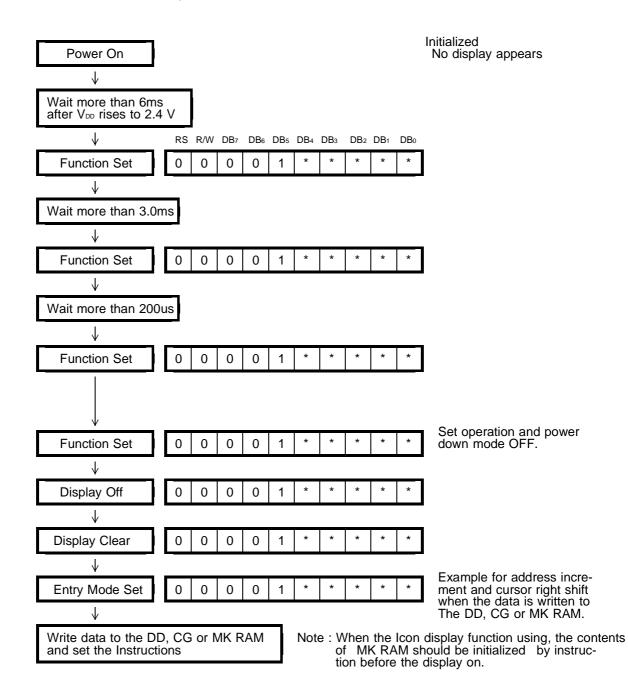

#### (3-3) Initialization by instruction

If the power supply conditions for the correct operation of the internal reset circuits are not met, the NJU6475B must be initialized by instruction.

#### (4) Power down Function

NJU6475B incorporates the power down mode to reduce the operating current.

The power down mode is set/reset by the function set instruction.

In the power down mode, all the character display and Icon display turn off and only static display operation is available.

The status of internal circuits at the power down mode is shown below.

-Main oscillator stops and sub oscillator for the static display starts the operation.

-Voltage converter, Key Scan, Voltage Regulator, Voltage follower (OP-AMP) are stopped.

-The contents of DD, CG, MK RAM are kept.

#### (5) LCD Display

(5-1) Power Supply for LCD Driving

NJU6475B incorporates voltage converter to generate the LCD driving voltage which is adjusted by the voltage regulater and the EVR.

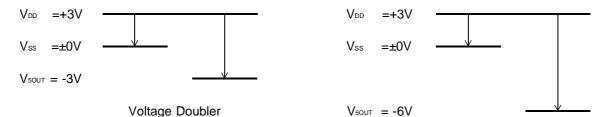

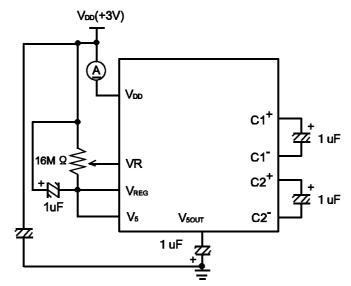

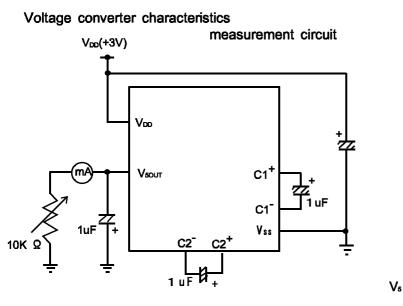

#### (a) Voltage Converter

-Voltage Tripler

By connecting capacitor between C1<sup>+</sup> and C1<sup>-</sup>, C2<sup>+</sup> and C2<sup>-</sup>, Vss and V<sub>50UT</sub> respectively, two times negative voltage of V<sub>DD</sub>--V<sub>SS</sub> output from V<sub>50UT</sub>.

#### -Voltage Doubler

By connecting capacitor between C2<sup>+</sup> and C2, Vss and V<sub>50UT</sub> respectively, and connecting the C1<sup>+</sup> terminal to C2<sup>+</sup> terminal, and C1 terminal being open, negative voltage of V<sub>DD</sub>--Vss output from V<sub>50UT</sub>.

Voltage Tripler

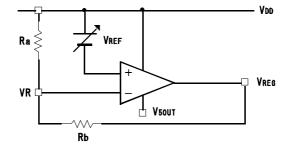

(b) Voltage Regulator

Voltage Regulator incorporates a OP-AMP which is supplied  $V_{DD}$  and  $V_{50UT}$ , and a reference voltage source ( $V_{REF}$ ).

By setting the VR level by connecting Ra and Rb, the regulator which amplifies  $V_{REF}$ , outputs the LCD driving voltage to the  $V_{REG}$  terminal.

Therefore the LCD driving voltage can be output between  $V_{\mbox{\tiny DD}}$  and  $V_{\mbox{\tiny REG}}$  by setting.

$V_{REG} = (1 + Rb / Ra) V_{REF}$  in condition,  $V_{DD} = 0V$ ,  $V_{REG} < V_{50UT}$

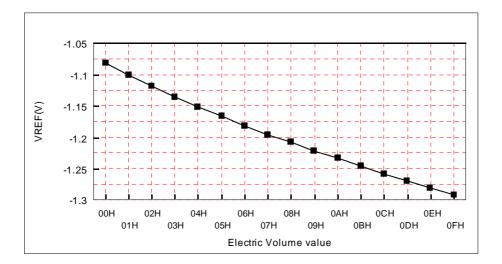

The EVR functions  $V_{REF}$  value adjustment from 1st step to 16th by a step when the 4 bit data write into the EVR register by the instruction.

Set the EVR register to  $(00)_{H}$  when the EVR function is unused. Use variable resistances to external to the external resistances Ra, Rb and thermistor if need due to the voltage reference V<sub>REF</sub> is changed by the lot and operating temperature.

Take care the noise input on the VR terminal because of it is designed with high impedance. Short wiring should be required to avoid the noise input, if necessary.

New Japan Radio Co.,Ltd.

[ The Voltage Reference VREF Characteristics ]

Supply Voltage :  $V_{DD} = 0V, V_{SS} = -3V$

Temperature : 25 °C

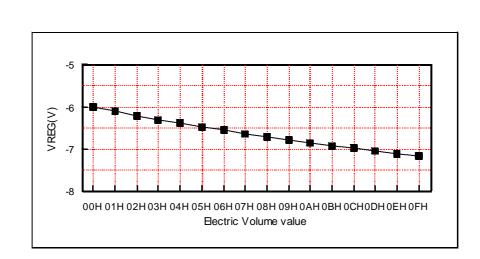

[ The LCD Operating Voltage  $V_{\text{REG}}$  Characteristics ]

Supply Voltage:  $V_{DD} = 0V, V_{SS} = -3V,$ Voltage Tripler Output:  $V_{50UT} = -9V$ External Resistances :  $Ra = 180K\Omega, Rb = 820K\Omega$ Temperature: 25 °C

Used Formulation

:  $V_{\text{REG}}(XX)_{\text{H}} = (1 + 820 k\Omega / 180 k\Omega) V_{\text{REF}}(XX)_{\text{H}}$

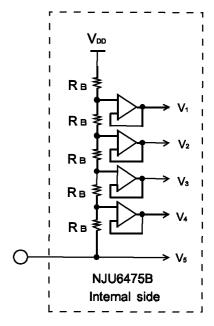

#### (c) Bleeder Resistance

Each LCD driving voltage  $(V_1, V_2, V_3, V_4, V_5)$  is generated by the high impedance bleeder resistance buffered by voltage follower OP-AMP to get a enough display characteristics with low operating current. The bleeder resistance is set 1/7 bias suitable for 1/36 duty by 5M $\Omega$  resistance in total.

The capacitor connected between V<sub>5</sub> and V<sub>DD</sub> is needed for stabilizing V<sub>5</sub>. The determination of the each capacitance of C<sub>1</sub>, C<sub>2</sub> and C<sub>3</sub> generating for LCD operating voltage is required to operate with the LCD panel actually.

The capacitance for the typical application is shown below:

LCD Driving Voltage vs Duty

| Power  | Duty Ratio | 1/36                             |

|--------|------------|----------------------------------|

| Supply | Bias       | 1/7                              |

|        | VLCD       | V <sub>DD</sub> - V <sub>5</sub> |

| 3+                  | aaV                       |                      |                                  |

|---------------------|---------------------------|----------------------|----------------------------------|

| c1 <sup>+</sup> zzz | C1 <sup>+</sup>           |                      |                                  |

|                     | - C1 <sup>-</sup>         |                      | V ⊳ ⊳(+3V)                       |

| c₂ <sup>‡</sup>     | C2 <sup>+</sup>           |                      | RB1 Ş                            |

|                     | С2 <sup>-</sup><br>V ₅о⊎т |                      | $\downarrow \rightarrow \vee_1$  |

| _                   | V₅                        |                      |                                  |

| <del></del>         | Vreg                      |                      |                                  |

| C4, #               | VR                        |                      |                                  |

| VR1                 | NJU6475B                  |                      |                                  |

|                     |                           |                      |                                  |

|                     |                           |                      |                                  |

|                     | V D D                     | V 5 O                | → V 5                            |

| <b>_</b>            | Typica                    | Il capacitance : N.  | JU6475B Bleeder Resistance       |

| +                   |                           | C1,C2,C3,C4=1.0~10μF | and Buffer Ampllifire            |

|                     |                           |                      | RB1=714KΩ typ                    |

| 777                 |                           |                      | RB2=2.14Μ Ω typ<br>RB=5.0M Ω typ |

|                     |                           |                      | RD-D.VW & Lyp                    |

$V_{\mbox{\tiny LCD}}$  is the maximum amplitude for LCD driving voltage.

Typical application for LCD operating voltage generation

Note : Take care the noise into the VR terminal as designed with high impedance. Short wiring or sealed wiring are required to avoid the noise, if necessary.

New Japan Radio Co.,Ltd.

(5-2) Relation between oscillation frequency and LCD frame frequency

As the NJU6475B incorporates oscillation capacitor and resistor for CR oscillation, 180KHz oscillation is available without any external components. (1 Clock = 5.56us)

1/36 Duty

1 frame = 5.56 (us) x 62 x 36 = 12.4 (ms) Frame frequency = 1 / 12.4 (ms) = 80.6 (Hz)

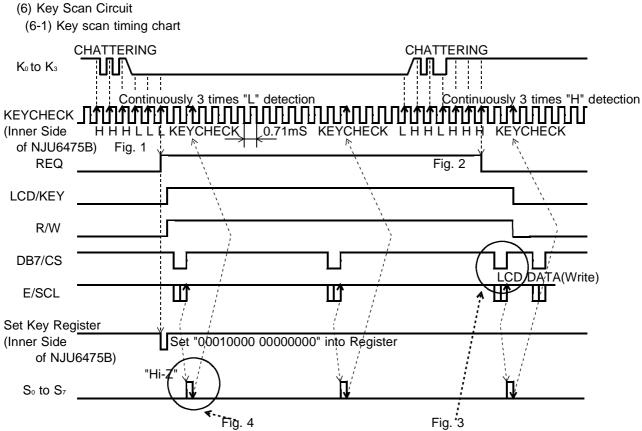

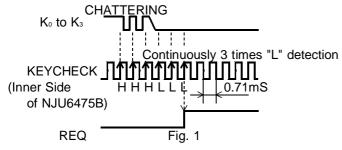

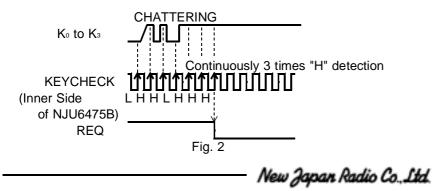

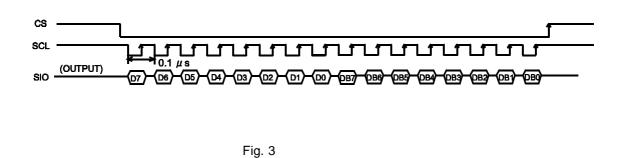

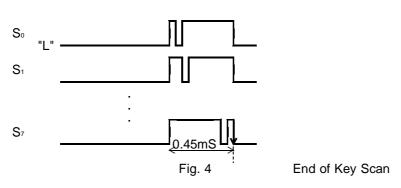

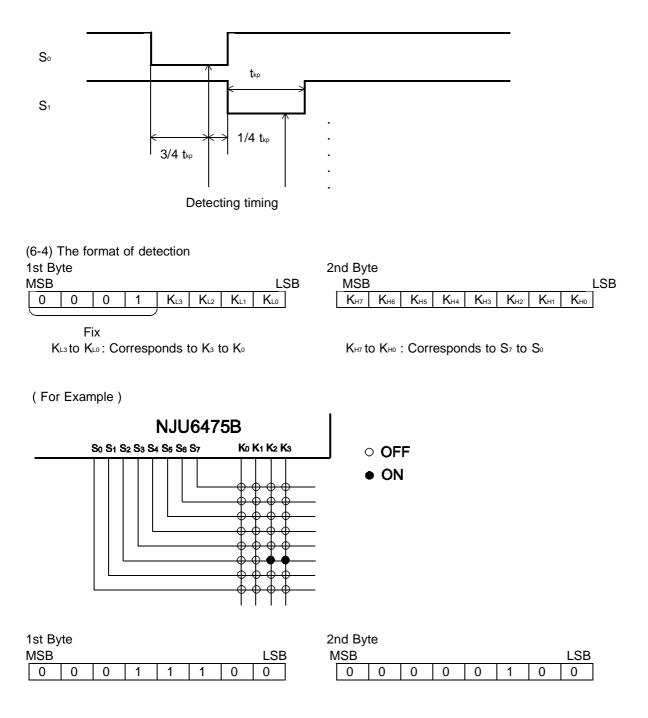

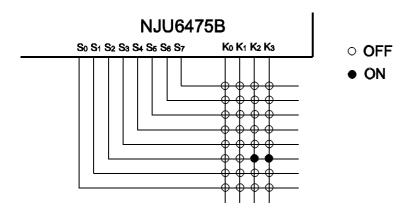

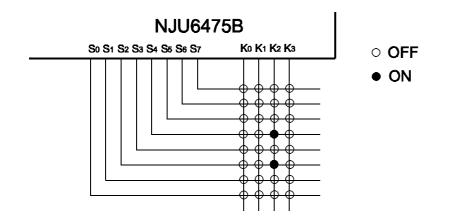

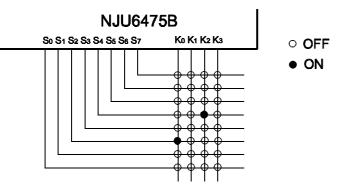

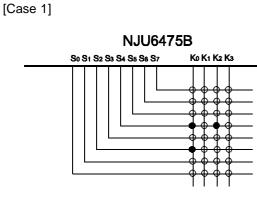

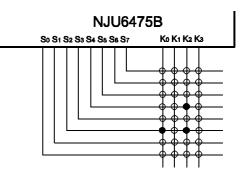

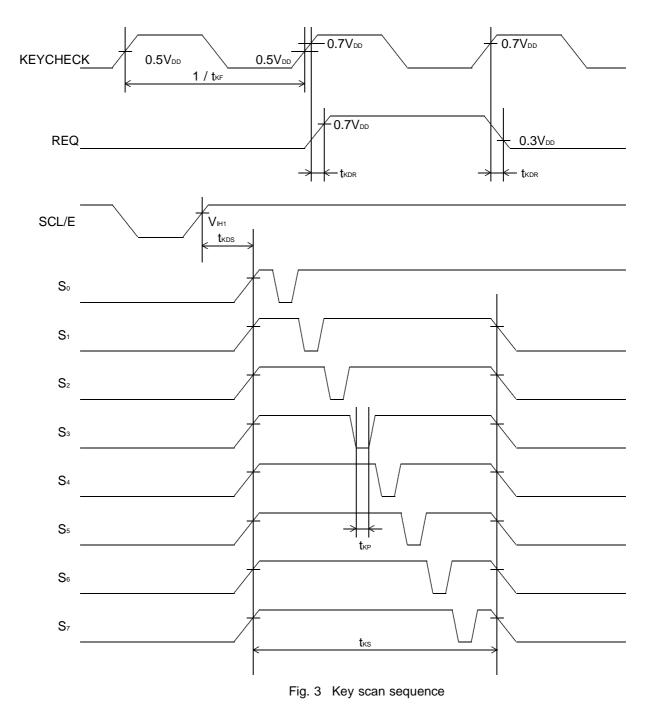

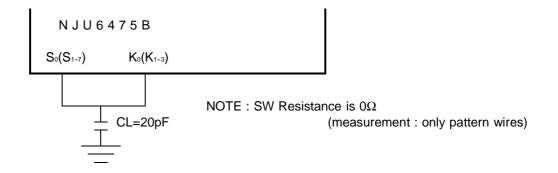

(6-2) Key Scan

- KEYCHECK signal always operates to check the status of keys excepting for power down mode.