## **OVERVIEW**

The SM9103M is a photodiode photoelectric current-to-voltage conversion head amplifier LSI for optical disk pickups in DVDRAM/DVDROM equipment. It sums the photodiode current data signals and then converts the signals to a differential signal for output. The output tracking servo and focusing servo signals are derived from built-in sum and difference circuits, and the gain for these servo signals can be adjusted using serial interface controls. Each of the signals from the photodiodes, used to generate DPD (Differential Phase Detection) tracking servo signal, is current-to-voltage converted and then also output. It operates from a single 5 V supply, and is available in 36-pin plastic SSOP packages.

#### **FEATURES**

- RAM/ROM gain switching, low-noise RF signal generator (differential output)

- ROM tracking DPD signal output

- Variable-gain RAM tracking push-pull signal output

- Address signal, high-speed push-pull signal output

- Variable-gain focus error signal output

- Tracking PD sum signal output

- Focus PD sum signal output

- Offset correction timing output (logic)

- Temperature monitor function

- Serial interface to control internal parameter settings

- Sleep-mode function

- Single 5 V supply

- 36-pin plastic SSOP

#### TYPICAL APPLICATIONS

- Double-speed DVDROM equipment

- Double-speed DVDRAM equipment

#### ORDERING INFORMATION

| Device  | Package     |

|---------|-------------|

| SM9103M | 36-pin SSOP |

## **PINOUT**

#### 36-pin SSOP

(Top view)

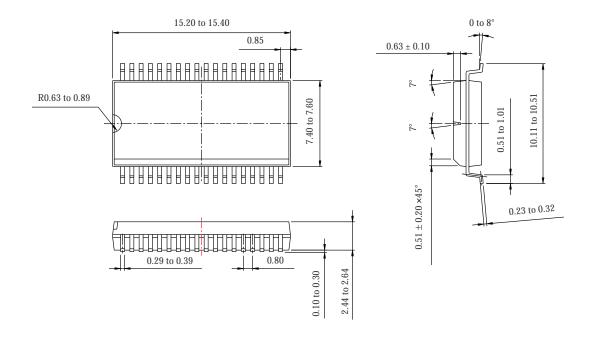

## PACKAGE DIMENSIONS

(Unit: mm)

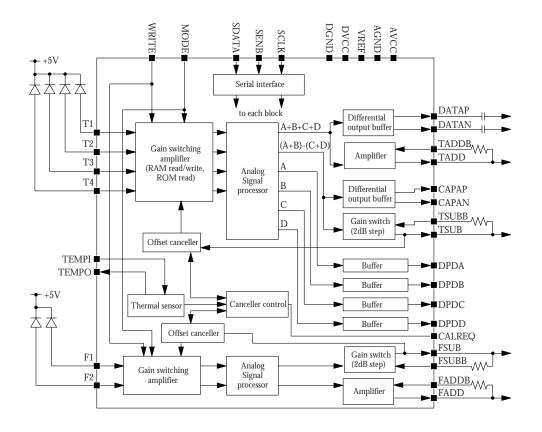

## **BLOCK DIAGRAM**

## SM9103M

## **PIN DESCRIPTION**

| Number | Name   | I/O <sup>1</sup> | Function                                                                                            |

|--------|--------|------------------|-----------------------------------------------------------------------------------------------------|

| 1      | MODE   | lpd              | Mode switching/offset correction control input 1                                                    |

| 2      | WRITE  | lpd              | Mode switching/offset correction control input 2                                                    |

| 3      | DGND   | -                | Logic circuit ground. Connect to the analog ground if there is no dedicated pickup or logic ground. |

| 4      | DVCC   | -                | Logic circuit supply. Connect to the analog supply if there is no dedicated pickup or logic supply. |

| 5      | TEMPO  | 0                | Thermal sensor test output. Leave open for normal operation                                         |

| 6      | TEMPI  | I                | Thermal sensor test input. Leave open for normal operation                                          |

| 7      | T1     | ı                | Tracking PD input A                                                                                 |

| 8      | T2     | I                | Tracking PD input B                                                                                 |

| 9      | Т3     | I                | Tracking PD input C                                                                                 |

| 10     | T4     | ı                | Tracking PD input D                                                                                 |

| 11     | F1     | I                | Focus PD input E                                                                                    |

| 12     | F2     | I                | Focus PD input F                                                                                    |

| 13     | AGND   | -                | Analog circuit ground                                                                               |

| 14     | VREF   | I                | 2.0 V reference voltage input                                                                       |

| 15     | FSUBB  | I                | Focus error signal feedback input                                                                   |

| 16     | FSUB   | 0                | Focus error signal output                                                                           |

| 17     | FADDB  | I                | Focus sum signal feedback input                                                                     |

| 18     | FADD   | 0                | Focus sum signal output                                                                             |

| 19     | AGND   | -                | Analog circuit ground                                                                               |

| 20     | AVCC   | -                | Analog circuit supply                                                                               |

| 21     | DPDD   | 0                | Buffered tracking signal output D for DPD servo                                                     |

| 22     | DPDC   | 0                | Buffered tracking signal output C for DPD servo                                                     |

| 23     | DPDB   | 0                | Buffered tracking signal output B for DPD servo                                                     |

| 24     | DPDA   | 0                | Buffered tracking signal output A for DPD servo                                                     |

| 25     | DATAN  | 0                | Phase-modulated data signal differential inverting output                                           |

| 26     | DATAP  | 0                | Phase-modulated data signal differential non-inverting output                                       |

| 27     | TSUBB  | I                | Tracking push-pull signal feedback input                                                            |

| 28     | TSUB   | 0                | Tracking push-pull signal output                                                                    |

| 29     | CAPAN  | 0                | ID data signal differential inverting output                                                        |

| 30     | CAPAP  | 0                | ID data signal differential non-inverting output                                                    |

| 31     | TADDB  | ı                | Tracking PD sum signal feedback input                                                               |

| 32     | TADD   | 0                | Tracking PD sum signal output                                                                       |

| 33     | CALREQ | 0                | Offset correction status/request output                                                             |

| 34     | SENB   | 1                | Serial interface enable input                                                                       |

| 35     | SDATA  | I/O              | Serial interface data input/acknowledge output                                                      |

| 36     | SCLK   | I                | Serial interface clock input                                                                        |

$<sup>1. \</sup>quad I = input, \ Ipd = Input \ with \ built-in \ pull-down \ resistor, \ I/O = input/output, \ O = output$

## **SPECIFICATIONS**

# **Absolute Maximum Ratings**

GND = 0 V

| Parameter                   | Symbol           | Condition | Rating                   | Unit |

|-----------------------------|------------------|-----------|--------------------------|------|

| Supply voltage range        | V <sub>CC</sub>  |           | -0.5 to 7.0              | V    |

| Input voltage range         | V <sub>IN</sub>  |           | $-0.5$ to $V_{CC} + 0.5$ | V    |

| Input current range         | I <sub>IN</sub>  |           | - 3.0 to +3.0            | mA   |

| Operating temperature range | T <sub>opr</sub> |           | 0 to 70                  | °C   |

| Storage temperature range   | T <sub>stg</sub> |           | -40 to 125               | °C   |

| Power dissipation           | P <sub>D</sub>   |           | 250                      | mW   |

| Soldering temperature       | T <sub>sld</sub> |           | 260                      | °C   |

| Soldering time              | t <sub>sld</sub> |           | 10                       | S    |

# **Recommended Operating Conditions**

GND = 0 V

| Parameter                             | Symbol           | Condition | Rating       | Unit |

|---------------------------------------|------------------|-----------|--------------|------|

| Specs-guaranteed supply voltage range | V <sub>CC</sub>  |           | 4.75 to 5.25 | V    |

| Operating supply voltage range        | V <sub>CC</sub>  |           | 4.5 to 5.5   | V    |

| Reference voltage input               | V <sub>REF</sub> |           | 1.89 to 2.11 | V    |

| Operating temperature range           | T <sub>opr</sub> |           | 0 to 70      | °C   |

## **DC Electrical Characteristics**

$$V_{CC}$$

= 5 V ± 5%, GND = 0 V,  $T_a$  = 0 to 70 °C

| Parameter                                               | Symbol           | Condition                         |                       | Rating |                    |      |  |

|---------------------------------------------------------|------------------|-----------------------------------|-----------------------|--------|--------------------|------|--|

| Parameter                                               | Syllibol         | Condition                         | min                   | typ    | max                | Unit |  |

| Comment accomment on 1                                  | I <sub>CC1</sub> | Operating mode                    | -                     | 24     | 30                 | mA   |  |

| Current consumption I                                   | I <sub>CC2</sub> | Sleep mode                        | -                     | ı      | 1                  | IIIA |  |

| MODE, WRITE, SENB, SDATA, SCLK HIGH-level input voltage | V <sub>IH</sub>  |                                   | 0.8V <sub>CC</sub>    | -      | -                  | V    |  |

| MODE, WRITE, SENB, SDATA, SCLK LOW-level input voltage  | V <sub>IL</sub>  |                                   | -                     | -      | 0.2V <sub>CC</sub> | V    |  |

| MODE, WRITE HIGH-level input current                    | I <sub>IH1</sub> | V <sub>IN</sub> = V <sub>CC</sub> | 50                    | 100    | 200                | μΑ   |  |

| SENB, SDATA, SCLK HIGH-level input current              | I <sub>IH2</sub> | V <sub>IN</sub> = V <sub>CC</sub> | -                     | -      | 3                  | μΑ   |  |

| MODE, WRITE, SENB, SDATA, SCLK LOW-level input current  | I <sub>IL</sub>  | V <sub>IN</sub> = 0 V             | -3                    | -      | -                  | μА   |  |

| CALREQ HIGH-level output voltage                        | V <sub>OH</sub>  | I <sub>OH</sub> = -0.2 mA         | V <sub>CC</sub> - 0.2 | -      | -                  | V    |  |

| CALREQ LOW-level output voltage                         | V <sub>OL1</sub> | I <sub>OL</sub> = 0.8 mA          | -                     | -      | 0.4                | V    |  |

| SDATA LOW-level output voltage                          | V <sub>OL2</sub> | I <sub>OL</sub> = 7 mA            | -                     | -      | 1.0                | V    |  |

| VREF input current                                      | I <sub>REF</sub> | V <sub>REF</sub> = 2.0 V          | _                     | _      | 250                | μΑ   |  |

<sup>1.</sup>  $18 \text{ k}\Omega$  resistor connected between TSUB and TSUBB

## **Tracking PD Input Characteristics (T1, T2, T3, T4)**

$$V_{CC}$$

= 5 V  $\pm$  5%, GND = 0 V,  $T_a$  = 0 to 70 °C

| Parameter                      | Condition         |                       |     | Unit  |     |                   |

|--------------------------------|-------------------|-----------------------|-----|-------|-----|-------------------|

| Faranietei                     |                   |                       | min | typ   | max | Oill              |

| Input impedance                | No signal         |                       | -   | -     | 250 | Ω                 |

| Input conversion noise current | 100 kHz to 10 MHz | RAM read <sup>1</sup> | -   | 0.035 | -   |                   |

|                                |                   | ROM read <sup>1</sup> | -   | 0.27  | -   | μA <sub>rms</sub> |

| Pin voltage                    | No signal         | •                     | -   | -     | 1.5 | V                 |

<sup>1.</sup> DATAP – DATAN output difference operation when 10 pF capacitors are connected to T1, T2, T3, T4

<sup>47</sup>  $k\Omega$  resistor connected between TADD and TADDB

<sup>22</sup>  $\mbox{k}\Omega$  resistor connected between FSUB and FSUBB

<sup>27</sup>  $k\Omega$  resistor connected between FADD and FADDB

SENB, SDATA, SCLK connected to GND; All other pins (excluding supply and ground pins) open circuit.

## **Data Signal Processor Characteristics**

$$V_{CC}$$

= 5 V ± 5%, GND = 0 V,  $T_a$  = 0 to 70 °C

| Parameter                                                         | Condition                                   |                     | Unit |                     |       |

|-------------------------------------------------------------------|---------------------------------------------|---------------------|------|---------------------|-------|

| raiailletei                                                       | Condition                                   | min                 | typ  | max                 | Offic |

| DATAP-DATAN current-to-voltage                                    | RAM read                                    | 10.0                | 12.5 | 15.0                | kΩ    |

| converter coefficient <sup>1</sup>                                | ROM read                                    | 2.50                | 3.12 | 3.74                | K22   |

| CAPAP—CAPAN current-to-voltage converter coefficient <sup>2</sup> | RAM read                                    | 11.3                | 14.1 | 16.9                | kΩ    |

| DATAP, DATAN, CAPAP, CAPAN output impedance                       |                                             | -                   | -    | 100                 | Ω     |

| DATAP, DATAN, CAPAP, CAPAN output center voltage <sup>3</sup>     | No signal                                   | 0.9V <sub>REF</sub> | -    | 1.1V <sub>REF</sub> | V     |

| CAPAP, CAPAN output center voltage difference <sup>3</sup>        | No signal                                   | -                   | -    | ±50                 | mV    |

| DATAP, DATAN, CAPAP, CAPAN output operating output voltage        | 10 kΩ load, output center voltage reference | -0.7                | -    | +0.7                | V     |

| Variable coefficient switching time                               | $RAM \leftrightarrow ROM$ read              | -                   | -    | 10                  | ms    |

| Saturation output reset time <sup>4</sup>                         | RAM write → RAM read                        | -                   | -    | 500                 | ns    |

| DATAP, DATAN signal bandwidth <sup>5</sup>                        | f = 100 kHz –3 dB frequency                 | 19                  | -    | -                   | MHz   |

| CAPAP, CAPAN signal bandwidth <sup>5</sup>                        | f = 100 kHz –3 dB frequency                 | 20                  | -    | -                   | MHz   |

| DATAP-DATAN, CAPAP-CAPAN gain peaking <sup>5</sup>                | f = 100 kHz –3 dB frequency                 | -3                  | -    | +0.5                | dB    |

| DATAP-DATAN, CAPAP-CAPAN group delay time <sup>5</sup>            | f = 1 to 10 MHz                             | -                   | -    | ±1.0                | ns    |

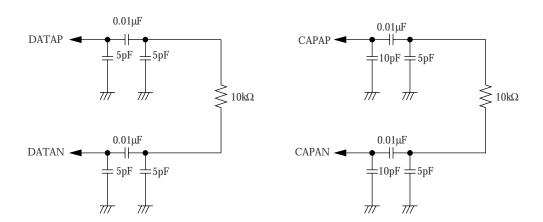

- 1. [DATAP DATAN] =  $K \times [I_{T1} + I_{T2} + I_{T3} + I_{T4}]$ 2. [CAPAP CAPAN] =  $K \times \{[I_{T1} + I_{T2}] [I_{T3} + I_{T4}]\}$ 3.  $5 \text{ } \Omega$  load connected to ground to prevent abnormal operation

- 4. Converging to within final value ± 10%

- 5. 10 pF input load capacitors connected to T1, T2, T3, T4. DATAP, DATAN, CAPAP, CAPAN output load conditions shown below.

# **Tracking Signal Processor Characteristics**

$V_{CC}$  = 5 V  $\pm$  5%, GND = 0 V,  $T_a$  = 0 to 70 °C

| Parameter                                                  | Condition                                                        |                                                                      |                  | Unit  |       |       |

|------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------|------------------|-------|-------|-------|

| raniotor                                                   |                                                                  | Condition                                                            |                  | typ   | max   | O.I.K |

|                                                            | RAM read                                                         |                                                                      | 10.64            | 11.95 | 13.26 |       |

| TSUB current-to-voltage converter coefficient <sup>1</sup> | ROM read                                                         | $R_f = 18 \text{ k}\Omega,$<br>$V_{OUT} = V_{REF} \pm 0.8 \text{ V}$ | 2.67             | 2.99  | 9.92  | kΩ    |

|                                                            | RAM write                                                        | - OUT REI                                                            | 1.78             | 1.99  | 2.20  |       |

|                                                            | RAM read                                                         |                                                                      | 27.82            | 31.25 | 34.68 |       |

| FADD current-to-voltage converter coefficient <sup>2</sup> | ROM read                                                         | $R_f = 47 \text{ k}\Omega$                                           | 6.95             | 7.80  | 8.65  | kΩ    |

|                                                            | RAM write                                                        |                                                                      | 4.63             | 5.20  | 5.77  |       |

| OPDA, DPDB, DPDC, DPDD                                     | RAM read                                                         |                                                                      | 40.0             | 50.0  | 60.0  | 10    |

| current-to-voltage converter coefficient <sup>3</sup>      | ROM read                                                         |                                                                      | 10.0             | 12.5  | 15.0  | kΩ    |

| T1, T2, T3, T4 converter coefficient relative error        | TSUB output, RA                                                  | M/ROM read                                                           | -                | -     | ±2    | %     |

| TSUB, TADD, DPDA, DPDB, DPDC,<br>DPDD output impedance     |                                                                  |                                                                      | -                | -     | 100   | Ω     |

| TSUB operating output voltage                              | 10 kΩ load conne                                                 | cted to VREF                                                         | 1                | -     | 3     | V     |

| TADD, DPDA, DPDB, DPDC, DPDD operating output voltage      | 10 kΩ load conne                                                 | cted to VREF                                                         | V <sub>REF</sub> | -     | 3     | V     |

|                                                            | $RAMread \leftrightarrow ROMread$                                |                                                                      | -                | -     | 10    | ms    |

| Converter coefficient switching time                       | RAM write ↔ RA                                                   | M read                                                               | -                | -     | 3     | μs    |

| TSUB, TADD signal bandwidth <sup>4</sup>                   | DC to -3 dB frequency                                            |                                                                      | 1                | -     | -     | MHz   |

| DPDA, DPDB, DPDC, DPDD signal<br>bandwidth <sup>4</sup>    | f = 100 kHz to -3 dB frequency                                   |                                                                      | 5                | -     | -     | MHz   |

| TSUB, TADD gain peaking <sup>4</sup>                       | f = 10 kHz to -3 d                                               | B frequency                                                          | -3               | -     | +0.5  | dB    |

| DPDA, DPDB, DPDC, DPDD gain<br>peaking <sup>4</sup>        | f = 100 kHz to -3                                                | dB frequency                                                         | -3               | -     | +4.0  | dB    |

| TSUB phase response <sup>4</sup>                           | @ f = 100 kHz                                                    |                                                                      | -                | -     | 10    | ٥     |

| DPDA, DPDB, DPDC, DPDD group                               | f = 1 to 5 MHz gro<br>absolute value                             | up delay differential                                                | -                | -     | 5     | ns    |

| delay <sup>4</sup>                                         | Relative error betv                                              | veen 4 pins                                                          | -                | -     | 1.0   |       |

|                                                            |                                                                  | RAM read/write max gain                                              | -                | _     | ±10.0 |       |

| TCUD offeet vallege                                        | No input signal,<br>V <sub>REF</sub> reference,                  | RAM read, min to max gain                                            | -                | -     | ±26   |       |

| TSUB offset voltage                                        | post-correction,<br>$T_a = 25$ °C,<br>$R_f = 18 \text{ k}\Omega$ | RAM read/write differential gain max.                                | -                | -     | ±4    | - mV  |

|                                                            |                                                                  | ROM read,<br>gain min/max                                            | -                | -     | ±100  |       |

| TADD offset voltage                                        | No input signal,                                                 | RAM read                                                             | -                | -     | ±30   | m\/   |

| TADD offset voltage                                        | V <sub>REF</sub> reference                                       | ROM read                                                             | -                | -     | ±300  | – mV  |

| DPDA, DPDB, DPDC, DPDD offset<br>voltage                   | No input signal,<br>V <sub>REF</sub> reference                   | RAM/ROM read                                                         | -550             | -     | +50   | mV    |

| TSUB offset voltage temperature coefficient                | $R_f = 18 \text{ k}\Omega$                                       |                                                                      | -                | -     | ±0.4  | mV/°C |

| TSUB variable gain range                                   |                                                                  |                                                                      | -16              | -     | +14   | dB    |

| TSUB variable gain step width                              |                                                                  |                                                                      | -                | 2     | _     | dB    |

| Parameter                             | C                                     | Condition    |     | Rating |      |      |  |

|---------------------------------------|---------------------------------------|--------------|-----|--------|------|------|--|

|                                       |                                       | ondition     | min | typ    | max  | Unit |  |

| TSUB gain switching absolute accuracy | V <sub>OUT</sub> = V <sub>REF</sub> ± | -16 to +8 dB | -   | -      | ±0.5 | dB   |  |

|                                       | 0.8 V +10 to +14 dB                   |              | -   | -      | ±1.0 | uБ   |  |

<sup>1.</sup> TSUB =  $K \times \{[I_{T1} + I_{T2}] - [I_{T3} + I_{T4}]\}$ , gain = 0 dB

TSUB, TADD, DPDA, DPDB, DPDC, DPDD: 10 pF output load capacitance

TSUB, TADD: 10  $k\Omega$  load resistance

DPDA, DPDB, DPDC, DPDD: 100  $k\Omega$  load resistance

## Focus PD Input Characteristics (F1, F2)

$$V_{CC}$$

= 5 V  $\pm$  5%, GND = 0 V,  $T_a$  = 0 to 70 °C

| Parameter                      | Condition                             |                        |     | Unit |     |                   |

|--------------------------------|---------------------------------------|------------------------|-----|------|-----|-------------------|

| raianietei                     |                                       |                        | min | typ  | max | Offic             |

| Input impedance                | No signal                             |                        | -   | -    | 250 | Ω                 |

|                                |                                       | RAM read <sup>1</sup>  | -   | -    | 24  |                   |

| Input conversion noise current | DC to 10 kHz                          | ROM read <sup>1</sup>  | -   | -    | 96  | nA <sub>rms</sub> |

|                                |                                       | RAM write <sup>1</sup> | -   | -    | 150 |                   |

| Pin voltage                    | No signal, V <sub>REF</sub> reference |                        | -   | -    | ±50 | mV                |

<sup>1.</sup> Conversion from FSUB output noise value when 14 pF capacitors connected to F1 and F2

## **Focus Signal Processor Characteristics**

$$V_{CC} = 5 \text{ V} \pm 5\%$$

, GND = 0 V,  $T_a = 0$  to 70 °C

| Parameter                                                  | Condition                      |                                                                       |                  | Unit |      |      |

|------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------|------------------|------|------|------|

| raianietei                                                 |                                | onunion                                                               | min              | typ  | max  | Oill |

|                                                            | RAM read                       |                                                                       | 370              | 415  | 460  |      |

| FSUB current-to-voltage converter coefficient <sup>1</sup> | ROM read                       | $R_f = 22 \text{ k}\Omega,$<br>$V_{OUT} = V_{REF} \pm 0.35 \text{ V}$ | 94               | 105  | 116  | kΩ   |

|                                                            | RAM write                      | OUT KEI                                                               | 58               | 65   | 72   |      |

|                                                            | RAM read                       |                                                                       | 223              | 250  | 277  |      |

| FADD current-to-voltage converter coefficient <sup>2</sup> | ROM read                       | $R_f = 27 \text{ k}\Omega$                                            | 56.1             | 63   | 69.9 | kΩ   |

|                                                            | RAM write                      |                                                                       | 35.6             | 40   | 44.1 |      |

| F1, F2 converter coefficient relative error                | FSUB output, RAM/ROM read      |                                                                       | -                | -    | ±2   | %    |

| FSUB, FADD output impedance                                |                                |                                                                       | -                | -    | 100  | Ω    |

| FSUB operating output voltage                              | 10 kΩ load connec              | cted to VREF                                                          | 1                | -    | 3    | V    |

| FADD operating output voltage                              | 10 kΩ load connec              | cted to VREF                                                          | V <sub>REF</sub> | -    | 3    | V    |

| Converter coefficient quitables time                       | RAM read $\leftrightarrow$ ROI | M read                                                                | -                | -    | 10   | ms   |

| Converter coefficient switching time                       | RAM write ↔ RAI                | M read                                                                | -                | -    | 3    | μs   |

| FSUB, FADD signal bandwidth <sup>3</sup>                   | DC to -3 dB frequency          |                                                                       | 200              | -    | -    | kHz  |

| FSUB, FADD gain peaking <sup>3</sup>                       | f = 10 kHz to -3 dB frequency  |                                                                       | -3               | -    | +0.5 | dB   |

| FSUB, FADD phase response <sup>3</sup>                     | @ f = 10 kHz                   |                                                                       | -                | -    | 5    | 0    |

<sup>2.</sup> TADD =  $K \times [I_{T1} + I_{T2} + I_{T3} + I_{T4}]$ 3. DPDA =  $K \times I_{T1}$ , DPDB =  $K \times I_{T2}$ , DPDC =  $K \times I_{T3}$ , DPDD =  $K \times I_{T4}$ 4. T1, T2, T3, T4: 10 pF input load capacitance

| Parameter                                   |                                                 | Condition                             |     | Rating |       |       |  |

|---------------------------------------------|-------------------------------------------------|---------------------------------------|-----|--------|-------|-------|--|

| Parameter                                   |                                                 | onanion                               | min | typ    | max   | Unit  |  |

| FSUB offset voltage                         | No input signal,                                | RAM read/write, ROM read max gain     | -   | -      | ±7.0  |       |  |

|                                             | V <sub>REF</sub> reference,<br>post-correction, | RAM read, min to max gain             | -   | -      | ±21   | mV    |  |

|                                             | T <sub>a</sub> = 25°C                           | RAM read/write differential gain max. | -   | -      | ±4    |       |  |

| FADD offset voltage                         | No input signal, V <sub>F</sub>                 | REF reference                         | -   | -      | ±50   | mV    |  |

| FSUB offset voltage temperature coefficient |                                                 |                                       | -   | -      | ±0.22 | mV/°C |  |

| FSUB variable gain range                    |                                                 |                                       | -16 | -      | +14   | dB    |  |

| FSUB variable gain step width               |                                                 |                                       | -   | 2      | -     | dB    |  |

| FSUB gain switching absolute accuracy       | V <sub>OUT</sub> = V <sub>REF</sub> ±           | -16 to +8 dB                          | -   | -      | ±0.5  | 40    |  |

|                                             | 0.35 V                                          | +10 to +14 dB                         | -   | -      | ±1.0  | - dB  |  |

## **Mode Control Logic**

| Contro      | ol input    | Operating mode | Offset correction |  |

|-------------|-------------|----------------|-------------------|--|

| WRITE       | MODE        | Operating mode |                   |  |

| LOW or open | LOW or open | RAM read       |                   |  |

| LOW or open | HIGH        | ROM read       | Active            |  |

| HIGH        | LOW or open | DAM write      |                   |  |

| HIGH        | HIGH        | RAM write      | Inactive          |  |

## **Offset Correction Characteristics**

$$V_{CC}$$

= 5 V  $\pm$  5%, GND = 0 V,  $T_a$  = 0 to 70  $^{\circ}C$

| Parameter                                    | Cumbal           | Condition                                          |     | I In it |      |      |

|----------------------------------------------|------------------|----------------------------------------------------|-----|---------|------|------|

| Parameter                                    | Symbol Condition |                                                    | min | typ     | max  | Unit |

| TSUB offset residual                         |                  | V <sub>REF</sub> reference, T <sub>a</sub> = 25 °C | -   | -       | ±8.5 | mV   |

| FSUB offset residual                         |                  | V <sub>REF</sub> reference, T <sub>a</sub> = 25 °C | -   | -       | ±5.5 | mV   |

| Supply voltage droop detect level            | V <sub>1</sub>   |                                                    | 1.9 | 2.8     | 3.7  | V    |

| Correction circuit startup supply voltage    | V <sub>2</sub>   |                                                    | 3.2 | 3.8     | 4.4  | V    |

| V <sub>1</sub> and V <sub>2</sub> difference | $V_2 - V_1$      |                                                    | 0.7 | 1.0     | 1.3  | V    |

| Correction thermal sensor detect temperature |                  |                                                    | 15  | 20      | 25   | °C   |

| Offset correction time                       |                  |                                                    | -   | -       | 150  | ms   |

<sup>1.</sup> FSUB =  $K \times [I_{F1} - I_{F2}]$ , gain = 0 dB 2. FADD =  $K \times [I_{F1} + I_{F2}]$ 3. F1, F2: 14 pF input load capacitance

FSUB, FADD: 10 pF output load capacitance, 10  $k\Omega$  load resistance

## **Serial Interface Characteristics**

$$V_{CC}$$

= 5 V  $\pm$  5%, GND = 0 V,  $T_a$  = 0 to 70 °C

| Parameter                   | Symbol             | Condition |     | Unit |     |       |

|-----------------------------|--------------------|-----------|-----|------|-----|-------|

| Parameter                   | Syllibol           |           | min | typ  | max | Oilli |

| SCLK pulse cycle            | t <sub>cySCK</sub> |           | 100 | -    | -   | ns    |

| SCLK HIGH-level pulsewidth  | t <sub>whSCK</sub> |           | 40  | -    | -   | ns    |

| SCLK LOW-level pulsewidth   | t <sub>wisck</sub> |           | 40  | -    | -   | ns    |

| SENB setup time             | t <sub>sSEN</sub>  |           | 20  | _    | _   | ns    |

| SENB hold time              | t <sub>hSEN</sub>  |           | 40  | _    | _   | ns    |

| SDATA setup time            | t <sub>sSDA</sub>  |           | 15  | _    | _   | ns    |

| SDATA hold time             | t <sub>hSDA</sub>  |           | 15  | -    | -   | ns    |

| ACK setup time <sup>1</sup> | t <sub>sACK</sub>  |           | 0   | -    | 20  | ns    |

| ACK hold time <sup>1</sup>  | t <sub>hACK</sub>  |           | -   | -    | 50  | ns    |

| SENB interval               | t <sub>inSEN</sub> |           | 100 | _    | -   | ns    |

<sup>1.</sup> ACK is the acknowledge output (n-channel open-drain). LOW-level output when the data received is valid. SDATA load capacitance is 15 pF.

#### FUNCTIONAL DESCRIPTION

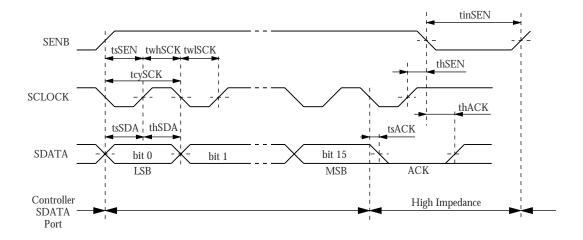

#### Serial Interface

The SM9103M uses a serial interface comprising 2 ports to control and set TSUB/FSUB output gain switching, sleep mode to reduce current consump-

tion, and TSUB/FSUB offset correction. The address and bit configuration of each port is shown in table 1.

Table 1. Port address and bit configuration<sup>1</sup>

|     | Bit number   |     |     |     |     |     |     |   |     |     |     |     |      |   |   |

|-----|--------------|-----|-----|-----|-----|-----|-----|---|-----|-----|-----|-----|------|---|---|

| 15  | 14           | 13  | 12  | 11  | 10  | 9   | 8   | 7 | 6   | 5   | 4   | 3   | 2    | 1 | 0 |

|     | Data Address |     |     |     |     |     |     |   |     |     |     |     |      |   |   |

| MSB | В            |     |     |     |     |     | LSB |   |     |     |     |     |      |   |   |

| TG3 | TG2          | TG1 | TG0 | FG3 | FG2 | FG1 | FG0 | × | LOW | LOW | LOW | LOW | LOW  | × | × |

| SL1 | CS1          | -   | -   | -   | -   | -   | -   | × | LOW | LOW | LOW | LOW | HIGH | × | × |

1.  $\times$  = don't care, - = unassigned

TG3 to TG0: TSUB gain set bits. Default = 0111 (0 dB)

FG3 to FG0: FSUB gain set bits. Default = 0111 (0 dB)

SL1: sleep mode set bit. Sleep mode when 1, normal operation when 0. Default = 0.

CS1: offset correction control. Offset correction when 1, normal operation when 0. Default = 0.

Serial data is input on SDATA with the LSB first in sync with the falling edge of the SCLK clock. After the 16th SCLK falling edge and 16 bits of valid data has been input, the SDATA n-channel open-drain output goes LOW to perform the function of an acknowledge signal.

If the number of SCLK cycles which occur when SENB (serial interface enable) is HIGH is less than

# 16, the received data is ignored and the internal port is not updated. If the number of SCLK cycles is greater than 16, the data is still considered value up to the 16th SCLK falling edge, the data is latched into the internal port, and the acknowledge signal is output. The acknowledge signal is held until SENB goes LOW again.

#### **Data Signal Processor**

This stage creates the data signal and ID signal for output. The weak current from the tracking PD cells (T1, T2, T3, T4) are input to the front-end amplifier where the signals are current-to-voltage converted at fixed gain.

The gain setting is controlled by pins WRITE and MODE. WRITE switches between read/write, and MODE switches the gain between values corresponding to high-reflectivity and low-reflectivity discs. These signals control the settings for RAM (low-reflectivity disc) read/write and ROM (high-reflectivity disc) read.

The front-end amplifier outputs are processed by the signal processor block to generate intermediate signals. The data signal, (A + B + C + D), is converted to a difference signal by a differential output buffer and output on DATAP and DATAN. The ID signal, generated from the difference between 2 signals, (A + B) and (C + D), is converted to a difference signal by a differential output buffer and output on CAPAP and CAPAN. The data signal (DATAP, DATAN) and ID signal (CAPAP, CAPAN) DC components are removed using output stage capacitive networks.

T1, T2, T3 and T4 have a hold function to provide the appropriate reverse bias required by the tracking PD to ensure the data read bandwidth.

## **Tracking Signal Processor**

The tracking stage generates the push-pull tracking error signal and output signal for DPD servo, as well as a push-pull sum signal used as an auxiliary signal.

The [(A + B) - (C + D)] signal from the common-data front-end amplifier and signal processor block is sent to the gain switching block. The gain switching block amplifies the difference signal using one of 16 preset gain settings in 2 dB steps to form a push-pull signal output on TSUB. A feedback resistor connected to TSUBB is used to ensure gain setting stability. The gain of the gain switching block is controlled by serial interface control bits as shown in table 2.

Each signal from T1, T2, T3, T4 is buffered and then output on DPDA, DPDB, DPDC, DPDD, respectively, for DPD servos.

The auxiliary signal is generated from the push-pull sum signal (A + B + C + D). This signal is buffered (TAB) and output on TADD. A feedback resistor connected to TADDB is used to ensure gain setting stability.

Table 2. TSUB gain setting

| TG3 | TG2 | TG1 | TG0 | Gain (dB) <sup>1</sup> |

|-----|-----|-----|-----|------------------------|

| 0   | 0   | 0   | 0   | +14                    |

| 0   | 0   | 0   | 1   | +12                    |

| 0   | 0   | 1   | 0   | +10                    |

| 0   | 0   | 1   | 1   | +8                     |

| 0   | 1   | 0   | 0   | +6                     |

| 0   | 1   | 0   | 1   | +4                     |

| 0   | 1   | 1   | 0   | +2                     |

| 0   | 1   | 1   | 1   | 0                      |

| 1   | 0   | 0   | 0   | -2                     |

| 1   | 0   | 0   | 1   | -4                     |

| 1   | 0   | 1   | 0   | -6                     |

| 1   | 0   | 1   | 1   | -8                     |

| 1   | 1   | 0   | 0   | -10                    |

| 1   | 1   | 0   | 1   | -12                    |

| 1   | 1   | 1   | 0   | -14                    |

| 1   | 1   | 1   | 1   | -16                    |

<sup>1.</sup> Default is 0 dB

## **Focus Signal Processor**

The focus stage generates the focus error signal from the focus PD, and a sum signal. The weak focus PD current signals (F1, F2) are input to the front-end amplifier and then current-to-voltage converted at fixed gain.

The front-end amplifier output is sent to the signal processor block where the focus error signal (F1 – F2) and the sum signal (F1 + F2) are generated.

The focus error signal is sent to the gain switching block. The gain switching block amplifies the difference signal using one of 16 preset gain settings in 2 dB steps with output on FSUB. A feedback resistor connected to FSUBB is used to ensure gain setting stability. The gain of the gain switching block is controlled by serial interface control bits as shown in table 3.

The sum is buffered and output on FADD. A feed-back resistor connected to FADDB is used to ensure gain setting stability.

Table 3. FSUB gain setting

| FG3             | FG2 | FG1 | FG0 | Gain (dB) <sup>1</sup> |  |  |

|-----------------|-----|-----|-----|------------------------|--|--|

| 0               | 0   | 0   | 0   | +14                    |  |  |

| 0               | 0   | 0   | 1   | +12                    |  |  |

| 0               | 0   | 1   | 0   | +10                    |  |  |

| 0               | 0   | 1   | 1   | +8                     |  |  |

| 0               | 1   | 0   | 0   | +6                     |  |  |

| 0               | 1   | 0   | 1   | +4                     |  |  |

| 0               | 1   | 1   | 0   | +2                     |  |  |

| 0               | 1   | 1   | 1   | 0                      |  |  |

| 1               | 0   | 0   | 0   | -2                     |  |  |

| 1               | 0   | 0   | 1   | -4                     |  |  |

| 1               | 0   | 1   | 0   | -6                     |  |  |

| 1               | 0   | 1   | 1   | -8                     |  |  |

| 1               | 1   | 0   | 0   | -10                    |  |  |

| 1               | 1   | 0   | 1   | -12                    |  |  |

| 1               | 1   | 1   | 0   | -14                    |  |  |

| 1               | 1   | 1   | 1   | -16                    |  |  |

| Defeate to 0.4D |     |     |     |                        |  |  |

<sup>1.</sup> Default is 0 dB

#### Offset Correction

The SM9103M has built-in offset correction circuits for tracking and focus. During offset correction, the internal the device operates in RAM read mode, and FSUB and TSUB operate at maximum gain (+14 dB). The outputs on FSUB, FADD and TSUB are indeterminate. Also, inputs T1, T2, T3, T4 and F1, F2 may be ignored. After correction is complete, the FSUB and TSUB gain settings return to their default values (0 dB).

Offset correction is performed under the following conditions:

- When power is applied.

- When the supply drops below  $2.8 \pm 0.9$  V and then rises to above  $3.8 \pm 0.6$  V.

- When sleep mode operation is cancelled.

- When the serial interface bit CS1 is 1. Note that if SL1 is also 1, then SL1 has priority.

Table 4. Offset correction setting

| CS1 | Offset correction <sup>1</sup> |  |  |

|-----|--------------------------------|--|--|

| 0   | No correction                  |  |  |

| 1   | Correction                     |  |  |

1. Default is No correction

#### Sleep Mode

The SM9103M features a sleep mode which can be used when the device is not operating to significantly reduce current consumption. The sleep mode is controlled by serial interface bit SL1.

If the voltage falls below  $2.8 \pm 0.9$  V during offset correction, then correction stops and does not restart until the supply recovers to above  $3.8 \pm 0.6$  V.

During offset correction, the CALREQ output is held HIGH. CALREQ goes LOW after correction stops.

The SM9103M also incorporates a temperature detect function which detects temperature changes of  $20\pm5$  °C from the time the initial correction is performed. If a temperature change is detected, CAL-REQ goes HIGH and the device waits for an offset correction instruction.

Note that when both WRITE and MODE are HIGH, offset correction is inactive and the output appears uncorrected. However, if a correction start condition occurs when correction is inactive, such as the correction flag CS1 set to 1, then correction operation is initiated internally but does not appear at the output unless correction is activated prior to correction operation finishing.

Once correction has been made inactive, the output remains uncorrected even if correction is subsequently reactivated. In this case, the output remains uncorrected until a valid correction start condition is detected.

Table 5. Sleep mode settings

| SL1  | Sleep mode <sup>1</sup> | Mode description |

|------|-------------------------|------------------|

| LOW  | OFF                     | Normal operation |

| HIGH | ON                      | Sleep condition  |

1. Default is OFF

## **Preset Function**

When power is applied or after offset correction, all serial interface flags are reset to their default values.

Flags TG3 to TG0 and FG3 to FG0 are also set to their default values in sleep mode.

NIPPON PRECISION CIRCUITS INC. reserves the right to make changes to the products described in this data sheet in order to improve the design or performance and to supply the best possible products. Nippon Precision Circuits Inc. assumes no responsibility for the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision Circuits Inc. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification. The products described in this data sheet are not intended to use for the apparatus which influence human lives due to the failure or malfunction of the products. Customers are requested to comply with applicable laws and regulations in effect now and hereinafter, including compliance with export controls on the distribution or dissemination of the products. Customers shall not export, directly or indirectly, any products without first obtaining required licenses and approvals from appropriate government agencies.

### NIPPON PRECISION CIRCUITS INC.

4-3, Fukuzumi 2-chome Koto-ku, Tokyo 135-8430, Japan Telephone: 03-3642-6661 Facsimile: 03-3642-6698

NC9806AE 1998.12