# SM5823AP High-speed, 24-bit SIPO/PISO Converter

### **OVERVIEW**

The SM5823AP is a high-speed, 24-bit serial-toparallel converter and parallel-to-serial converter fabricated in Molygate <sup>®</sup> CMOS.

The SM5823AP features a mode selection scheme that allows it to operate as 8-, 16- or 24-bit converters (SIPO and PISO). It also features TTL-compatible, buffered input/outputs for easy bus interfacing, 30 MHz maximum operating frequency and low power consumption, making it ideal for digital video and audio signal processing applications.

## FEATURES

- Functions

- 8/16/24-bit serial-to-parallel converter and parallel-to-serial converter

- 30 MHz maximum operating frequency

- 24-bit parallel I/O, general-purpose port bus interface

- Extendable to lengths greater than 24 bits for both SIPO and PISO conversion

- TTL-compatible input/outputs

- 5 ±0.5 V supply

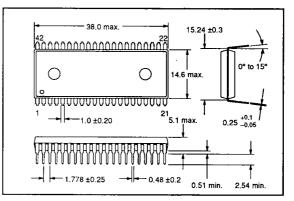

- 42-pin shrink DIP

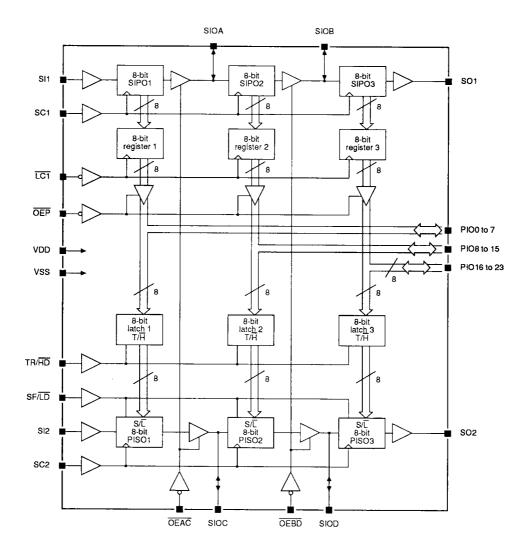

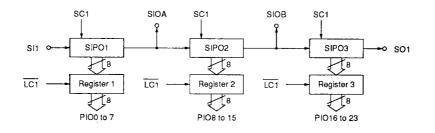

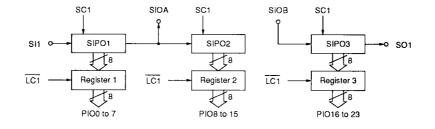

- Component blocks

- Three 8-bit SIPO registers

- Three 8-bit parallel output registers

- Three 8-bit parallel input latches

- Three 8-bit PISO registers

- One 24-bit parallel input/output

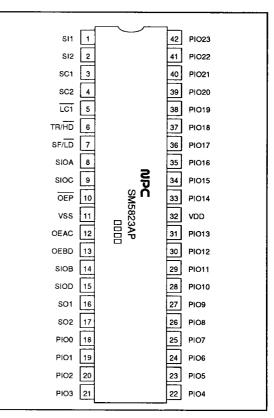

## PINOUT

## PACKAGE DIMENSIONS

#### Unit: mm

## **BLOCK DIAGRAM**

### **PIN DESCRIPTION**

| Number | Name       | I/O | Description                                                          |

|--------|------------|-----|----------------------------------------------------------------------|

| 1      | SI1        | 1   | SIPO serial data 1                                                   |

| 2      | SI2        |     | PISO serial data 1                                                   |

| 3      | SC1        | 1   | SIPO shift clock (rising-edge trigger)                               |

| 4      | SC2        |     | PISO shift clock (rising-edge trigger)                               |

| 5      | <u>LC1</u> | I   | SIPO data latch clock (falling-edge trigger)                         |

| 6      | TR/HD      | I   | PISO data latch clock. Transparent when HIGH and hold when LOW       |

| 7      | SF/LD      | . I | PISO shift/load control signal. Shift when HIGH and load when LOW    |

| 8      | SIOA       | 1/0 | SIPO serial output 1 and SIPO serial input 2                         |

| 9      | SIOC       | 1/0 | PISO serial output 1 and PISO serial input 2                         |

| 10     | OEP        | I   | Parallel output enable signal. Enable when LOW and disable when HIGH |

| 11     | VSS        |     | Ground                                                               |

#### SM5823AP

| Number   | Name           | ٧O  | Description                                                                      |

|----------|----------------|-----|----------------------------------------------------------------------------------|

| 12       | ÖEAC           | 1   | SIOA and SIOC serial output enable signal. Enable when LOW and disable when HIGH |

| 13       | OEBD           |     | SIOB and SIOD serial output enable signal. Enable when LOW and disable when HIGH |

| 14       | SIOB           | I/O | SIPO serial output 2 and SIPO serial input 3                                     |

| 15       | SIOD           | 1/0 | PISO serial output 2 and PISO serial input 3                                     |

| 16       | SO1            | 0   | SIPO serial output 3                                                             |

| 17       | SO2            | 0   | PISO serial output 3                                                             |

| 18 to 31 | PIO0 to PIO13  | 1/0 | Parallel input/outputs                                                           |

| 32       | VDD            |     | 5 ±0.5 V supply                                                                  |

| 33 to 42 | PIO14 to PIO23 | I/O | Parallel input/outputs                                                           |

## SPECIFICATIONS

## Absolute Maximum Ratings

$V_{ss} = 0 V$

| Parameter                 | Symbol           | Rating                       | Unit   |

|---------------------------|------------------|------------------------------|--------|

| Supply voltage range      | V <sub>DD</sub>  | -0.3 to 7.0                  | v      |

| Input voltage range       | V <sub>IN</sub>  | -0.3 to V <sub>DD</sub> +0.3 | v      |

| Power dissipation         | PD               | 500                          | mW     |

| Storage temperature range | T <sub>stg</sub> | -40 to 125                   | deg. C |

| Soldering temperature     | T <sub>sld</sub> | 255                          | deg. C |

| Soldering time            | t <sub>sld</sub> | 10                           | s      |

## **Recommended Operating Conditions**

$V_{ss} = 0 V$

| Parameter                   | Symbol           | Rating     | Unit   |

|-----------------------------|------------------|------------|--------|

| Supply voltage range        | V <sub>DD</sub>  | 4.5 to 5.5 | V      |

| Operating temperature range | Т <sub>орг</sub> | 20 to 70   | deg. C |

#### **DC Electrical Characteristics**

$V_{DD}$  = 4.5 to 5.5 V,  $T_a$  = -20 to 70 deg. C,  $V_{SS}$  = 0 V unless otherwise noted

| Parameter                     | Symbol          | Condition                                        |     | - Unit |     |     |

|-------------------------------|-----------------|--------------------------------------------------|-----|--------|-----|-----|

| Falanielei                    | Symbol          |                                                  | min | typ    | max | Ona |

| Standby current consumption   | ls              | $V_{IN} = V_{DD}$ or 0 V                         |     | -      | 1.0 | μΑ  |

| Operating current consumption | IDD             | $V_{DD} = 5 V$ , f = 30 MHz,<br>all outputs open | _   | -      | 20  | mA  |

| HIGH-level input voltage      | VIH             | See notes 1 and 2.                               | 2.4 | _      | ~   | v   |

| LOW-level input voltage       | ViL             | See notes 1 and 2.                               | -   | -      | 0.5 | V   |

| HIGH-level output voltage     | V <sub>OH</sub> | $I_{OH} = -1.0$ mA.<br>See notes 2 and 3.        | 2.5 | -      | _   | v   |

NIPPON PRECISION CIRCUITS-3

| Parameter                                           | Symbol             | Condition                                                              |                             | Rating |     |     | Unit |

|-----------------------------------------------------|--------------------|------------------------------------------------------------------------|-----------------------------|--------|-----|-----|------|

| Falameter                                           | Symbol Condition   |                                                                        | min typ                     |        | max |     |      |

|                                                     | V <sub>OL1</sub>   | See notes                                                              | l <sub>OL</sub> =<br>4.0 mA | -      | -   | 0.4 | v    |

| LOW-level output voltage                            | V <sub>OL2</sub> 2 | 2 and 3.                                                               | loL =<br>16.0 mA            | -      | -   | 0.8 |      |

| HIGH-level input current                            | l <sub>IH</sub>    | $V_{IN} = V_{DD}$ .                                                    | See note 1.                 | _      | _   | 1.0 | μΑ   |

| LOW-level input current                             | I <sub>IL</sub>    | $V_{iN} = 0 V.$                                                        | See note 1.                 | -      | 10  | 20  | μA   |

| High-impedance output HIGH-level<br>leakage current | I <sub>ZH</sub>    | $V_{\overline{OEP}} = V_{\overline{OE}}$<br>VIH, VOUT =<br>See note 2. |                             | -      | -   | 5.0 | μА   |

| HIGH-impedance output LOW-level<br>leakage current  | I <sub>ZL</sub>    | VOEP = VOE<br>VIH, VOUT =<br>See note 2.                               |                             | -      | _   | 5.0 | μA   |

#### Notes

1. Pins SI1, SI2, SC1, SC2, IC1, TR/HD, SF/ID, OEP, OEAC and OEBD are TTL-level inputs with pull-up resistances.

2. Pins SIOA, SIOB, SIOC, SIOD and PIO0 to PIO23 are TTL-level input/outputs.

3. Pins SO1 and SO2 are TTL-level outputs.

#### **AC Electrical characteristics**

$V_{DD}$  = 4.5 to 5.5 V,  $T_a$  = -20 to 70 deg. C,  $V_{SS}$  = 0 V unless otherwise noted

| Parameter                         | Symbol           | Condition                         |     | Rating |     | Unit |

|-----------------------------------|------------------|-----------------------------------|-----|--------|-----|------|

| rdiameter                         | Symbol           | Condition                         | min | typ    | max | Unit |

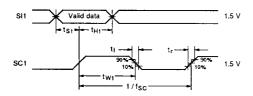

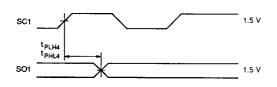

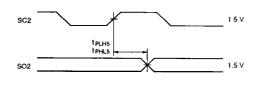

| SC1 and SC2 shift clock frequency | fsc              | 50% duty.<br>See figures 1 and 2. | 0   | -      | 30  | MHz  |

| SI1 to SC1 setup time             | ts1              | Can firme 1                       | 15  | _      | -   | ns   |

| SI1 to SC1 hold time              | tH1              | See figure 1.                     | 0   | -      | -   | ns   |

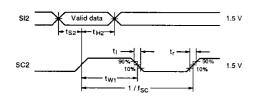

| SI2 to SC2 setup time             | ts2              | 0                                 | 20  | -      | -   | ns   |

| SI2 to SC2 hold time              | t <sub>H2</sub>  | See figure 2.                     | 0   | _      | -   | ns   |

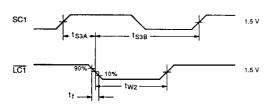

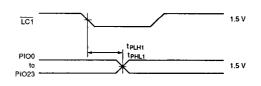

| SC1 to LC1 setup time             | t <sub>S3A</sub> | See figure 3.                     | 15  | _      | _   | ns   |

| Sol to col setup time             | ts3B             |                                   | 5   | -      | -   |      |

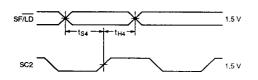

| SF/LD to SC2 setup time           | ts4              |                                   | 15  | _      |     | ns   |

| SF/LD to SC2 hold time            | t <sub>H4</sub>  | See figure 4.                     | 0   | -      | -   | ns   |

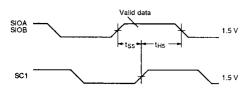

| SIOA, SIOB to SC1 setup time      | tss              | Can have 5                        | 20  | -      | -   | ns   |

| SIOA, SIOB to SC1 hold time       | t <sub>H5</sub>  | See figure 5.                     | 0   | -      | -   | ns   |

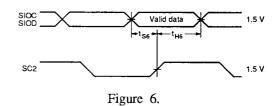

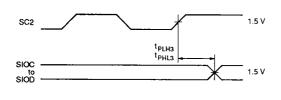

| SIOC, SIOD to SC2 setup time      | t <sub>S6</sub>  | 0                                 | 20  | -      | _   | ns   |

| SIOC, SIOD to SC2 hold time       | t <sub>H6</sub>  | See figure 6.                     | 0   | -      | _   | ns   |

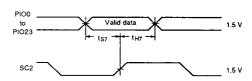

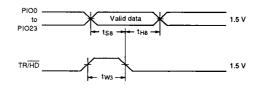

| PIOn to SC2 setup time            | ts7              | $V_{TR/\overline{HD}} = V_{1H}$   | 30  |        | -   | ns   |

| PIOn to SC2 hold time             | tH7              | See figure 7.                     | 0   |        | -   | ns   |

| PIOn to TR/HD setup time          | tsa              |                                   | 20  | -      |     | ns   |

| PIOn to TR/HD hold time           | t <sub>H8</sub>  | - See figure 8.                   | 0   | -      |     | ns   |

| SC1 and SC2 pulsewidth            | tw1              | See figures 1 and 2.              | 15  | -      | ~   | ns   |

| LC1 pulsewidth                    | tw2              | See figure 3.                     | 20  | -      | -   | ns   |

NIPPON PRECISION CIRCUITS-4

#### SM5823AP

| Parameter                                   |                 | O dition                                                                       |     | Rating |     |      |

|---------------------------------------------|-----------------|--------------------------------------------------------------------------------|-----|--------|-----|------|

| raiameter                                   | Symbol          | Condition                                                                      | min | typ    | max | Unit |

| TR/HD pulsewidth                            | tw3             | See figure 8.                                                                  | 20  | -      | -   | ns   |

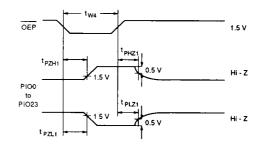

| OEP pulsewidth                              | tw4             | See figure 14.                                                                 | 40  | -      | -   | ns   |

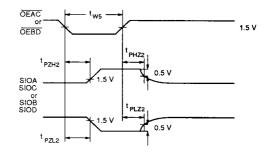

| OEAC and OEBD pulsewidth                    | tws             | See figure 15.                                                                 | 40  | -      | -   | ns   |

| Clock rise time                             | tr              |                                                                                | -   | _      | 100 | ns   |

| Clock fall time                             | t <sub>f</sub>  | - See figures 1 and 2.                                                         | -   | -      | 100 | ns   |

| PIO0 to PIO23 output propagation            | tPLH1           | See note 1.                                                                    | -   | -      | 60  |      |

| delay time                                  | tPHL1           | See figure 9.                                                                  | _   | -      | 60  | ns   |

| SIOA and SIOB output propagation            | tPLH2           | See note 1.                                                                    | _   | -      | 40  |      |

| delay time                                  | tPHL2           | See figure 10.                                                                 | -   | -      | 40  | ns   |

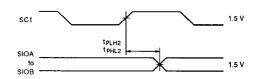

| SIOC and SIOD output propagation delay time | tPLH3           | See note 1.<br>See figure 11.                                                  | -   | _      | 40  |      |

|                                             | tPHL3           |                                                                                | -   | _      | 40  | ns   |

| SO1 output propagation datau time           | tPLH4           | See note 1.<br>See figure 12.                                                  | _   |        | 35  |      |

| SO1 output propagation delay time           | tPHL4           |                                                                                | _   | -      | 35  | ns   |

| SO2 output propagation dolou time           | tPLH5           | See note 1.<br>See figure 13.                                                  | -   | -      | 35  |      |

| SO2 output propagation delay time           | tPHL5           |                                                                                | _   | _      | 35  | ns   |

| PIO0 to PIO23 enable propagation            | tPZL1           | See note 2.                                                                    | _   | _      | 50  |      |

| delay time                                  | tpzh1           | See figure 14.                                                                 | _   | -      | 50  | ns   |

| PIO0 to PIO23 disable propagation           | tPLZ1           | See note 2.                                                                    | -   | _      | 50  |      |

| delay time                                  | tphz1           | See figure 14.                                                                 | -   | _      | 50  | ns   |

| SIOA to SIOD enable propagation             | tpzl2           | See note 2.                                                                    | -   | _      | 40  |      |

| delay time                                  | tpzH2           | See figure 15.                                                                 | _   | -      | 40  | ns   |

| SIOA to SIOD disable propagation            | tPLZ2           | See note 2.                                                                    | -   |        | 40  | 1    |

| delay time                                  | tPHZ2           | See figure 15.                                                                 | _   | -      | 40  | ns   |

| Input capacitance                           | C <sub>in</sub> | f = 1 MHz                                                                      | -   | -      | 10  | ρF   |

| Input/output capacitance                    | Cio             | $f = 1 MHz, V \overline{OEP} = V \overline{OEAC} = V \overline{OEBD} = V_{IH}$ | -   | -      | 20  | pF   |

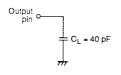

Notes

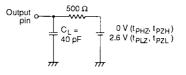

1. Measurement circuit 1

2. Measurement circuit 2

## **Timing Characteristics**

Figure 7.

Figure 8.

Figure 10.

SM5823AP

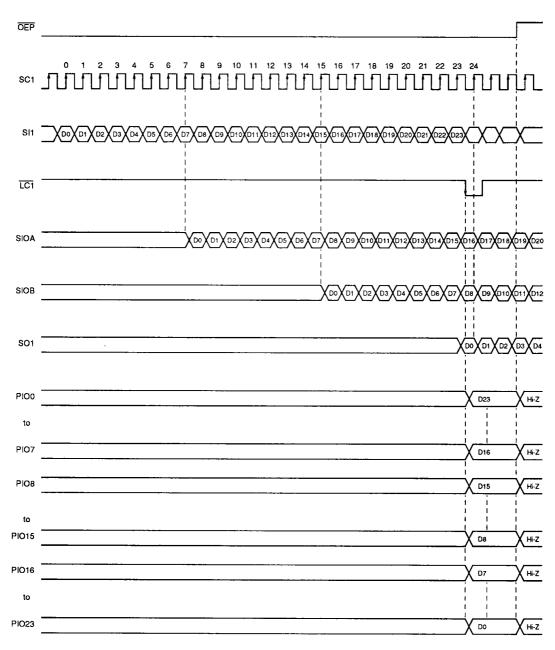

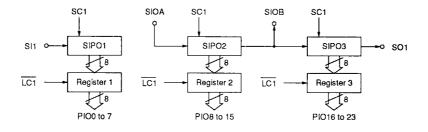

Figure 16. 24-bit SIPO ( $\overline{OEAC}$  = LOW,  $\overline{OEBD}$  = LOW)

J

I

## FUNCTIONAL DESCRIPTION

# Serial-to-parallel Converter Mode (OEP = LOW)

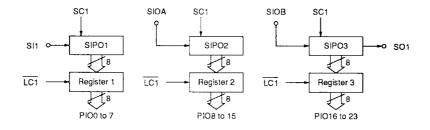

In this mode, the levels on OEAC and OEBD define a further four sub-modes. These sub-modes determine the configuration of three 8-bit shift registers making up the serial-to-parallel converter.

| Mode<br>name | OEAC | OEBD | Function                                                                                                                                       |

|--------------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| SPM1         | LOW  | LOW  | 1 $	imes$ (24-bit serial $ ightarrow$ 24-bit parallel)                                                                                         |

| SPM2         | LOW  | HIGH | $1 \times (16\text{-bit serial} \rightarrow 16\text{-bit parallel})$<br>AND $1 \times (8\text{-bit serial} \rightarrow 8\text{-bit parallel})$ |

| SPM3         | HIGH | LOW  | $1 \times (8$ -bit serial $\rightarrow 8$ -bit parallel)<br>AND $1 \times (16$ -bit serial $\rightarrow 16$ -bit<br>parallel)                  |

| SPM4         | HIGH | HIGH | $3 	imes$ (8-bit serial $\rightarrow$ 8-bit parallel)                                                                                          |

The mode selected determines which input(s) of SI1, SIOA and SIOB will function as a serial data input. Data is shifted on the rising edge of SC1.

The shift register (SIPO) output data from each SIPO is latched into general-purpose registers in 8-bit units on the falling edge of the data latch clock,  $\overline{LC1}$ .

Data is output on consecutive outputs from PIO0 up to PIO23, depending on the mode selected.

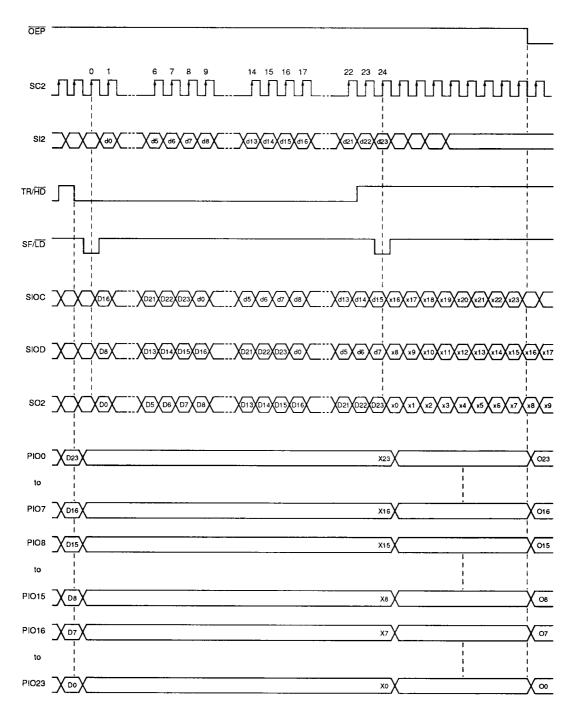

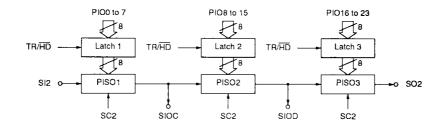

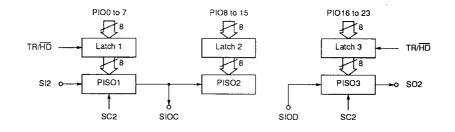

# Parallel-to-serial Converter Mode (OEP = HIGH)

In this mode, the levels on  $\overline{OEAC}$  and  $\overline{OEBD}$  define a further four sub-modes. These sub-modes determine the configuration of three 8-bit shift registers making up the parallel-to-serial converter.

| Mode<br>name | OEAC | OEBD | Function                                                                                                                     |

|--------------|------|------|------------------------------------------------------------------------------------------------------------------------------|

| PSM1         | LOW  | LOW  | $1 \times (24$ -bit parallel $\rightarrow 24$ -bit serial)<br>OR $3 \times (8$ -bit parallel $\rightarrow 8$ -bit<br>serial) |

| PSM2         | LOW  | HIGH | 2 $	imes$ (8-bit parallel $ ightarrow$ 8-bit serial)                                                                         |

| PSM3         | HIGH | LOW  | $1 \times 16$ -bit parallel $\rightarrow 16$ -bit serial)<br>OR 2 $\times$ (8-bit parallel $\rightarrow 8$ -bit<br>serial)   |

| PSM4         | HIGH | HIGH | $1 \times (8$ -bit parallel $\rightarrow 8$ -bit serial)                                                                     |

The parallel input data is input on consecutive inputs from PIO0 up to PIO23, depending on the mode selected.

Input parallel data is passed directly to the PISO shift registers when  $TR/\overline{HD}$  is HIGH (transparent mode). The input data is latched when  $TR/\overline{HD}$  goes LOW.

Data is loaded into the PISO registers when SF/LD goes LOW, and shifting is enabled when SF/LD goes HIGH. Data is shifted in three 8-bit units on the rising edge of the data shift clock, SC2.

The mode selected determines which output(s) of SO2, SIOC and SIOD will function as a serial output.

**Mode Selection**

Serial-to-parallel converter mode ( $\overline{OEP} = LOW$ )

SPM1 ( $\overline{OEAC}$  = LOW,  $\overline{OEBD}$  = LOW)

#### SPM2 ( $\overline{OEAC}$ = LOW, $\overline{OEBD}$ = HIGH)

#### SPM3 ( $\overline{OEAC}$ = HIGH, $\overline{OEBD}$ = LOW)

#### SPM4 ( $\overline{OEAC}$ = HIGH, $\overline{OEBD}$ = HIGH)

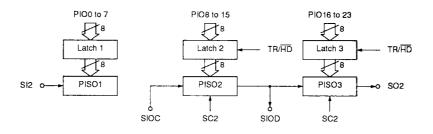

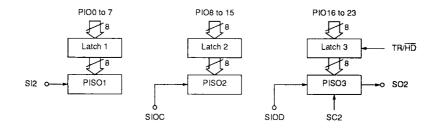

## Parallel-to-serial converter mode (OEP = HIGH)

#### **PSM1** ( $\overline{OEAC}$ = LOW, $\overline{OEBD}$ = LOW)

#### PSM2 ( $\overline{OEAC}$ = LOW, $\overline{OEBD}$ = HIGH)

PSM3 ( $\overline{OEAC}$  = HIGH,  $\overline{OEBD}$  = LOW)

#### PSM4 ( $\overline{OEAC}$ = HIGH, $\overline{OEBD}$ = HIGH)

## **Equivalent Circuits**

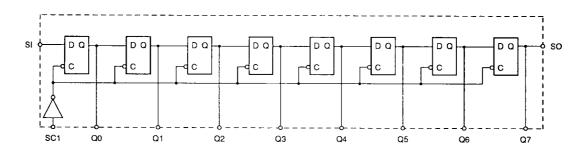

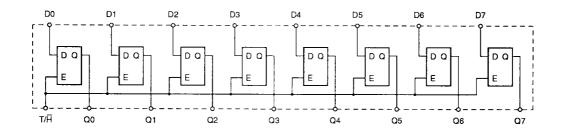

### 8-bit SIPO

## 8-bit register

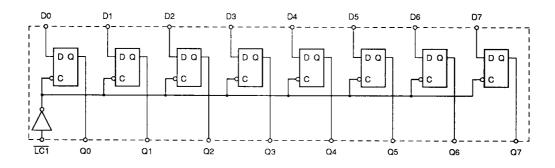

#### 8-bit latch

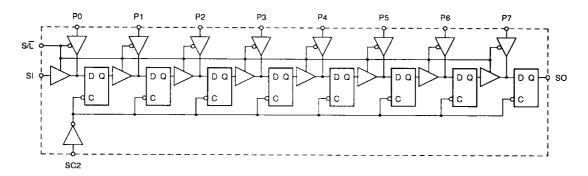

#### 8-bit PISO

NIPPON PRECISION CIRCUITS LTD. reserves the right to make changes to the products contained in this data sheet in order to improve the design or performance and to supply the best possible products. Nippon Precision Circuits Ltd. assumes no responsibility for the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision Circuits Ltd. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification.

NIPPON PRECISION CIRCUITS LTD.

3-9, Taihei 4-chome Sumida-ku, Tokyo 130, Japan Telephone: 03-5608-5571 Facsimile: 03-5608-5566

NC890/8E1993.10