#### **OVERVIEW**

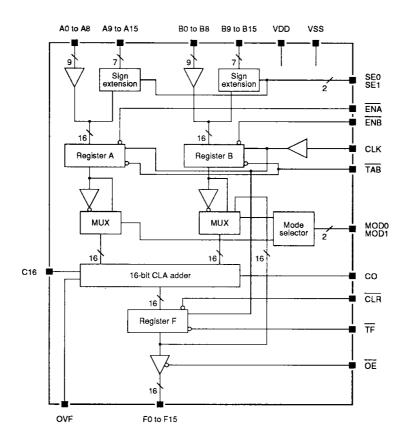

The SM5833AF is a 16-bit adder fabricated in Molybdenum-gate CMOS. It performs addition, subtraction and accumulation of 2s-complement data at a maximum operating speed of 25 MHz. It features input and output registers that can be programmed independently for transparent operation.

The SM5833AF can be employed as the input/output adder in a video-bandwidth digital filter, enabling two-dimensional filtering and other highspeed signal processing.

### **FEATURES**

- 16-bit 2s-complement input/output data

- Comprises

- 16-bit CLA adder

- 1  $\times$  16-bit parallel output register

- 2 × 16-bit parallel input registers

- 25 MHz maximum operating frequency (register mode only)

- Adder, subtractor and accumulator operating modes

- Overflow detected flag

- Input data sign bit extension

- Input/output register transparent operation

- Two SM5833AFs can be cascaded to form a 32-bit adder.

- TTL-compatible input/output levels

- Molybdenum-gate CMOS process

- Single 5 V supply

- 64-pin flat plastic package

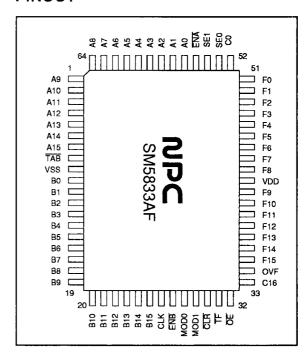

#### **PINOUT**

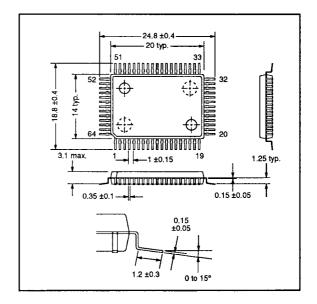

## PACKAGE DIMENSIONS

Unit: mm

# **BLOCK DIAGRAM**

# PIN DESCRIPTION

| Number | Name | 1/0 | Description                              |

|--------|------|-----|------------------------------------------|

| 1      | A9   | iρ  | Input A (bit 9)                          |

| 2      | A10  | ip  | Input A (bit 10)                         |

| 3      | A11  | ip  | Input A (bit 11)                         |

| . 4    | A12  | ip  | Input A (bit 12)                         |

| 5      | A13  | ip  | Input A (bit 13)                         |

| 6      | A14  | ip  | Input A (bit 14)                         |

| 7      | A15  | ip  | Input A (MSB)                            |

| 8      | TAB  | ip  | Register A and B transparent-mode select |

| 9      | VSS  |     | Ground                                   |

| 10     | BO   | ip  | Input B (LSB)                            |

| 11     | B1   | ip  | Input B (bit 1)                          |

| 12     | B2   | ip  | Input B (bit 2)                          |

| 13     | В3   | ip  | Input B (bit 3)                          |

| 14     | B4   | ip  | Input B (bit 4)                          |

| 15     | B5   | ip  | Input B (bit 5)                          |

| 16     | B6   | ip  | Input B (bit 6)                          |

## SM5833AF

| Number | Name | 1/0 | Description                             |

|--------|------|-----|-----------------------------------------|

| 17     | B7   | ip  | Input B (bit 7)                         |

| 18     | B8   | ip  | Input B (bit 8)                         |

| 19     | B9   | ip  | Input B (bit 9)                         |

| 20     | B10  | ip  | Input B (bit 10)                        |

| 21     | B11  | ip  | Input B (bit 11)                        |

| 22     | B12  | ip  | Input B (bit 12)                        |

| 23     | B13  | ip  | Input B (bit 13)                        |

| 24     | B14  | ip  | Input B (bit 14)                        |

| 25     | B15  | ip  | Input B (MSB)                           |

| 26     | CLK  | i   | Clock input (rising-edge trigger)       |

| 27     | ENB  | ip  | Register B enable                       |

| 28     | MOD0 | ip  | Made colors size                        |

| 29     | MOD1 | ip  | Mode select pins                        |

| 30     | CLR  | ip  | Output register clear                   |

| 31     | TF   | ip  | Output register transparent-mode select |

| 32     | ŌĒ   | ip  | Output enable                           |

| 33     | C16  | 0   | Carry output                            |

| 34     | OVF  | 0   | Overflow detected flag                  |

| 35     | F15  | 0   | Sum operation output (MSB)              |

| 36     | F14  | 0   | Sum operation output (bit 14)           |

| 37     | F13  | 0   | Sum operation output (bit 13)           |

| 38     | F12  | 0   | Sum operation output (bit 12)           |

| 39     | F11  | 0   | Sum operation output (bit 11)           |

| 40     | F10  | 0   | Sum operation output (bit 10)           |

| 41     | F9   | 0   | Sum operation output (bit 9)            |

| 42     | VDD  |     | Supply voltage                          |

| 43     | F8   | 0   | Sum operation output (bit 8)            |

| 44     | F7   | 0   | Sum operation output (bit 7)            |

| 45     | F6   | 0   | Sum operation output (bit 6)            |

| 46     | F5   | 0   | Sum operation output (bit 5)            |

| 47     | F4   | 0   | Sum operation output (bit 4)            |

| 48     | F3   | 0   | Sum operation output (bit 3)            |

| 49     | F2   | 0   | Sum operation output (bit 2)            |

| 50     | F1   | 0   | Sum operation output (bit 1)            |

| 51     | F0   | 0   | Sum operation output (LSB)              |

| 52     | CO   | i   | Carry input                             |

| 53     | SE0  | ip  |                                         |

| 54     | SE1  | ip  | Sign extension bit select pins          |

| Number | Name       | VO | Description       |

|--------|------------|----|-------------------|

| 55     | ENA        | ip | Register A enable |

| 56     | A0         | ip | Input A (LSB)     |

| 57     | A1         | ip | Input A (bit 1)   |

| 58     | A2         | ip | Input A (bit 2)   |

| 59     | A3         | ip | Input A (bit 3)   |

| 60     | A4         | ip | Input A (bit 4)   |

| 61     | <b>A</b> 5 | ip | Input A (bit 5)   |

| 62     | <b>A</b> 6 | ip | Input A (bit 6)   |

| 63     | <b>A</b> 7 | ip | Input A (bit 7)   |

| 64     | <b>A</b> 8 | ip | Input A (bit 8)   |

#### Note

i = input pin, ip = input pin with pull-up resistance, o = output pin

## **SPECIFICATIONS**

## **Absolute Maximum Ratings**

$V_{ss} = 0 V$

| Parameter                 | Symbol           | Rating                   | Unit   |

|---------------------------|------------------|--------------------------|--------|

| Supply voltage range      | V <sub>DD</sub>  | -3.0 to 7.0              | ٧      |

| Input voltage range       | V <sub>IN</sub>  | $-0.3$ to $V_{DD} + 0.3$ | ٧      |

| Power dissipation         | P <sub>D</sub>   | 250                      | mW     |

| Storage temperature range | T <sub>stg</sub> | -40 to 125               | deg. C |

| Soldering temperature     | Tsld             | 255                      | deg. C |

| Soldering time            | tsid             | 10                       | s      |

## **Recommended Operating Conditions**

$V_{ss} = 0 V$

| Parameter                   | Symbol          | Rating       | Unit   |

|-----------------------------|-----------------|--------------|--------|

| Supply voltage range        | V <sub>DD</sub> | 4.75 to 5.25 | ٧      |

| Operating temperature range | Торг            | -20 to 70    | deg. C |

## **DC Electrical Characteristics**

$V_{DD}$  = 4.75 to 5.25 V,  $T_a$  = -20 to 70 deg. C,  $V_{SS}$  = 0 V

| Parameter                | Symbol          | Condition                                           |     | Unit |      |      |

|--------------------------|-----------------|-----------------------------------------------------|-----|------|------|------|

|                          |                 |                                                     | min | typ  | max  | Oint |

| Standby supply current   | ls              | V <sub>IN</sub> = V <sub>DD</sub> or 0 V            | _   | 1.0  | 10.0 | μΑ   |

| Operating supply current | loo             | V <sub>DD</sub> = 5 V, f = 25 MHz, all outputs open | _   | 30   | 60   | mA.  |

| HIGH-level input voltage | V <sub>IH</sub> | 0 4 4 0                                             | 2.4 | -    | -    | ٧    |

| LOW-level input voltage  | V <sub>IL</sub> | See notes 1 and 2.                                  | _   | -    | 0.5  | ٧    |

| Parameter                                                     | Symbol          | Condition                                                 |     | Rating |     |      |

|---------------------------------------------------------------|-----------------|-----------------------------------------------------------|-----|--------|-----|------|

|                                                               | Symbol          | Condition                                                 | min | typ    | max | Unit |

| F0 to F15, C16 and OVF<br>HIGH-level output voltage           | V <sub>OH</sub> | I <sub>OH</sub> = -0.1 mA.<br>See note 3.                 | 2.5 | -      | -   | ٧    |

| F0 to F15, C16 and OVF<br>LOW-level output voltage            | V <sub>OL</sub> | loL = 4.0 mA.<br>See note 3.                              | -   | -      | 0.4 | ٧    |

| LOW-level input current                                       | I <sub>IL</sub> | V <sub>IN</sub> = 0 V. See note 2.                        | _   | 10     | 20  | μΑ   |

| HIGH-level input leakage current                              | Існ             | V <sub>IN</sub> = V <sub>DD</sub> .<br>See notes 1 and 2. |     | -      | 1.0 | μΑ   |

| LOW-level input leakage current                               | I <sub>LL</sub> | V <sub>IN</sub> = 0 V. See note 1.                        | -   |        | 1.0 | μΑ   |

| F0 to F15 high-impedance<br>HIGH-level output leakage current | lzн             | VOE = VIH, VOUT = VDD                                     | _   | _      | 5.0 | μΑ   |

| F0 to F15 high-impedance<br>LOW-level output leakage current  | lzL             | $V_{\overline{OE}} = V_{IH}, V_{OUT} = 0 V$               | _   | _      | 5.0 | μΑ   |

### Notes

- 1. Pins CLK and C0 are TTL-level inputs.

- 2. Pins A0 to A15, B0 to B15, MOD0, MOD1, SE0, SE1,  $\overline{\text{CLR}}$ ,  $\overline{\text{TAB}}$ ,  $\overline{\text{TF}}$ ,  $\overline{\text{ENA}}$ ,  $\overline{\text{ENB}}$  and  $\overline{\text{OE}}$  are TTL-level inputs with pull-up resistances.

- 3. Pins F0 to F15, C16 and OVF are TTL-level outputs.

## **AC Electrical Characteristics**

## Standard register mode

$V_{DD}$  = 4.75 to 5.25 V,  $T_a$  = -20 to 70 deg. C,  $V_{SS}$  = 0 V

| Parameter                                 | Symbol          | Condition                          | Rating |     |     | 11   |

|-------------------------------------------|-----------------|------------------------------------|--------|-----|-----|------|

| rarameter                                 |                 | Condition                          | min    | typ | max | Unit |

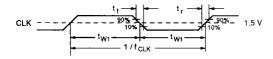

| Clock frequency                           | folk            | 50% duty, TAB = HIGH,<br>TF = HIGH | 0      | -   | 25  | MHz  |

| Clock pulsewidth                          | tw <sub>1</sub> | -                                  | .15    | -   | -   | ns   |

| Clock rise time                           | t <sub>r</sub>  | See figure 1.                      | _      | _   | 100 | ns   |

| Clock fall time                           | t <sub>i</sub>  |                                    | -      | _   | 100 | ns   |

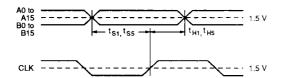

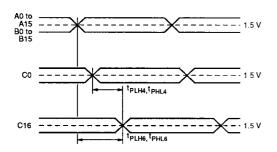

| A0 to A15 and B0 to B15 data setup time   | tsı             | TAB = HIGH.                        | 12     | _   | -   | ns   |

| A0 to A15 and B0 to B15 data<br>hold time | t <sub>H1</sub> | See figure 2.                      | 3      | -   | -   | ns   |

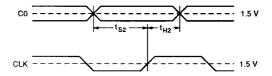

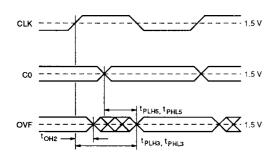

| C0 carry setup time                       | ts2             | TF = HIGH.                         | 22     | -   | -   | ns   |

| C0 carry hold time                        | t <sub>H2</sub> | See figure 3.                      | 0      | -   | _   | ns   |

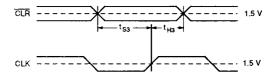

| CLR clear setup time                      | ts3             | TF = HIGH.                         | 15     | -   | _   | ns   |

| CLR clear hold time                       | t <sub>H3</sub> | See figure 4.                      | 15     | _   | -   | ns   |

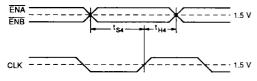

| ENA and ENB enable setup time             | ts4             | TAB = HIGH.                        | 15     | _   | _   | ns   |

| ENA and ENB enable hold time              | t <sub>H4</sub> | See figure 5.                      | 3      | _   | -   | ns   |

| MOD0 and MOD1 mode setup time             | tss             | TF = HIGH                          | 100    | _   | _   | ns   |

| MODO and MOD1 mode hold time              | t <sub>H5</sub> |                                    | 0      | _   | -   | ns   |

| Parameter                               | Symbol Condition  | Condition                                       |     | Rating |     | Unit |

|-----------------------------------------|-------------------|-------------------------------------------------|-----|--------|-----|------|

| r aranneter                             |                   | Condition                                       | min | typ    | max | Unit |

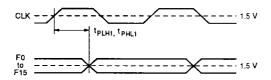

| OLK to E. data and add to the           | tPLH1             | TF = HIGH.                                      | -   | _      | 28  |      |

| CLK to Fn data output delay time        | t <sub>PHL1</sub> | See figure 6.<br>See note 1.                    |     | -      | 28  | ns   |

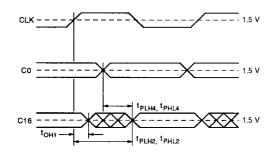

| CLK to C16 carry output                 | tPLH2             | TAB = HIGH.                                     | -   | -      | 50  |      |

| delay time                              | tPHL2             | See figure 7.                                   | _   | -      | 50  | ns   |

| CLK to C16 carry output hold time       | toH1              | See note 1.                                     | 15  | _      | -   | ns   |

| CLK to OVF overflow output              | <b>t</b> РLH3     |                                                 | _   | _      | 56  |      |

| delay time                              | ‡PHL3             | TAB = HIGH.<br>See figure 9.                    | _   | -      | 56  | ns   |

| CLK to OVF overflow output<br>hold time | <b>t</b> он2      | See note 1.                                     | 15  | -      | -   | ns   |

| C0 to C16 carry output delay time       | ¹PLH4             | See figure 7.                                   | _   | _      | 40  |      |

| to to the carry output delay time       | t <sub>PHL4</sub> | See note 1.                                     | _   | _      | 40  | ns   |

| C0 to OVF overflow output               | t <sub>PLH5</sub> | See figure 9.                                   | _   | -      | 40  |      |

| delay time                              | t <sub>PHL5</sub> | See note 1.                                     | _   | _      | 40  | ns   |

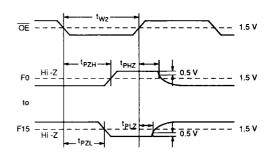

| F0 to F15 output enable                 | t <sub>PZL</sub>  | See figure 13.                                  | _   | -      | 35  |      |

| delay time                              | t <sub>PZH</sub>  | See note 2.                                     | _   | _      | 35  | ns   |

| F0 to F15 output disable                | †PLZ              | See figure 13.                                  | -   | _      | 35  |      |

| delay time                              | t <sub>PHZ</sub>  | See note 2.                                     | _   | -      | 35  | ns   |

| OE pulsewidth                           | t <sub>W2</sub>   | See figure 13.                                  | 20  | -      | -   | ns   |

| Input capacitance                       | C <sub>IN</sub>   | f = 1 MHz                                       | -   | -      | 10  | pF   |

| Output capacitance                      | Cout              | $f = 1 \text{ MHz}, V_{\overline{OE}} = V_{IH}$ |     | -      | 20  | pF   |

## Notes

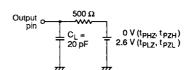

- 1. Measurement circuit 1

- 2. Measurement circuit 2

- 3. Typical values are measured at  $V_{DD}$  = 5 V and  $T_a$  = 25 deg. C.

## Transparent register mode

TAB = LOW, TF = HIGH

$V_{\text{DD}}$  = 4.75 to 5.25 V,  $T_{\text{a}}$  = -20 to 70 deg. C,  $V_{\text{SS}}$  = 0 V

| Parameter                                 | Symbol Co         | Condition     | Rating |     |     | Unit |

|-------------------------------------------|-------------------|---------------|--------|-----|-----|------|

|                                           |                   | Condition     | min    | typ | max | Onic |

| A0 to A15 and B0 to B15 data setup time   | tss               | Saa farra 2   | 42     | -   | -   | ns   |

| A0 to A15 and B0 to B15 data<br>hold time | t <sub>H5</sub>   | See figure 2. | 0      | -   | -   | ns   |

| CIV to F. data sutanti dalam tima         | t <sub>PLH1</sub> | See figure 6. | -      | -   | 28  |      |

| CLK to Fn data output delay time          | <sup>†</sup> PHL1 | See note 1.   | -      | _   | 28  | ns   |

| CO to C16 some autout dolor time          | t <sub>PLH4</sub> | See figure 8. | -      | -   | 40  |      |

| C0 to C16 carry output delay time         | t <sub>PHL4</sub> | See note 1.   | -      | -   | 40  | ns   |

| Parameter                                 | Symbol            | Condition                     | Rating |     |     | 114  |

|-------------------------------------------|-------------------|-------------------------------|--------|-----|-----|------|

|                                           |                   | Condition                     | min    | typ | max | Unit |

| C0 to OVF overflow output                 | †PLH5             | See figure 10.                | _      | -   | 40  |      |

| delay time                                |                   | See note 1.                   | _      | -   | 40  | ns   |

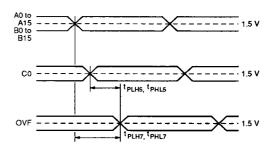

| A and B to C16 carry output               | tplH6             | See figure 8. See note 1.     | _      | -   | 57  |      |

| delay time                                | t <sub>PHL6</sub> |                               | -      | -   | 57  | ns   |

| A and B to OVF overflow output delay time | tPLH7             | See figure 10.<br>See note 1. | -      | -   | 63  |      |

|                                           | ¹PHL7             |                               | -      | _   | 63  | ns   |

### **Notes**

- 1. Measurement circuit 1

- 2. Measurement circuit 2

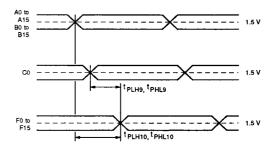

# $\overline{\mathsf{TAB}} = \mathsf{HIGH}, \ \overline{\mathsf{TF}} = \mathsf{LOW}$

$V_{DD}$  = 4.75 to 5.25 V,  $T_{\text{\tiny A}}$  = -20 to 70 deg. C,  $V_{SS}$  = 0 V

| Parameter                                 | Cumbal            | Condition                    |     | Rating |     | 11-14 |

|-------------------------------------------|-------------------|------------------------------|-----|--------|-----|-------|

| Parameter                                 | Symbol            | Condition                    | min | typ    | max | Unit  |

| A0 to A15 and B0 to B15 data setup time   | t <sub>S1</sub>   | Con Found 0                  | 12  | -      | -   |       |

| A0 to A15 and B0 to B15 data<br>hold time | t <sub>H1</sub>   | See figure 2.                | 3   | _      | _   | ns    |

| CLK to C16 carry output                   | tPLH2             |                              | -   | -      | 50  |       |

| delay time                                | tPHL2             | See figure 7.<br>See note 1. | -   | -      | 50  | ns    |

| CLK to C16 carry output hold time         | t <sub>OH1</sub>  |                              | 15  | -      | -   | ns    |

| CLK to OVF overflow output                | t <sub>PLH3</sub> | See figure 9. See note 1.    |     | -      | 56  | ns    |

| delay time                                | t <sub>PHL3</sub> |                              | _   | -      | 56  |       |

| CLK to OVF overflow output<br>hold time   | tон2              |                              | 15  | _      | _   | ns    |

| CO to C16 corru autout dalay time         | tPLH4             | See figure 7.                | -   | -      | 40  | - ns  |

| C0 to C16 carry output delay time         | t <sub>PHL4</sub> | See note 1.                  | _   | -      | 40  |       |

| C0 to OVF overflow output                 | tPLH5             | See figure 9.                | _   | -      | 40  | ns    |

| delay time                                | tPHL5             | See note 1.                  | -   | -      | 40  |       |

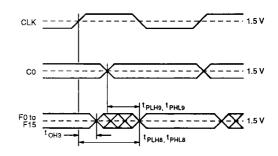

| CLK to Fn data output delay time          | t <sub>PLH8</sub> |                              | _   |        | 58  | ns    |

| OLK to Fit data dutpor delay time         | tPHL8             | See figure 11. See note 1.   | _   | -      | 58  |       |

| CLK to Fn data output hold time           | tонз              |                              | 15  | -      | _   | ns    |

| CO to Fn data output delay time           | t <sub>PLH9</sub> | See figure 11.               |     | _      | 48  | ns    |

| 50 to the data doublit detay time         | t <sub>PHL9</sub> | See note 1.                  | -   | -      | 48  |       |

### Notes

- 1. Measurement circuit 1

- 2. Measurement circuit 2

# TAB = LOW, TF = LOW

$V_{DD}$  = 4.75 to 5.25 V,  $T_a$  = -20 to 70 deg. C,  $V_{SS}$  = 0 V

| Parameter                                 | Symbol             | Condition                     | Rating |     |     | 11-14 |

|-------------------------------------------|--------------------|-------------------------------|--------|-----|-----|-------|

|                                           |                    |                               | min    | typ | max | Unit  |

| C0 to C16 carry output delay time         | t <sub>PLH4</sub>  | See figure 8.                 | -      | -   | 40  | ns    |

|                                           | ₹PHL4              | See note 1.                   | -      | _   | 40  |       |

| C0 to OVF overflow delay time             | tPLH5              | See figure 10.                | -      | -   | 40  | ns    |

|                                           | t <sub>PHL5</sub>  | See note 1.                   | -      | _   | 40  |       |

| A and B to C16 carry output               | tPLH6              | See figure 8.<br>See note 1.  | -      | -   | 57  | ns    |

| delay time                                | tPHL6              |                               | -      | -   | 57  |       |

| A and B to OVF overflow output delay time | t <sub>PLH7</sub>  | See figure 10.<br>See note 1. | -      | -   | 63  | ns    |

|                                           | tPHL7              |                               | -      | _   | 63  |       |

| C0 to Fn data output delay time           | tPLH9              | See figure 12.<br>See note 1. | -      | _   | 48  | ns    |

|                                           | t <sub>PHL9</sub>  |                               | _      | -   | 48  |       |

| A and B to Fn data output delay time      | t <sub>PLH10</sub> | See figure 12.<br>See note 1. | -      | _   | 60  | ns    |

|                                           | t <sub>PHL10</sub> |                               | -      | -   | 60  |       |

### Notes

- 1. Measurement circuit 1

- 2. Measurement circuit 2

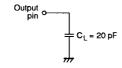

### **Measurement Circuits**

### Measurement circuit 1

## Measurement circuit 2

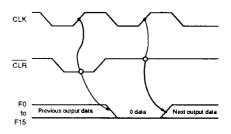

## **Timing Diagrams**

Figure 1. CLK input waveform

Figure 2. A and B data input timing

Figure 3. Carry input timing

Figure 4. Clear input timing

Figure 5. Enable input timing

Figure 6. Output data timing  $(\overline{TF} = HIGH)$

Figure 7. Carry output timing  $(\overline{TAB} = HIGH)$

Figure 8. Carry output timing  $(\overline{TAB} = LOW)$

Figure 9. Overflow output timing ( $\overline{TAB} = HIGH$ )

Figure 10. Overflow output timing ( $\overline{TAB} = LOW$ )

Figure 11. Output data timing ( $\overline{TAB} = HIGH$ ,  $\overline{TF} = LOW$ )

Figure 12. Output data timing ( $\overline{TAB} = LOW$ ),  $\overline{TF} = LOW$ )

Figure 13. Output enable control timing

### **FUNCTIONAL DESCRIPTION**

### Operating Mode Selection (MOD0, MOD1, C0)

MOD0 and MOD1 select the operating mode as shown in the following table. These pins have internal pull-up resistances, and adder mode is selected if they are left open.

The C0 input on the LSB end needs to be switched to correspond to the selected operating mode. C0 must be LOW for adder mode, and HIGH for subtraction mode.

| MOD0 | MOD1 | C0<br>(See note) | Operating mode        |

|------|------|------------------|-----------------------|

| HIGH | HIGH | LOW              | $A + B \rightarrow F$ |

| HIGH | LOW  | HIGH             | $A - B \rightarrow F$ |

| LOW  | HIGH | HIGH             | –A + B → F            |

| LOW  | LOW  | LOW              | A + F → F             |

#### Note

For cascade connections, this is the input level on C0 pin on the lowest device in the cascade (LSB end).

### Cascade Connection (C16, C0)

A 32-bit adder can be configured using two SM5833AFs by connecting the carry output C16 of the lower 16-bit adder to the carry input C0 of the upper 16-bit adder. Note that because the 32-bit adder operates as a ripple-carry adder, operating speed is reduced.

### Overflow Detect (OVF)

OVF goes HIGH when an arithmetic overflow is detected. It is driven directly from the CLA adder and is not latched. Note must be taken of the clock rate and OVF output delay when interfacing circuitry to this pin.

### Sign Extension (SE0, SE1)

Input data words shorter than 16 bits can be used by the SM5833AF by setting the SE0 and SE1 control pins as shown in the following table. Word lengths of 10, 12, 14 and 16 bits can be selected; the most-significant bit of the selected word length is sign-extended to 16 bits. Note that both inputs must have the same input word length.

SE0 and SE1 have internal pull-up resistances, so 16-bit input words are selected if they are left open.

| SE0  | SE1  |            | fore sign<br>nsion | Input data |  |

|------|------|------------|--------------------|------------|--|

|      |      | Input A    | Input B            | length     |  |

| LOW  | LOW  | <b>A</b> 9 | B9                 | 10 bits    |  |

| HIGH | LOW  | A11        | B11                | 12 bits    |  |

| LOW  | HIGH | A13        | B13                | 14 bits    |  |

| HIGH | HIGH | A15        | B15                | 16 bits    |  |

### **Register Control**

### Transparent mode (TAB, TF)

Input registers A and B and output register F support a transparent mode of operation. Note that after selecting transparent mode, the previous register contents are corrupted.

| TAB  | Input registers A and B |

|------|-------------------------|

| HIGH | Register mode           |

| LOW  | Transparent mode        |

| TF   | Input register F        |

| TF   | Input register F |

|------|------------------|

| HIGH | Register mode    |

| LOW  | Transparent mode |

## Input register enable control (ENA, ENB)

ENA and ENB function as the latch clock enables for input registers A and B, respectively. Neither register can be updated while it is in the disabled state; they maintain the previously-latched data. Accordingly, these control signals allow data input to both registers from a single bus.

| ENA  | Input register A |

|------|------------------|

| HIGH | Disable          |

| LOW  | Enable           |

| ENB  | Input register B |

|------|------------------|

| HIGH | Disable          |

| LOW  | Enable           |

## Tristate output enable control (OE)

OE controls the output tristate buffers. This allows inputs and outputs to be connected to a single data bus.

| ŌĒ   | Output operation |

|------|------------------|

| HIGH | High impedance   |

| LOW  | Output           |

## Output register clear (CLR)

Output register F is cleared by setting  $\overline{\text{CLR}}$  LOW. In accumulator mode, this function must be used to initialize the output register before starting an accumulation.

Figure 14. Clear operation timing

NIPPON PRECISION CIRCUITS LTD. reserves the right to make changes to the products contained in this data sheet in order to improve the design or performance and to supply the best possible products. Nippon Precision Circuits Ltd. assumes no responsibility for the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision Circuits Ltd. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification.

#### NIPPON PRECISION CIRCUITS LTD.

3-9, Taihei 4-chome Sumida-ku, Tokyo 130, Japan Telephone: 03-5608-5571 Facsimile: 03-5608-5566

NC8915AE 1993.11