# CLC400 Fast Settling, Wideband Low-Gain Monolithic Op Amp

## **General Description**

The CLC400 is a high-speed, fast-settling operational amplifier designed for low-gain applications. Constructed using a unique, proprietary design and an advanced complementary bipolar process, the CLC400 offers performance far beyond that normally offered by ordinary monolithic op amps. In addition, unlike many other high-speed op amps the CLC400 offers both high performance and stability without the need for compensation circuitry—even at a gain of +1.

The fast 12ns settling to 0.05% and its ability to drive capacitive loads makes the CLC400 an ideal flash A/D driver. The wide bandwidth of 200MHz and the very linear phase ensure unsurpassed signal fidelity. Systems employing digital to analog converters also benefit from the use of the CLC400—especially if linearity and drive levels are important to system performance.

The CLC400 provides a simple, high-performance solution for video distribution and line driving applications. The 50mA output current and guaranteed specifications for 100 ohm loads provide ample drive capability and assured performance.

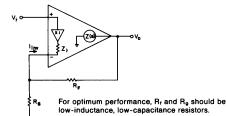

The CLC400 is based on National's proprietary op amp topology that uses current feedback instead of the usual voltage feedback. This unique design has many advantages over conventional designs (such as settling time that is relatively independent of gain), yet it is used in basically the same way (see the gain equations in Figures 1 and 2, page 4). However, an understanding of the topology will aid in achieving the best performance. The following discussion will proceed for the non-inverting gain configuration with the inverting mode analysis being very similar.

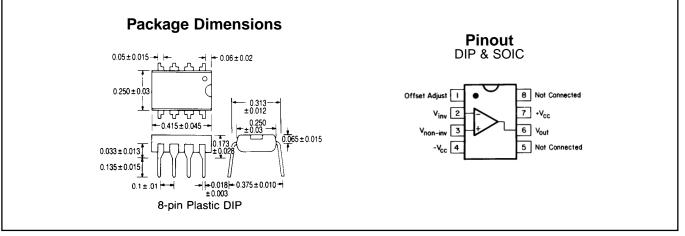

The CLC400 is available in several versions to meet a variety of requirements. A three-letter suffix determines the version:

| CLC400AJP | -40°C to +85°C  | 8-pin plastic DIP      |

|-----------|-----------------|------------------------|

| CLC400AJE | -40°C to +85°C  | 8-pin plastic SOIC     |

| CLC400AIB | -40°C to +85°C  | 8-pin hermetic CERDIP  |

| CLC400A8B | -55°C to +125°C | 8-pin hermetic CERDIP, |

|           |                 | MIL-STD-833, Level B   |

DESC SMD number: 5962-89970

### Features

- -3dB bandwidth of 200MHz

- 0.05% settling in 12ns

- Low power, 150mW

- Low distortion, -60dBc at 20MHz

- Stable without compensation

- Overload and short circuit protected

- ±1 to ±8 closed-loop gain range

### **Applications**

- Flash, precision A/D conversion

- Video distribution

- Line drivers

- D/A current-to-voltage conversion

- Photodiode, CCD preamps

- IF processors

- High-speed communications

June 1999

© 1999 National Semiconductor Corporation Printed in the U.S.A.

| CLC400 Electrical                                                                                                                                                                                                                                                 | Characteristics                                                                           | <b>6</b> (A <sub>V</sub> = +2,                      | V <sub>cc</sub> = ±5V, F                                                                  | R <sub>L</sub> = 100Ω,                          | , R <sub>f</sub> = <b>250</b> Ω;                                                          | unless spec                                                 | ified)                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------|

| PARAMETERS                                                                                                                                                                                                                                                        | CONDITIONS                                                                                | TYP                                                 | MAX 8                                                                                     | MIN RA                                          | TINGS                                                                                     | UNITS                                                       | SYMBOL                                                           |

| Ambient Temperature                                                                                                                                                                                                                                               | CLC400AJ                                                                                  | +25°C                                               | -40°C                                                                                     | +25°C                                           | +85°C                                                                                     |                                                             |                                                                  |

| FREQUENCY DOMAIN RESP<br>- 3dB bandwidth                                                                                                                                                                                                                          |                                                                                           | 200<br>50                                           | 150<br>35                                                                                 | 150<br>35                                       | 120<br>35                                                                                 | MHz<br>MHz                                                  | SSBW<br>LSBW                                                     |

| gain flatness<br>peaking<br>peaking<br>rolloff<br>linear phase deviation                                                                                                                                                                                          | V <sub>out</sub> <0.5 <sub>pp</sub><br><40MHz<br>>40MHz<br><75MHz<br>to 75MHz             | 0<br>0<br>0.6<br>0.2                                | 0.4<br>0.7<br>1.0<br>1.0                                                                  | 0.3<br>0.5<br>1.0<br>1.0                        | 0.4<br>0.7<br>1.3<br>1.2                                                                  | dB<br>dB<br>dB<br>°                                         | GFPL<br>GFPH<br>GFR<br>LPD                                       |

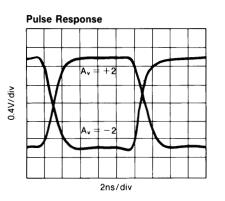

| TIME DOMAIN RESPONSE<br>rise and fall time<br>settling time to $\pm 0.1\%$<br>$\pm 0.05\%$<br>overshoot<br>slew rate $A_v = +2$<br>$A_v = -2$                                                                                                                     | 0.5V step<br>5V step<br>2V step<br>2V step<br>0.5V step                                   | 1.6<br>6.5<br>10<br>12<br>0<br>700<br>1600          | 2.4<br>10<br>13<br>15<br>15<br>430<br>—                                                   | 2.4<br>10<br>13<br>15<br>10<br>430<br>—         | 2.4<br>10<br>13<br>15<br>10<br>430<br>—                                                   | ns<br>ns<br>ns<br>%<br>V/μs<br>V/μs                         | TRS<br>TRL<br>TSP<br>TS<br>OS<br>SR<br>SR1                       |

| DISTORTION AND NOISE RE<br>2nd harmonic distortion<br>3rd harmonic distortion<br>equivalent input noise<br>noise floor<br>integrated noise                                                                                                                        | SPONSE<br>2V <sub>pp</sub> , 20MHz<br>2V <sub>pp</sub> , 20MHz<br>>1MHz<br>1MHz to 200MHz | -60<br>-60<br>-157<br>40                            | -40<br>-50<br>-154<br>57                                                                  | -45<br>-50<br>-154<br>57                        | -45<br>-50<br>-153<br>63                                                                  | dBc<br>dBc<br>dBm(1Hz)<br>μV                                | HD2<br>HD3<br>SNF<br>INV                                         |

| STATIC, DC PERFORMANCE<br>*input offset voltage<br>average temperature coefficient<br>*input bias current<br>average temperature coefficient<br>average temperature coefficient<br>power supply rejection ratio<br>common mode rejection ratio<br>*supply current | non-inverting<br>nt<br>inverting                                                          | 2<br>20<br>10<br>100<br>50<br>50<br>50<br>15        | $\pm 8.2$<br>$\pm 40$<br>$\pm 36$<br>$\pm 200$<br>$\pm 36$<br>$\pm 200$<br>45<br>45<br>23 | ±5.0<br>±20<br>±20<br>±20<br><br>45<br>45<br>23 | $\pm 9.0$<br>$\pm 40$<br>$\pm 20$<br>$\pm 100$<br>$\pm 30$<br>$\pm 100$<br>45<br>45<br>23 | mV<br>μV/°C<br>μA<br>nA/°C<br>μA<br>nA/°C<br>dB<br>dB<br>mA | VIO<br>DVIO<br>IBN<br>DIBN<br>IBI<br>DIBI<br>PSRR<br>CMRR<br>ICC |

| MISCELLANEOUS PERFORM<br>non-inverting input<br>output impedance<br>output voltage range<br>common mode input range<br>output current                                                                                                                             | IANCE<br>resistance<br>capacitance<br>at DC<br>no load<br>for rated performance           | $200 \\ 0.5 \\ 0.1 \\ \pm 3.5 \\ \pm 2.1 \\ \pm 60$ | >50<br><2.0<br><0.2<br>>3.0<br>>1.2<br>>35                                                | >100<br><2.0<br><0.2<br>>3.2<br>>2.0<br>>50     | >100<br><2.0<br><0.2<br>>3.2<br>>2.0<br>>50                                               | kΩ<br>pF<br>Ω<br>V<br>V<br>mA                               | RIN<br>CIN<br>RO<br>VO<br>CMIR<br>IO                             |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

±7V

60mA

$^{\pm V_{cc}}_{10V}$

+ 150°C

10 sec

500V

24

- 40°C to + 85°C

- 65°C to + 150°C

# **Absolute Maximum Ratings**

output is short circuit protected to

common mode input voltage differential input voltage junction temperature

operating temperature range

storage temperature range

lead solder duration (+ 300°C)

EDS rating (human body model)

ground, but maximum reliability will be maintained if l<sub>out</sub> does not exceed...

**Reliability Information**

# **Miscellaneous Ratings**

recommended gain range

±1 to ±8

NOTES: \* AJ

100% tested at + 25°C, sample at + 85°C.

| Package Thermal Resistance |                 |               |  |  |  |

|----------------------------|-----------------|---------------|--|--|--|

| Package                    | θ <sub>JC</sub> | $\theta_{JA}$ |  |  |  |

| AJP                        | 70°C/W          | 125°C/W       |  |  |  |

| AJE                        | 65°C/W          | 145°C/W       |  |  |  |

| AIB                        | 35°C/W          | 145°C/W       |  |  |  |

| A8B                        | 35°C/W          | 145°C/W       |  |  |  |

| http://www.national.com |  |

|-------------------------|--|

Transistor count

AJ:

$V_{cc}$

lout

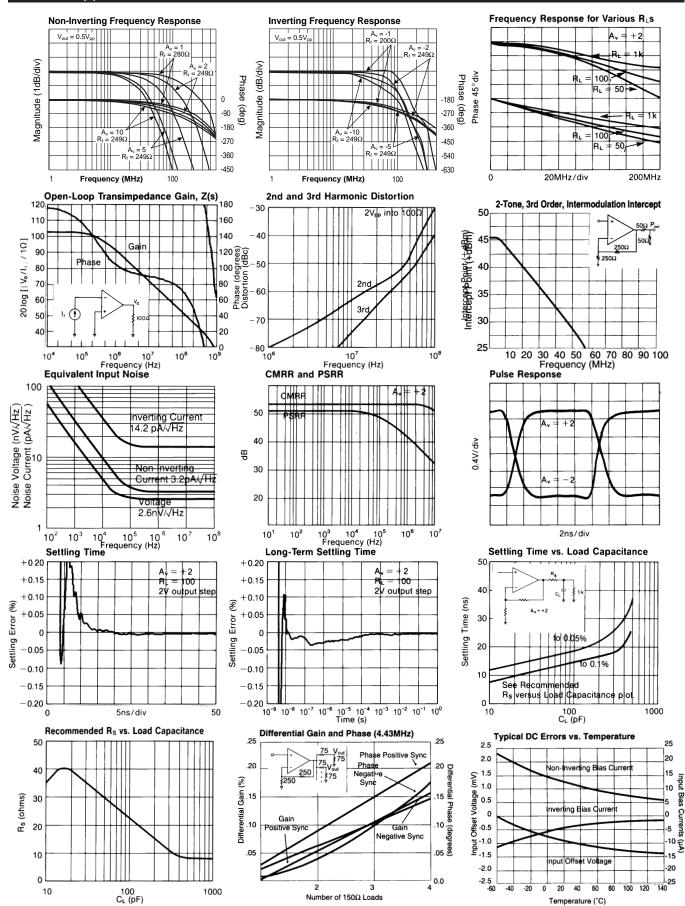

# CLC400 Typical Performance Characteristics ( $T_A = 25^\circ$ , $A_v = +2$ , $V_{CC} = \pm 5V$ , $R_L = 100\Omega$ ; unless specified)

http://www.national.com

#### Understanding the Loop Gain

Referring to the equivalent circuit of Figure 3, any current flowing in the inverting input is amplified to a voltage at the output through the transimpedance gain shown on the plots on page 3. This Z(s) is analogous to the open-loop gain of a voltage feedback amplifier.

Figure 3: current feedback topology

Developing the non-inverting frequency response for the topology of Figure 3 yields:

$$\frac{V_{o}}{V_{i}} = \frac{1 + R_{f}/R_{g}}{1 - 1/LG}$$

Eq. (1)

where LG is the loop gain defined by,

$$LG = \frac{Z(s)}{R_{1}} \times \frac{1}{1 + Z_{1}/(R_{1} | | R_{0})}$$

Eq. (2)

Equation 1 has a form identical to that for a voltage feedback amplifier with the differences occurring in the LG expression, Equation 2. For an idealized treatment, set  $Z_i = 0$  which results in a very simple LG =  $Z(s)/R_f$  (Derivation of the transfer function for the case where  $Z_i = 0$  is given in Application Note AN300-1). Using the Z(s) (open-loop transimpedance gain) plot shown on the previous page and dividing by the recommended  $R_f = 250\Omega$ , yields a large loop gain at DC. As a result, Equation 1 shows that the closed-loop gain at DC is very close to  $(1 + R_f/R_o)$ .

At higher frequencies, the roll-off of Z(s) determines the closed-loop frequency response which, ideally, is dependent only on R<sub>t</sub>. The specifications reported on the previous pages are therefore valid only for the specified R<sub>t</sub> = 250 Ω. Increasing R<sub>t</sub> from 250 Ω will decrease the loop gain and bandwidth, while decreasing it will increase the loop gain possibly leading to inadequate phase margin and closed-loop peaking. Conversely, fixing R<sub>t</sub> will hold the frequency response constant while the closed-loop gain can be adjusted using R<sub>t</sub>.

The CLC400 departs from this idealized analysis to the extent that the inverting input impedance is finite. With the low quiescent power of the CLC400,  $Z_i = 50\Omega$  leading to a drop in loop gain and bandwidth at high gain settings, as given by Equation 2. The second term in Equation 2 accounts for the division in feedback current that occurs between  $Z_i$  and  $R_i || R_g$  at the inverting node of the CLC400. This decrease in bandwidth at High Gains."

#### **DC Accuracy and Noise**

Since the two inputs for the CLC400 are quite dissimilar, the noise and offset error performance differs somewhat from that of a standard differential input amplifier. Specifically, the inverting input current noise is much larger than the non-inverting current noise. Also the two input bias currents are physically unrelated rendering bias current cancellation through matching of the inverting and non-inverting pin resistors ineffective.

In Equation 3, the output offset is the algebraic sum of the equivalent input voltage and current sources that influence DC operation. Output noise is determined similarly except that a root-sum-of-squares replaces the algebraic sum.  $R_{\rm s}$  is the non-inverting pin resistance.

Output Offset

$$V_o = \pm IBN \times R_s (1 + R_t/R_g) \pm VIO (1 + R_t/R_g) \pm IBI \times R_t$$

Eq. (3)

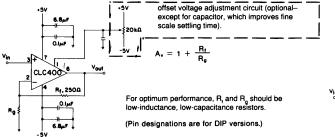

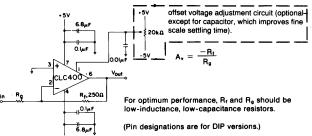

Figure 2: recommended inverting gain circuit

An important observation is that for fixed R<sub>f</sub>, offsets as referred to the input improve as the gain is increased (divide all terms by  $1 + R_f/R_g$ ). A similar result is obtained for noise where noise figure improves as gain increases.

### Selecting Between the CLC400 or CLC401

The CLC400 is intended for gains of  $\pm 1$  to  $\pm 8$  while the CLC401 is designed for gains of  $\pm 7$  to  $\pm 50$ . Optimum performance is achieved with a feedback resistor of  $250\Omega$  with the CLC400 and  $1.5k\Omega$  with the CLC401—this distinction may be important in transimpedance applications such as D/A buffering. Although the CLC400 can be used at higher gains, the CLC401 will provide a wider bandwidth because loop gain losses due to finite  $Z_i$  are lower with the larger CLC401 feedback resistor as explained above. On the other hand, the lower recommended feedback resistance of the CLC400 minimizes the output errors due to inverting input noise and bias currents.

#### **Increasing Bandwidth At High Gains**

Bandwidth may be increased at high closed-loop gains by adjusting R<sub>f</sub> and R<sub>g</sub> to make up for the losses in loop gain that occur at these high gain settings due to current division at the inverting input. An approximate relationship may be obtained by holding the LG expression constant as the gain is changed from the design point used in the specifications (that is, R<sub>f</sub> = 250 $\Omega$  and R<sub>g</sub> = 250 $\Omega$ ). For the CLC400 this gives,

$$R_f = 350 - 50A_v$$

and  $R_g = \frac{350 - 50A_v}{A_v - 1}$  Eq. (4)

where  $A_{\nu}$  is the non-inverting gain. Note that with  $A_{\nu}=+2$  we get the specified  $R_{f}=250\Omega,$  while at higher gains, a lower value gives stable performance with improved bandwidth.

#### **Capacitive Feedback**

Capacitive feedback should not be used with the CLC400 because of the potential for loop instability. See Application Note OA-7 for active filter realizations with the CLC400.

#### **Offset Adjustment Pin**

Pin 1 can be connected to a potentiometer as shown in Figure 1 and used to adjust the input offset of the CLC400. Full range adjustment of  $\pm 5V$  on pin 1 will yield a  $\pm 10$ mV input offset adjustment range. Pin 1 should always be bypassed to ground with a ceramic capacitor located close to the package for best settling performance.

#### **Printed Circuit Layout**

As with any high frequency device, a good PCB layout will enhance performance. Ground plane construction and good power supply bypassing close to the package are critical to achieving full performance. In the non-inverting configuration, the amplifier is sensitive to stray capacitance to ground at the inverting input. Hence, the inverting node connections should be small with minimal coupling to the ground plane. Shunt capacitance across the feedback resistor should not be used to compensate for this effect.

Parasitic or load capacitance directly on the output will introduce additional phase shift in the loop degrading the loop phase margin and leading to frequency response peaking. A small series resistor before the capacitance effectively decouples this effect. The graphs on the preceding page illustrate the required resistor value and resulting performance vs. capacitance.

Precision buffed resistors (PRP8351 series from Precision Resistive Products) with low parasitic reactances were used to develop the data sheet specifications. Precision carbon composition resistors will also yield excellent results. Standard spirally-trimmed RN55D metal film resistors will work with a slight decrease in bandwidth due to their reactive nature at high frequencies.

Evaluation PC boards (part no. 730013 for through-hole and 730027 for SOIC) for the CLC400 are available.

This page intentionally left blank.

#### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 2501 Miramar Tower 1-23 Kimberley Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.