# CLC405 Low-Cost, Low-Power, 110MHz Op Amp with Disable

### **General Description**

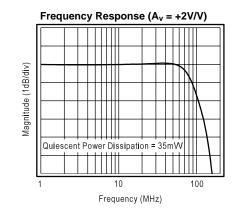

The CLC405 is a low-cost, wideband (110MHz) op amp featuring a TTL-compatible disable which quickly switches off in 18ns and back on in 40ns. While disabled, the CLC405 has a very high input/output impedance and its total power consumption drops to a mere 8mW. When enabled, the CLC405 consumes only 35mW and can source or sink an output current of 60mA. These features make the CLC405 a versatile, high-speed solution for demanding applications that are sensitive to both power and cost.

Utilizing National's proven architectures, this current feedback amplifier surpasses the performance of alternative solutions and sets new standards for low power at a low price. This power-conserving op amp achieves low distortion with -72dBc and -70dBc for second and third harmonics respectively. Many high source impedance applications will benefit from the CLC405's  $6M\Omega$  input impedance. And finally, designers will have a bipolar part with an exceptionally low 100nA non-inverting bias current.

With 0.1dB flatness to 50MHz and low differential gain and phase errors, the CLC405 is an ideal part for professional video processing and distribution. However, the 110MHz -3dB bandwidth (A $_{\rm V}$  = +2) coupled with a 350V/ $\mu$ s slew rate also make the CLC405 a perfect choice in cost-sensitive applications such as video monitors, fax machines, copiers, and CATV systems.

#### **Features**

- Low-cost

- Very low input bias current: 100nA

- High input impedance: 6MΩ

- 110MHz -3dB bandwidth  $(A_v = +2)$

- Low power: I<sub>cc</sub> = 3.5mA

- Ultra-fast enable/disable times

- High output current: 60mA

### **Applications**

- Desktop video systems

- Multiplexers

- Video distribution

- Flash A/D driver

- High-speed switch/driver

- High-source impedance applications

- Peak detector circuits

- Professional video processing

- High resolution monitors

#### CLC405 Electrical Characteristics (A<sub>V</sub> = +2, R<sub>f</sub> = $348\Omega$ : V<sub>cc</sub> = $\pm$ 5V, R<sub>L</sub> = $100\Omega$ unless specified) **PARAMETERS** CONDITIONS MIN/MAX RATINGS **UNITS NOTES TYP Ambient Temperature** CLC405AJ +25°C +25°C 0 to 70°C -40 to 85°C FREQUENCY DOMAIN RESPONSE $V_{out} < 1.0V_{pp}$ $V_{out} < 5.0V_{pp}$ $V_{out} < 0.5V_{pp}$ (R<sub>f</sub> = 2K) $V_{out} < 1.0V_{pp}$ -3dB bandwidth 110 75 50 45 MHz 42 31 27 26 MHz 1 -3dB bandwidth $A_V = +1$ 135 MHz ±0.1dB bandwidth 50 15 MHz $V_{out} < 1.0V_{pp}$ DC to 200MHz gain flatness peaking dB 0 0.6 0.8 1.0 rolloff <30MHz 0.05 0.3 0.4 0.5 dB linear phase deviation <20MHz 0.3 0.7 0.7 0.6 deg NTSC, R<sub>L</sub>=150 $\Omega$ NTSC, R<sub>L</sub>=150 $\Omega$ (Note 2) differential gain 0.01 0.03 0.04 0.05 % 0.01 2 % NTSC, $R_L$ =150 $\Omega$ NTSC, $R_L$ =150 $\Omega$ (Note 2) differential phase 0.25 0.4 0.5 0.55 deg deg 2 0.08 TIME DOMAIN RESPONSE rise and fall time 2V step 5 7.5 8.2 8.4 ns settling time to 0.05% 2V step 18 27 36 39 ns 3 12 12 overshoot 2V step 12 % 350 2V step 260 225 215 V/µs slew rate $A_V = +2$ $A_{V} = -1$ 1V step 650 V/µs **DISTORTION AND NOISE RESPONSE** $2V_{pp}$ , 1MHz/10MHz $2V_{pp}$ , 1MHz/10MHz -72/-52 -46 dBc 2<sup>nd</sup> harmonic distortion -45 -44 B 3<sup>rd</sup> harmonic distortion -70/-57 -50 -47 -46 dBc equivalent input noise non-inverting voltage >1MHz 5 6.3 6.6 6.7 nV/√Hz 12 >1MHz 15 17 pA/√Hz inverting current 16 >1MHz 4.2 pA/√Hz non-inverting current 3 3.8 4 STATIC DC PERFORMANCE 5 7 input offset voltage 8 mV Α 30 50 μV/°C average drift 50 900 1600 2800 input bias current non-inverting 100 nΑ Α nA/°C average drift 3 8 11 input bias current inverting 1 5 7 10 Α μΑ average drift 17 40 45 nA/°C power supply rejection ratio DC 45 47 46 dB 52 common-mode rejection ratio DC 50 45 44 43 dB supply current 35 40 41 44 Α $R_L = \infty$ mA disabled $R_L = \infty$ 8.0 0.9 0.95 1 mA Α **SWITCHING PERFORMANCE** 40 55 turn on time 58 58 ns to >50dB attn. @ 10MHz 18 26 32 turn off time 30 ns 55 10MHz 59 55 55 dВ off isolation high input voltage 2 2 2 $V_{IH}$ V $\mathsf{V}_{\mathsf{IL}}$ 0.8 8.0 0.8 ٧ low input voltage **MISCELLANEOUS PERFORMANCE** input resistance non-inverting 6 3 2.4 1 $M\Omega$ 182 input resistance inverting Ω 2 2 input capacitance non-inverting 1 2 pF 1.8 1.5 V common mode input range ±2.2 1.7 $R_L = 100\Omega$ + 3.5,-2.8 +3.1,-2.7 +2.9,-2.6 ٧ output voltage range +2.4,-1.6 output voltage range +4.0,-3.3 +3.9,-3.2 +3.8,-3.1 +3.7,-2.8 ٧ $R_L = \infty$

Recommended gain range ±1 to ±40V/V

output resistance, closed loop

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

40

0.06

## **Absolute Maximum Ratings**

supply voltage ±7V I<sub>out</sub> is short circuit protected to ground common-mode input voltage ±Vcc maximum junction temperature +150°C storage temperature range -65°C to +150°C lead temperature (soldering 10 sec) +300°C

Transitor count

40

0.2

68

mΑ

Ω

### **Notes**

20

0.4

1) At temps < 0°C, spec is guaranteed for  $R_L$  = 500 $\Omega$ .

38

0.25

- 2) An 825 $\Omega$  pull-down resistor is connected between  $V_o$  and - $V_{cc}$ .

- A) J-level: spec is 100% tested at +25°C

- B) Guaranteed at 10MHz.

2

output current

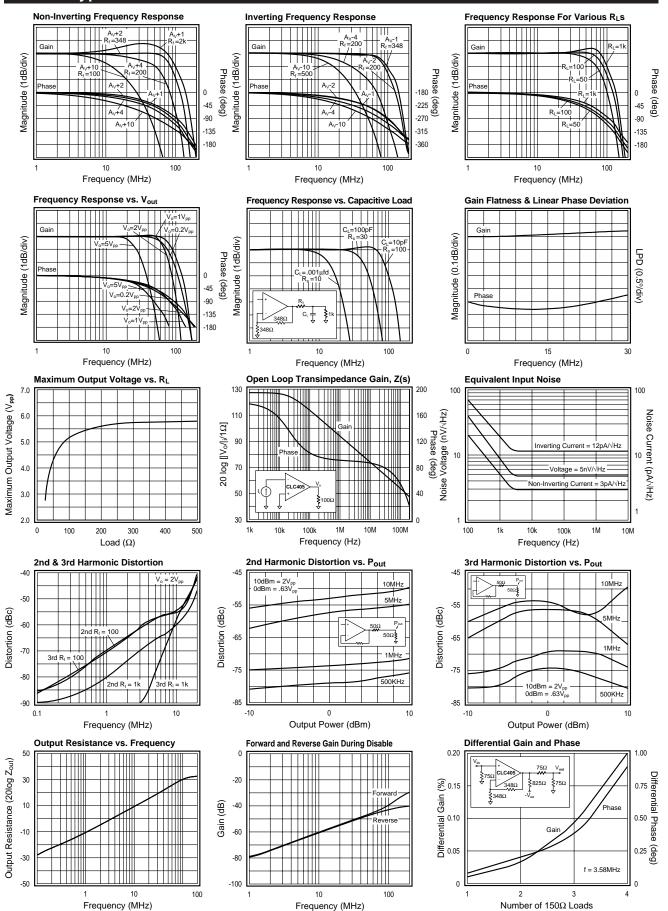

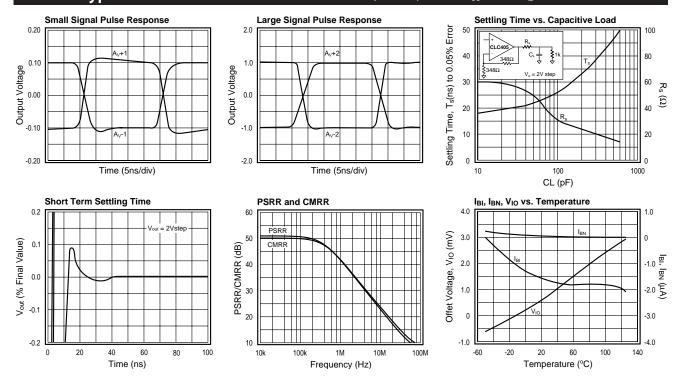

### CLC405 Typical Performance Characteristics (A<sub>V</sub> = +2, R<sub>f</sub> = 348 $\Omega$ : V<sub>cc</sub> = $\pm$ 5V, R<sub>L</sub> = 100 $\Omega$ unless specified)

#### CLC405 OPERATION

#### Feedback Resistor

The feedback resistor,  $R_{\rm f}$ , determines the loop gain and frequency response for a current feedback amplifier. Unless otherwise stated, the performance plots and data sheet specify CLC405 operation with  $R_{\rm f}$  of  $348\Omega$  at a gain of +2V/V. Optimize frequency response for different gains by changing  $R_{\rm f}$ . Decrease  $R_{\rm f}$  to peak frequency response and extend bandwidth. Increase  $R_{\rm f}$  to roll off of the frequency response and decrease bandwidth. Use a  $2k\Omega$   $R_{\rm f}$  for unity gain, voltage follower circuits.

Use application note OA-13 to optimize your  $R_f$  selection. The equations in this note are a good starting point for selecting  $R_f$ . The value for the inverting input impedance for OA-13 is approximately 182 $\Omega$ .

#### Enable/Disable Operation Using ±5V Supplies

The CLC405 has a TTL & CMOS logic compatible disable function. Apply a logic low (i.e. < 0.8V) to pin 8, and the CLC405 is guaranteed disabled across its temperature range. Apply a logic high to pin 8, (i.e. > 2.0V) and the CLC405 is guaranteed enabled. Voltage, not current, at pin 8 determines the enable/disable state of the CLC405.

Disable the CLC405 and its inputs and output become high impedances. While disabled, the CLC405's quiescent power drops to 8mW.

Use the CLC405's disable to create analog switches or multiplexers. Implement a single analog switch with one CLC405 positioned between an input and output. Create an analog multiplexer with several CLC405s. Tie the outputs together and put a different signal on each CLC405 input.

Operate the CLC405 without connecting pin 8. An internal  $20k\Omega$  pull-up resistor guarantees the CLC405 is enabled when pin 8 is floating.

#### Enable/Disable Operation for Single or Unbalanced Supply Operation

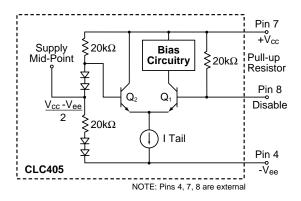

Figure 1

Figure 1 illustrates the internal enable/disable operation of the CLC405. When pin 8 is left floating or is tied to  $+V_{cc}$ , Q1 is on and pulls tail current through the CLC405 bias circuitry. When pin 8 is less than 0.8V above the supply midpoint, Q1 stops tail current from flowing in the CLC405 circuitry. The CLC405 is now disabled.

#### **Disable Limitations**

The feedback resistor,  $R_{\rm f}$ , limits off isolation in inverting gain configurations. Do not apply voltages greater than +V<sub>cc</sub> or less than -V<sub>ee</sub> to pin 8 or any other pin.

#### Input - Bias Current, Impedances, and Source **Termination Considerations**

The CLC405 has:

- $\bullet$  a 6M $\Omega$  non-inverting input impedance.

- a 100nA non-inverting input bias current.

If a large source impedance application is considered, remove all parasitic capacitance around the non-inverting input and source traces. Parasitic capacitances near the input and source act as a low-pass filter and reduce bandwidth.

Current feedback op amps have uncorrelated input bias currents. These uncorrelated bias currents prevent source impedance matching on each input from canceling offsets. Refer to application note OA-07 of the data book to find specific circuits to correct DC offsets.

#### **Layout Considerations**

Whenever questions about layout arise, USE THE EVALUATION BOARD AS A TEMPLATE.

Use the CLC730013 and CLC730027 evaluation boards for the DIP and SOIC respectively. These board layouts were optimized to produce the typical performance of the CLC405 shown in the data sheet. To reduce parasitic capacitances, the ground plane was removed near pins 2, 3, and 6. To reduce series inductance, trace lengths of components and nodes were minimized.

Parasitics on traces degrade performance. Minimize coupling from traces to both power and ground planes. Use low inductive resistors for leaded components.

Do not use dip sockets for the CLC405 DIP amplifiers. These sockets can peak the frequency domain response or create overshoot in the time domain response. Use flush-mount socket pins when socketing is necessary. The 730013 circuit board device holes are sized for Cambion P/N 450-2598 socket pins or their functional equivalent.

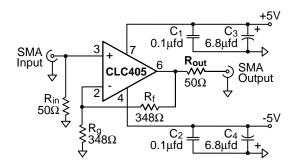

Insert the back matching resistor ( $R_{out}$ ) shown in Figure 2 when driving coaxial cable or a capacitive load. Use the plot in the typical performance section labeled "Settling Time vs. Capacitive Load" to determine the optimum resistor value for Rout for different capacitive loads. This optimal resistance improves settling tim for pulse-type applications and increases stability.

Figure 2

Use power-supply bypassing capacitors when operating this amplifier. Choose quality 0.1μF ceramics for C<sub>1</sub> and C2. Choose quality 6.8µF tantalum capacitors for  $C_3$  and  $C_4$ . Place the  $0.1\mu F$  capacitors within 0.1 inches from the power pins. Place the 6.8µF capacitors within 3/4 inches from the power pins.

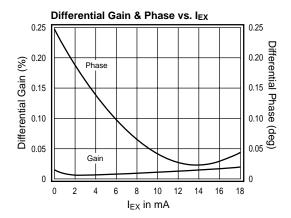

#### Video Performance vs. IEX

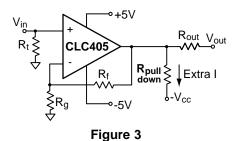

Improve the video performance of the CLC405 by drawing extra current from the amplifier output stage. Using a single external resistor as shown in Figure 3. you can adjust the differential phase. Video performance vs. IFX is illustrated below in Graph 1. This graph represents positive video performance with negative synchronization pulses.

#### Graph1

The value for  $R_{pd}$  in Figure 3 is determined by :

$$R_{pd} = \frac{5}{I_{ex}}$$

at ±5V supplies.

### Wideband Digital PGA

As shown on the front page, the CLC405 is easily configured as a digitally controlled programmable gain amplifier. Make a PGA by configuring several amplifiers at required gains. Keep  $R_{f}$  near  $348\Omega$  and change  $R_{\alpha}$ for each different gain. Use a TTL decoder that has enough outputs to control the selection of different gains and the buffer stage. Connect the buffer stage like the buffer of the front page. The buffer isolates each gain stage from the load and can produce a gain of zero for a gain selection of zero. Use of an inverter (7404) on the buffer disable pin to keep the buffer operational at all gains except zero. Or float the buffer disable pin for a continuous enable state.

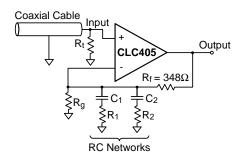

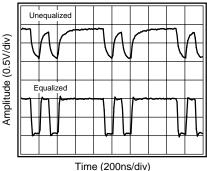

#### Amplitude Equalization

Sending signals over coaxial cable greater than 50 meters in length will attenuate high frequency signal components. Equalizers restore the attenuated components of this signal. The circuit in Figure 4, is an op amp equalizer. The RC networks peak the response of the CLC405 at higher frequencies. This peaking restores cable-attenuated frequencies. Graph 2 shows how the equalizer actually restored a digital word through 150 meters of coaxial cable.

Figure 4

#### **Digital Word Amplitude Equalization**

Graph 2

The values used to produce Graph 2 are:

$R_q = 348\Omega$   $C_1 = 470pF$   $C_2 = 70pF$

$R_1 = 450\Omega$   $R_2 = 90\Omega$

#### **Amplitude Equalizer**

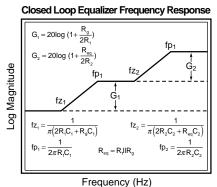

Place the first zero (fz<sub>1</sub>) at some low frequency (540 khz for Graph 2).  $R_1$  &  $C_1$  produce a pole (fp<sub>1</sub> @ 750khz) that cancels fz<sub>1</sub>. Place a second zero at a higher frequency (fz<sub>2</sub> @ 12Mhz).  $R_2$  &  $C_2$  provide a canceling pole (of fp<sub>2</sub> = 25Mhz).

Graph 3 shows the closed loop response of the op amp equalizer with equations for the poles, zeros, and gains.

Graph 3

Note: For very-high frequency equalization, use a higher bandwidth part (i.e. CLC44X)

| Package Thermal Resistance |        |        |  |

|----------------------------|--------|--------|--|

| Package                    | θjc    | θjΑ    |  |

| Plastic (AJP)              | 75°/W  | 125°/W |  |

| Surface Mount (AJE)        | 130°/W | 150°/W |  |

| CerDip                     | 65°/W  | 155°/W |  |

| Ordering Information                                    |                   |                           |  |

|---------------------------------------------------------|-------------------|---------------------------|--|

| Model                                                   | Temperature Range | Description               |  |

| CLC405AJP                                               | -40°C to +85°C    | 8-pin PDIP                |  |

| CLC405AJE                                               | -40°C to +85°C    | 8-pin SOIC                |  |

| CLC405AIB                                               | -40°C to +85°C    | 8-pin CerDIP              |  |

| CLC405ALC                                               | -40°C to +85°C    | dice                      |  |

| CLC405AMC                                               | -55°C to +125°C   | dice, MIL-STD-883         |  |

| CLC405A8B                                               | -55°C to +125°C   | 8-pin CerDIP, MIL-STD-883 |  |

| Contact factory for other packages and DESC SMD number. |                   |                           |  |

#### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### **Life Support Policy**

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### National Semiconductor Corporation

1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

#### National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

#### National Semiconductor Hong Kong Ltd.

2501 Miramar Tower 1-23 Kimberley Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600

Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309 Fax: 81-043-299-2408