# CLC412 Dual Wideband Video Op Amp

# **General Description**

The CLC412 combines a high-speed complementary bipolar process with National's current-feedback topology to produce a very high-speed dual op amp. The CLC412 provides a 250MHz small-signal bandwidth at a gain of +2V/V and a 1300V/ $\mu$ s slew rate while consuming only 50mW per amplifier from ±5V supplies.

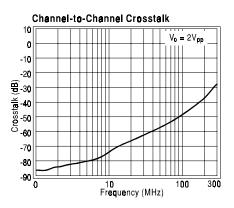

The CLC412 offers exceptional video performance with its 0.02% and 0.02° differential gain and phase errors for NTSC and PAL video signals while driving one back terminated  $75\Omega$  load. The CLC412 also offers a flat gain response of 0.1dB to 30MHz and very low channel-to-channel crosstalk of -76dB at 10MHz. Additionally, each amplifier can deliver a 70mA continuous output current. This level of performance makes the CLC412 an ideal dual op amp for high-density broadcast-quality video systems.

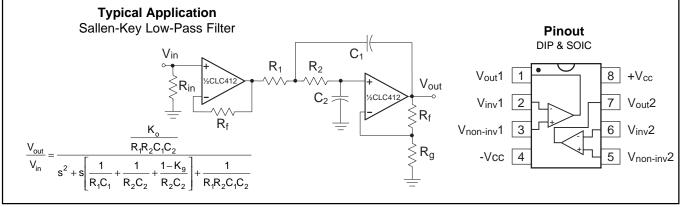

The CLC412's two very well-matched amplifiers support a number of applications such as differential line drivers and receivers. In addition, the CLC412 is well suited for Sallen Key active filters in applications such as anti-aliasing filters for high-speed A/D converters. Its small 8-pin SOIC package, low power requirement, low noise and distortion allow the CLC412 to serve portable RF applications such as IQ-channels.

The CLC412 is available in the following versions.

| CLC412AJP    | -40°C to +85°C  | 8-pin Plastic DIP    |

|--------------|-----------------|----------------------|

| CLC412AJE    | -40°C to +85°C  | 8-pin Plastic SOIC   |

| CLC412AIB    | -40°C to +85°C  | 8-pin CERDIP         |

| CLC412A8B    | -55°C to +125°C | 8-pin CERDIP,        |

|              |                 | MIL-STD-883, Level B |

| CLC412A8L-2A | -55°C to +125°C | 20-pin LCC,          |

|              |                 | MIL-STD-883, Level B |

| CLC412AMC    | -55°C to +125°C | dice,                |

|              |                 | MIL-STD-883, Level B |

DESC SMD number: 5962-94719

# Features

- Wide bandwidth:  $330 \text{MHz} (A_v = +1 \text{V/V})$

- 250MHz (A<sub>v</sub>=+2V/V)

- 0.1dB gain flatness to 30MHz

- Low power: 5mA/channel

- Very low diff. gain, phase: 0.02%, 0.02°

- -76dB channel-to-channel crosstalk (10MHz)

- Fast slew rate: 1300V/µs

- Unity-gain stable

## **Applications**

- HDTV, NTSC & PAL video systems

- Video switching and distribution

- IQ amplifiers

- Wideband active filters

- Cable drivers

- DC coupled single-to-differential conversions

© 1999 National Semiconductor Corporation Printed in the U.S.A.

#### http://www.national.com

June 1999

| CLC412 Electrical C                            |                                  |            |            |            |            | $R_{L} = 1009$     | -      |

|------------------------------------------------|----------------------------------|------------|------------|------------|------------|--------------------|--------|

| PARAMETERS                                     | CONDITIONS                       | TYP        | MIN/M      | AX RATIN   | GS         | UNITS              | SYMBOL |

| AmbientTemperature                             | CLC412AJ                         | +25°C      | -40°C      | +25°C      | +85°C      |                    |        |

| FREQUENCY DOMAIN RESPON                        | SE                               |            |            |            |            |                    |        |

| -3dB bandwidth                                 | $V_{out} < 0.5 V_{pp}$           | 250        | 150        | 175        | 135        | MHz                | SSBW   |

|                                                | $V_{out} < 4.0 V_{pp}$           | 105        | 80         | 80         | 65         | MHz                | LSBW   |

| gain flatness                                  | $V_{out} < 0.5 V_{pp}$           |            |            |            |            |                    |        |

| peaking                                        | DC to 30MHz                      | 0.1        | 0.1        | 0.1        | 0.2        | dB                 | GFP    |

| rolloff                                        | DC to 30MHz                      | 0.1        | 0.4        | 0.3        | 0.3        | dB                 | GFR    |

| linear phase deviation                         | DC to 75MHz                      | 0.5        | 1.3        | 1.0        | 1.0        | deg                | LPD    |

| differential gain                              | 4.43MHz, $R_{L}$ =150 $\Omega$   | 0.02       | 0.04       | 0.04       | 0.08       | %                  | DG     |

| differential phase                             | 4.43MHz, $R_L=150\Omega$         | 0.02       | 0.04       | 0.04       | 0.08       | deg                | DP     |

| TIME DOMAIN RESPONSE                           |                                  |            |            |            |            |                    |        |

| rise and fall time                             | 0.5V step                        | 1.4        | 2.3        | 2.0        | 2.6        | ns                 | TRS    |

|                                                | 4V step                          | 3.2        | 4.4        | 4.4        | 4.8        | ns                 | TRL    |

| settling time to 0.05%                         | 2V step                          | 12         | 18         | 18         | 20         | ns                 | TSS    |

| overshoot                                      | 0.5V step                        | 8          | 15         | 15         | 15         | %                  | OS     |

| slew rate                                      | 2V step                          | 1300       | 1000       | 1000       | 800        | V/μs               | SR     |

| DISTORTION AND NOISE RESPO                     | DNSE                             |            |            |            |            |                    |        |

| 2 <sup>nd</sup> harmonic distortion            | 2V <sub>pp</sub> , 20MHz         | - 46       | - 42       | - 42       | - 38       | dBc                | HD2    |

| 3 <sup>rd</sup> harmonic distortion            | 2V <sub>pp</sub> , 20MHz         | - 50       | - 46       | - 46       | - 42       | dBc                | HD3    |

| 3 <sup>rd</sup> order intermodulation intercep |                                  | 43         |            |            |            | dBm <sub>1Hz</sub> | IMD    |

| equivalent noise input                         |                                  |            |            |            |            |                    |        |

| non-inverting voltage                          | >1MHz                            | 3.0        | 3.4        | 3.4        | 3.8        | nV/√Hz             | VN     |

| inverting current                              | >1MHz                            | 12.0       | 13.9       | 13.9       | 15.5       | pA/√Hz             | NICN   |

| non-inverting current                          | >1MHz                            | 2.0        | 2.6        | 2.6        | 3.0        | pA/√Hz             | ICN    |

| noise floor                                    | >1MHz                            | - 157      | - 156      | - 156      | - 155      | dBm <sub>1Hz</sub> | SNF    |

| crosstalk input-referred                       | 10MHz                            | - 76       | - 70       | - 70       | - 70       | dB                 | XTLKA  |

| STATIC DC PERFORMANCE                          |                                  |            |            |            |            |                    |        |

| *input offset voltage                          |                                  | ±2         | ± 10       | ± 6        | ±12        | mV                 | VIO    |

| average drift                                  |                                  | ± 30       | ± 60       |            | ± 60       | μV/°C              | DVIO   |

| *input bias current                            | non-inverting                    | ±5         | ±28        | ± 12       | ±12        | μA                 | IBN    |

| average drift                                  | -                                | ± 30       | ± 187      |            | ±90        | nA/°C              | DIBN   |

| *input bias current                            | inverting                        | ± 3        | ± 34       | ± 15       | ± 20       | mA                 | IBI    |

| average drift                                  |                                  | ±20        | ± 125      |            | ± 80       | nA/°C              | DIBI   |

| power supply rejection ratio                   | DC                               | 50         | 46         | 46         | 44         | dB                 | PSRR   |

| common mode rejection ratio                    | DC                               | 50         | 45         | 45         | 43         | dB                 | CMRR   |

| *supply current                                | R <sub>L</sub> = ∞               | 10.2       | 13.6       | 12.8       | 12.8       | mA                 | ICC    |

| MISCELLANEOUS PERFORMAN                        | CE                               |            |            |            |            |                    |        |

| input resistance                               | non-inverting                    | 1000       | 300        | 500        | 500        | kΩ                 | RIN    |

| input capacitance                              | non-inverting                    | 1.0        | 2.0        | 2.0        | 2.0        | pF                 | CIN    |

| output resistance                              | closed loop                      | 0.04       | 0.6        | 0.3        | 0.2        | Ω                  | ROUT   |

| output voltage range                           | R <sub>L</sub> =∞                | + 3.8,-3.3 | + 3.6,-2.9 | + 3.7,-3.0 | + 3.7,-3.0 | V                  | VO     |

|                                                | $R_{L} = 100\Omega$              | + 3.1,-2.9 | + 2.0,-2.5 | ± 2.7      | ± 2.7      | V                  | VOL    |

|                                                | $R_{L} = 100\Omega$ (0° to 70°C) |            |            | + 2.5,-2.6 |            | V                  | VOLC   |

| input voltage range                            | common mode                      | ± 2.2      | ± 1.4      | ± 2.0      | ± 2.0      | V                  | CMIR   |

| output current                                 |                                  | 70         | 25         | 45         | 45         | mA                 | IO     |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

| Absolute Maximum                                                                                                                                                                       | Miscellaneous Ratings                                               |                                     |                  |                    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------|------------------|--------------------|--|--|

| V <sub>cc</sub>                                                                                                                                                                        | ±7V                                                                 | Recommended gain range ±1 to ±10V/V |                  |                    |  |  |

| l <sub>out</sub> short circuit protected to ground, however maximum re<br>is obtained if l <sub>out</sub> does not exceed<br>common-mode input voltage<br>maximum junction temperature | Notes:<br>* AJ :100% tested at +25°C.<br>Package Thermal Resistance |                                     |                  |                    |  |  |

| operating temperature range: AJ<br>storage temperature range                                                                                                                           | -40°C to +85°C<br>-65°C to +150°C                                   | Fackage memorial Resistance         |                  |                    |  |  |

| lead temperature (soldering 10 sec)                                                                                                                                                    | +300°C                                                              | Package                             | θ <sub>JC</sub>  | θ <sub>JA</sub>    |  |  |

| ESD (100V machine test)                                                                                                                                                                | 1000V                                                               | AJP<br>AJE                          | 70°C/W<br>65°C/W | 125°C/W<br>145°C/W |  |  |

| Reliability Information                                                                                                                                                                |                                                                     | A8B                                 | 40°C/W           | 130°C/W            |  |  |

| Transistor count                                                                                                                                                                       | 68                                                                  |                                     |                  |                    |  |  |

#### http://www.national.com

#### Application Introduction

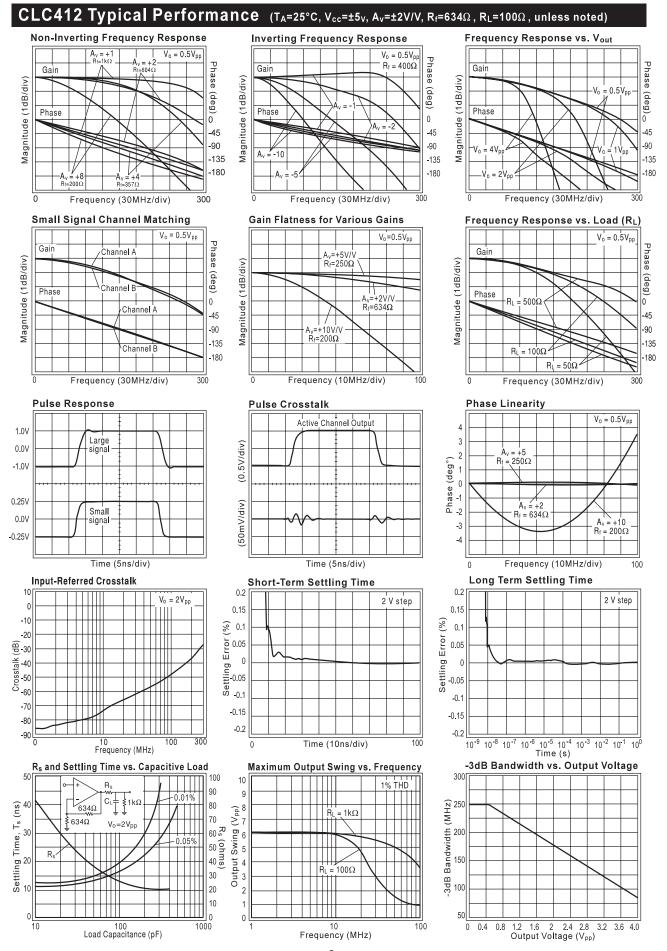

Offered in an 8-pin package for reduced space and cost, the wideband CLC412 dual current-feedback op amp provides closely matched DC & AC electrical performance characteristics making the part an ideal choice for wideband signal processing. Applications such as broadcast-quality video systems, IQ amplifiers, filter blocks, high-speed peak detectors, integrators and transimpedance amplifiers will all find superior performance in the CLC412 dual op amp.

#### **Feedback Resistor Selection**

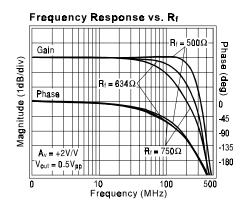

The loop gain and frequency response for a current-feedback operational amplifier is determined largely by the feedback resistor, R<sub>f</sub>. The Electrical Characteristics and Typical Performance plots specify an R<sub>f</sub> of  $634\Omega$ , a gain of +2V/V and operation with  $\pm 5V$  power supplies (unless otherwise stated). Generally, lowering R<sub>f</sub> from its recommended value will peak the frequency response and extend the bandwidth while increasing its value will roll off the response. Reducing the value of R<sub>f</sub> too far below its recommended value will cause overshoot, ringing and eventually oscillation.

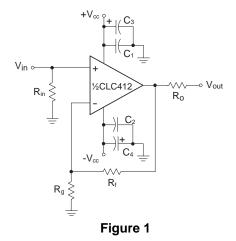

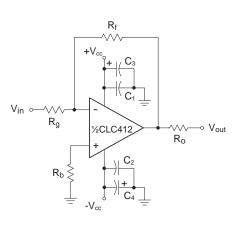

The plot above labeled "Frequency Response vs.  $R_f$ " shows the CLC412's frequency and phase response as  $R_f$  is varied while the gain remains constant at +2V/V ( $R_L$ =100 $\Omega$ ). This plot shows that one particular value of  $R_f$  will optimize the frequency and phase response at the specified gain setting, i.e. 634 $\Omega$  at a gain of +2V/V. Current-feedback op amps, unlike voltage-feedback op amps, have a direct relationship between their frequency

### Figure 2

and phase response to the value of the feedback resistor,  $R_f$ . For more information see Application Note OA-13 which describes the relationship between  $R_f$  and closed-loop frequency response.

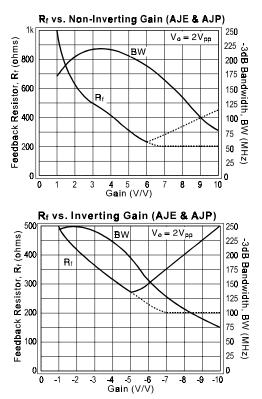

When configuring the CLC412 for other inverting or noninverting gains, it is necessary to adjust the value of the feedback resistor in order to optimize the device's frequency and phase response. The two plots below provide the means of selecting the recommended feedback-resistor value for both inverting and non-

inverting gain selections. Both plots show the value of R<sub>f</sub> approaching a non-zero minimum (dashed line) at high gains, which is characteristic of current-feedback op amps, while the linear portion of the two (solid) curves (i.e.  $-5>A_v>+6$ ) results from the limitation placed on R<sub>g</sub> (i.e. R<sub>g</sub>  $\geq 50\Omega$ ). This limitation is due to the desire to keep R<sub>g</sub> greater in value than that of the inverting input resistance. Therefore, the resulting small-signal

bandwidth curves, labeled "BW", correspond to the two (solid) "R<sub>f</sub>" curves. These results may deviate from that produced by the analysis of OA-13 since these plots were produced from an actual board layout that included parasitic capacitances not accounted for by the analysis of OA-13. It should be noted that a non-inverting gain of +1V/V requires an R<sub>f</sub> =1k $\Omega$  and the output voltage used for both plots is  $2V_{pp}$ .

In order to bandlimit the CLC412 at any particular gain setting, a larger value of  $R_f$  (than previously recommended in the plots above) is needed. Following the analysis in OA-13, we find the CLC412's "optimum feedback transimpedance",  $Z_t^*$ , below.

$$Z_t^* = R_f + R_{in} \left( 1 + \frac{R_f}{R_g} \right)$$

$$= 634 + 60 \left( 1 + \frac{634}{634} \right)$$

$$= 754\Omega$$

$$20LOG (754) = 57.5dB$$

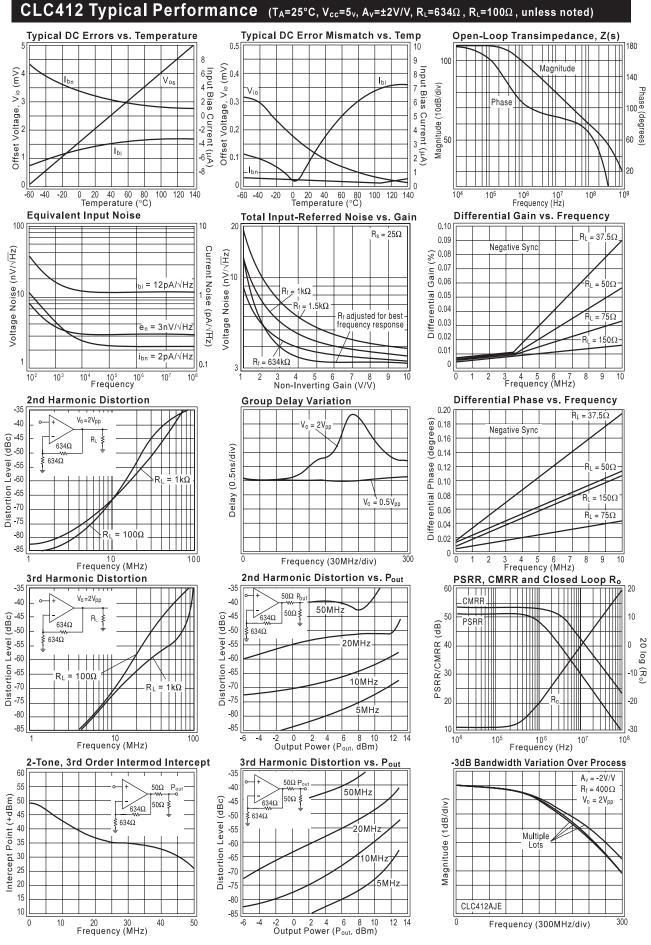

The "optimum feedback transimpedance" is unique for each current-feedback op amp and determines the recommended value of R<sub>f</sub> for a particular gain setting. Drawing a horizontal line on the "Open-loop Transimpedance, Z(s)" plot from 57.5dB (on the left vertical axis), we find the intersection with the transimpedance magnitude trace occurs at a frequency of 180MHz. This frequency is only an approximation of the CLC412's small-signal bandwidth. From this intersection, one can see that an increase in Z<sub>t</sub> will produce a new intersection occurring at a lower frequency. This is the process to follow when bandlimiting. Once the target small-signal bandwidth is determined, the new value of Z<sub>t</sub> is picked off the graph at the point where the this frequency and the transimpedance magnitude trace intersect. One can then back track to figure the value of the feedback resistor,  $R_f = Z_t - R_{in}(1 + R_f / R_a)$ . This new value of R<sub>f</sub> will produce the desired frequency roll-off.

#### **Circuit Layout**

With all high-frequency devices, board layouts with stray capacitances have a strong influence over AC performance. The CLC412 is no exception and its input and output pins are particularly sensitive to the coupling of parasitic capacitances (to ac ground) arising from traces or pads placed too closely (<0.1") to power or ground planes. In some cases, due to the frequency response peaking caused by these parasitics, a small adjustment of the feedback resistor value will serve to compensate the frequency response. Also, it is very important to keep the parasitic capacitance across the feedback resistor to an absolute minimum.

The performance plots in the data sheet can be reproduced using the evaluation boards available from Comlinear. There are two types of boards; the DIP (#730038) and SOIC (#730036). The #730036 board uses all SMT parts for the evaluation of the CLC412 in its

surface mount package. Either of these layouts can assist the designer in obtaining the desired performance. In addition, the boards can serve as an example layout for the final production printed circuit board.

Care must also be taken with the CLC412's layout in order to achieve the best circuit performance, particularly channel-to-channel isolation. The decoupling capacitors (both tantalum and ceramic) must be chosen with good high frequency characteristics to decouple the power supplies and the physical placement of the CLC412's external components is critical. Grouping each amplifier's external components with their own ground connection and separating them from the external components of the opposing channel with the maximum possible distance is recommended. The input ( $R_{in}$ ) and gain-setting resistors ( $R_g$ ) are the most critical. It is also recommended that the ceramic decoupling capacitor ( $0.1\mu$ F chip or radial-leaded with low ESR) should be placed as closely to the power pins as possible.

#### Package Parasitics

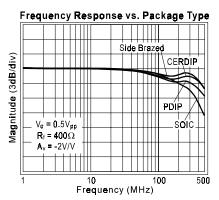

In addition to the parasitic capacitances arising from the board layout, each of the CLC412's packages has its own characteristic set of parasitic capacitances and inductances causing frequency response variation from package to package as shown in the plot below labeled "Frequency Response vs. Package Type". Due to its much smaller size, the CLC412AJE (8-pin SOIC) shows the least amount of peaking.

#### **Matching Performance**

With proper board layout, the AC performance match between the two CLC412's amplifiers can be tightly

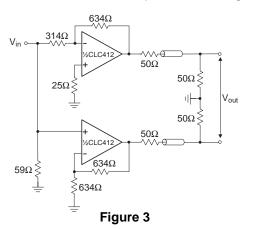

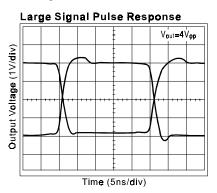

controlled as shown in Typical Performance plot labeled "Small-Signal Channel Matching". The measurements were performed with SMT components using the recommended value of feedback resistor of  $634\Omega$  at a gain of +2V/V. The pulse response plot labeled "Pulse Matching" found below shows the group delay matching between amplifiers of the CLC412. The circuit topology is described in Figure 3.

The CLC412's amplifiers, built on the same die, provide the advantage of having tightly matched DC characteristics. The typical DC matching specifications of the CLC412 are:

$\Delta$ Vio = ±0.60mV,  $\Delta$ Ibn = ±0.25 $\mu$ A,  $\Delta$ Ibi = ±1.5 $\mu$ A.

#### **Slew Rate and Settling Time**

One of the advantages of current-feedback topology is an inherently high slew rate which produces a wider full-power bandwidth. The CLC412 has a typical slew rate of 1300V/ $\mu$ s. The required slew rate for a design can be calculated by the following equation: SR=2 $\pi$ fV<sub>pk</sub>

Careful attention to parasitic capacitances is critical to achieving the best settling time performance. The CLC412 has a typical short term settling time to 0.05% of 12ns for a 2 volt step. Also, the amplifier is virtually free of any long term thermal tail effects at low gains as shown in the Typical Performance plot labeled "Long Term Settling Time".

When measuring settling time, a solid ground plane should be used in order to reduce ground inductance which can cause common-ground-impedance coupling. Power supply and ground trace parasitic capacitances and the load capacitance will also affect settling time.

Placing a series resistor ( $R_s$ ) at the output pin is recommended for optimal settling time performance when driving a capacitive load. The Typical Performance plot labeled " $R_s$  and Settling Time vs. Capacitive Load" provides a means for selecting a value of  $R_s$  for a given capacitive load. The plot also shows the resulting settling time to 0.05 and 0.01%.

### **DC & Noise Performance**

A current-feedback amplifier's input stage does not have equal nor correlated bias currents, therefore they cannot be canceled and each contributes to the total DC offset voltage at the output by the following equation:

$$V_{offset} = \pm \left( I_{bn} * R_s \left( 1 + \frac{R_f}{R_g} \right) + V_{io} \left( 1 + \frac{R_f}{R_g} \right) + I_{bi} * R_f \right)$$

The input resistor  $R_{in}$  is the resistance looking from the non-inverting input back towards the source. For inverting DC-offset calculations, the source resistance seen by the input resistor  $R_g$  must be included in the output offset calculation as a part of the non-inverting gain equation. Application note OA-7 gives several circuits for DC offset correction. The noise currents for the inverting and non-inverting inputs are graphed in the Typical Performance plot labeled "Equivalent Input Noise". A more complete discussion of amplifier input-referred noise and external resistor noise contribution can be found in OA-12.

#### **Differential Gain & Phase**

The CLC412 can drive multiple video loads with very low differential gain and phase errors. The Typical Performance plots labeled "Differential Gain vs. Frequency" and "Differential Phase vs. Frequency" show performance for loads from 1 to 4. The Electrical Characteristics table also specifies guaranteed performance for one 150 $\Omega$  load at 4.43MHz. For NTSC video, the guaranteed performance specifications also apply. Application note OA-08, "Differential Gain and Phase for Composite Video Systems," describes in detail the techniques used to measure differential gain and phase.

#### I/O Voltage & Output Current

The usable common-mode input voltage range (CMIR) of the CLC412 specified in the Electrical Characteristics table of the data sheet shows a range of  $\pm 2.2$  volts. Exceeding this range will cause the input stage to saturate and clip the output signal.

The output voltage range is determined by the load resistor and the choice of power supplies. With  $\pm 5$  volts the class A/B output driver will typically drive +3.1/-2.7 volts into a load resistance of 100 $\Omega$ . Increasing the supply voltages will change the common-mode input and output voltage swings while at the same time increase the internal junction temperature. The output voltage for different load resistors can be determined from the data sheet plots labeled "Frequency Response vs. Load (R<sub>L</sub>)" and "Maximum Output Swing vs. Frequency".

#### **Applications Circuits**

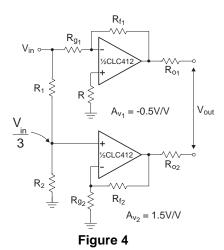

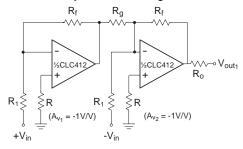

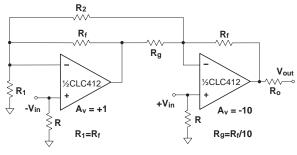

#### Single-to-Differential Line Driver.

The CLC412's well matched AC channel-response allows a single-ended input to be transformed to highly-matched push-pull driver. From a 1V single-ended input the circuit of Figure 4 produces 1V differential signal between the two outputs. For larger signals, the input voltage divider ( $R_1$ =2 $R_2$ ) is necessary to limit the input voltage on channel 2. To achieve the same performance when driving a matched load, see Figure 3.

Differential Line Receiver. Figures 5 and 5a show two different implementations of an instrumentation amplifier which convert differential signals to single-ended. Figure 5a allows CMRR adjustment through R<sub>2</sub>.

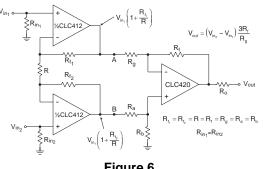

#### **High-Speed Instrumentation Amplifier.**

For applications requiring higher CMRR the composite circuit of Figure 6 uses the two amplifiers of the CLC412 to create balanced inputs for the CLC420 voltagefeedback op amp. The DC CMRR can be fine tuned through the adjustment of R<sub>b</sub>. Further improvement of

Figure 6

CMRR over frequency can be achieved through the placement of an RC network between the outputs (A and B) of the two amplifiers of the CLC412.

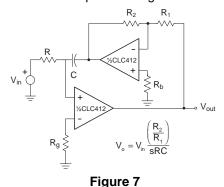

## Non-Inverting Current-Feedback Integrator.

The circuit of Figure 7 achieves its high-speed integration by placing one of the CLC412's amplifiers in the feedback loop of the second amplifier configured as shown.

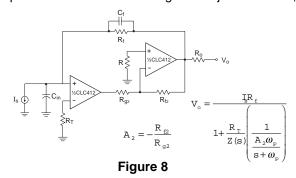

Low-Noise Wide-Bandwidth Transimpedance Amplifier. Figure 8 implements a low-noise transimpedance amplifier using both channels of the CLC412. This circuit takes advantage of the lower inputbias-current noise of the non-inverting input and achieves negative feedback through the second CLC412 channel. The output voltage is set by the value of R<sub>f</sub> while frequency compensation is achieved through the adjustment of R<sub>T</sub>.

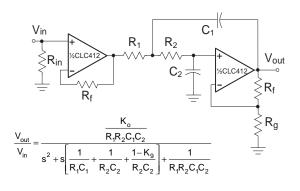

Buffered 2nd-Order Sallen-Key Low-Pass Filter.

Figure 9 shows one implementation of a 2nd order Sallen-Key low pass filter buffered by one of the CLC412's channels. The CLC412 enables greater precision since it provides the advantage of very low output impedance and very linear phase throughout the pass-band.

Figure 9

This page intentionally left blank.

This page intentionally left blank.

This page intentionally left blank.

#### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 2501 Miramar Tower 1-23 Kimberley Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.