# CLC5509 Ultra-Low Noise Preamplifier

# **General Description**

The CLC5509 is a high performance, ultra-low noise preamplifier designed for applications requiring unconditional stability for wide ranges of complex input loads. Both input impedance and gain are externally adjustable, which make it simple to interface to peizoelectric ultrasound transducers. The CLC5509 preamplifier's low 0.58n√Hz total input noise makes it ideal for noise sensitive front ends. The high repeatability in group delay over voltage and temperature translates into precision edge measurements for Doppler applications.

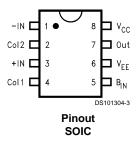

The IC consists of an emitter input, common base amplifier stage followed by a low distortion, closed loop buffer. External negative feedback creates a well controlled input impedance to allow a near noiseless active input transmission line termination. The preamp is stable against changes in source impedance of 50 to  $200\Omega$  over temperature and supply variations, with gains from 14dB to 26dB. The CLC5509 preamp architecture is also well suited for use with magneto-resistive tape or disk drive heads. In these applications the head bias current can be reused to bias the preamp. The part is packaged in an 8-pin plastic SOIC, and runs off  $\pm5V$  supplies. External biasing is required for the input signal path.

The CLC5509 is constructed using an advanced complementary bipolar process and National Semiconductor's proven high performance architectures.

#### **Features**

- 0.58nV√Hz total input noise @ 12MHz

- < .5ns group delay repeatability

- High cutoff -3dB @ 33MHz

- Low cutoff -3dB @ 0.5MHz

- 2.0dB noise figure @ 50Ω

- -60dBc intermod for 2V<sub>PP</sub> @ 5MHz

- Supply current: 11mA

- Available in 8-pin SOIC

# **Applications**

- Ultrasound preamp

- Tape drive preamp

- Disk drive preamp

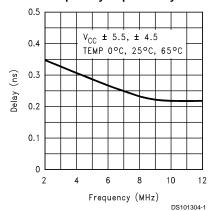

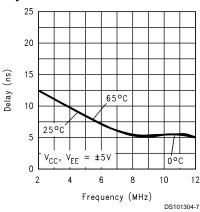

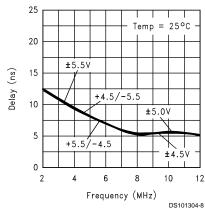

#### **Group Delay Repeatability**

# **Connection Diagram**

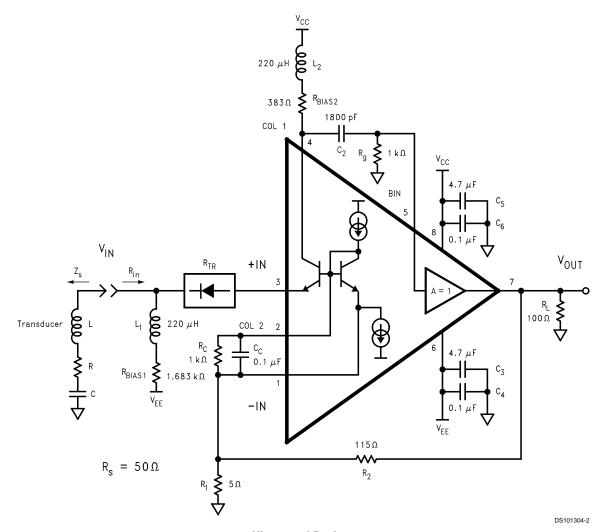

# **Typical Application**

**Ultrasound PreAmp**

# **Ordering Information**

| Package    | Temperature Range<br>Industrial<br>0°C to 70°C | Packaging<br>Marking | Transport Media | NSC<br>Drawing |

|------------|------------------------------------------------|----------------------|-----------------|----------------|

| 8-pin SOIC | CLC5509CM                                      | CLC5509CM            | Rails           | M08A           |

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ±5.5V

Output Current 70mA

$\begin{array}{lll} \mbox{Common-Mode Input Voltage} & \pm \mbox{V}_{\rm CC} \\ \mbox{Maximum Junction Temperature} & +150 \mbox{^{\circ}C} \\ \mbox{Storage Temperature Range} & -65 \mbox{^{\circ}C to } +150 \mbox{^{\circ}C} \\ \mbox{Lead Temperature (soldering 10 sec)} & +300 \mbox{^{\circ}C} \\ \mbox{ESD Rating (human body model)} & 4000 \mbox{V} \\ \end{array}$

# **Electrical Characteristics** (Note 3)

(V<sub>CC</sub>, V<sub>EE</sub> =  $\pm 5$ V, R<sub>S</sub> =  $50\Omega$ , A<sub>V</sub> = 10V/V, R<sub>g</sub> = 1k $\Omega$ , R<sub>L</sub> =  $100\Omega$ ; unless specified)

| Symbol     | Parameter                            | Conditions                                           | Тур         | Min/Max<br>Ratings<br>(Note 2) | Units |

|------------|--------------------------------------|------------------------------------------------------|-------------|--------------------------------|-------|

| Ambient T  | emperature                           | CLC5509                                              | +25°C       | +25°C                          |       |

| Frequenc   | y Domain Response                    |                                                      |             |                                |       |

|            | -3dB Bandwidth                       | V <sub>O</sub> < 2.0V <sub>PP</sub>                  |             |                                |       |

|            | High Cutoff                          | -3dB                                                 | 33          | 28<br>45                       | MHz   |

|            | Low Cutoff                           | -3dB                                                 | 0.5         | 0.4<br>0.7                     | MHz   |

|            | Gain Flatness Inband                 | 2 < 12.5MHz, V <sub>O</sub> < 1.0V <sub>PP</sub>     | –1.5<br>+.1 |                                | dB    |

|            | Gain Accuracy @ 5MHz                 |                                                      |             | ±0.3                           | dB    |

|            | Phase Variation                      | $3 < 9$ MHz, $V_O < .1$ $V_{PP}$                     | 1           |                                | Deg   |

|            | Gain Variation                       | $3 < 9$ MHz, $V_O < .1$ $V_{PP}$                     | .3          |                                | dB    |

| Time Don   | nain Response                        |                                                      |             |                                | •     |

|            | Rise and Fall Time                   | 2V step                                              | 10          | 10<br>15                       | ns    |

|            | Settling Time to 0.2%                | 2V step                                              | 1           |                                | μs    |

|            | Overshoot                            | 2V step                                              | 0           | 5                              | %     |

|            | Group Delay                          | 2.5MHz < 10MHz, V <sub>IN</sub> = 10mV <sub>PP</sub> | 5.5         | 3<br>7.5                       | ns    |

|            | Group Delay Repeatability            |                                                      | .5          |                                | ns    |

| Distortion | And Noise Response                   |                                                      |             |                                |       |

|            | 2nd Harmonic Distortion              | < 12.5MHz, V <sub>IN</sub> = 100mV <sub>PP</sub>     | -51         |                                | dBc   |

|            | 3rd Harmonic Distortion              |                                                      | -56         |                                | dBc   |

|            | Intermodulation Distortion           | @ 5MHz                                               | -65         |                                | dBc   |

|            | Equivalent Input Noise Voltage (eni) | $>$ 1MHz, R <sub>S</sub> = $50\Omega$                | 0.7         | 0.78                           | nV√Hz |

|            | Noise Figure                         | @ 50Ω                                                | 2           | 2.4                            | dB    |

|            | Optimum R <sub>S</sub>               |                                                      | 85          | 80<br>110                      | Ω     |

| Static, DO | Performance                          |                                                      |             |                                |       |

|            | PSRR (preamp only)                   | < 1MHz                                               | 40          |                                | dB    |

|            | Supply Current (preamp only)         | R <sub>L</sub> = ∞                                   | 9           | 11                             | mA    |

| Miscellan  | eous Performance                     |                                                      |             |                                |       |

|            | Output Impedance                     | DC < 12MHz                                           | 0.2         | 0.2<br>1                       | Ω     |

|            | Output Voltage Range                 | $R_L = 100\Omega$                                    | ±2          | ±1.7                           | V     |

|            | Output Current                       |                                                      | ±45         | ±35                            | mA    |

# Electrical Characteristics (Note 3) (Continued)

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

Note 2: Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

Note 3: All data taken in circuit shown as typical application.

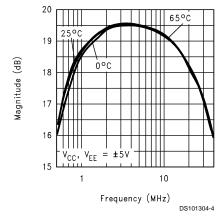

# **Typical Performance Characteristics**

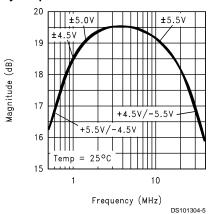

#### Frequency Response

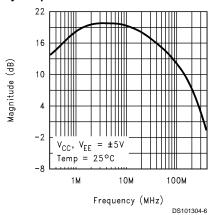

#### Frequency Response

#### Frequency Response

#### **Group Delay**

## **Group Delay**

#### 3rd Harmonic Distortion

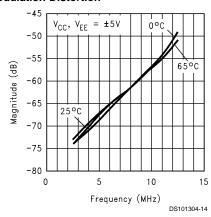

#### **3rd Harmonic Distortion**

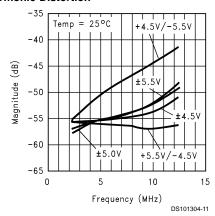

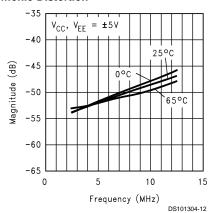

#### 2rd Harmonic Distortion

#### **2rd Harmonic Distortion**

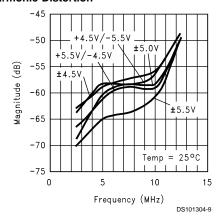

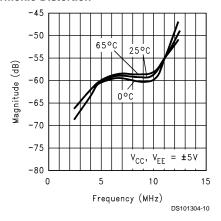

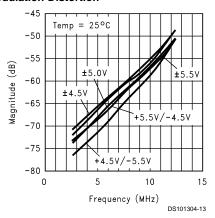

#### Intermodulation Distortion

#### Intermodulation Distortion

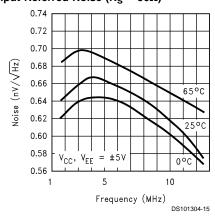

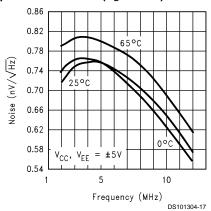

## Total Input Referred Noise ( $R_S = 50\Omega$ )

Total Input Referred Noise ( $R_s = 50\Omega$ )

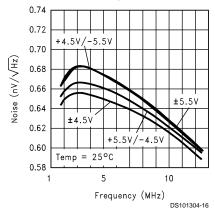

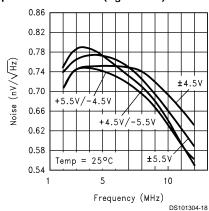

Total Input Referred Noise (R<sub>s</sub> = 100 $\Omega$ )

Total Input Referred Noise ( $R_S = 100\Omega$ )

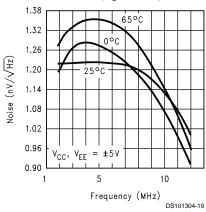

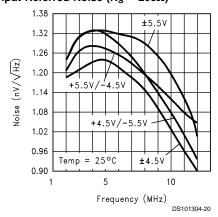

Total Input Referred Noise ( $R_S = 200\Omega$ )

Total Input Referred Noise ( $R_S = 200\Omega$ )

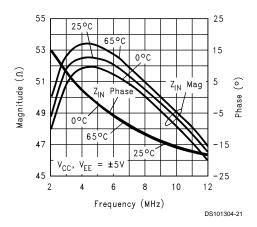

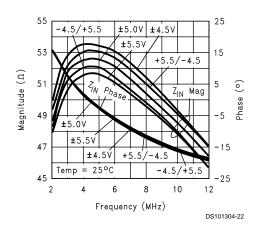

$\mathbf{Z}_{\mathsf{in}}$

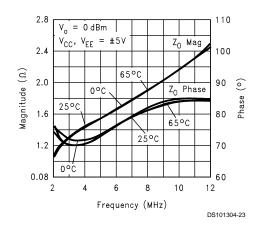

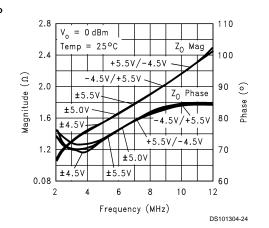

# $\mathbf{Z}_{\mathbf{O}}$

## $\mathbf{z_o}$

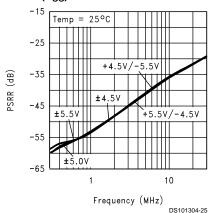

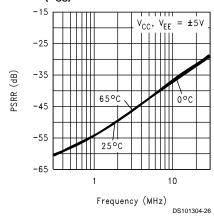

# Positive PSRR (V<sub>CC</sub>)

#### Positive PSRR (V<sub>CC</sub>)

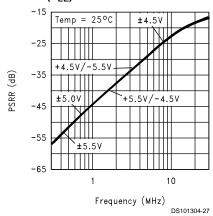

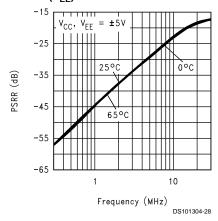

## Negative PSRR (V<sub>EE</sub>)

# Negative PSRR (V<sub>EE</sub>)

# **Application Information**

#### Introduction

The CLC5509 is a two stage ultra-low noise preamplifier, with low distortion, and externally variable input impedance. The unusual emitter driven input stage remains stable for a wide range of transducer source loads. The input termination can be matched (for 50-200 $\Omega$  source matching) to a wide range of complex loads (C $_{\rm S}$  up to 5000pF and C $_{\rm P}$  up to 10000pF, L $_{\rm S}$  up to 1 $\mu$ H). The IC was designed for low cost multiple channel ultrasound applications requiring flexible configurations for a variety of transmit/receive topologies. In a typical application, the CLC5509 is connected to a single element of an ultrasound transducer through a transmit/receive switch.

#### Theory of Operation

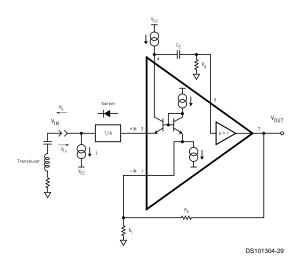

The CLC5509 simplified circuit is shown in *Figure 1*. For analysis, the transmit/receive switch diode is modeled in the circuit as a series resistance  $R_{TR}$  with a voltage drop of  $V_{RT}$ . A piezo transducer generated, single-ended voltage signal is applied to the emitter input of the 1st stage. The voltage signal is converted to a current (i) that is passed through a high pass filter then restored back to a voltage signal at  $R_g$ . A high speed, low distortion, unity gain buffer, applies the signal to the load and feedback resistor. Negative feedback from the buffer output to the inverting input completes the signal path.

FIGURE 1. Simplified Circuit

The input and output voltage can be expressed as shown:

$$V_{in} = (R_{TR} + r_e) i + V_O (R_1/(R_1 + R_2))$$

$V_O = -(i \times R_a)$  for  $\alpha = 1$

The input resistance is calculated

$$R_{IN} = \frac{V_{IN}}{Li} = R_{TR} + r_e + R_g(R_1/(R_1 + R_2))$$

The current  $\rm I_{\rm BIAS1}$  is the input stage emitter current that sets  $\rm r_{\rm e}.$

$$I_{BIAS1} = (V_{EE} - V_{TR})/R_{BIAS1}$$

for  $V_{EE} = V_{TR} = .65V$

$r_e = 26mV/I_{BIAS1}$

Combining terms, then solving for close loop gain  $V_{\text{O}}/V_{\text{in}}$  results in

$$A_{CL} \simeq \frac{R_g}{R_{IN}}$$

www.national.com

# **Application Information** (Continued)

#### **Choosing External Component Values**

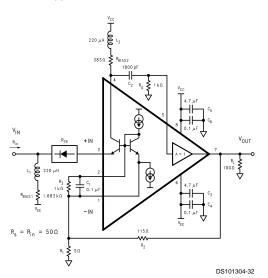

There are three key parameters to consider in the design: Noise, signal bandwidth, and gain. Refer to *Figure 2*.

The best noise performance for a given transmit/receive switch  $R_{TR}$  is obtained by: choosing  $R_S$  between  $50\Omega$  and  $200\Omega$ ; selecting the matching termination resistance  $R_{\rm in}$ ; and by reducing  $I_{\rm BIAS1}$  (by increasing  $R_{\rm BIAS1}$ ) to increase  $r_{\rm e}$  which optimizes the Noise Figure (NF). For this circuit, with  $R_{TR}=6\Omega$ , the optimum NF is achieved at  $R_s\sim95\Omega$  when  $R_{\rm in}$  is set to  $50\Omega$  and  $R_s\sim145\Omega$  when  $R_{\rm in}$  is set to  $200\Omega$ .

The signal bandwidth is determined by the selection of L $_1$ , L $_2$ , R $_{\rm BIAS1}$  and R $_{\rm BIAS2}$  which set the open loop gain roll-off of the first stage. R $_g$  and C $_2$  form a desirable signal path filter that introduces an additional highpass pole. The filter values can be chosen to create a sharper high frequency roll off of the closed loop gain. For R $_g$  = 1k, C2 ~ 470pF the small signal (V $_{\rm in}$  < 25mW), wide bandwidth performance can be observed. By increasing C $_2$  (to > 1500pF) and increasing output series resistance with a small resistor, the stability and harmonic distortion performance can be improved for large signals. This filter can also be designed as a multi-pole Butterworth filter but care must be taken to ensure stability with the desired load over the operating temperature range.

The passband gain is customer selected by setting  $R_{\rm g}$  and  $R_{\rm in}$ . Note that using  $R_{\rm 1}$  to reduce or increase the gain allows for minimal interaction with other parameters.

Capacitor  $C_C$  and resistor  $R_C$  are used for local compensation of the gm input stage with values of  $C_C$  = 0.1 $\mu$ F and  $R_C$  = 1k for the applications described below.

FIGURE 2. Complete Circuit

#### **Calculating and Measuring the Noise**

The circuit input referred noise is best calculated using a SPICE model where the external components can be optimized for the transducer source impedance and transmit/receive switch impedance. The SPICE model for the CLC5509 is available on the NSC web site. Refer to the figures for total noise performance over temperature and supply at 3mA. Once the noise is modeled and circuit parameters chosen the evaluation board can be used to measure actual noise performance.

To measure the CLC5509 input referred noise vs. other noise sources, several key steps should be followed. The

bench setup is fairly simple using the evaluation board and a spectrum analyzer. (If a noise figure meter is available that is even easier yet.) The procedure requires calibrating out the spectrum analyzer background noise, and other noise sources from the CLC5509 noise. Since the thermal noise of a resistor is well known, add a series resistor R4 between the signal source V<sub>in</sub> and the L<sub>1</sub>, R<sub>BIAS1</sub> bias network for these noise measurements. Several R<sub>4</sub> resistor values are used as "reference" noise sources. The values chosen depend on the  $R_s$  of the system. For  $R_s = 50\Omega$ , resistor ( $R_4$ ) with values of 0, 12.5, 25,  $50\Omega$  should be used. If  $R_s = 200\Omega$ , resistors  $(R_4)$  with values of 0, 25, 50, 100,  $200\Omega$  should be used. Start by connecting the analyzer input to the evaluation board output. Remove R4 from the signal source and connect R₄ to GND. Now take at least 10 measurements and average them for each R4 reference value. Be sure to divide the result by the analyzer and circuit gain to make the noise input referred. Subtract the  $R_4 = 0\Omega$  results from the data for each value. Compare the result to the theoretical noise values. They should agree closely over the  $R_s = 0$  to  $R_{in}$  range. This verifies the test method. The CLC5509 noise is the  $R_s$  =  $0\Omega$  data point. A similar procedure can be used to remove the T/R switch noise by varying the T/R bias current  $I_{\text{BIAS1}}$ . The total circuit noise performance can now be optimized for R<sub>in</sub> as described above.

#### **Evaluation Board**

Evaluation boards are available for customer product evaluation for the 8-pin SOIC. Evaluation kits that contain an evaluation board and CLC5509 samples can be obtained by calling National Semiconductor's Customer Service Center. The evaluation kit number is CLC730101. The evaluation board utilizes surface mount components. The corner frequencies are set to ~ 0.9MHz to 12.5MHz with a passband gain set at 20dB. The highpass filter is set at  $R_{q} = 1k$ , C<sub>2</sub> = 470pF to view small signal (V<sub>in</sub> < 25mV) performance. Increasing C<sub>4</sub> (to > 1500pF) reduces the bandwidth and improves distortion for large signals. R9, is a back match resistor that terminates the output and isolates cable capacitance, for minimum distortion, over the frequency band of interest. An  $R_{in} \sim 50.2\Omega$  was chosen for  $R_s = 50\Omega$  (this source resistor  $R_s$  is open ) and  $R_{TR}$  = 0, with  $I_{BIAS1}$  set to 3mA. The expected input referred noise based on bench measurements on similar boards is ~ 0.6nV√Hz or a NF of 2dB. The noise can be optimized with slight variations in R2, R<sub>g</sub> and R<sub>BIAS1</sub>. If transmit/receive switches are added to the evaluation board both the voltage drop and RTR should be compensated for. The Rin, gain and noise will be affected by the addition of the T/R switch. The  $V_{TR}$  drop can be removed, to a first order, by adding a second switch in series with the feedback gain setting resistor R<sub>1</sub> to ground. This will restore the input DC level to  $\sim$  0V. This T/R switch diode should be biased with a resistor (~  $R_{\mbox{\scriptsize BIAS2}})$  to  $\mbox{\scriptsize V}_{\mbox{\scriptsize CC}}$  and bypassed with a 0.1µF cap to maintain the same AC performance as the evaluation board without the switches.

#### **CLC5509 Applications**

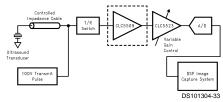

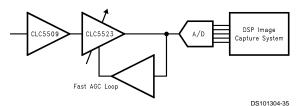

The signal path for a typical ultrasound transceiver is shown in *Figure 3*.

FIGURE 3.

www.national.com

# Application Information (Continued)

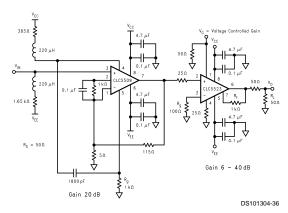

The CLC5509 system dynamic range performance is enhanced by using the CLC5523 variable gain amplifier as a post amplifier. See *Figure 4* below.

The signal gain range is divided between the CLC5509 preamplifier and the post amplifier to allow wider dynamic range and better performance for high crest factor signals. There are two common ways the CLC5523 variable gain could be controlled. The first, *Figure 5*, uses a DAC to digitally increase the gain in discrete steps. The second *Figure 6* uses an AGC loop to maintain the maximum system input signal-to-noise. Refer to the CLC5523 data sheet applications for the implementation details.

FIGURE 4. Low Noise Pre Amp with Variable Gain Amplifier Circuit

FIGURE 5. V<sub>G</sub> Controlled by DAC in Discrete Steps

FIGURE 6. V<sub>G</sub> Controlled by AGC Loop

www.national.com 10

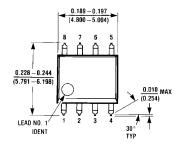

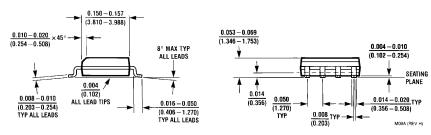

## Physical Dimensions inches (millimeters) unless otherwise noted

8-pin SOIC Order Number CLC5509CM NS Product Number M08A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

National Semiconductor Europe

Fax: +49 (0) 1 80-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 1 80-530 85 85 English Tel: +49 (0) 1 80-532 78 32 Français Tel: +49 (0) 1 80-532 93 58 Italiano Tel: +49 (0) 1 80-534 16 80 National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com

Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National Semiconductor