💫 National Semiconductor

February 1992

# NS32FX161-15/NS32FX161-20/NS32FX164-20/ NS32FX164-25/NS32FV16-20/NS32FV16-25 Advanced Imaging/Communication Signal Processors

## **General Description**

The NS32FX164, the NS32FV16 and the NS32FX161 are high-performance 32-bit members of the Series 32000®/ EP™ family of National's Embedded System Processors™ specifically optimized for CCITT Group 2 and Group 3 Facsimile Applications, Data Modems, Voice Mail Systems, Laser Printers, or any combination of the above.

Unless specified otherwise any reference to the NS32FX164 in this document applies to the NS32FV16 and the NS32FX161 as well.

The NS32FX164 can perform all the computations and control functions required for a stand-alone Fax system, a PC add-in Fax/Voice/Data Modem card or a Laser/Fax system.

It also meets the performance requirements to implement 14400, 9600 and 7200 bps modems complying with CCITT V.17, V.29 and V.27 standards. The NS32FV16 supports V.29 and V.27 standards as well as voice. The NS32FX161 supports V.29 and V.27 standards.

The NS32FX164 provides a 16 Mbyte Linear external address space and a 16-bit external data bus.

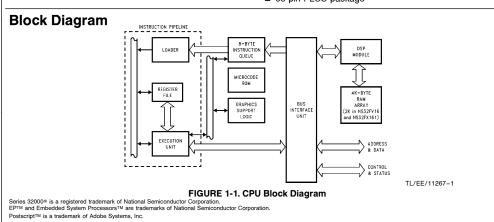

The CPU core, which is the same as that of the NS32CG16, incorporates a 32-bit ALU and instruction pipeline, and an 8-byte prefetch queue.

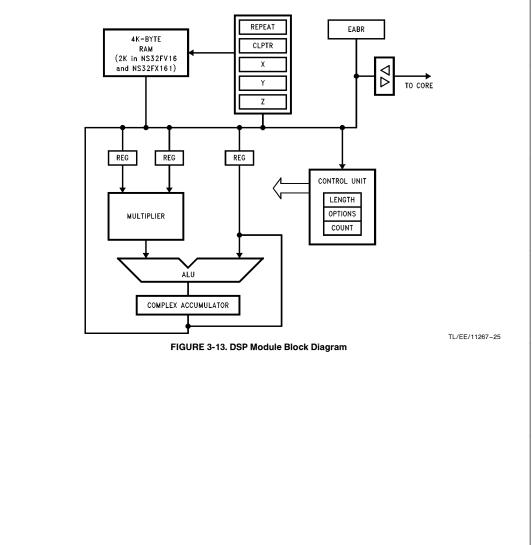

Also integrated on-chip with the CPU are a DSP Module (DSPM) and a 4K-byte RAM Array (2K in the NS32FV16 and NS32FX161). The DSPM is a complete processing unit, capable of autonomous operation parallel to the CPU core operation. The DSPM executes programs stored in an internal on-chip Random Access Memory (RAM), and manipulates data stored either in the internal RAM or in an external off-chip memory. To maximize utilization of hardware resources, the DSPM contains a pipelined DSP-oriented datapath, and a control logic that implements a set of DSP vector commands

The NS32FX164 capabilities can be expanded by using an external floating point unit (FPU) which directly interfaces to the NS32FX164 using the slave protocol. The CPU-FPU cluster features high speed execution of the floating-point instructions.

The NS32FX164 highly-efficient architecture combined with the NS32CG16 graphics instructions and the high-performance vector operation capability, makes the device the ideal choice for Postscript™ and Fax applications.

## Features

- Software compatible with the Series 32000/EP processors

- Designed around the CPU core of the NS32CG16

- Pin compatible with the NS32FX16

- 32-bit architecture and implementation

- On-chip DSP Module for high-speed DSP operations

- Special support for graphics applications

- 18 graphics instructions Binary compression/expansion capability for font

- storage using RLL encoding

- Pattern magnification Interface to an external BITBLT processing units for

- fast color BITBLT operations 4K-byte on-chip RAM array (2K in NS32FV16 and

- NS32FX161) On-chip clock generator

- Floating-point support via the NS32081 or NS32181 Optimal interface to large memory arrays via the NS32CG821 and the DP84xx family of DRAM controllers

- Power save mode

- High-speed CMOS technology

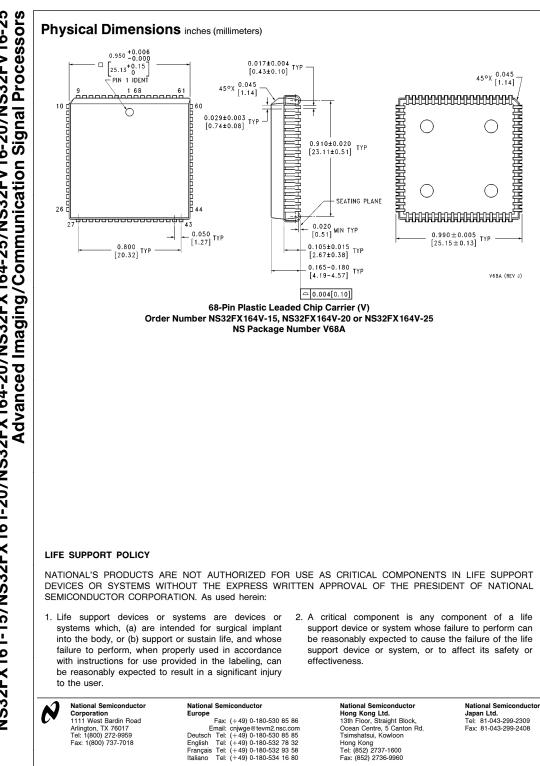

- 68-pin PLCC package

© 1995 National Semiconductor Corporation TL/EE11267 RRD-B30M115/Printed in U.S.A

## **Table of Contents**

| 1.0 PRODUCT INTRODUCTION6                         |

|---------------------------------------------------|

| 1.1 NS32FX164 Special Features6                   |

| 2.0 ARCHITECTURAL DESCRIPTION7                    |

| 2.1 Register Set7                                 |

| 2.1.1 General Purpose Registers7                  |

| 2.1.2 Address Registers8                          |

| 2.1.3 Processor Status Register                   |

| 2.1.4 Configuration Register9                     |

| 2.1.5 DSP Module Registers9                       |

| 2.2 Memory Organization11                         |

| 2.2.1 Address Mapping12                           |

| 2.3 Modular Software Support12                    |

| 2.4 Instruction Set12                             |

| 2.4.1 General Instruction Format                  |

| 2.4.2 Addressing Modes14                          |

| 2.4.3 Instruction Set Summary16                   |

| 2.5 Graphics Support                              |

| 2.5.1 Frame Buffer Addressing                     |

| 2.5.2 BITBLT Fundamentals                         |

| 2.5.2.1 Frame Buffer Architecture                 |

| 2.5.2.2 Bit Alignment                             |

| 2.5.2.3 Block Boundaries and Destination<br>Masks |

| 2.5.2.4 BITBLT Directions                         |

| 2.5.2.5 BITBLT Variations                         |

| 2.5.3 Graphics Support Instructions               |

| 2.5.3.1 BITBLT (BIT-aligned BLock Transfer).23    |

| 2.5.3.2 Pattern Fill                              |

| 2.5.3.3 Data Compression, Expansion and           |

| Magnify24                                         |

| 2.5.3.3.1 Magnifying Compressed<br>Data           |

|                                                   |

| 3.0 FUNCTIONAL DESCRIPTION26                      |

| 3.1 Instruction Execution                         |

| 3.1.1 Operating States                            |

| 3.1.2 Instruction Endings                         |

| 3.1.2.2 Suspended Instructions                    |

| 3.1.2.3 Terminated Instructions                   |

| 3.1.2.4 Partially Completed Instructions27        |

| 3.1.3 Slave Processor Instructions                |

| 3.1.3.1 Slave Processor Protocol                  |

| 3.1.3.2 Floating-Point Instructions               |

| 3.2 Exception Processing                          |

| 3.2.1 Exception Acknowledge Sequence              |

|                                                   |

| nems     |                                                   |

|----------|---------------------------------------------------|

| 3.2.2    | Returning from an Exception Service<br>Procedure  |

| 3.2.3    | Maskable Interrupts                               |

|          | 3.2.3.1 Non-Vectored Mode                         |

|          | 3.2.3.2 Vectored Mode: Non-Cascaded               |

|          | Case                                              |

|          | 3.2.3.3 Vectored Mode: Cascaded Case35            |

| 3.2.4    | Non-Maskable Interrupt37                          |

| 3.2.5    | Traps                                             |

| 3.2.6    | Priority among Exceptions                         |

| 3.2.7    | Exception Acknowledge Sequences: Detailed<br>Flow |

|          | 3.2.7.1 Maskable/Non-Maskable Interrupt           |

|          | Sequence                                          |

|          | 3.2.7.2 SLAVE/ILL/SVC/DVZ/FLG/BPT/UND             |

|          | Trap Sequence                                     |

|          | 3.2.7.3 Trace Trap Sequence                       |

| 3.3 Debu | gging Support40                                   |

| 3.3.1    | Instruction Tracing40                             |

| 3.4 DSP  | Module                                            |

| 3.4.1    | Programming Model40                               |

| 3.4.2    | RAM Organization and Data Types41                 |

|          | 3.4.2.1 Integer Values                            |

|          | 3.4.2.2 Aligned-Integer Values41                  |

|          | 3.4.2.3 Real Values41                             |

|          | 3.4.3.4 Aligned-Real Values41                     |

|          | 3.4.2.5 Extended Precision Real Values41          |

|          | 3.4.2.6 Complex Values42                          |

| 3.4.3    | Command List Format42                             |

| 3.4.4    | CPU Core Interface42                              |

|          | 3.4.4.1 Synchronization of Parallel Operation .42 |

|          | 3.4.4.2 DSPM RAM Organization43                   |

| 3.4.5    | DSPM Instruction Set43                            |

|          | 3.4.5.1 Conventions                               |

|          | 3.4.5.2 Type Casting43                            |

|          | 3.4.5.3 General Notes                             |

|          | 3.4.5.4 Load Register Instructions44              |

|          | 3.4.5.5 Store Register Instructions45             |

|          | 3.4.5.6 Adjust Register Instructions              |

|          | 3.4.5.7 Flow Control Instructions                 |

|          | 3.4.5.8 Internal Memory Move Instructions 48      |

|          | 3.4.5.9 External Memory Move Instructions48       |

|          | 3.4.5.10 Arithmetic/Logical Instructions49        |

|          | 3.4.5.11 Multiply-and-Accumulate                  |

|          | Instructions49                                    |

|          | 3.4.5.12 Multiply-and-Add Instructions50          |

|          | 3.4.5.13 Clipping and Min/Max Instructions52      |

|          | 3.4.5.14 Special Instructions53                   |

|          |                                                   |

# Table of Contents (Continued)

| 3.5 System Interface55                |  |  |  |  |  |

|---------------------------------------|--|--|--|--|--|

| 3.5.1 Power and Grounding55           |  |  |  |  |  |

| 3.5.2 Clocking56                      |  |  |  |  |  |

| 3.5.3 Power Save Mode57               |  |  |  |  |  |

| 3.5.4 Resetting                       |  |  |  |  |  |

| 3.5.5 Bus Cycles58                    |  |  |  |  |  |

| 3.5.5.1 Bus Status58                  |  |  |  |  |  |

| 3.5.5.2 Basic Read and Write Cycles58 |  |  |  |  |  |

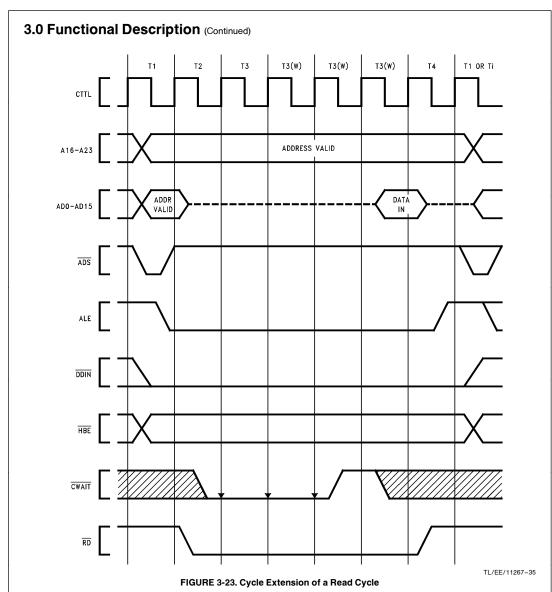

| 3.5.5.3 Cycle Extension62             |  |  |  |  |  |

| 3.5.5.4 Instruction Fetch Cycles63    |  |  |  |  |  |

| 3.5.5.5 Interrupt Control Cycles64    |  |  |  |  |  |

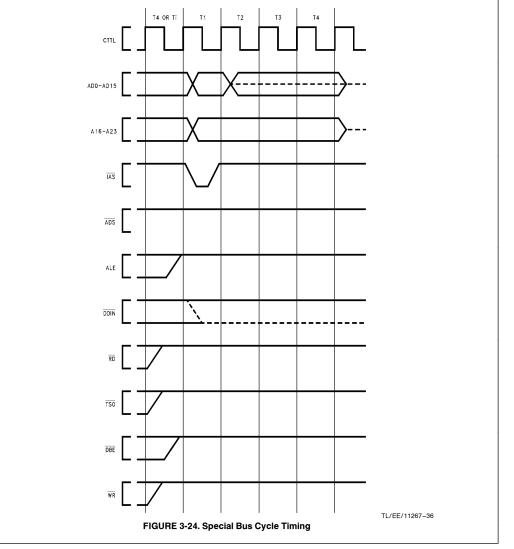

| 3.5.5.6 Special Bus Cycles65          |  |  |  |  |  |

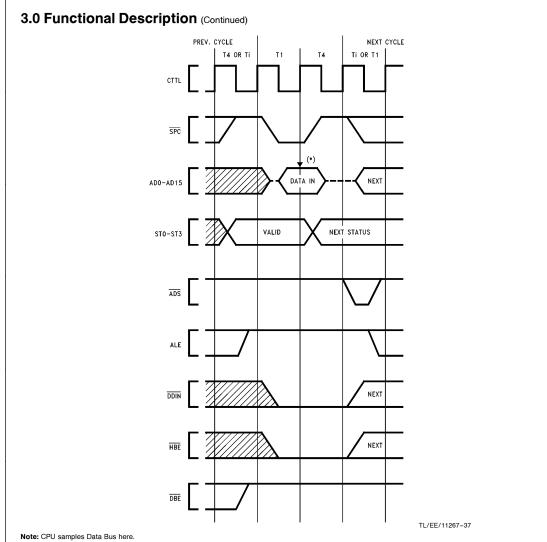

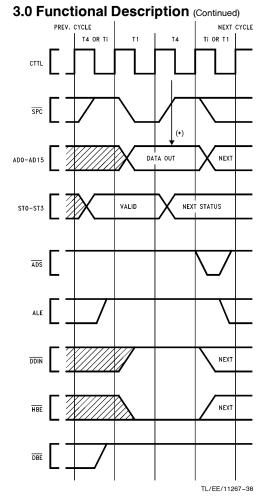

| 3.5.5.7 Slave Processor Bus Cycles 65 |  |  |  |  |  |

| 3.5.5.8 Data Access Sequences67       |  |  |  |  |  |

| 3.5.5.9 Bus Access Control            |  |  |  |  |  |

| 3.5.5.10 Instruction Status71         |  |  |  |  |  |

| 4.0 DEVICE SPECIFICATIONS             |  |  |  |  |  |

| 4.1 NS32FX164 Pin Descriptions71      |  |  |  |  |  |

| 4.1.1 Supplies                        |  |  |  |  |  |

| 4.1.2 Input Signals71                 |  |  |  |  |  |

| 4.1.3 Output Signals71                |  |  |  |  |  |

| 4.1.4 Input-Output Signals72          |  |  |  |  |  |

| 4.2 Absolute Maximum Ratings74                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 4.3 Electrical Characteristics74                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 4.4 Switching Characteristics74                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 4.4.1 Definitions74                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 4.4.2 Timing Tables75                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 4.4.2.1 Output Signals: Internal Propagation<br>Delays                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 4.4.2.2 Input Signal Requirements77                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 4.4.3 Timing Diagrams79                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

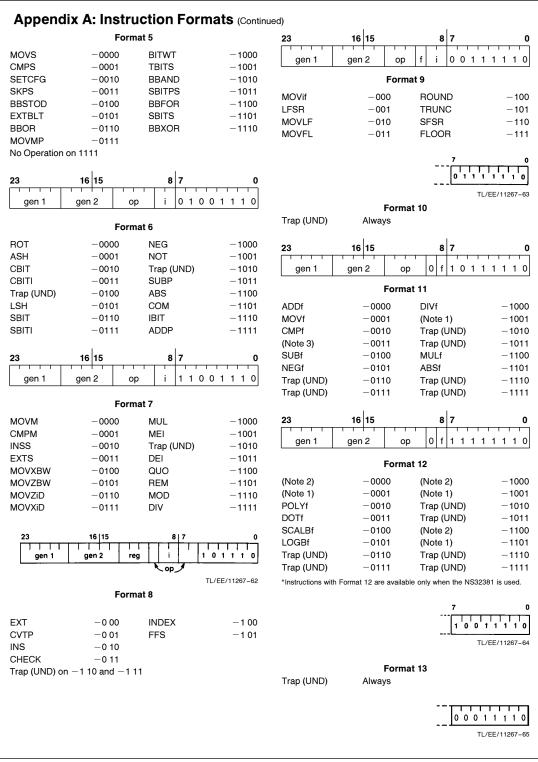

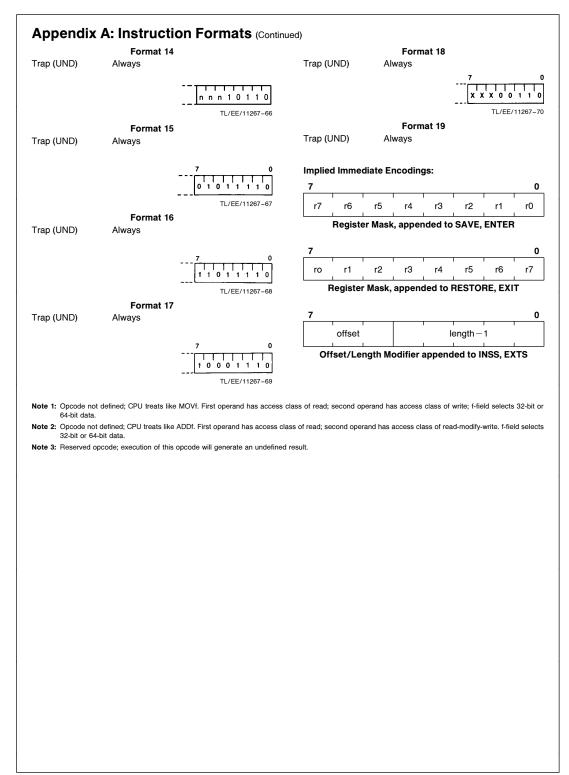

| APPENDIX A: INSTRUCTION FORMATS89                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| APPENDIX B: INSTRUCTION EXECUTION TIMES 92                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| B.1 Basic and Floating-Point Instructions                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| B.1 Basic and Floating-Point Instructions92                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| B.1 Basic and Floating-Point Instructions                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| B.1 Basic and Floating-Point Instructions       92         B.1.1 Equations       92         B.1.2 Notes on Table Use       93         B.1.3 Calculation of the Execution Time TEX for Basic                                                                                                                    |  |  |  |  |  |

| B.1 Basic and Floating-Point Instructions       92         B.1.1 Equations       92         B.1.2 Notes on Table Use       93         B.1.3 Calculation of the Execution Time TEX for Basic Instructions       93         B.1.4 Calculation of the Execution Time TEX for                                      |  |  |  |  |  |

| B.1 Basic and Floating-Point Instructions       92         B.1.1 Equations       92         B.1.2 Notes on Table Use       93         B.1.3 Calculation of the Execution Time TEX for Basic Instructions       93         B.1.4 Calculation of the Execution Time TEX for Floating-Point Instructions       93 |  |  |  |  |  |

# List of Figures

| FIGURE 1-1.  | CPU Block Diagram                                      |

|--------------|--------------------------------------------------------|

| FIGURE 2-1.  | NS32FX164 Internal Registers                           |

| FIGURE 2-2.  | Processor Status Register (PSR)                        |

| FIGURE 2-3.  | Configuration Register (CFG)9                          |

| FIGURE 2-4.  | DSP Module Registers Address Map                       |

| FIGURE 2-5.  | Accumulator Format                                     |

| FIGURE 2-6.  | X, Y, Z Registers Format9                              |

| FIGURE 2-7.  | EABR Register Format                                   |

| FIGURE 2-8.  | OVF Register Format                                    |

| FIGURE 2-9.  | PARAM Register Format                                  |

| FIGURE 2-10. | REPEAT Register Format                                 |

| FIGURE 2-11. | EXT Register Format                                    |

|              | CLSTAT Register Format                                 |

| FIGURE 2-13. | DSPINT and DSPMASK Register Format11                   |

|              | NMISTAT Register Format11                              |

| FIGURE 2-15. | NS32FX164 Address Mapping12                            |

|              | NS32FX164 Run-Time Environment                         |

| FIGURE 2-17. | General Instruction Format                             |

|              | Index Byte Format                                      |

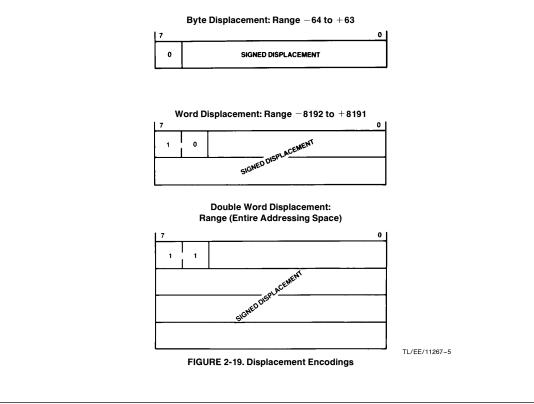

|              | Displacement Encodings14                               |

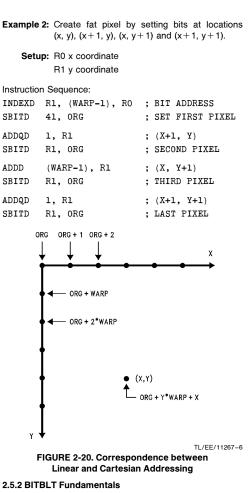

|              | Correspondence between Linear and Cartesian Addressing |

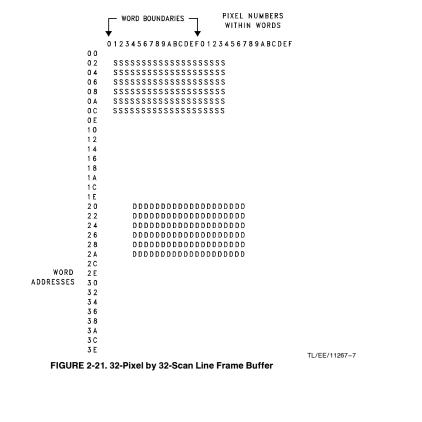

|              | 32-Pixel by 32-Scan Line Frame Buffer                  |

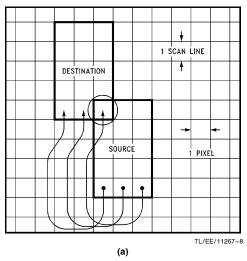

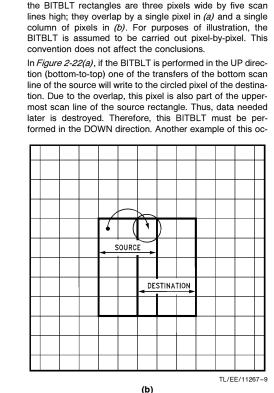

|              | Overlapping BITBLT Blocks                              |

|              | BB Instructions Format                                 |

|              | BITWT Instruction Format                               |

| FIGURE 2-25. | EXTBLT Instruction Format                              |

| FIGURE 2-26. | MOVMPi Instruction Format                              |

|              |                                                        |

|              | List of Figures (Continued)                                                   |

|--------------|-------------------------------------------------------------------------------|

| FIGURE 2-27. | . TBITS Instruction Format                                                    |

| FIGURE 2-28. | . SBITS Instruction Format                                                    |

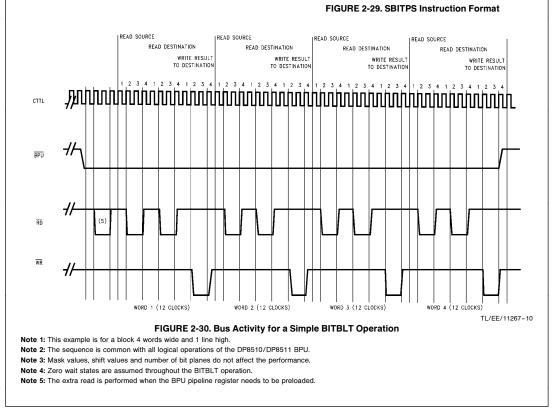

| FIGURE 2-29. | . SBITPS Instruction Format                                                   |

| FIGURE 2-30. | . Bus Activity for a Simple BITBLT Operation                                  |

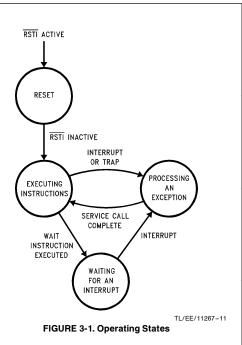

| FIGURE 3-1.  | Operating States                                                              |

| FIGURE 3-2.  | Slave Processor Protocol                                                      |

| FIGURE 3-3.  | Slave Processor Status Word                                                   |

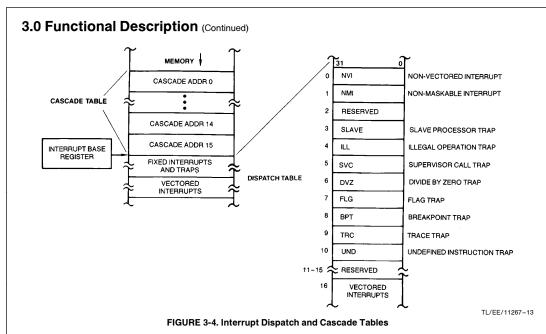

| FIGURE 3-4.  | Interrupt Dispatch and Cascade Tables                                         |

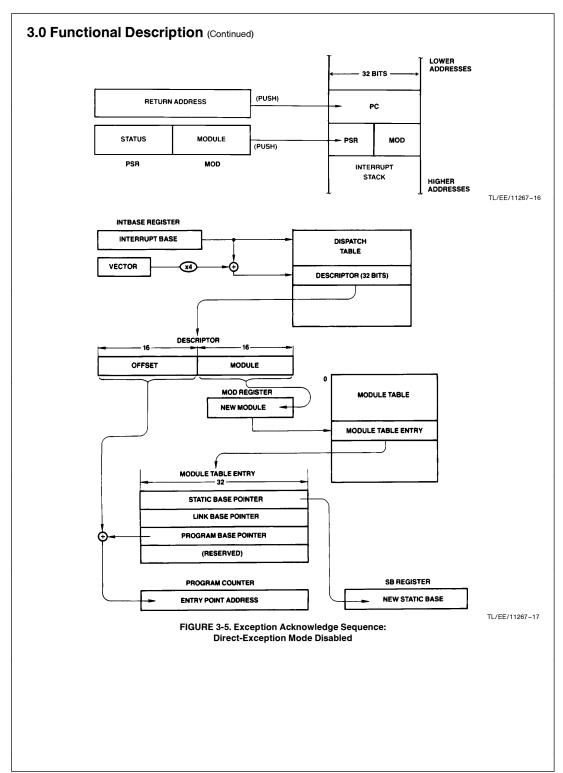

| FIGURE 3-5.  | Exception Acknowledge Sequence: Direct-Exception Mode Disabled                |

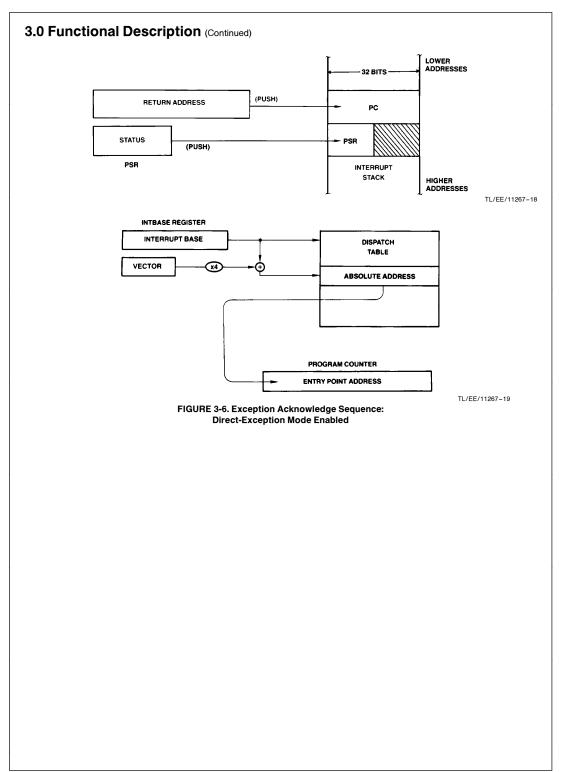

| FIGURE 3-6.  | Exception Acknowledge Sequence: Direct-Exception Mode Enabled                 |

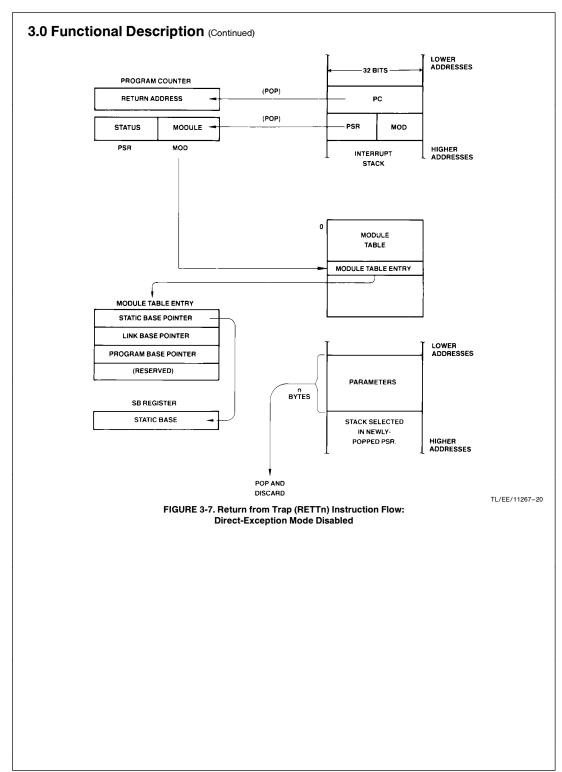

| FIGURE 3-7.  | Return from Trap (RETTn) Instruction Flow: Direct-Exception Mode Disabled     |

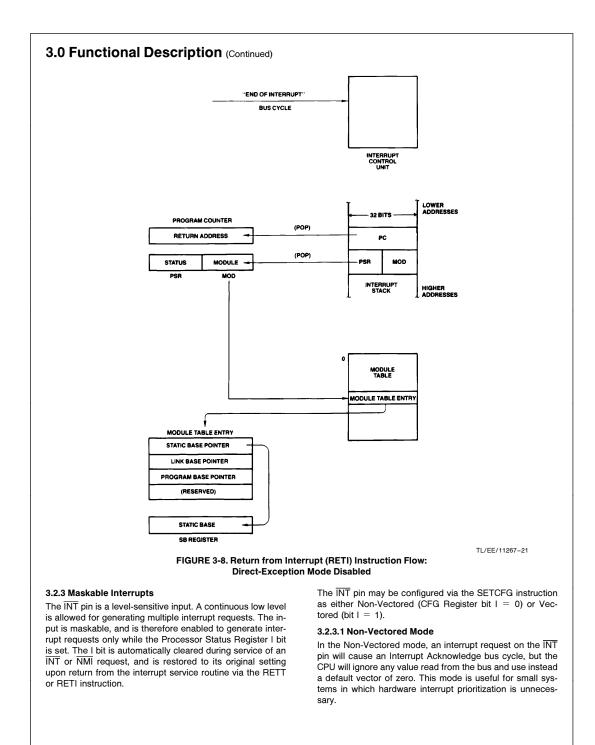

| FIGURE 3-8.  | Return from Interrupt (RETI) Instruction Flow: Direct-Exception Mode Disabled |

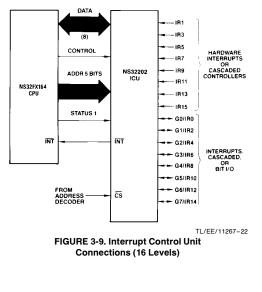

| FIGURE 3-9.  | Interrupt Control Unit Connections (16 Levels)                                |

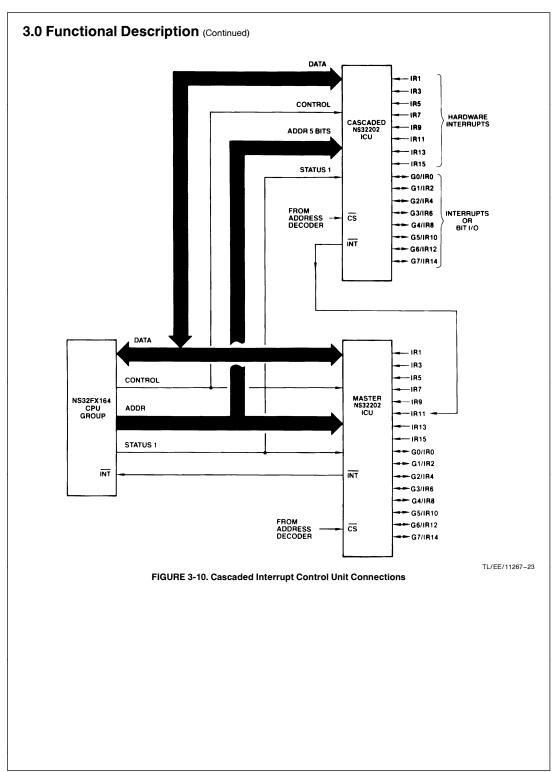

| FIGURE 3-10. | . Cascaded Interrupt Control Unit Connections                                 |

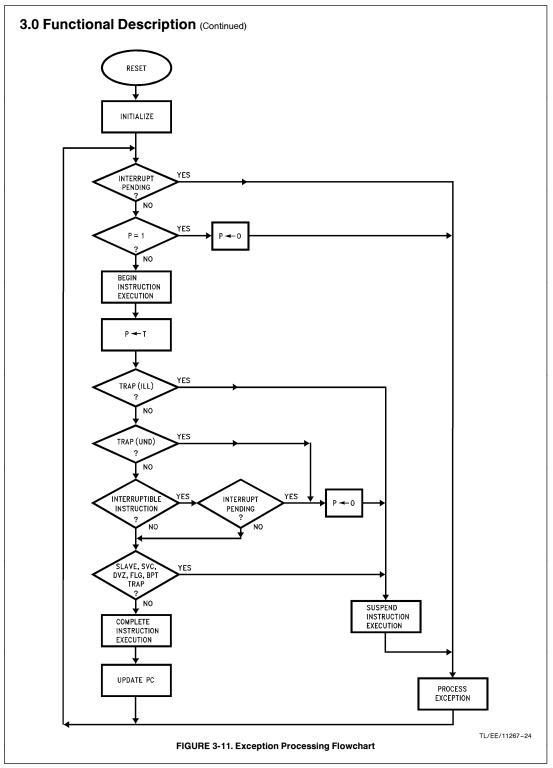

| FIGURE 3-11. | Exception Processing Flowchart                                                |

| FIGURE 3-12. | . Service Sequence                                                            |

| FIGURE 3-13. | . DSP Module Block Diagram                                                    |

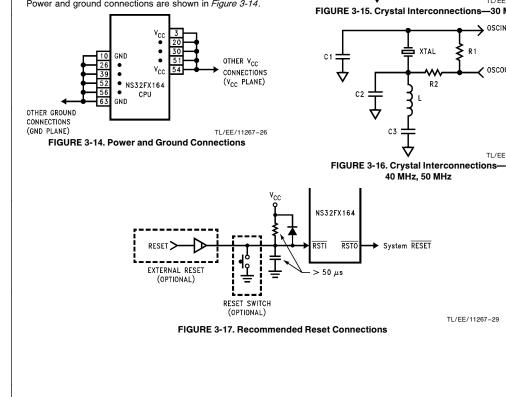

| FIGURE 3-14. | . Power and Ground Connections                                                |

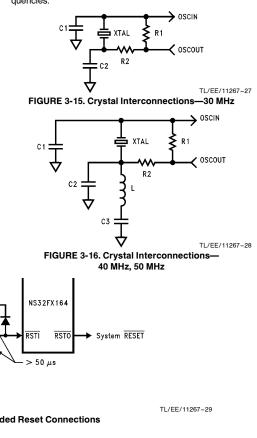

| FIGURE 3-15. | . Crystal Interconnections—30 MHz                                             |

| FIGURE 3-16. | . Crystal Interconnections—40 MHz, 50 MHz56                                   |

| FIGURE 3-17. | . Recommended Reset Connections                                               |

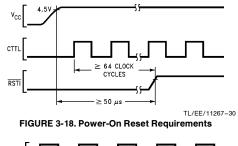

| FIGURE 3-18. | . Power-On Reset Requirements                                                 |

| FIGURE 3-19. | . General Reset Timing                                                        |

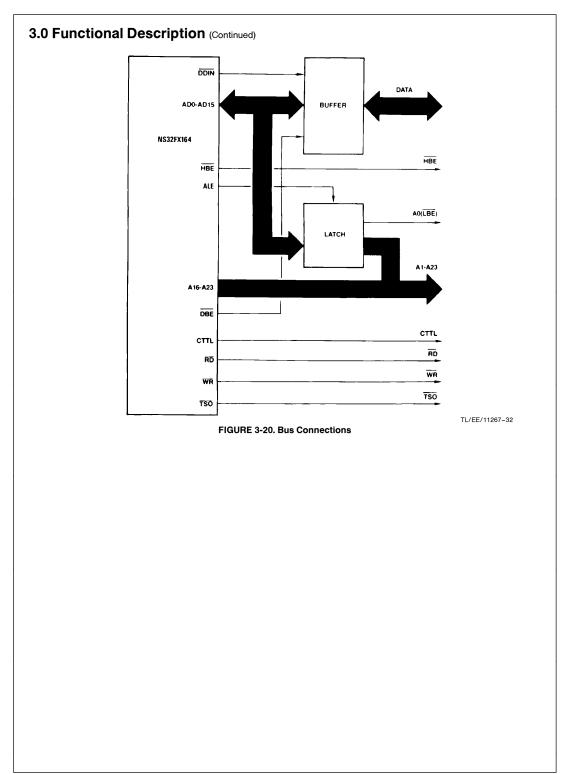

| FIGURE 3-20. | . Bus Connections                                                             |

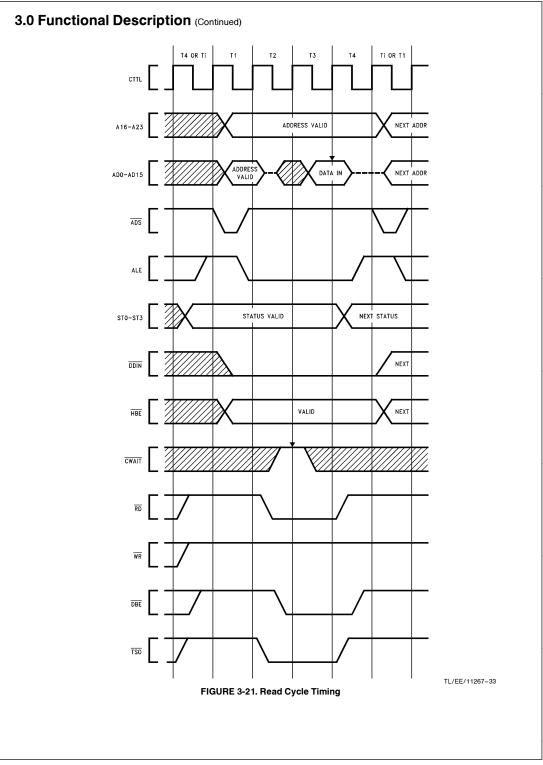

| FIGURE 3-21. | . Read Cycle Timing                                                           |

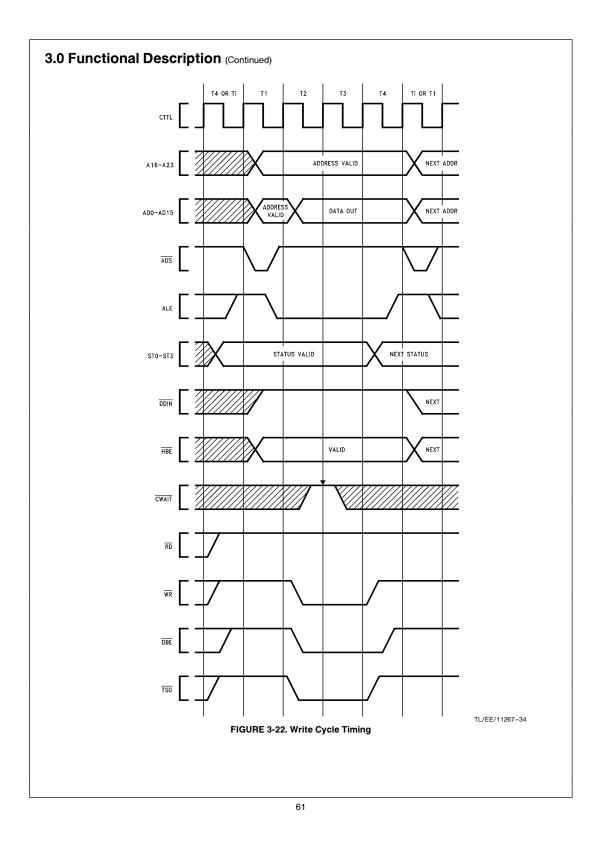

| FIGURE 3-22. | . Write Cycle Timing                                                          |

| FIGURE 3-23. | . Cycle Extension of a Read Cycle                                             |

| FIGURE 3-24. | . Special Bus Cycle Timing                                                    |

| FIGURE 3-25. | . Slave Processor Read Cycle                                                  |

| FIGURE 3-26. | . Slave Processor Write Cycle                                                 |

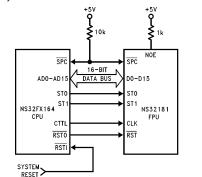

| FIGURE 3-27. | NS32FX164 and FPU Interconnections                                            |

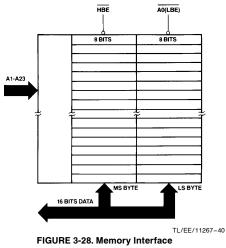

| FIGURE 3-28. | . Memory Interface                                                            |

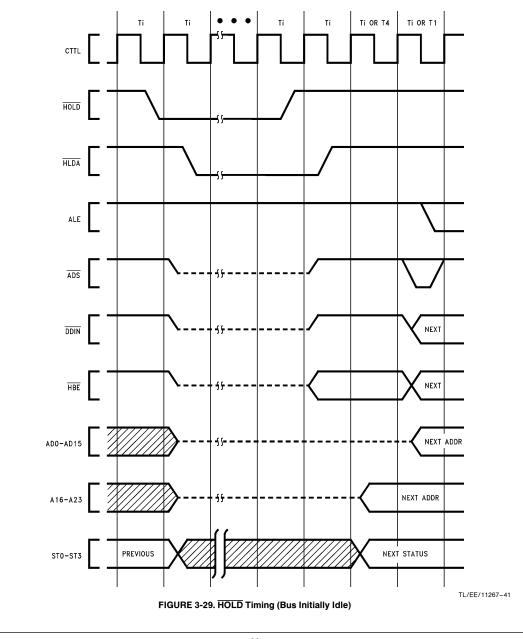

| FIGURE 3-29. | . HOLD Timing (Bus Initially Idle)                                            |

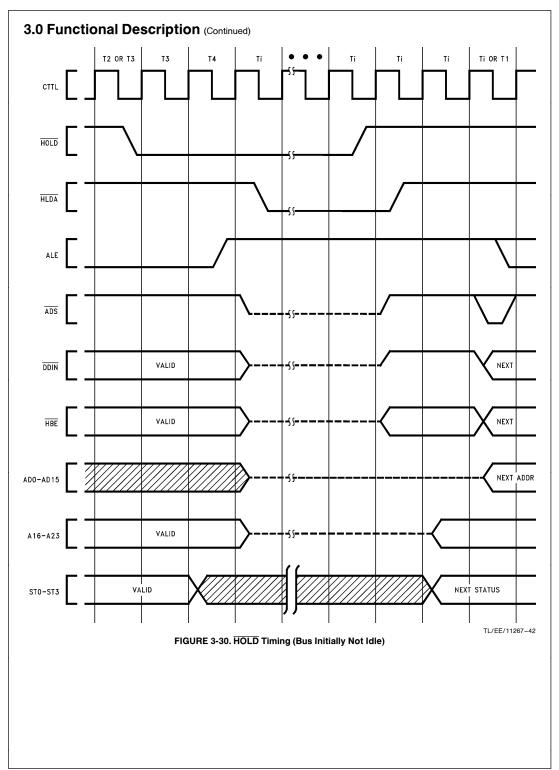

| FIGURE 3-30. | . HOLD Timing (Bus Initially Not Idle)                                        |

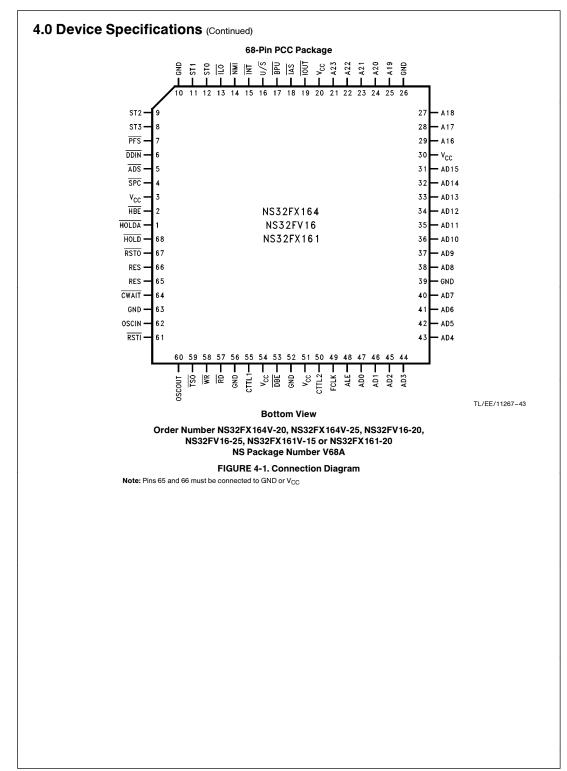

| FIGURE 4-1.  | Connection Diagram                                                            |

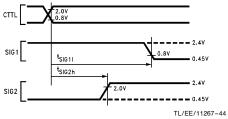

| FIGURE 4-2.  | Output Signals Specification Standard74                                       |

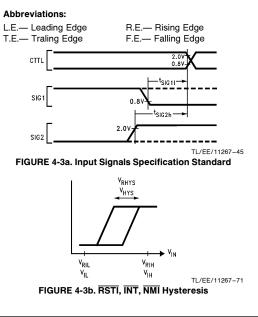

| FIGURE 4-3a. | . Input Signals Specification Standard                                        |

| FIGURE 4-3b. | . RSTI, INT, NMI Hysteresis                                                   |

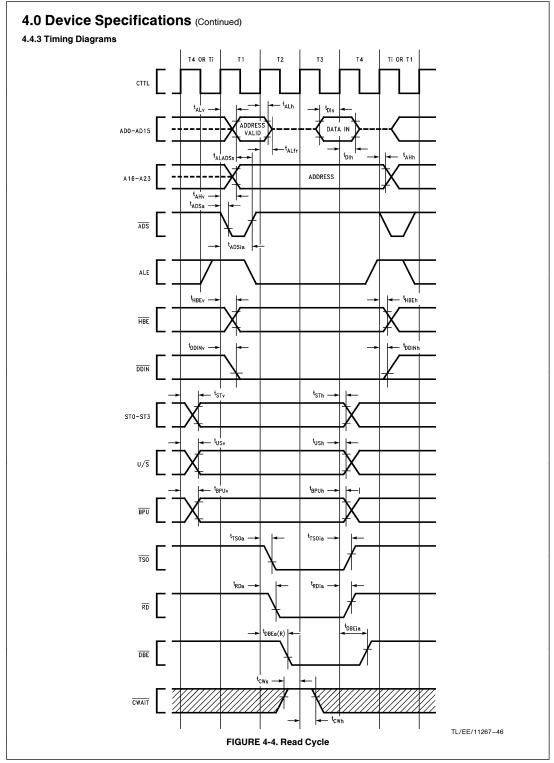

| FIGURE 4-4.  | Read Cycle                                                                    |

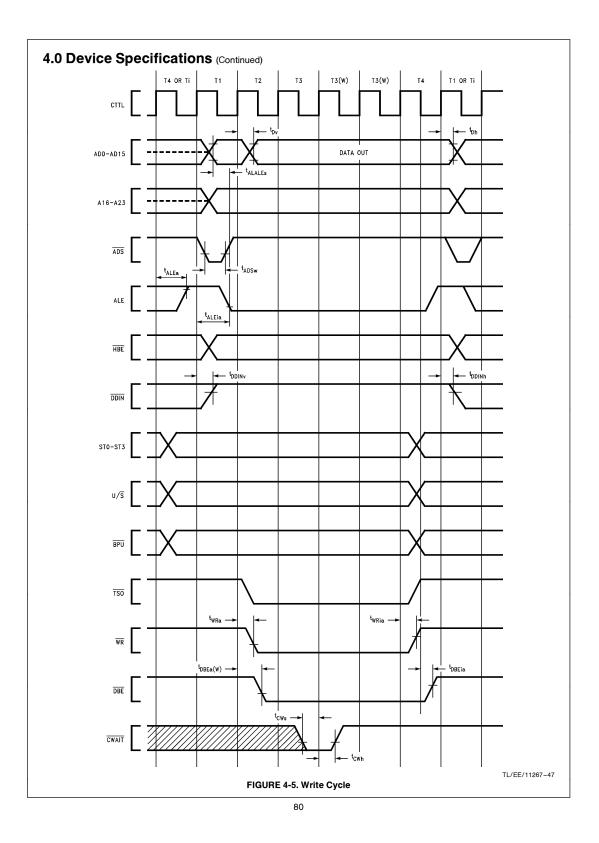

| FIGURE 4-5.  | Write Cycle                                                                   |

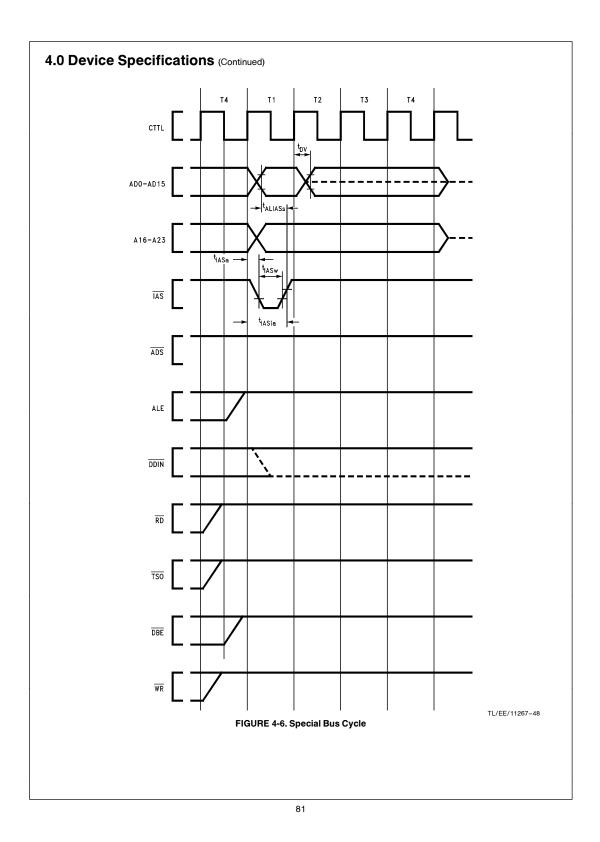

| FIGURE 4-6.  | Special Bus Cycle                                                             |

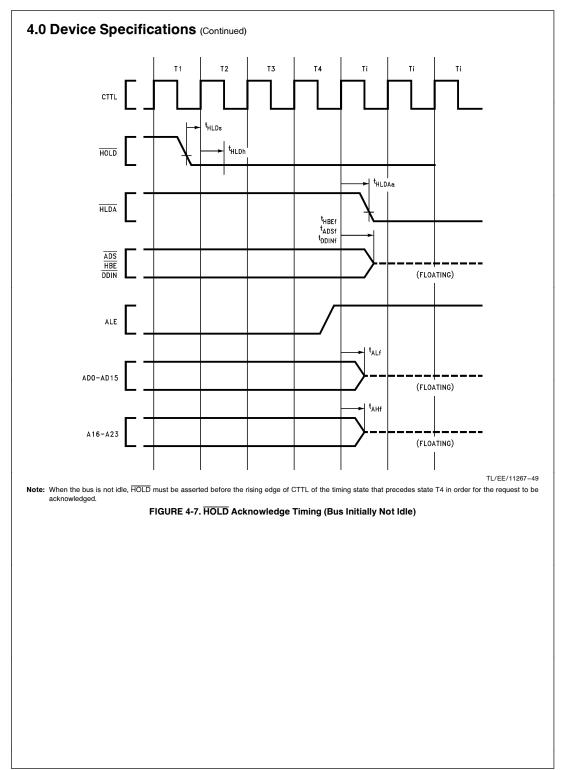

| FIGURE 4-7.  | HOLD Acknowledge Timing (Bus Initially Not Idle)                              |

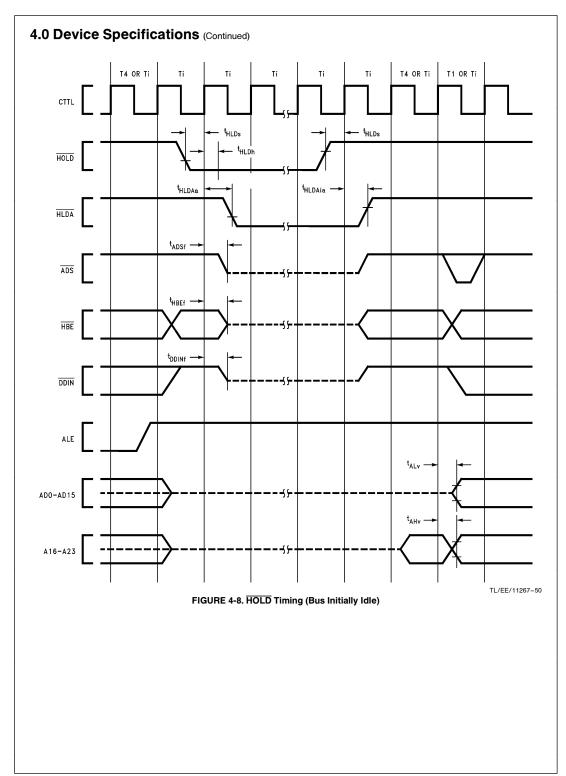

| FIGURE 4-8.  | HOLD Timing (Bus Initially Idle)                                              |

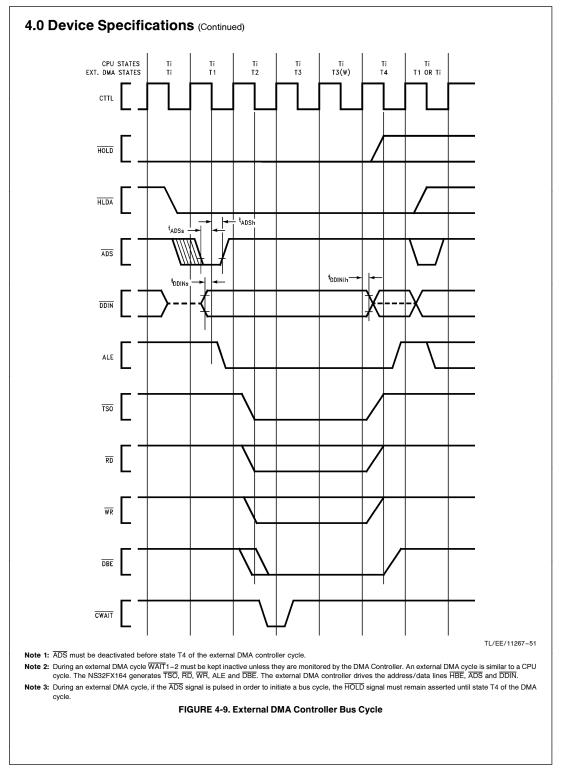

| FIGURE 4-9.  | External DMA Controller Bus Cycle                                             |

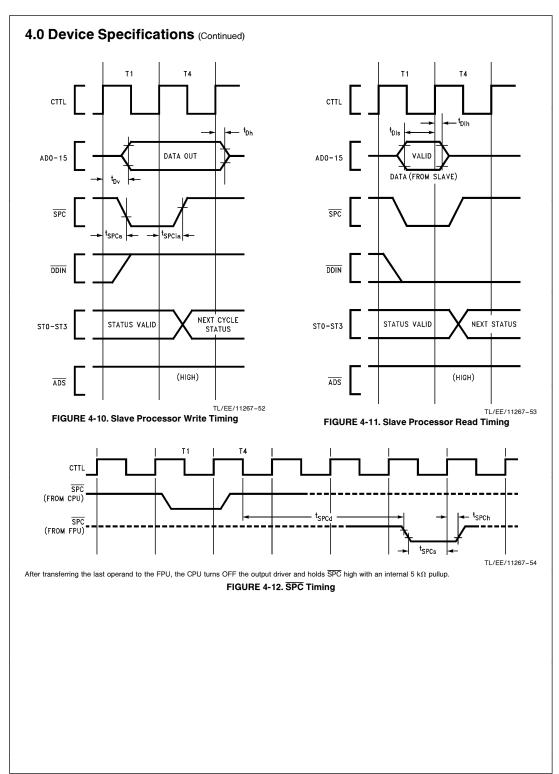

| FIGURE 4-10. | . Slave Processor Write Timing                                                |

| FIGURE 4-11. | . Slave Processor Read Timing                                                 |

| FIGURE 4-12. | . SPC Timing                                                                  |

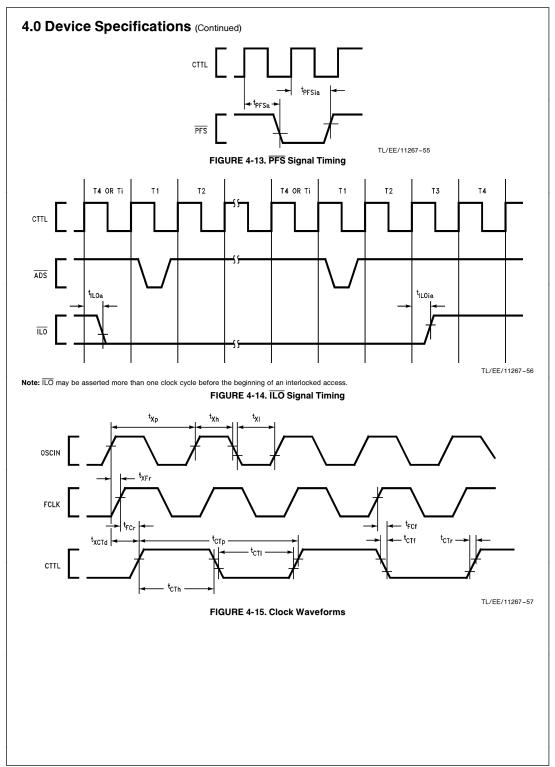

| FIGURE 4-13. | . PFS Signal Timing                                                           |

| FIGURE 4-14. | . ILO Signal Timing                                                           |

| FIGURE 4-15. | . Clock Waveforms                                                             |

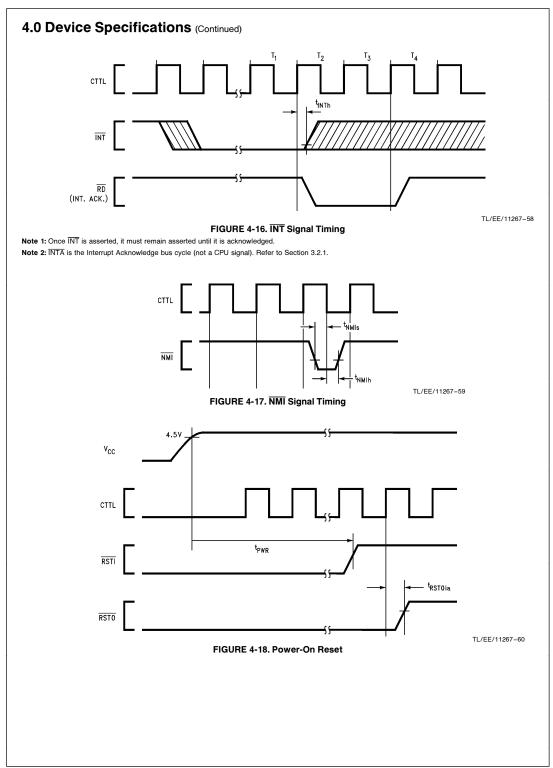

| FIGURE 4-16. | INT Signal Timing                                                             |

|              |                                                                               |

| List of Figures (Continued)                                                              |  |

|------------------------------------------------------------------------------------------|--|

| FIGURE 4-17. NMI Signal Timing                                                           |  |

| FIGURE 4-18. Power-On Reset                                                              |  |

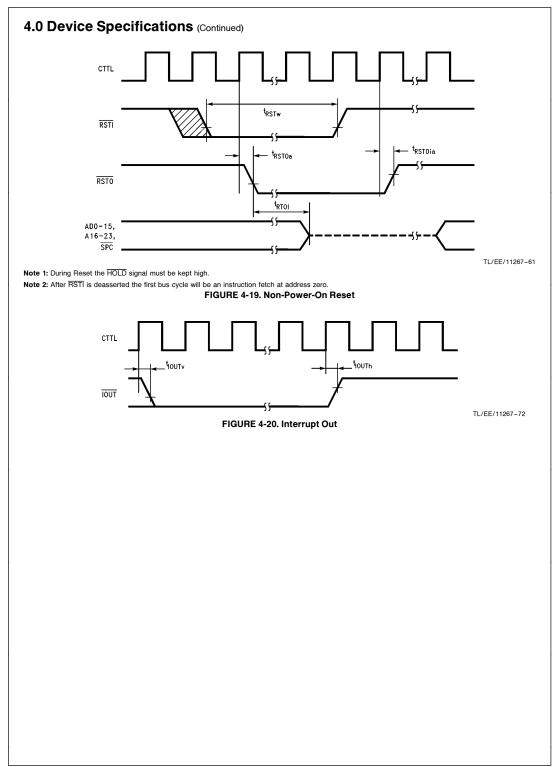

| FIGURE 4-19. Non-Power-On Reset                                                          |  |

| FIGURE 4-20. Interrupt Out                                                               |  |

| List of Tables                                                                           |  |

| TABLE 2-1. NS32FX164 Addressing Modes    15                                              |  |

| TABLE 2-2. NS32FX164 Instruction Set Summary    16                                       |  |

| TABLE 2-3. 'op' and 'i' Field Encodings       23                                         |  |

| TABLE 3-1.         Floating-Point Instruction Protocols         28                       |  |

| TABLE 3-2. Summary of Exception Processing                                               |  |

| TABLE 3-3.         External Oscillator Specifications Crystal Characteristics         57 |  |

| TABLE 3-4. Interrupt Sequences                                                           |  |

| TABLE 3-5. Bus Cycle Categories                                                          |  |

| TABLE 3-6. Data Access Sequences   68                                                    |  |

| TABLE B-1. Basic Instructions                                                            |  |

| TABLE B-2. Floating-Point Instructions: CPU Portion                                      |  |

| TABLE B-3. Average Instruction Execution Times with No Wait-States                       |  |

| TABLE B-4. Average Instruction Execution Times with Wait-States         100              |  |

## **1.0 Product Introduction**

The NS32FX164 is a high speed CMOS microprocessor in the Series 32000/EP family.

It includes two main execution units: the NS32CG16 compatible CPU core and the DSP Module. The CPU core is designed for general purpose computations and system control functions. The DSP Module is tuned to perform the DSP primitives needed in Voice Band Modems. The NS32FX164 also incorporates a 4K-byte RAM Array as a shared resource for both the CPU core and the DSP Module (2K-byte in the NS32FV16 and the NS32FX161).

The NS32FX164 is software-compatible with all other CPUs in the family.

The device incorporates all of the Series 32000 advanced architectural features, with the exception of the virtual memory capability.

Brief descriptions of the NS32FX164 features that are shared with other members of the family are provided below:

**Powerful Addressing Modes.** Nine addressing modes available to all instructions are included to access data structures efficiently.

**Data Types.** The architecture provides for numerous data types, such as byte, word, doubleword, and BCD, which may be arranged into a wide variety of data structures.

Symmetric Instruction Set. While avoiding special case instructions that compilers can't use, the Series 32000 family incorporates powerful instructions for control operations, such as array indexing and external procedure calls, which save considerable space and time for compiled code.

**Memory-to-Memory Operations.** The Series 32000 CPUs represent two-address machines. This means that each operand can be referenced by any one of the addressing modes provided.

This powerful memory-to-memory architecture permits memory locations to be treated as registers for all useful operations. This is important for temporary operands as well as for context switching.

Large, Uniform Addressing. The NS32FX164 has 24-bit address pointers that can address up to 16 megabytes without any segmentation; this addressing scheme provides flexible memory management without add-on expense.

**Modular Software Support.** Any software package for the Series 32000 architecture can be developed independent of all other packages, without regard to individual addressing. In addition, ROM code is totally relocatable and easy to access, which allows a significant reduction in hardware and software cost.

**Software Processor Concept.** The Series 32000 architecture allows future expansions of the instruction set that can be executed by special slave processors, acting as exten-

sions to the CPU. This concept of slave processors is unique to the Series 32000 architecture. It allows software compatibility even for future components because the slave hardware is transparent to the software. With future advances in semiconductor technology, the slaves can be physically integrated on the CPU chip itself.

To summarize, the architectural features cited above provide three primary performance advantages and characteristics:

- High-Level Language Support

- · Easy Future Growth Path

- Application Flexibility

#### 1.1 NS32FX164 SPECIAL FEATURES

In addition to the above Series 32000 features, the NS32FX164 provides features that make the device extremely attractive for a wide range of applications where graphics support, low chip count, and low power consumption are required.

The most relevant of these features are the enhanced Digital Signal Processing performance which makes the chip very attractive for facsimile applications, and the graphics support capabilities, that can be used in applications such as printers, CRT terminals, and other varieties of display systems, where text and graphics are to be handled.

Graphics support is provided by eighteen instructions that allow operations such as BITBLT, data compression/expansion, fills, and line drawing, to be performed very efficiently. In addition, the device can be easily interfaced to an external BITBLT Processing Unit (BPU) for high BITBLT performance.

The NS32FX164 allows systems to be built with a relatively small amount of random logic. The bus is highly optimized to allow simple interfacing to a large variety of DRAMs and peripheral devices. All the relevant bus access signals and clock signals are generated on-chip. The cycle extension logic is also incorporated on-chip.

The device is fabricated in a low-power, high speed CMOS technology. It also includes a power-save feature that allows the clock to be slowed down under software control, thus minimizing the power consumption. This feature can be used in those applications where power saving during periods of low performance demand is highly desirable.

The power save feature, the DSP Module and the Bus Characteristics are described in the "Functional Description" section. A general overview of BITBLT operations and a description of the graphics support instructions is provided in Section 2.5. Details on all the NS32FX164 graphics instructions can be found in the NS32CG16 Printer/Display Processor Programmer's Reference Supplement.

## 1.0 Product Introduction (Continued)

Below is a summary of the instructions that are directly applicable to graphics along with their intended use.

| Instruction                                                  | Application                                                                                                                                                                                                                                                                                                                   |  |  |  |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BBAND<br>BBOR<br>BBFOR<br>BBXOR<br>BBSTOD<br>BITWT<br>EXTBLT | The BITBLT group of instructions provide a method of quickly imaging characters, creating patterns, windowing and other block oriented effects.                                                                                                                                                                               |  |  |  |

| MOVMP                                                        | Move Multiple Pattern is a very fast instruction for clearing memory and drawing patterns and lines.                                                                                                                                                                                                                          |  |  |  |

| TBITS                                                        | Test Bit String will measure the length of 1's<br>or 0's in an image, supporting many data<br>compression methods (RLL), TBITS may<br>also be used to test for boundaries of<br>images.                                                                                                                                       |  |  |  |

| SBITS                                                        | Set Bit String is a very fast instruction for<br>filling objects, outline characters and<br>drawing horizontal lines.<br>The TBITS and SBITS instructions support<br>Group 3 and Group 4 CCITT standards for<br>compression and decompression<br>algorithms.                                                                  |  |  |  |

| SBITPS                                                       | Set Bit Perpendicular String is a very fast<br>instruction for drawing vertical, horizontal<br>and 45° lines.<br>In printing applications SBITS and SBITPS<br>may be used to express portrait and<br>landscape respectively from the same<br>compressed font data. The size of the<br>character may be scaled as it is drawn. |  |  |  |

| SBIT<br>CBIT<br>TBIT<br>IBIT                                 | The Bit group of instructions enable single<br>pixels anywhere in memory to be set,<br>cleared, tested or inverted.                                                                                                                                                                                                           |  |  |  |

| INDEX                                                        | The INDEX instruction combines a multiply-<br>add sequence into a single instruction. This<br>provides a fast translation of an X-Y<br>address to a pixel relative address.                                                                                                                                                   |  |  |  |

## 2.0 Architectural Description

## 2.1 REGISTER SET

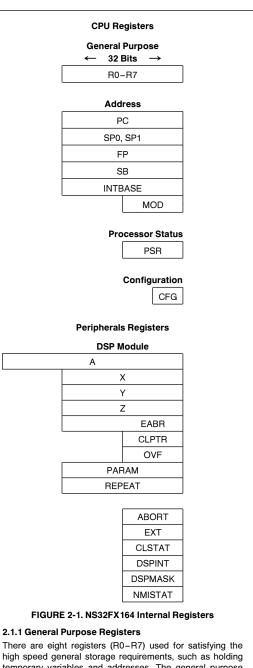

The NS32FX164 has 32 internal registers. 17 of these registers belong to the CPU portion of the device and are addressed either implicitly by specific instructions or through the register addressing mode. The other 15 control the operation of the DSP Module, and are memory mapped. Figure 2-1 shows the NS32FX164 internal registers.

high speed general storage requirements, such as holding temporary variables and addresses. The general purpose registers are free for any use by the programmer. They are 32 bits in length. If a general purpose register is specified for an operand that is 8 or 16 bits long, only the low part of the register is used; the high part is not referenced or modified.

#### 2.0 Architectural Description (Continued) 2.1.2 Address Registers

The seven address registers are used by the processor to implement specific address functions. Except for the MOD register that is 16 bits wide, all the others are 32 bits. A description of the address registers follows.

**PC—Program Counter.** The PC register is a pointer to the first byte of the instruction currently being executed. The PC is used to reference memory in the program section.

**SP0, SP1—Stack Pointers.** The SP0 register points to the lowest address of the last item stored on the INTERRUPT STACK. This stack is normally used only by the operating system. It is used primarily for storing temporary data, and holding return information for operating system subroutines and interrupt and trap service routines. The SP1 register points to the lowest address of the last item stored on the USER STACK. This stack is used by normal user programs to hold temporary data and subroutine return information.

When a reference is made to the selected Stack Pointer (see PSR S-bit), the terms "SP Register" or "SP" are used. SP refers to either SP0 or SP1, depending on the setting of the S bit in the PSR register. If the S bit in the PSR is 0, SP refers to SP0. If the S bit in the PSR is 1 then SP refers to SP1.

Stacks in the Series 32000 architecture grow downward in memory. A Push operation pre-decrements the Stack Pointer by the operand length. A Pop operation post-increments the Stack Pointer by the operand length.

**FP—Frame Pointer.** The FP register is used by a procedure to access parameters and local variables on the stack. The FP register is set up on procedure entry with the ENTER instruction and restored on procedure termination with the EXIT instruction.

The frame pointer holds the address in memory occupied by the old contents of the frame pointer.

SB—Static Base. The SB register points to the global variables of a software module. This register is used to support relocatable global variables for software modules. The SB register holds the lowest address in memory occupied by the global variables of a module.

**INTBASE—Interrupt Base.** The INTBASE register holds the address of the dispatch table for interrupts and traps (Section 3.2.1).

**MOD—Module.** The MOD register holds the address of the module descriptor of the currently executing software module. The MOD register is 16 bits long, therefore the module table must be contained within the first 64 kbytes of memory.

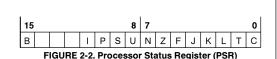

### 2.1.3 Processor Status Register

The Processor Status Register (PSR) holds status information for the microprocessor.

The PSR is sixteen bits long, divided into two eight-bit halves. The low order eight bits are accessible to all programs, but the high order eight bits are accessible only to programs executing in Supervisor Mode.

- C The C bit indicates that a carry or borrow occurred after an addition or subtraction instruction. It can be used with the ADDC and SUBC instructions to perform multipleprecision integer arithmetic calculations. It may have a setting of 0 (no carry or borrow) or 1 (carry or borrow).

- T The T bit causes program tracing. If this bit is set to 1, a TRC trap is executed after every instruction (Section 3.3.1).

- L The L bit is altered by comparison instructions. In a comparison instruction the L bit is set to "1" if the second operand is less than the first operand, when both operands are interpreted as unsigned integers. Otherwise, it is set to "0". In Floating-Point comparisons, this bit is always cleared.

- K Reserved for use by the CPU.

- J Reserved for use by the CPU.

- F The F bit is a general condition flag, which is altered by many instructions (e.g., integer arithmetic instructions use it to indicate overflow).

- Z The Z bit is altered by comparison instructions. In a comparison instruction the Z bit is set to "1" if the second operand is equal to the first operand; otherwise it is set to "0".

- N The N bit is altered by comparison instructions. In a comparison instruction the N bit is set to "1" if the second operand is less than the first operand, when both operands are interpreted as signed integers. Otherwise, it is set to "0".

- U If the U bit is "1" no privileged instructions may be executed. If the U bit is "0" then all instructions may be executed. When U=0 the processor is said to be in Supervisor Mode; when U=1 the processor is said to be in User Mode. A User Mode program is restricted from executing certain instructions and accessing certain registers which could interfere with the operating system. For example, a User Mode program is prevented from changing the setting of the flag used to indicate its own privilege mode. A Supervisor Mode program is assumed to be a trusted part of the operating system, hence it has no such restrictions.

- S The S bit specifies whether the SP0 register or SP1 register is used as the Stack Pointer. The bit is automatically cleared on interrupts and traps. It may have a setting of 0 (use the SP0 register) or 1 (use the SP1 register).

- The P bit prevents a TRC trap from occurring more than once for an instruction (Section 3.3.1). It may have a setting of 0 (no trace pending) or 1 (trace pending).

- I If I=1, then all interrupts will be accepted. If I=0, only the NMI interrupt is accepted. Trap enables are not affected by this bit.

- B Reserved for use by the CPU. This bit is set to 1 during the execution of the EXTBLT instruction and causes the BPU signal to become active. Upon reset, B is set to zero and the BPU signal is set high.

- Note 1: When an interrupt is acknowledged, the B, I, P, S and U bits are set to zero and the BPU signal is set high. A return from interrupt will restore the original values from the copy of the PSR register saved in the interrupt stack.

- Note 2: If BITBLT (BB) or EXTBLT instructions are executed in an interrupt routine, the PSR bits J and K must be cleared first.

#### 2.1.4 Configuration Register

The Configuration Register (CFG) is 32 bits wide, of which 5 bits are implemented. The implemented bits enable various operating modes for the CPU, including vectoring of interrupts, execution of floating-point instructions, processing of exceptions and selection of clock scaling factor. The CFG is programmed by the SETCFG instruction. The format of CFG is shown in *Figure 2-3*. The various control bits are described below.

| 31       | 8  | 7             |    |   |   | 0 |

|----------|----|---------------|----|---|---|---|

| Reserved | DE | Res           | С  | М | F | Ι |

|          |    | tion Deviator | 10 |   |   |   |

FIGURE 2-3. Configuration Register (CFG)

- I Interrupt vectoring. This bit controls whether maskable interrupts are handled in nonvectored (I=0) or vectored (I=1) mode. Refer to Section 3.2.3 for more information.

- F Floating-point instruction set. This bit indicates whether a floating-point unit (FPU) is present to execute floating-point instructions. If this bit is 0 when the CPU executes a floating-point instruction, a Trap (UND) occurs. If this bit is 1, then the CPU transfers the instruction and any necessary operands to the FPU using the slave-processor protocol described in Section 3.1.3.1.

- M Clock scaling. This bit is used in conjunction with the C-bit to select the clock scaling factor.

- C Clock scaling. Same as the M-bit above. Refer to Section 3.5.3 on "Power Save Mode" for details.

- **DE** Direct-Exception mode enable. This bit enables the Direct-Exception mode for processing exceptions. When this mode is selected, the CPU response time to interrupts and other exceptions is significantly improved. Refer to Section 3.2 for more information.

#### 2.1.5 DSP Module Registers

The DSP Module (DSPM) contains 15 memory-mapped registers. All the registers, except OVF, CLSTAT, ABORT, DSPINT and NMISTAT, are readable and writable. OVF, CLSTAT, DSPINT and NMISTAT are read-only. ABORT is write-only.

The DSPM registers are divided into two groups, according to their function. PARAM, OVF, X, Y, Z, A, REPEAT, CLPTR and EABR are called DSPM dedicated registers. CLSTAT, ABORT, DSPINT, DSPMASK, EXT and NMISTAT are called CPU core interface registers.

Accesses to these registers must be aligned; word and double-word accesses must occur on word and double-word address boundaries respectively. Failing to do so will cause unpredictable results. *Figure 2-4* shows the address map of the DSP Module registers.

| Register | Register |

|----------|----------|

| Name     | Address  |

| PARAM    | FFFF8000 |

| OVF      | FFFF8004 |

| Х        | FFFF8008 |

| Y        | FFFF800C |

| Z        | FFFF8010 |

| А        | FFFF8014 |

| REPEAT   | FFFF8018 |

| CLPTR    | FFFF8020 |

| EABR     | FFFF8024 |

| CLSTAT   | FFFF9000 |

| ABORT    | FFFF9004 |

| DSPINT   | FFFF9008 |

| DSPMASK  | FFFF900C |

| EXT      | FFFF9010 |

| NMISTAT  | FFFF9014 |

#### FIGURE 2-4. DSP Module Registers Address Map A—Accumulator

The format of the accumulator is shown in Figure 2-5.

33 0 33 0

| Imaginary | Real |

|-----------|------|

#### FIGURE 2-5. Accumulator Format

The A register is a complex accumulator. It has two 34-bit fields: a real part, and an imaginary part. Bits 15 through 30 of the real and the imaginary parts of the accumulator can be read or written by the core in one double-word access. Bits 15 through 30 of the real part are mapped to the operand's bits 0 through 15, and bits 15 through 30 of the imaginary part are mapped to the operand's bits 16 through 31. The accumulator can also be read and written by the command-list execution unit using the SA, SEA, LA and LEA instructions (See Section 3.4 for more information).

Note that when a value is stored in the accumulator by the core, the value of PARAM.RND bit is copied into bit position 14 of both real and imaginary parts of the accumulator. This technique allows rounding of the accumulator's value in the following DSPM instructions (See Section 3.4.5.3 for more information on rounding).

When the Accumulator is loaded either by the core or by the LA or LEA instructions, bits 31–33 of the real and the imaginary accumulators are loaded with the values of bit 30 of the real and the imaginary parts respectively.

When the Accumulator is loaded either by the core or by the LA instruction, bits 0-13 of the real and the imaginary accumulators are loaded with zeros.

#### X, Y, Z-Vector Pointers

The format of X, Y, and Z registers is shown in Figure 2-6.

| 31 16                                | 15 8     | 7 4         | 3 0       |  |  |  |

|--------------------------------------|----------|-------------|-----------|--|--|--|

| ADDRESS                              | Reserved | WRAP-AROUND | INCREMENT |  |  |  |

| FIGURE 2-6. X, Y, Z Registers Format |          |             |           |  |  |  |

The X, Y, and Z registers are used for addressing up to three vector operands. They are 32-bit registers, with three fields: ADDRESS, INCREMENT, and WRAP-AROUND. The value in the ADDRESS field specifies the address of a word in the on-chip memory. This field has 16 bits, and can address up to 64 Kwords of internal memory. The ADDRESS fields are initialized with the vector operands' start-addresses by commands in the command list. At the beginning of each vector operation, the contents of the ADDRESS field are copied to incrementors. Increments can be used by vector instructions to step through the corresponding vector operands while executing the appropriate calculations. There is an address wrap-around for those vector instructions that require some of their operands to be located in cyclic buffers. The allowed values for the increment field are 0 through 15. The actual increment will be 2increment words. The allowed values for the WRAP-AROUND field are 0 through 15. The actual wrap-around will be 2WRAP-AROUND words. The WRAP-AROUND must be greater or equal to the INCREMENT.

The X, Y, and Z registers can be read and written by the core. These registers can be read and written by the command-list execution unit, as well as by the core, when using SX, SXL, SXH, SY, SZ, LX, LY and LZ instructions.

#### EABR—External Address Base Register

The format of the external address base register is shown in *Figure 2-7*.

| 31 1            | 7  | 16              | 0 |

|-----------------|----|-----------------|---|

| ADDRESS         |    | 0               |   |

| FIGURE 2-7. EAI | BF | Register Format |   |

The EABR register is used together with a 16-bit address field to form a 32-bit external address. External addresses are specified as the sum of the value in EABR and two times the value of the 16-bit address pointed by registers X, Y or Z. The only value allowed to be written into bits 0 through 16 of EABR is "0". The EABR register can be read and written by the core. It can also be written by the command-list execution unit by using the LEABR instruction.

EABR can hold any value except for FFFE0000. Accessing external memory with an FFFE0000 in the EABR will cause unpredictable results.

#### **CLPTR—Command List Pointer**

The CLPTR is a 16-bit register that holds the address of the current command in the internal RAM. Writing into the CLPTR causes the DSPM command-list execution unit to begin executing commands, starting from the address in CLPTR. The CLPTR can be read and written by the core while the command-list execution is idle.

Whenever the DSPM command-list execution unit reads a command from the DSPM RAM, the value of CLPTR is updated to contain the address of the next command to be executed. This implies, for example, that if the last command in a list is in address N, the CLPTR will hold a value of N  $\,+\,$  1 following the end of command list execution.

#### **OVF**—Overflow Register

The format of the overflow register is shown in *Figure 2-8*.  $\begin{vmatrix} 15 & 2 & 1 \\ 15 & 2 & 1 \\ \end{vmatrix}$

FIGURE 2-8. OVF Register Format

The OVF register holds the current status of the DSPM arithmetic unit. It has two fields: OVF and SAT. The OVF bit is set to "1" whenever an overflow is detected in the DSPM 34-bit ALU (e.g., bits 32 and 33 of the ALU are not equal). No overflow detection is provided for integers. The SAT bit is set to "1" whenever a value read from the accumulator cannot be represented within the limits of its data type (e.g., 16 bits for real and integer, and 31 bits for extended real). In this case the value read from the accumulator will either be the maximum allowed value or the minimal allowed value for this data type depending on the sign of the accumulator value. Note that in some cases when the OVF is set, the SAT will not be set. The reason is that if an OVF occurred, the value in the accumulator can no longer be used for proper SAT detection. Upon reset, and whenever the ABORT register is written, the non reserved bits of the OVF register is cleared to "0".

The OVF is a read only register. It can be read by the core. It can also be read by the command-list execution unit using the SOVF instruction. Reading the OVF by either the core or the command-list execution unit clears it to "0".

#### PARAM—Vector Parameter Register

|                                  |     | 24 19 |     |     |     |        | 0 |

|----------------------------------|-----|-------|-----|-----|-----|--------|---|

| Reserved                         | RND | OP    | SUB | CLR | COJ | LENGTH |   |

| FIGURE 2-9 PARAM Register Format |     |       |     |     |     |        |   |

FIGURE 2-9. PARAM Register Format

The PARAM register is used to specify the number of iterations and special options for the various instructions. The options are: RND, OP, SUB, CLR, and COJ. The effect of each of the bits of the PARAM register is specified in Section 3.4.

The PARAM register can be read and written by the core. It can also be written by the command-list execution unit, by using the LPARAM instruction. The value written into PAR-AM.LENGTH must be greater then 0.

The value of PARAM.LENGTH is not changed during command-list execution, unless it is written into using the LPARAM instruction.

## REPEAT—Command-List Repeat Register

| The format of the repeat reg | ster is shown in <i>Figure 2-10</i> . |

|------------------------------|---------------------------------------|

|                              |                                       |

| 31 16 | 15 0              |

|-------|-------------------|

| COUNT | TARGET            |

|       | T Pagistor Format |

FIGURE 2-10. REPEAT Register Format

The REPEAT register is used, together with appropriate commands, to implement loops and branches in the command list. The count is used to specify the number of times a loop in the command list is to be repeated. The target is used to specify a jump address within the command list.

The REPEAT register can be read and written by the core. It can also be read and written by the command-list execution unit by using SREPEAT and LREPEAT instructions respectively.

The value of REPEAT.COUNT changes during the execution of the DJNZ command.

## ABORT—Abort Register

The ABORT register is used to force execution of the command list to halt. Writing any value into this register stops execution, and clears the contents of OVF, EXT, DSPINT and DSPMASK. The ABORT register can only be written and only by the core.

OVF SAT

EXT—External Memory Reference Control Register

The format of the external memory reference control register is shown in *Figure 2-11*.

| 1 1 | 5 1      | 0    |

|-----|----------|------|

|     | Reserved | HOLD |

FIGURE 2-11. EXT Register Format

The EXT register controls external references. The command-list execution unit checks the value of EXT.HOLD before each external memory reference. When EXT.HOLD is "0", external memory references are allowed. When EXT.HOLD is "1", and external memory references are requested, the execution of the command list will stop until EXT.HOLD is "0". Upon reset, and whenever the ABORT register is written, EXT.HOLD is cleared to "0". The EXT register can be read or written by the core.

#### CLSTAT—Command-List Execution Status Register

The format of the command-list execution status register is shown in *Figure 2-12*.

| 15       | 1 | 0   |

|----------|---|-----|

| Reserved |   | RUN |

#### FIGURE 2-12. CLSTAT Register Format

The CLSTAT register displays the current status of the execution of the command list. When the command-list execution is idle, CLSTAT.RUN is "0", and when it is active, CLSTAT.RUN is "1". Upon reset, the CLSTAT register is cleared to "0". It can only be read, and only by the core. DSPINT, DSPMASK, NMISTAT—Interrupt Control Registers

The format of DSPINT and DSPMASK is shown in *Figure* 2-13.

| 15 1     | 0    |

|----------|------|

| Reserved | HALT |

FIGURE 2-13. DSPINT and DSPMASK Register Format The DSPINT register holds the current status of interrupt requests. Whenever execution of the command list is stopped, the DSPINT.HALT bit is set to "1". The DSPINT is a read only register. It is cleared to "0" whenever it is read, whenever the ABORT register is written, and upon reset.

The DSPMASK register is used to mask the DSPINT. HALT flag. An interrupt request is transferred to the interrupt logic of the  $\overline{IOUT}$  output pin whenever the DSPINT.HALT bit is set to "1", and the DSPMASK.HALT bit is unmasked (set to "1"). See Section 4.0 for the functionality of  $\overline{IOUT}$ . DSPMASK can be read and written by the core. Upon reset, and whenever the ABORT register is written, all the bits in DSPMASK are cleared to "0".

The format of the NMISTAT register is shown in Figure 2-14.

| 15       | 3 | 2   | 1   | 0   |

|----------|---|-----|-----|-----|

| Reserved |   | ERR | UND | EXT |

FIGURE 2-14. NMISTAT Register Format

The NMISTAT holds the status of the current pending Non-Maskable Interrupt (NMI) requests.

Whenever the core attempts to access the DSPM address space while the CLSTAT.RUN bit is "1" (except for accesses to the CLSTAT, EXT, DSPINT, NMISTAT, DSPMASK, and ABORT registers) NMISTAT.ERR is set to "1". Whenever there is an attempt to execute a DBPT instruction, or a reserved DSPM instruction (Section 3.4), the NMISTAT.UND bit is set to "1".

When a high to low transition is detected on the  $\overline{\text{NMI}}$  input pin, NMISTAT.EXT bit is set to "1".

When one of the bits in NMISTAT is set to "1", an NMI request to the core is issued.

The NMISTAT register is cleared to 0 upon reset, and each time its contents are read.

When one of the bits in NMISTAT is set to 1, an NMI occurs. The NMI handler can read the NMISTAT register to determine the source of the interrupt. Note that since NMIs may be nested, it is possible that a second NMI handler (invoked while the previous handler has not yet exited) will read and handle more than one set bit in NMISTAT. Since the read operation clears the register, the interrupted handler may find that no bits are set.

#### 2.2 MEMORY ORGANIZATION

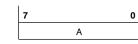

The main memory of the NS32FX164 is a uniform linear address space. Memory locations are numbered sequentially starting at zero and ending at  $2^{24} - 1$ . The number specifying a memory location is called an address. The contents of each memory location is a byte consisting of eight bits. Unless otherwise noted, diagrams in this document show data stored in memory with the lowest address on the right and the highest address on the left. Also, when data is shown vertically, the lowest address is at the top of a diagram and the highest address at the bottom of the diagram. When bits are numbered in a diagram, the least significant bit is given the number zero, and is shown at the right of the diagram. Bits are numbered in increasing significance and toward the left.

Byte at Address A

Two contiguous bytes are called a word. Except where noted, the least significant byte of a word is stored at the lower address, and the most significant byte of the word is stored at the next higher address. In memory, the address of a word is the address of its least significant byte, and a word may start at any address.

| 15 | 8   | 7 0 |

|----|-----|-----|

|    | A+1 | А   |

|    | MSB | LSB |

Word at Address A

Two contiguous words are called a double-word. Except where noted, the least significant word of a double-word is stored at the lowest address and the most significant word of the double-word is stored at the address two higher. In memory, the address of a double-word is the address of its least significant byte, and a double-word may start at any address.

Although memory is addressed as bytes, it is actually organized as words. Therefore, words and double-words that are aligned to start at even addresses (multiples of two) are accessed more quickly than words and double-words that are not so aligned.

#### 2.2.1 Address Mapping

The NS32FX164 supports the use of memory-mapped peripheral devices and coprocessors. Such memory-mapped devices can be located at arbitrary locations within the 16-Mbyte address range available externally.

Addresses marked as Reserved in Figure 2-15 are not available in the present implementation of the NS32FX164, and should not be used. The top 8-Mbyte block is reserved by National Semiconductor Corporation, and only a few locations within this block are presently used to access the on-chip RAM array and DSP Module registers. *Figure 2-15* shows the NS32FX164 address mapping.

| Start Address<br>(HEX) |                               |

|------------------------|-------------------------------|

| 00000000               | Memory and I/O                |

| 00FFFE00               | Interrupt Control             |

| 0100000                | Reserved                      |

| FFFE0000               | DSPM Internal RAM             |

| FFFE1000               | Reserved                      |

| FFFF8000               | DSPM Dedicated Registers      |

| FFFF8028               | Reserved                      |

| FFFF9000               | DSPM Control/Status Registers |

| FFFF9014               | Reserved                      |

| FIGURE 2-15.           | NS32FX164 Address Mapping     |

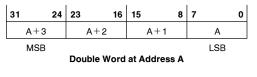

## 2.3 MODULAR SOFTWARE SUPPORT

The NS32FX164 provides special support for software modules and modular programs.

Each module in a NS32FX164 software environment consists of three components:

1. Program Code Segment.

This segment contains the module's code and constant data.

2. Static Data Segment.

3. Link Table.

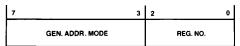

instruction. The Basic Instruction is one to three bytes long and contains the Opcode and up to two 5-bit General Addressing Mode ("Gen") fields. Following the Basic Instruction field is a set of optional extensions, which may appear depending on the instruction and the addressing modes selected.

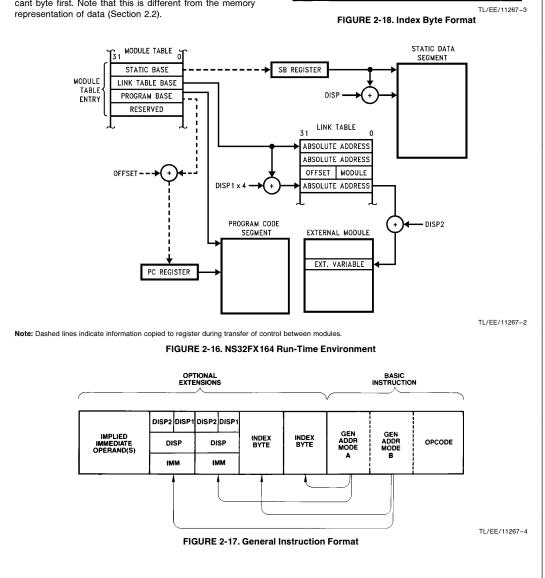

Scaled Index. In this case, the Gen field specifies only the Scale Factor (1, 2, 4 or 8), and the Index Byte specifies which General Purpose Register to use as the index, and which addressing mode calculation to perform before indexing

12

Normally, the linker program specifies the locations of the three components. The Static Data and Link Table typically reside in RAM; the code component can be either in RAM or in ROM. The three components can be mapped into noncontiguous locations in memory, and each can be independently relocated. Since the Link Table contains the absolute addresses of external variables, the linker need not assign absolute memory addresses for these in the module itself; they may be assigned at load time.

To handle the transfer of control from one module to another, the NS32FX164 uses a module table in memory and two registers in the CPU.

The Module Table is located within the first 64 kbytes of memory. This table contains a Module Descriptor (also called a Module Table Entry) for each module in the address space of the program. A Module Descriptor has four 32-bit entries corresponding to each component of a module:

- · The Static Base entry contains the address of the beginning of the module's static data segment.

- The Link Table Base points to the beginning of the module's Link Table.

- The Program Base is the address of the beginning of the code and constant data for the module.

- A fourth entry is currently unused but reserved.

The MOD Register in the CPU contains the address of the Module Descriptor for the currently executing module.

The Static Base Register (SB) contains a copy of the Static Base entry in the Module Descriptor of the currently executing module, i.e., it points to the beginning of the current module's static data area.

This register is implemented in the CPU for efficiency purposes. By having a copy of the static base entry or chip, the CPU can avoid reading it from memory each time a data item in the static data segment is accessed.

In an NS32FX164 software environment modules need not be linked together prior to loading. As modules are loaded, a linking loader simply updates the Module Table and fills the Link Table entries with the appropriate values. No modification of a module's code is required. Thus, modules may be stored in read-only memory and may be added to a system independently of each other, without regard to their individual addressing. Figure 2-16 shows a typical NS32FX164 run-time environment.

#### 2.4 INSTRUCTION SET

Used to store variables and data that may be accessed by all procedures within the module. This component contains two types of entries: Absolute Addresses and Procedure Descriptors.

An Absolute Address is used in the external addressing mode, in conjunction with a displacement and the current MOD Register contents to compute the effective address of an external variable belonging to another module.

The Procedure Descriptor is used in the call external procedure (CXP) instruction to compute the address of an external procedure.

2.4.1 General Instruction Format Figure 2-17 shows the general format of a Series 32000

Index Bytes appear when either or both Gen fields specify

Following Index Bytes come any displacements (addressing constants) or immediate values associated with the selected addressing modes. Each Disp/Imm field may contain one of two displacements, or one immediate value. The size of a Displacement field is encoded within the top bits of that field, as shown in *Figure 2-19*, with the remaining bits interpreted as a signed (two's complement) value. The size of an immediate value is determined from the Opcode field. Both Displacement and Immediate fields are stored most-significant byte first. Note that this is different from the memory representation of data (Section 2.2). Some instructions require additional "implied" immediates and/or displacements, apart from those associated with addressing modes. Any such extensions appear at the end of the instruction, in the order that they appear within the list of operands in the instruction definition (Section 2.4.3).

## 2.0 Architectural Description (Continued) 2.4.2 Addressing Modes

The NS32FX164 CPU generally accesses an operand by calculating its Effective Address based on information available when the operand is to be accessed. The method to be used in performing this calculation is specified by the programmer as an "addressing mode".

Addressing modes in the NS32FX164 are designed to optimally support high-level language accesses to variables. In nearly all cases, a variable access requires only one addressing mode, within the instruction that acts upon that variable. Extraneous data movement is therefore minimized. NS32FX164 Addressing Modes fall into nine basic types:

**Register:** The operand is available in one of the eight General Purpose Registers. In certain Slave Processor instructions, an auxiliary set of eight registers may be referenced instead.

**Register Relative:** A General Purpose Register contains an address to which is added a displacement value from the instruction, yielding the Effective Address of the operand in memory.

**Memory Space:** Identical to Register Relative above, except that the register used is one of the dedicated registers PC, SP, SB or FP. These registers point to data areas generally needed by high-level languages.

**Memory Relative:** A pointer variable is found within the memory space pointed to by the SP, SB or FP register. A displacement is added to that pointer to generate the Effective Address of the operand.

**Immediate:** The operand is encoded within the instruction. This addressing mode is not allowed if the operand is to be written.

**Absolute:** The address of the operand is specified by a displacement field in the instruction.

**External:** A pointer value is read from a specified entry of the current Link Table. To this pointer value is added a displacement, yielding the Effective Address of the operand.

**Top of Stack:** The currently-selected Stack Pointer (SP0 or SP1) specifies the location of the operand. The operand is pushed or popped, depending on whether it is written or read.

Scaled Index: Although encoded as an addressing mode, Scaled Indexing is an option on any addressing mode except Immediate or another Scaled Index. It has the effect of calculating an Effective Address, then multiplying any General Purpose Register by 1, 2, 4 or 8 and adding into the total, yielding the final Effective Address of the operand.

Table 2-1 is a brief summary of the addressing modes. For a complete description of their actions, see the Series 32000 Instruction Set Reference Manual.

In addition to the general modes, Register-Indirect with auto-increment/decrement and warps or pitch are available on several of the graphics instructions.

| TABLE 2-1. NS32FX164 Addressing Modes |                           |                     |                                                                                                                              |  |  |

|---------------------------------------|---------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| ENCODING<br>Register                  | MODE                      | ASSEMBLER SYNTAX    | EFFECTIVE ADDRESS                                                                                                            |  |  |

| 00000                                 | Register 0                | R0 or F0            | None: Operand is in the specifie                                                                                             |  |  |

| 00001                                 | Register 1                | R1 or F1            | register.                                                                                                                    |  |  |

| 00010                                 | Register 2                | R2 or F2            | Tegister.                                                                                                                    |  |  |

| 00011                                 | Register 3                | R3 or F3            |                                                                                                                              |  |  |

| 00100                                 | •                         | R4 or F4            |                                                                                                                              |  |  |

|                                       | Register 4                | R5 or F5            |                                                                                                                              |  |  |

| 00101<br>00110                        | Register 5                |                     |                                                                                                                              |  |  |

|                                       | Register 6                | R6 or F6            |                                                                                                                              |  |  |

| 00111<br>De sietes Deleti             | Register 7                | R6 or F7            |                                                                                                                              |  |  |

| Register Relativ                      |                           |                     |                                                                                                                              |  |  |

| 01000                                 | Register 0 relative       | disp(R0)            | Disp + Register.                                                                                                             |  |  |

| 01001                                 | Register 1 relative       | disp(R1)            |                                                                                                                              |  |  |

| 01010                                 | Register 2 relative       | disp(R2)            |                                                                                                                              |  |  |

| 01011                                 | Register 3 relative       | disp(R3)            |                                                                                                                              |  |  |

| 01100                                 | Register 4 relative       | disp(R4)            |                                                                                                                              |  |  |

| 01101                                 | Register 5 relative       | disp(R5)            |                                                                                                                              |  |  |

| 01110                                 | Register 6 relative       | disp(R6)            |                                                                                                                              |  |  |

| 01111                                 | Register 7 relative       | disp(R7)            |                                                                                                                              |  |  |

| Memory Relativ                        | /e                        |                     |                                                                                                                              |  |  |

| 10000                                 | Frame memory relative     | disp2(disp1 (FP))   | Disp2 + Pointer; Pointer found                                                                                               |  |  |

| 10001                                 | Stack memory relative     | disp2(disp1 (SP))   | address Disp 1 + Register. "SF                                                                                               |  |  |

| 10010                                 | Static memory relative    | disp2(disp1 (SB))   | is either SP0 or SP1, as selecte in PSR.                                                                                     |  |  |

| Reserved                              |                           |                     |                                                                                                                              |  |  |

| 10011                                 | (Reserved for Future Use) |                     |                                                                                                                              |  |  |

| Immediate                             |                           |                     |                                                                                                                              |  |  |

| 10100                                 | Immediate                 | value               | None: Operand is input from<br>instruction queue.                                                                            |  |  |

| Absolute                              |                           |                     |                                                                                                                              |  |  |

| 10101                                 | Absolute                  | @disp               | Disp.                                                                                                                        |  |  |

| External                              |                           |                     |                                                                                                                              |  |  |

| 10110                                 | External                  | EXT (disp1) + disp2 | Disp2 + Pointer; Pointer is four<br>at Link Table Entry number Disp                                                          |  |  |

| Top Of Stack                          |                           |                     |                                                                                                                              |  |  |

| 10111                                 | Top of stack              | TOS                 | Top of current stack, using eithe<br>User or Interrupt Stack Pointer,<br>as selected in PSR. Automatic<br>Push/Pop included. |  |  |

| Memory Space                          |                           |                     | -                                                                                                                            |  |  |

| 11000                                 | Frame memory              | disp(FP)            | Disp + Register; "SP" is either                                                                                              |  |  |

| 11001                                 | Stack memory              | disp(SP)            | SP0 or SP1, as selected in PSR                                                                                               |  |  |

| 11010                                 | Static memory             | disp(SB)            |                                                                                                                              |  |  |

| 11011                                 | Program memory            | *+ disp             |                                                                                                                              |  |  |

| Scaled Index                          | ,<br>,                    |                     |                                                                                                                              |  |  |

| 11100                                 | Index, bytes              | mode[Rn:B]          | EA (mode) + Rn.                                                                                                              |  |  |

| 11101                                 | Index, words              | mode[Rn:W]          | EA (mode) + $2 \times Rn$ .                                                                                                  |  |  |

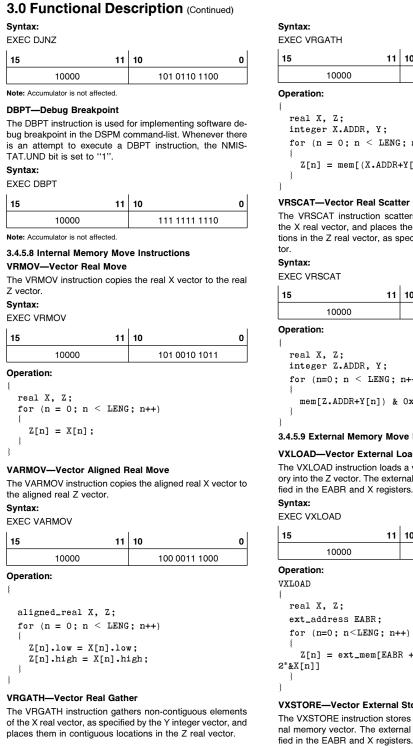

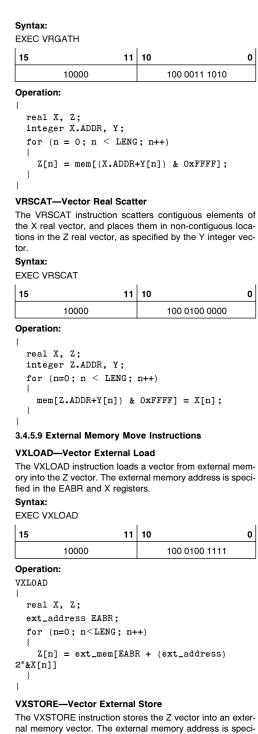

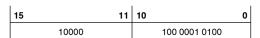

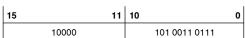

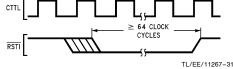

| 11110                                 | Index, double words       | mode[Rn:D]          | EA (mode) + $4 \times Rn$ .                                                                                                  |  |  |