January 1995

# LF11331/LF13331/LF11332/LF13332/LF11333/ LF13333/LF11201/LF13201/LF11202/LF13202 Quad SPST JFET Analog Switches

#### **General Description**

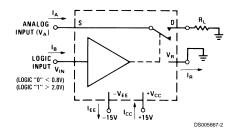

These devices are a monolithic combination of bipolar and JFET technology producing the industry's first one chip quad JFET switch. A unique circuit technique is employed to maintain a constant resistance over the analog voltage range of ±10V. The input is designed to operate from minimum TTL levels, and switch operation also ensures a break-before-make action.

These devices operate from ±15V supplies and swing a ±10V analog signal. The JFET switches are designed for applications where a dc to medium frequency analog signal needs to be controlled.

#### Features

- Analog signals are not loaded

- Constant "ON" resistance for signals up to ±10V and 100 kHz

- Pin compatible with CMOS switches with the advantage of blow out free handling

- Small signal analog signals to 50 MHz

- Break-before-make action:  $t_{OFF} < t_{ON}$

- High open switch isolation at 1.0 MHz: -50 dB

- Low leakage in "OFF" state: <1.0 nA

- TTL, DTL, RTL compatibility

- Single disable pin opens all switches in package on LF11331, LF11332, LF11333

- LF11201 is pin compatible with DG201

# **Test Circuit and Schematic Diagram**

FIGURE 1. Typical Circuit for One Switch

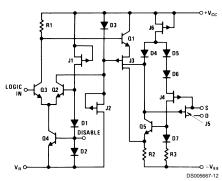

FIGURE 2. Schematic Diagram (Normally Open)

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

(Note 2)

Supply Voltage  $(V_{CC}-V_{EE})$

Reference Voltage Logic Input Voltage

Analog Voltage

Analog Current

$V_{\mathsf{EE}} \!\! \leq \!\! V_{\mathsf{R}} \!\! \leq \!\! V_{\mathsf{CC}}$

$V_R$ -4.0 $V \le V_{IN} \le V_R$ +6.0V $V_{EE} \le V_A \le V_{CC} + 6V$ ;  $V_A \le V_{EE} + 36V$

|I<sub>A</sub>|<20 mA

Power Dissipation (Note 3)

Molded DIP (N Suffix) Cavity DIP (D Suffix)

Operating Temperature Range

LF11201, 2 and LF11331, 2, 3 LF13201, 2 and LF13331, 2, 3

Storage Temperature Soldering Information

N and D Package (10 sec.)

SO Package:

Vapor Phase (60 sec.) Infrared (15 sec.)

500 mW 900 mW

> -55°C to +125°C 0°C to +70°C -65°C to +150°C

> > 300°C

215°C 220°C

# **Electrical Characteristics** (Note 4)

|                       |                                     | Conditions                                        |                      | LF11331/2/3<br>LF11201/2 |     |          | LF13331/2/3<br>LF13201/2 |     |           | Units |

|-----------------------|-------------------------------------|---------------------------------------------------|----------------------|--------------------------|-----|----------|--------------------------|-----|-----------|-------|

| Symbol                | Parameter                           |                                                   |                      |                          |     |          |                          |     |           |       |

|                       |                                     |                                                   |                      | Min                      | Тур | Max      | Min                      | Тур | Max       |       |

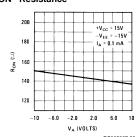

| R <sub>ON</sub>       | "ON" Resistance                     | V <sub>A</sub> =0, I <sub>D</sub> =1 mA           | T <sub>A</sub> =25°C |                          | 150 | 200      |                          | 150 | 250       | Ω     |

|                       |                                     |                                                   |                      |                          | 200 | 300      |                          | 200 | 350       | Ω     |

| R <sub>ON</sub> Match | "ON" Resistance Matching            |                                                   | T <sub>A</sub> =25°C |                          | 5   | 20       |                          | 10  | 50        | Ω     |

| $V_A$                 | Analog Range                        |                                                   |                      | ±10                      | ±11 |          | ±10                      | ±11 |           | V     |

| I <sub>S(ON) +</sub>  | Leakage Current in "ON" Condition   | Switch "ON," V <sub>S</sub> =V <sub>D</sub> =±10V | T <sub>A</sub> =25°C |                          | 0.3 | 5        |                          | 0.3 | 10        | nA    |

| I <sub>D(ON)</sub>    |                                     |                                                   |                      |                          | 3   | 100      |                          | 3   | 30        | nA    |

| I <sub>S(OFF)</sub>   | Source Current in "OFF" Condition   | Switch "OFF," V <sub>S</sub> =+10V,               | T <sub>A</sub> =25°C |                          | 0.4 | 5        |                          | 0.4 | 10        | nA    |

|                       |                                     | V <sub>D</sub> =-10V                              |                      |                          | 3   | 100      |                          | 3   | 30        | nA    |

| I <sub>D(OFF)</sub>   | Drain Current in "OFF" Condition    | Switch "OFF," V <sub>S</sub> =+10V,               | T <sub>A</sub> =25°C |                          | 0.1 | 5        |                          | 0.1 | 10        | nA    |

|                       |                                     | V <sub>D</sub> =-10V                              |                      |                          | 3   | 100      |                          | 3   | 30        | nA    |

| V <sub>INH</sub>      | Logical "1" Input Voltage           |                                                   |                      | 2.0                      |     |          | 2.0                      |     |           | V     |

| $V_{INL}$             | Logical "0" Input Voltage           |                                                   |                      |                          |     | 0.8      |                          |     | 0.8       | V     |

| I <sub>INH</sub>      | Logical "1" Input Current           | V <sub>IN</sub> =5V                               | T <sub>A</sub> =25°C |                          | 3.6 | 10<br>25 |                          | 3.6 | 40<br>100 | μA    |

| I <sub>INL</sub>      | Logical "0" Input Current           | V <sub>IN</sub> =0.8                              | T <sub>A</sub> =25°C |                          |     | 0.1      |                          |     | 0.1       | μA    |

|                       |                                     |                                                   |                      |                          |     | 1        |                          |     | 1         | μA    |

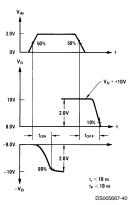

| t <sub>ON</sub>       | Delay Time "ON"                     | V <sub>S</sub> =±10V, (Figure 3)                  | T <sub>A</sub> =25°C |                          | 500 |          |                          | 500 |           | ns    |

| t <sub>OFF</sub>      | Delay Time "OFF"                    | V <sub>S</sub> =±10V, (Figure 3)                  | T <sub>A</sub> =25°C |                          | 90  |          |                          | 90  |           | ns    |

| $t_{ON}$ - $t_{OFF}$  | Break-Before-Make                   | V <sub>S</sub> =±10V, (Figure 3)                  | T <sub>A</sub> =25°C |                          | 80  |          |                          | 80  |           | ns    |

| C <sub>S(OFF)</sub>   | Source Capacitance                  | Switch "OFF," V <sub>S</sub> =±10V                | T <sub>A</sub> =25°C |                          | 4.0 |          |                          | 4.0 |           | pF    |

| $C_{D(OFF)}$          | Drain Capacitance                   | Switch "OFF," V <sub>D</sub> =±10V                | T <sub>A</sub> =25°C |                          | 3.0 |          |                          | 3.0 |           | pF    |

| C <sub>S(ON)+</sub>   | Active Source and Drain Capacitance | Switch "ON," V <sub>S</sub> =V <sub>D</sub> =0V   | T <sub>A</sub> =25°C |                          | 5.0 |          |                          | 5.0 |           | pF    |

| C <sub>D(ON)</sub>    |                                     |                                                   |                      |                          |     |          |                          |     |           |       |

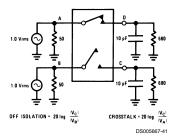

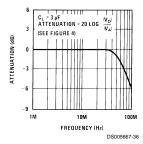

| I <sub>SO(OFF)</sub>  | "OFF" Isolation                     | (Figure 4), (Note 5)                              | T <sub>A</sub> =25°C |                          | -50 |          |                          | -50 |           | dB    |

| CT                    | Crosstalk                           | (Figure 4), (Note 5)                              | T <sub>A</sub> =25°C |                          | -65 |          |                          | -65 |           | dB    |

| SR                    | Analog Slew Rate                    | (Note 6)                                          | T <sub>A</sub> =25°C |                          | 50  |          |                          | 50  |           | V/µs  |

| I <sub>DIS</sub>      | Disable Current                     | (Figure 5), (Note 7)                              | T <sub>A</sub> =25°C |                          | 0.4 | 1.0      |                          | 0.6 | 1.5       | mA    |

|                       |                                     |                                                   |                      |                          | 0.6 | 1.5      |                          | 0.9 | 2.3       | mA    |

| IEE                   | Negative Supply Current             | All Switches "OFF," V <sub>S</sub> =±10V          | T <sub>A</sub> =25°C |                          | 3.0 | 5.0      |                          | 4.3 | 7.0       | mA    |

|                       |                                     |                                                   |                      |                          | 4.2 | 7.5      |                          | 6.0 | 10.5      | mA    |

| $I_R$                 | Reference Supply Current            | All Switches "OFF," V <sub>S</sub> =±10V          | T <sub>A</sub> =25°C |                          | 2.0 | 4.0      |                          | 2.7 | 5.0       | mA    |

|                       |                                     |                                                   |                      |                          | 2.8 | 6.0      |                          | 3.8 | 7.5       | mA    |

| I <sub>CC</sub>       | Positive Supply Current             | All Switches "OFF," V <sub>S</sub> =±10V          | T <sub>A</sub> =25°C |                          | 4.5 | 6.0      |                          | 7.0 | 9.0       | mA    |

|                       |                                     |                                                   |                      |                          | 6.3 | 9.0      |                          | 9.8 | 13.5      | mA    |

|                       |                                     |                                                   |                      |                          |     |          |                          |     |           |       |

Note 1: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits.

Note 2: Refer to RETSF11201X, RETSF11331X, RETSF11332X and RETSF11333X for military specifications.

Note 3: For operating at high temperature the molded DIP products must be derated based on a +100°C maximum junction temperature and a thermal resistance of  $\pm 150^{\circ}$  C/W, devices in the cavity DIP are based on a  $\pm 150^{\circ}$  C maximum junction temperature and are derated at  $\pm 100^{\circ}$  C/W.

# Electrical Characteristics (Note 4) (Continued)

Note 4: Unless otherwise specified,  $V_{CC}$ =+15V,  $V_{EE}$ =-15V,  $V_{R}$ =0V, and limits apply for -55°C $\leq$ T<sub>A</sub> $\leq$ +125°C for the LF11331/2/3 and the LF11201/2, -25°C $\leq$ T<sub>A</sub> $\leq$ +85°C for the LF13331/2/3 and the LF13201/2.

Note 5: These parameters are limited by the pin to pin capacitance of the package.

Note 6: This is the analog signal slew rate above which the signal is distorted as a result of finite internal slew rates.

Note 7: All switches in the device are turned "OFF" by saturating a transistor at the disable node as shown in Figure 5. The delay time will be approximately equal to the ton or toff plus the delay introduced by the external transistor.

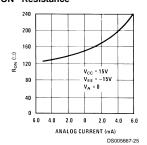

Note 8: This graph indicates the analog current at which 1% of the analog current is lost when the drain is positive with respect to the source.

Note 9:  $\theta_{\text{JA}}$  (Typical) Thermal Resistance

Molded DIP (N) 85°C/W

Cavity DIP (D) 100°C/W

Small Outline (M) 105°C/W

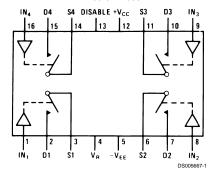

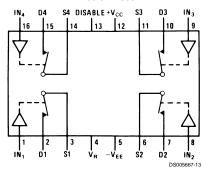

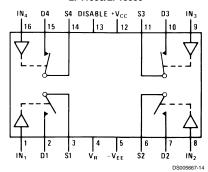

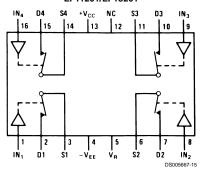

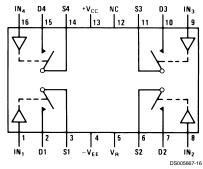

# Connection Diagrams (Top View for SO and Dual-In-Line Packages) (All Switches Shown are For Logical "0")

#### LF11331/LF13331

#### LF11332/LF13332

### LF11333/LF13333

#### LF11201/LF13201

**Connection Diagrams** (Top View for SO and Dual-In-Line Packages) (All Switches Shown are For Logical "0") (Continued)

#### LF11202/LF13202

Order Number LF13201D, LF11201D, LF11201D/883, LF13202D, LF11202D, LF11202D/883, LF13331D, LF11331D, LF11331D, LF11332D, LF11332D, LF11332D, LF11332D, LF11333D, LF1133D, LF1133D, LF1133D, LF1133D, LF1133D, LF113D, LF113D, LF113D, LF113D, LF113D, LF11D, LF1D, LF11D, LF1D, LF1D,

See NS Package Number D16C

Order Number LF13201M, LF13202M, LF13331M, LF13332M or LF13333M

See NS Package Number M16A

Order Number LF13201N, LF13202N, LF13331N, LF13332N or LF13333N

See NS Package Number N16A

Test Circuit and Typical Performance Curves Delay Time, Rise Time, Settling Time, and Switching Transients 2V/div 200 ns/div DS005667-18 2V/div 2V/div 2V/div 2V/div 200 ns/div 200 ns/div DS005667-21

www.national.com

# **Additional Test Circuits**

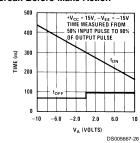

FIGURE 3.  $t_{\rm ON}$ ,  $t_{\rm OFF}$  Test Circuit and Waveforms for a Normally Open Switch

FIGURE 4. "OFF" Isolation, Crosstalk, Small Signal Response

# **Typical Performance Characteristics**

# "ON" Resistance

### "ON" Resistance

# "ON" Resistance

# **Typical Performance Characteristics** (Continued)

#### Break-Before-Make Action

#### **Switching Times**

# Crosstalk and "OFF" Isolation vs Frequency Using Test Circuit of Figure 5

# **Supply Current**

# **Supply Current**

# **Supply Current**

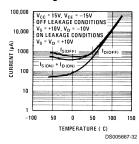

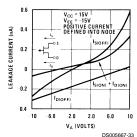

#### Switch Leakage Currents

#### Switch Leakage Current

#### **Switch Capacitances**

## Typical Performance Characteristics (Continued)

#### Slew Rate of Analog Voltage Above Which Signal Loading Occurs

#### Small Signal Response

#### **Maximum Accurate Analog Current** vs Temperature

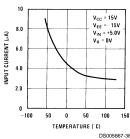

#### Logical "1" Input Bias Current

# **Application Hints GENERAL INFORMATION**

These devices are monolithic quad JFET analog switches with "ON" resistances which are essentially independent of analog voltage or analog current. The leakage currents are typically less than 1 nA at 25°C in both the "OFF" and "ON" switch states and introduce negligible errors in most applications. Each switch is controlled by minimum TTL logic levels at its input and is designed to turn "OFF" faster than it will turn "ON." This prevents two analog sources from being transiently connected together during switching. The switches designed for applications which break-before-make action, no analog current loss, medium speed switching times and moderate analog currents.

Because these analog switches are JFET rather than CMOS, they do not require special handling.

The logic input (IN), of each switch, is referenced to two forward diode drops (1.4V at 25°C) from the reference supply (VR) which makes it compatible with DTL, RTL, and TTL logic families. For normal operation, the logic "0" voltage can range from 0.8V to -4.0V with respect to  $V_R$  and the logic "1" voltage can range from 2.0V to 6.0V with respect to  $V_{\rm R}$ , provided  $V_{\text{IN}}$  is not greater than ( $V_{\text{CC}}$ -2.5V). If the input voltage is greater than ( $V_{\text{CC}}$ -2.5V), the input current will increase. If

the input voltage exceeds 6.0V or -4.0V with respect to  $V_R$ , a resistor in series with the input should be used to limit the input current to less than 100µA.

#### ANALOG VOLTAGE AND CURRENT

#### **Analog Voltage**

Each switch has a constant "ON" resistance ( $R_{ON}$ ) for analog voltages from ( $V_{EE}$ +5V) to ( $V_{CC}$ -5V). For analog voltages greater than (V<sub>CC</sub>-5V), the switch will remain ON independent of the logic input voltage. For analog voltages less than (V<sub>EE</sub>+5V), the ON resistance of the switch will increase. Although the switch will not operate normally when the analog voltage is out of the previously mentioned range, the source voltage can go to either ( $V_{EE}$ +36V) or ( $V_{CC}$ +6V), whichever is more positive, and can go as negative as V<sub>EE</sub> without destruction. The drain (D) voltage can also go to either (V<sub>EE</sub>+36V) or (V<sub>CC</sub>+6V), whichever is more positive, and can go as negative as (V<sub>CC</sub>-36V) without destruction.

#### **Analog Current**

With the source (S) positive with respect to the drain (D), the R<sub>ON</sub> is constant for low analog currents, but will increase at higher currents (>5 mA) when the FET enters the saturation region. However, if the drain is positive with respect to the source and a small analog current loss at high analog currents (Note 6) is tolerable, a low R<sub>ON</sub> can be maintained for analog currents greater than 5 mA at 25°C.

## **Application Hints** (Continued)

#### LEAKAGE CURRENTS

The drain and source leakage currents, in both the ON and the OFF states of each switch, are typically less than 1 nA at 25°C and less than 100 nA at 125°C. As shown in the typical curves, these leakage currents are Dependent on power supply voltages, analog voltage, analog current and the source to drain voltage.

#### **DELAY TIMES**

The delay time OFF ( $t_{OFF}$ ) is essentially independent of both the analog voltage and temperature. The delay time ON ( $t_{ON}$ ) will decrease as either ( $V_{CC}$ – $V_A$ ) decreases or the temperature decreases.

#### **POWER SUPPLIES**

The voltage between the positive supply ( $V_{CC}$ ) and either the negative supply ( $V_{EE}$ ) or the reference supply ( $V_R$ ) can be as much as 36V. To accommodate variations in input logic reference voltages,  $V_R$  can range from  $V_{EE}$  to ( $V_{CC}$ –4.5V). Care should be taken to ensure that the power supply leads for the device never become reversed in polarity or that the device is never inadvertently installed backwards in a test socket. If

one of these conditions occurs, the supplies would zener an internal diode to an unlimited current; and result in a destroyed device.

#### **SWITCHING TRANSIENTS**

When a switch is turned OFF or ON, transients will appear at the load due to the internal transient voltage at the gate of the switch JFET being coupled to the drain and source by the junction capacitances of the JFET. The magnitude of these transients is dependent on the load. A lower value  $R_{\rm L}$  produces a lower transient voltage. A negative transient occurs during the delay time ON, while a positive transient occurs during the delay time OFF. These transients are relatively small when compared to faster switch families.

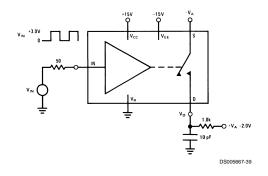

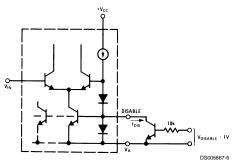

#### DISABLE NODE

This node can be used, as shown in Figure 5, to turn all the switches in the unit off independent of logic inputs. Normally, the node floats freely at an internal diode drop (=0.7V) above  $\mathsf{V}_\mathsf{R}$ . When the external transistor in Figure 5 is saturated, the node is pulled very close to  $\mathsf{V}_\mathsf{R}$  and the unit is disabled. Typically, the current from the node will be less than 1 mA. This feature is not available on the LF11201 or LF11202 series.

FIGURE 5. Disable Function

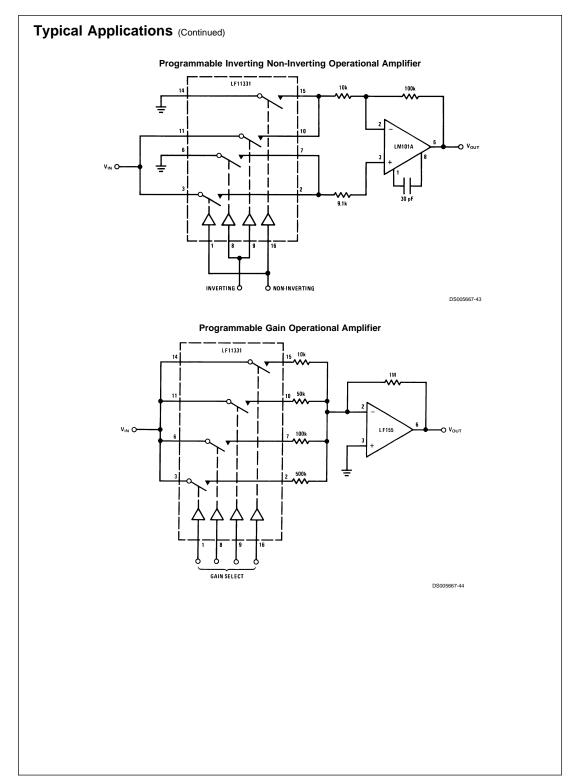

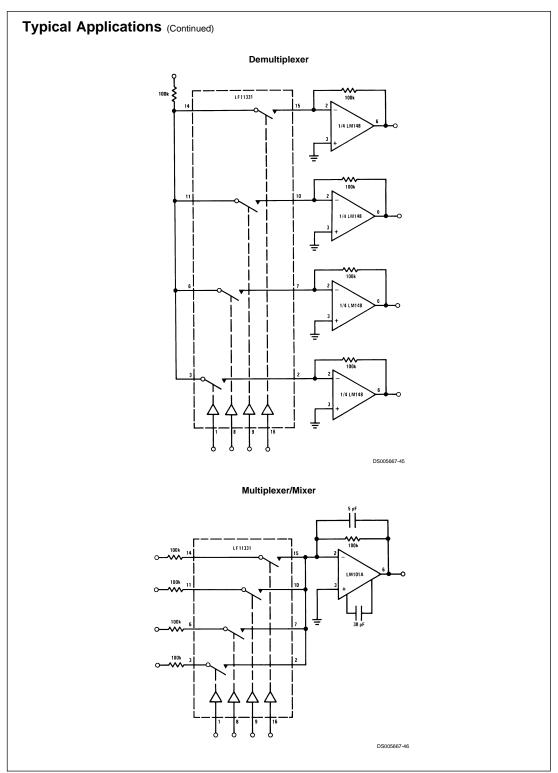

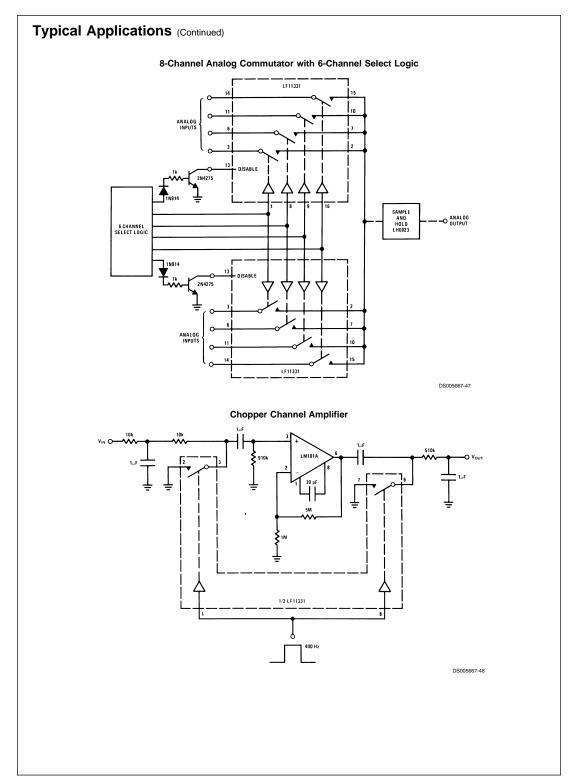

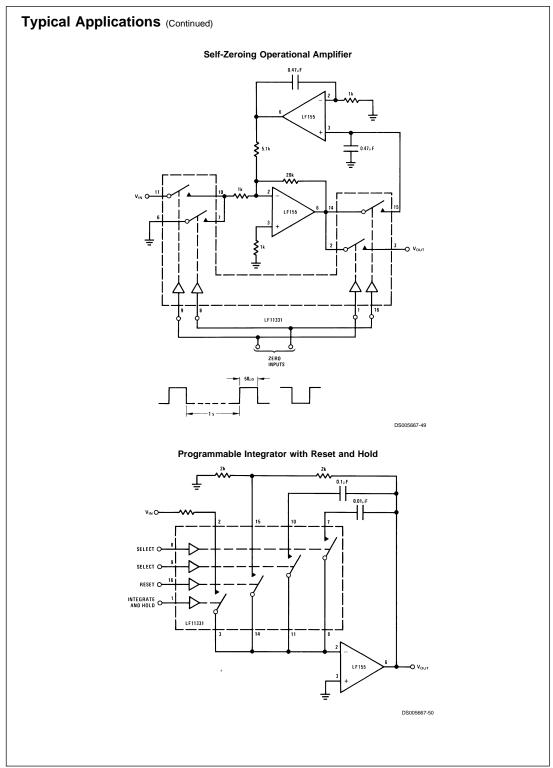

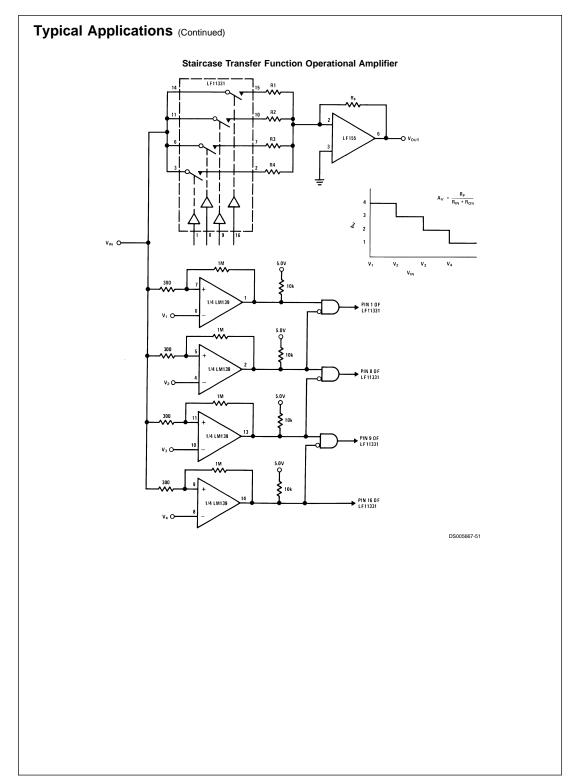

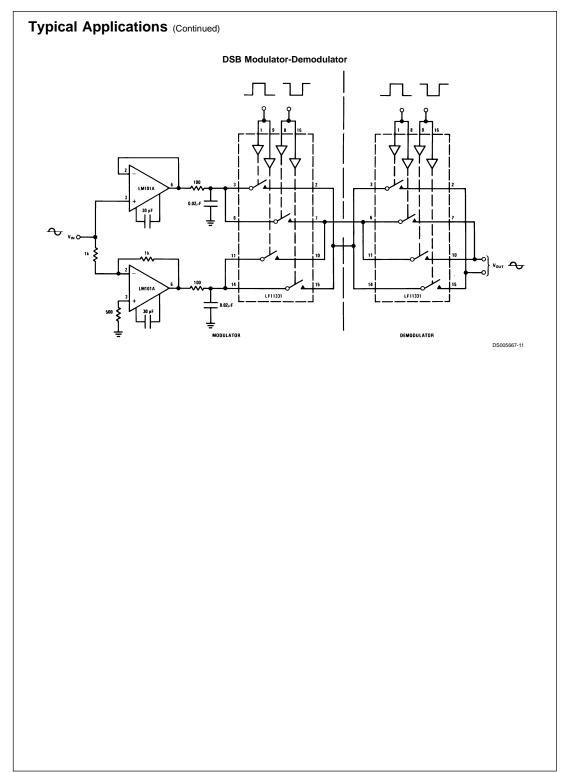

# **Typical Applications**

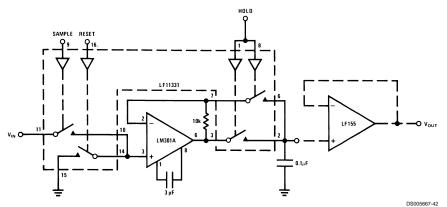

#### Sample and Hold with Reset

www.national.com

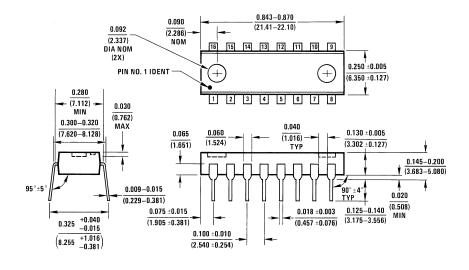

# Physical Dimensions inches (millimeters) unless otherwise noted

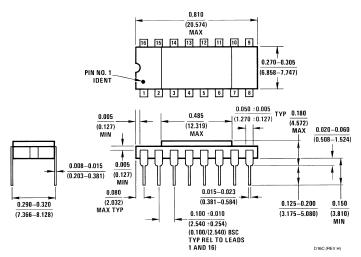

Order Number LF11201D, LF11201D/883, LF13201D, LF11202D, LF11202D/883, LF13202D, LF11331D, LF11331D/883, LF13331D, LF11332D, LF11332D/883, LF13332D, LF11333D/883 or LF13333D NS Package Number D16C

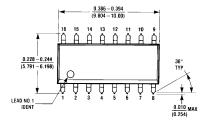

Order Number LF113201M, LF13202M, LF13331M, LF13332M or LF13333M NS Package Number M16A

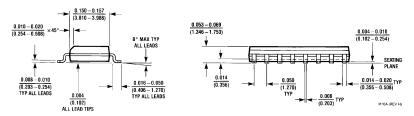

Order Number LF13201N, LF13202N, LF13331N, LF13332N or LF13333N NS Package Number N16A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas Tel: 1-800-272-9959 Fax: 1-800-737-7018

Email: support@nsc.com

www.national.com

National Semiconductor

Europe

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.cor

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-532 93 58

Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconducto Asia Pacific Custome Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd.

Tel: 81-3-5639-7560

Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.