95 mW max

# DAC0854 Quad 8-Bit Voltage-Output Serial D/A Converter with Readback

### **General Description**

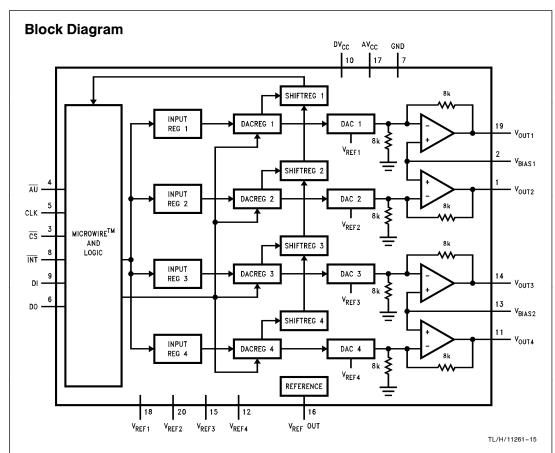

The DAC0854 is a complete quad 8-bit voltage-output digital-to-analog converter that can operate on a single 5V supply. It includes on-chip output amplifiers, internal voltage reference, and a serial microprocessor interface. By combining in one package the reference, amplifiers, and conversion circuitry for four D/A converters, the DAC0854 minimizes wiring and parts count and is hence ideally suited for applications where cost and board space are of prime concern.

The DAC0854 also has a data readback function, which can be used by the microprocessor to verify that the desired input word has been properly latched into the DAC0854's data registers. The data readback function simplifies the design and reduces the cost of systems which need to verify data integrity.

The logic comprises a MICROWIRETM-compatible serial interface and control circuitry. The interface allows the user to write to any one of the input registers or to all four at once. The latching registers are double-buffered, consisting of 4 separate input registers and 4 DAC registers. Double buffering allows all 4 DAC outputs to be updated simultaneously.

The four reference inputs allow the user to configure the system to have a separate output voltage range for each DAC. The output voltage of each DAC can range between 0.3V and 2.8V and is a function of  $V_{\mbox{\footnotesize{BIAS}}}, \, V_{\mbox{\footnotesize{REF}}},$  and the input word.

#### **Features**

- Single +5V supply operation

- MICROWIRE serial interface allows easy interface to many popular microcontrollers including the COPSTM and HPC™ families of microcontrollers

- Data readback capability

- Output data can be formatted to read back MSB or

- Versatile logic allows selective or global update of the DACs

- Power fail flag

- Output amplifiers can drive 2 kΩ load

- Synchronous/asynchronous update of the DAC outputs

### **Key Specifications**

- Guaranteed monotonic over temperature

- $\pm$  ½ LSB max ■ Integral linearity error Output settling time 2.7 us max Analog output voltage range 0.3V to 2.8V

- Supply voltage range 4.5V to 5.5V Clock frequency 10 MHz max

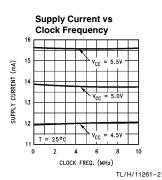

- Power dissipation (f<sub>CLK</sub> = 10 MHz) ■ On-board reference  $2.65V \pm 2\%$  max

# **Applications**

- Automatic test equipment

- Industrial process controls

- Automotive controls and diagnostics

- Instrumentation

#### **Connection Diagram**

#### **Ordering Information**

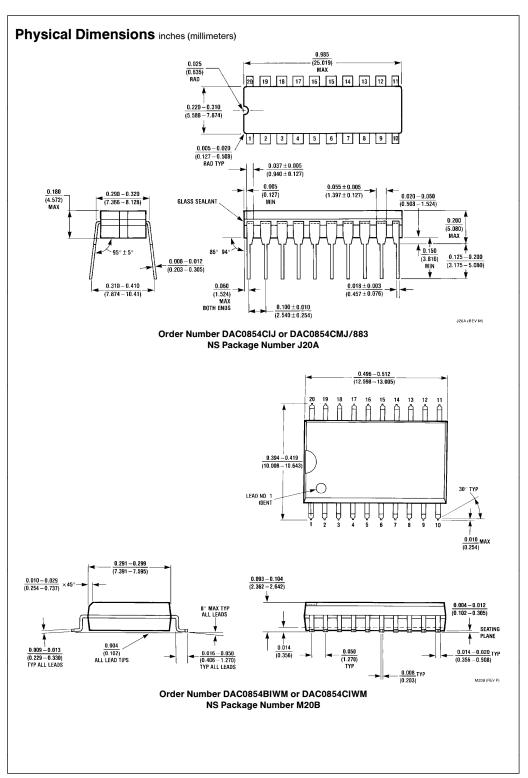

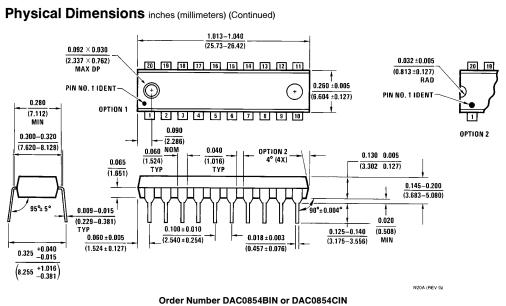

| Industrial (-40°C < T <sub>A</sub> +85°C)                         | Package            |  |  |

|-------------------------------------------------------------------|--------------------|--|--|

| DAC0854BIN, DAC0854CIN                                            | N20A Molded DIP    |  |  |

| DAC0854CIJ                                                        | J20A Ceramic DIP   |  |  |

| DAC0854BIWM, DAC0854CIWM                                          | M20B Small Outline |  |  |

| Military ( $-55^{\circ}$ C $<$ T <sub>A</sub> $< +125^{\circ}$ C) |                    |  |  |

| DAC0854CMJ/883                                                    | J20A Ceramic DIP   |  |  |

COPS™, HPC™ and MICROWIRE™ are trademarks of National Semiconductor Corporation.

#### Absolute Maximum Ratings (Notes 1 & 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

(Note 24)

ESD Susceptibility (Note 6)

Soldering Information

300°C

J Package (10 sec.)

260°C

N Package (10 sec.)

250°C

SO Package

Vapor Phase (60 sec.)

215°C

Infrared (15 sec.) (Note 7)

220°C

Storage Temperature

-65°C to +150°C

# Operating Ratings (Notes 1 & 2)

Supply Voltage 4.5V to 5.5V Supply Voltage Difference (AV $_{\rm CC}$  - DV $_{\rm CC}$ )  $\pm$  IV Temperature Range T $_{\rm MIN}$  < T $_{\rm A}$  < T $_{\rm MAX}$  DAC0854BIN, DAC0854CIN, DAC0854CIJ, DAC0854BIWM, DAC0854CIWM -40°C < T $_{\rm A}$  < 85°C DAC0854CMJ/883 -55°C < T $_{\rm A}$  < 125°C

# **Converter Electrical Characteristics**

The following specifications apply for AV $_{CC}=DV_{CC}=5V$ ,  $V_{REF}=2.65V$ ,  $V_{BIAS}=1.4V$ ,  $R_L=2\,k\Omega$  ( $R_L$  is the load resistor on the analog outputs – pins 1, 11, 14, and 19) and  $f_{CLK}=10$  MHz unless otherwise specified. **Boldface limits apply for T\_A=T\_J from T\_{MIN} to T\_{MAX}.** All other limits apply for T\_A=25°C.

1250V

| Symbol          | Parameter                                                                                        | Conditions                           | Typical<br>(Note 8) | Limit<br>(Note 9) | Units<br>(Limits) |  |

|-----------------|--------------------------------------------------------------------------------------------------|--------------------------------------|---------------------|-------------------|-------------------|--|

| TATIC CHAR      | ACTERISTICS                                                                                      |                                      |                     |                   |                   |  |

| n               | Resolution                                                                                       | f <sub>CLK</sub> = 10 MHz            | 8                   | 8                 | bits              |  |

|                 | Monotonicity                                                                                     | (Note 10)                            | 8                   | 8                 | bits              |  |

|                 | Integral Linearity Error DAC0854BIN, DAC0854BIWM DAC0854CIN, DAC0854CIJ, DAC0854CIWM, DAC0854CMJ | (Note 11)                            |                     | ± 0.5             | LSB (max)         |  |

|                 | Differential Linearity Error                                                                     |                                      |                     | ± 1.0             | LSB (max)         |  |

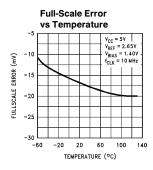

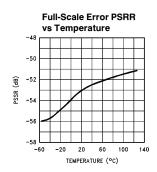

|                 | Fullscale Error                                                                                  | (Note 12)                            |                     | ± 35              | mV                |  |

|                 | Fullscale Error Tempco                                                                           | (Note 13)                            | -30                 |                   | ppm/°C            |  |

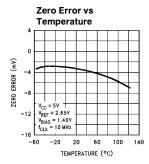

|                 | Zero Error                                                                                       | (Note 14)                            |                     | ± 35              | mV                |  |

|                 | Zero Error Tempco                                                                                | (Note 13)                            | -30                 |                   | ppm/°C            |  |

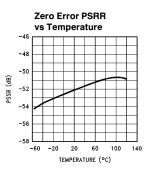

|                 | Power Supply Sensitivity                                                                         | (Note 15)                            | -34                 | dB (max)          |                   |  |

| YNAMIC CHA      | RACTERISTICS                                                                                     |                                      |                     |                   |                   |  |

| $t_{S+}$        | Positive Voltage Output<br>Settling Time                                                         | (Note 16)<br>C <sub>L</sub> = 200 pF | 1.5                 | 2.1               | μs                |  |

| t <sub>s-</sub> | Negative Voltage Output<br>Settling Time                                                         | (Note 16)<br>C <sub>L</sub> = 200 pF | 1.8                 | 2.7               | μs                |  |

|                 | Digital Crosstalk                                                                                | (Note 17)                            | 1.8                 |                   | mV <sub>p-p</sub> |  |

|                 | Digital Feedthrough                                                                              | (Note 18)                            | 8.5                 |                   | mV <sub>p-p</sub> |  |

|                 | Clock Feedthrough                                                                                | (Note 19)                            | 3.3                 |                   | mV <sub>p-p</sub> |  |

|                 | Channel-to-Channel Isolation                                                                     | (Note 20) -78                        |                     |                   | dB                |  |

|                 | Glitch Energy                                                                                    | (Note 21)                            | 7                   |                   | nV-s              |  |

|                 | Peak Value of Largest Glitch                                                                     |                                      | 38                  |                   | mV                |  |

| PSRR            | Power Supply Rejection Ratio                                                                     | (Note 22)                            | -49                 |                   | dB                |  |

# **Converter Electrical Characteristics** (Continued)

The following specifications apply for  $AV_{CC} = DV_{CC} = 5V$ ,  $V_{REF} = 2.65V$ ,  $V_{BIAS} = 1.4V$ ,  $R_L = 2 \, k\Omega$  ( $R_L$  is the load resistor on the analog outputs – pins 1, 11, 14, and 19) and  $f_{CLK} = 10$  MHz unless otherwise specified. **Boldface limits apply for T<sub>A</sub>** = **T<sub>J</sub> from T<sub>MIN</sub> to T<sub>MAX</sub>**. All other limits apply for  $T_A = 25^{\circ}C$ .

| Symbol                        | Parameter                                                                                                                                                                  | Conditions                                 | Typical<br>(Note 3) | Limit<br>(Note 4) | Units<br>(Limits)               |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------|-------------------|---------------------------------|

| DIGITAL AND I                 | DC ELECTRICAL CHARACTERIS                                                                                                                                                  | STICS                                      |                     |                   |                                 |

| V <sub>IN(1)</sub>            | Logical "1" Input Voltage                                                                                                                                                  | $AV_{CC} = DV_{CC} = 5.5V$                 |                     | 2.0               | V (min)                         |

| V <sub>IN(0)</sub>            | Logical "0" Input Voltage                                                                                                                                                  |                                            | 0.8                 | V (max)           |                                 |

| I <sub>IL</sub>               | Digital Input Leakage Current                                                                                                                                              |                                            | 1                   | 5                 | μΑ (max)                        |

| C <sub>IN</sub>               | Input Capacitance                                                                                                                                                          |                                            | 4                   |                   | pF                              |

| C <sub>OUT</sub>              | Output Capacitance                                                                                                                                                         |                                            | 5                   |                   | pF                              |

| V <sub>OUT(1)</sub>           | Logical "1" Output Voltage                                                                                                                                                 | I <sub>SOURCE</sub> = 0.8 mA               |                     | 2.4               | V (min)                         |

| V <sub>OUT(0)</sub>           | Logical "0" Output Voltage                                                                                                                                                 | I <sub>SINK</sub> = 3.2 mA                 |                     | 0.4               | V (max)                         |

| V <sub>INT</sub>              | Interrupt Pin Output Voltage                                                                                                                                               | 10 kΩ Pullup                               |                     | 0.4               | V (max)                         |

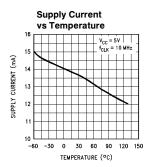

| Is                            | Supply Current                                                                                                                                                             | Outputs Unloaded                           | 14                  | 19                | mA                              |

| REFERENCE IN                  | NPUT CHARACTERISTICS                                                                                                                                                       |                                            |                     |                   |                                 |

| V <sub>REF</sub>              | Input Voltage Range                                                                                                                                                        |                                            | 0-2.75              |                   | V                               |

| R <sub>REF</sub>              | Input Resistance                                                                                                                                                           |                                            | 7                   | 4<br>10           | $k\Omega$ (min) $k\Omega$ (max) |

| C <sub>REF</sub>              | Input Capacitance                                                                                                                                                          | Full-Scale Data Input                      | 40                  |                   | pF                              |

| BIAS INPUT C                  | HARACTERISTICS                                                                                                                                                             |                                            | •                   |                   |                                 |

| V <sub>BIAS</sub>             | V <sub>BIAS</sub> Input Voltage Range                                                                                                                                      |                                            | 0.3-1.4             |                   | V                               |

|                               | Input Leakage                                                                                                                                                              |                                            | 1                   |                   | μΑ                              |

| C <sub>BIAS</sub>             | Input Capacitance                                                                                                                                                          |                                            | 9                   |                   | pF                              |

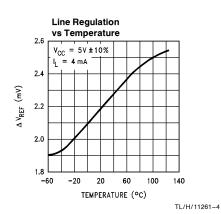

| SANDGAP REF                   | FERENCE CHARACTERISTICS (C                                                                                                                                                 | C <sub>L</sub> = 220μF)                    |                     |                   |                                 |

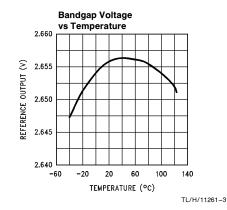

| V <sub>REF</sub> OUT          | Output Voltage                                                                                                                                                             |                                            |                     | 2.65 ± 2%         | V                               |

| $\Delta V_{REF}/\Delta T$     | Tempco                                                                                                                                                                     | (Note 23)                                  | 22                  |                   | ppm/°C                          |

|                               | Line Regulation                                                                                                                                                            | $4.5V < V_{CC} < 5.5V, I_L = 4 \text{ mA}$ | 2                   | 5                 | mV                              |

| $\Delta V_{REF}/\Delta I_{L}$ | $ \begin{array}{c c} \text{$'\Delta I_L$} & \text{Load Regulation} & 0 < I_L < 4 \text{ mA} \\ 0 < I_L < 4 \text{ mA; CMJ Suffix} \\ -1 < I_L < 0 \text{ mA} \end{array} $ |                                            | 2<br>2<br>2.5       | 6<br>15           | mV<br>mV<br>mV                  |

| I <sub>SC</sub>               | Short Circuit Current                                                                                                                                                      | V <sub>REF</sub> OUT = 0V                  | 12                  |                   | mA                              |

| C ELECTRICA                   | AL CHARACTERISTICS                                                                                                                                                         |                                            |                     |                   |                                 |

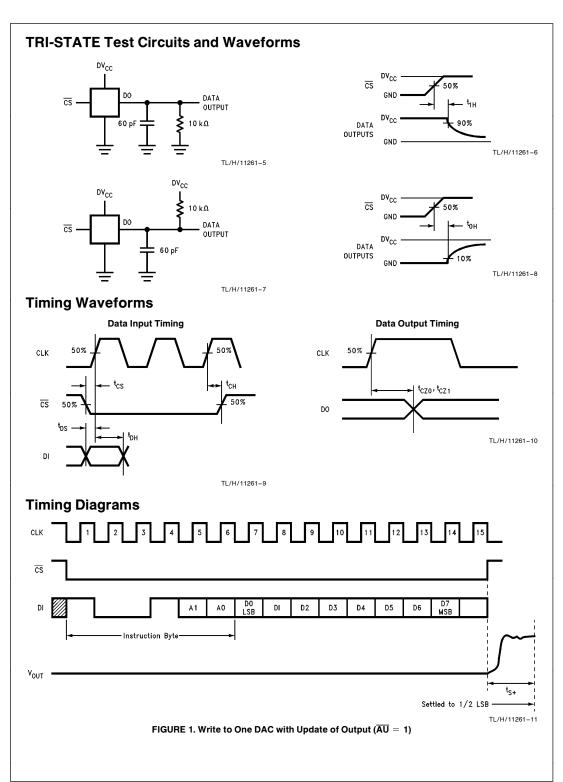

| t <sub>DS</sub>               | Data Setup Time                                                                                                                                                            |                                            |                     | 10                | ns (min)                        |

| t <sub>DH</sub>               | Data Hold Time                                                                                                                                                             |                                            |                     | 0                 | ns (min)                        |

| t <sub>CS</sub>               | Control Setup Time                                                                                                                                                         |                                            |                     | 15                | ns (min)                        |

| t <sub>CH</sub>               | Control Hold Time                                                                                                                                                          |                                            |                     | 0                 | ns (min)                        |

| t <sub>MIN</sub>              | Clock Frequency                                                                                                                                                            |                                            |                     | 10                | MHz (max                        |

| t <sub>H</sub>                | Minimum Clock High Time                                                                                                                                                    |                                            |                     | 20                | ns (min)                        |

| tL                            | Minimum Clock Low Time                                                                                                                                                     |                                            |                     | 40                | ns (min)                        |

# **Converter Electrical Characteristics (Continued)**

The following specifications apply for AV $_{CC}=DV_{CC}=5V$ ,  $V_{REF}=2.65V$ ,  $V_{BIAS}=1.4V$ ,  $R_{L}=2~k\Omega$  ( $R_{L}$  is the load resistor on the analog outputs – pins 1, 11, 14, and 19) and  $f_{CLK}=10$  MHz unless otherwise specified. **Boldface limits apply for T\_A = T\_J from T\_{MIN} to T\_{MAX}.** All other limits apply for  $T_{A}=25^{\circ}C$ .

| Symbol           | Parameter                 | Conditions       | Typical<br>(Note 3) | Limit<br>(Note 4) | Units<br>(Limits) |

|------------------|---------------------------|------------------|---------------------|-------------------|-------------------|

| AC ELECTRICAL    | CHARACTERISTICS (Continue | ed)              |                     |                   |                   |

| t <sub>CZ1</sub> | Output Hi-Z to Valid 1    |                  |                     | 37                | ns (max)          |

| t <sub>CZ0</sub> | Output Hi-Z to Valid 0    |                  |                     | 42                | ns (max)          |

| t <sub>1H</sub>  | CS to Output Hi-Z         | 10 kΩ with 60 pF |                     | 130               | ns (max)          |

| t <sub>0H</sub>  | CS to Output Hi-Z         | 10 kΩ with 60 pF |                     | 117               | ns (max)          |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional. These ratings do not guarantee specific performance limits, however. For guaranteed specifications and test conditions, see the Converter Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to ground, unless otherwise specified.

Note 3: When the input voltage  $(V_{IN})$  at any pin exceeds the power supply rails  $(V_{IN} \le GND \text{ or } V_{IN} \ge V^+)$  the absolute value of current at that pin should be limited to 5 mA or less.

Note 4: The sum of the currents at all pins that are driven beyond the power supply voltages should not exceed 20 mA.

Note 5: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$  (maximum junction temperature),  $\Theta_{JA}$  (package junction to ambient thermal resistance), and  $T_A$  (ambient temperature). The maximum allowable power dissipation at any temperature is  $P_{Dmax} = (T_{Jmax} - T_A)/\Theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. The table below details  $T_{Jmax}$  and  $\Theta_{JA}$  for the various packages and versions of the DAC0864.

| Part Number              | T <sub>Jmax</sub> (°C) | ⊕ <sub>JA</sub> (°C/W) |

|--------------------------|------------------------|------------------------|

| DAC0854BIN, DAC0854CIN   | 125                    | 46                     |

| DAC0854BIJ, DAC0854CIJ   | 125                    | 53                     |

| DAC0854BIWM, DAC0854CIWM | 125                    | 64                     |

| DAC0854CMJ/883           | 150                    | 53                     |

Note 6: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor

Note 7: See AN450 "Surface Mounting Methods and Their Effect on Production Reliability" of the section titled "Surface Mount" found in any current Linear Databook for other methods of soldering surface mount devices.

Note 8: Typicals are at  $T_J = 25^{\circ}\text{C}$  and represent most likely parametric norm.

Note 9: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 10: A monotonicity of 8 bits for the DAC0854 means that the output voltage changes in the same direction (or remains constant) for each increase in the input

Note 11: Integral linearity error is the maximum deviation of the output from the line drawn between zero and full-scale (excluding the effects of zero error and full-scale error).

Note 12: Full-scale error is measured as the deviation from the ideal 2.800V full-scale output when  $V_{REF} = 2.650V$  and  $V_{BIAS} = 1.400V$ .

Note 13: Full-scale error tempco and zero error tempco are defined by the following equation:

$$Error\ tempco = \left[\frac{Error\ (T_{MAX}) - Error\ (T_{MIN})}{V_{SPAN}}\right] \quad \left[\frac{10^6}{T_{MAX} - T_{MIN}}\right]$$

where Error  $(T_{MAX})$  is the zero error or full-scale error at  $T_{MAX}$  (in volts), and Error  $(T_{MIN})$  is the zero error or full-scale error at  $T_{MIN}$  (in volts);  $V_{SPAN}$  is the output voltage span of the DAC0854, which depends on  $V_{BIAS}$  and  $V_{REF}$ .

Note 14: Zero error is measured as the deviation from the ideal 0.310V output when  $V_{REF}=2.650V$ ,  $V_{BIAS}=1.400V$ , and the digital input word is all zeros. Note 15: Power Supply Sensitivity is the maximum change in the offset error or the full-scale error when the power supply differs from its optimum 5V by up to 0.25V (5%). The load resistor  $R_L=5~k\Omega$ .

Note 16: Positive or negative settling time is defined as the time taken for the output of the DAC to settle to its final full-scale or zero output to within ±0.5 LSB. This time shall be referenced to the 50% point of the positive edge of CS, which initiates the update of the analog outputs.

Note 17: Digital crosstalk is the glitch measured on the output of one DAC while applying an all 0s to all 1s transition at the input of the other DACs.

Note 18: All DACs have full-scale outputs latched and DI is clocked with no update of the DAC outputs. The glitch is then measured on the DAC outputs.

Note 19: Clock feedthrough is measured for each DAC with its output at full-scale. The serial clock is then applied to the DAC at a frequency of 10 MHz and the glitch on each DAC full-scale output is measured.

Note 20: Channel-to-channel isolation is a measure of the effect of a change in one DAC's output on the output of another DAC. The V<sub>REF</sub> of the first DAC is varied between 1.4V and 2.65V at a frequency of 15 kHz while the change in full-scale output of the second DAC is measured. The first DAC is loaded with all 0s.

Note 21: Glitch energy is the difference between the positive and negative glitch areas at the output of the DAC when a 1 LSB digital input code change is applied to the input. The glitch energy will have its largest value at one of the three major transitions. The peak value of the maximum glitch is separately specified.

Note 22: Power Supply Rejection Ratio is measured by varying  $AV_{CC} = DV_{CC}$  between 4.75V and 5.25V with a frequency of 10 kHz and measuring the proportion of this signal imposed on a full-scale output of the DAC under consideration.

Note 23: The bandgap reference tempco is defined by the following equation:

Tempco =

$$\left[ \frac{V_{REF} \left( T_{MAX} \right) - V_{REF} \left( T_{MIN} \right)}{V_{REF} \left( T_{ROOM} \right)} \right] \cdot \left[ \frac{10^6}{T_{MAX} - T_{MIN}} \right]$$

where  $T_{ROOM} = 25^{\circ}\text{C}$ ,  $V_{REF}$  ( $T_{MAX}$ ) is the reference output at  $T_{MAX}$ , and similarly for  $V_{REF}$  ( $T_{MIN}$ ) and  $V_{REF}$  ( $T_{ROOM}$ ).

Note 24: A Military RETS specification is available upon request.

# **Typical Converter Performance Characteristics**

# **Typical Reference Performance Characteristics**

# **Pin Description**

| V <sub>OUT1</sub> (19)<br>V <sub>OUT2</sub> (1)<br>V <sub>OUT3</sub> (14) | The voltage output connections of the four DACS. These provide output voltages in the range 0.3V-2.8V. | AU(4)                  | When this pin is taken low, all DAC outputs will be asynchronously updated. CS must be held high during the update. |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------|

| V <sub>OUT4</sub> (11)                                                    |                                                                                                        | V <sub>REF1</sub> (18) | The voltage reference inputs for the four                                                                           |

| V <sub>REF</sub> OUT(16)                                                  | The internal voltage reference output.                                                                 | V <sub>REF2</sub> (20) | DACs. The allowed range is 0V-2.75V.                                                                                |

|                                                                           | The output of the reference is 2.65V                                                                   | V <sub>REF3</sub> (15) |                                                                                                                     |

|                                                                           | $\pm 2\%$ . This pin should be bypassed with                                                           | V <sub>REF4</sub> (12) |                                                                                                                     |

|                                                                           | a 220 $\mu$ F capacitor.                                                                               | <u>CS</u> (3)          | The Chip Select control input. This input is                                                                        |

| V <sub>BIAS1</sub> (2)                                                    | V <sub>BIAS1</sub> is connected to the non-inverting                                                   |                        | active low.                                                                                                         |

| V <sub>BIAS2</sub> (13)                                                   | inputs of output amplifiers 1 and 2,                                                                   | CLK(5)                 | The external clock input pin.                                                                                       |

|                                                                           | thereby setting the virtual ground                                                                     | DI(9)                  | The serial data input. The data is clocked in                                                                       |

|                                                                           | voltage for DAC's 1 and 2, while V <sub>BIAS2</sub>                                                    |                        | LSB first. Preceding the data byte are 4 or 6                                                                       |

|                                                                           | performs this function for DAC's 3 and 4.                                                              |                        | bits of instructions.                                                                                               |

|                                                                           | The allowed range is 0.3V -1.4V.                                                                       | DO(6)                  | The serial data output. The data can be                                                                             |

| GND(7)                                                                    | The system ground pin. Connect to                                                                      |                        | clocked out either MSB or LSB first, and on                                                                         |

|                                                                           | clean ground point.                                                                                    |                        | either the positive or negative edge of the                                                                         |

| DV <sub>CC</sub> (10)                                                     | The digital and analog power supply                                                                    |                        | clock.                                                                                                              |

| AV <sub>CC</sub> (17)                                                     | pins. The power supply range of the                                                                    | ĪNT(8)                 | The power interrupt output. On an                                                                                   |

|                                                                           | DAC0854 is 4.5V - 5.5V. To guarantee                                                                   |                        | interruption of the power supply, this pin                                                                          |

|                                                                           | accuracy, it is required that the AV <sub>CC</sub>                                                     |                        | goes low. Since this pin has an open drain                                                                          |

|                                                                           | and DV <sub>CC</sub> pins be bypassed separately                                                       |                        | output, a 10 k $\Omega$ pull-up resistor must be                                                                    |

|                                                                           | with bypass capacitors of 10 $\mu$ F                                                                   |                        | connected to the supply.                                                                                            |

|                                                                           | tantalum in parallel with 0.1 $\mu\text{F}$ ceramic.                                                   |                        |                                                                                                                     |

### **Applications Information**

#### FUNCTIONAL DESCRIPTION

The DAC0854 is a monolithic quad 8-bit digital-to-analog converter that is designed to operate on a single 5V supply. Each of the four units is comprised of an input register, a DAC register, a shift register, a current output DAC, and an output amplifier. In addition, the DAC0854 has an onboard bandgap reference and a logic unit which controls the internal operation of the DAC0854 and interfaces it to microprocessors.

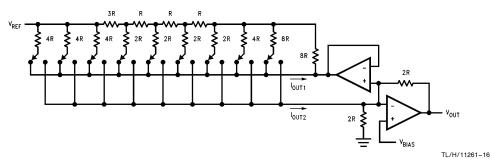

Each of the four internal 8-bit DACs uses a modified R-2R ladder to effect the digital-to-analog conversion (*Figure 5*). The resistances corresponding to the 2 most significant bits are segmented to reduce glitch energy and to improve matching. The bottom of the ladder has been modified so that the voltage across the LSB resistor is much larger than the input offset voltage of the buffer amplifier. The input digital code determines the state of the switches in the ladder network. The sum of currents I<sub>OUT1</sub> and I<sub>OUT2</sub> is fixed and is given by

The current output  $I_{OUT2}$  is applied to the internal output amplifier and converted to a voltage. The output voltage of each DAC is a function of  $V_{BIAS}$ ,  $V_{REF}$ , and the digital input word, and is given by

$$V_{OUT} = 2 (V_{REF} - V_{BIAS}) \frac{DATA}{256} + \frac{511}{128} V_{BIAS} - \frac{255}{128} V_{REF}$$

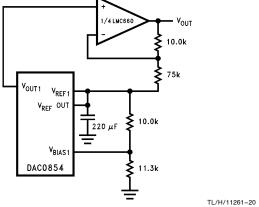

The output voltage range for each DAC is 0.3V-2.8V. This range can be achieved by using the internal 2.65V reference and a voltage divider network which provides a  $V_{BIAS}$  of 1.40V (Figure 6). In this case the DAC transfer function is

$$V_{OUT} = 2.5 \frac{\text{(DATA)}}{256} + 0.310$$

The output impedance of any external reference that is used will affect the accuracy of the conversion. In order that this error be less than  $1\!\!/_2$  LSB, the output impedance of the external reference must be less than  $7.8\Omega.$

TL/H/11261-17

$$I_{OUT1} + I_{OUT2} = \left(\frac{V_{REF} - V_{BIAS}}{R}\right) \frac{255}{256}$$

FIGURE 5. Equivalent Circuit of R-2R Ladder and Output Amplifier

V<sub>REF</sub> OUT REF

V<sub>REF1</sub> DAC 1

V<sub>REF2</sub> DAC 2

V<sub>OUT1</sub>

V<sub>REF3</sub> DAC 3

V<sub>OUT3</sub>

V<sub>REF4</sub> DAC 4

V<sub>OUT4</sub>

V<sub>REF4</sub> DAC 4

V<sub>OUT4</sub>

V<sub>OUT5</sub>

V<sub>OUT6</sub>

V<sub>OUT6</sub>

V<sub>OUT7</sub>

V<sub>OUT7</sub>

V<sub>OUT7</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

V<sub>OUT9</sub>

FIGURE 6. Generating a  $V_{\mbox{\footnotesize BIAS}}=\,$  1.40V from the Internal Reference

# **Digital Interface**

The DAC0854 has two interface modes: a WRITE mode and a READ mode. The WRITE mode is used to convert an 8-bit digital input word into a voltage. The READ mode is used to read back the digital data that was sent to one or all of the DACs. These modes are selected by the appropriate setting of the RD/WR bit, which is part of the instruction byte. The instruction byte precedes the data byte at the DI pin. In both modes, a high level on the Start Bit (SB) alerts the DAC to respond to the remainder of the input stream.

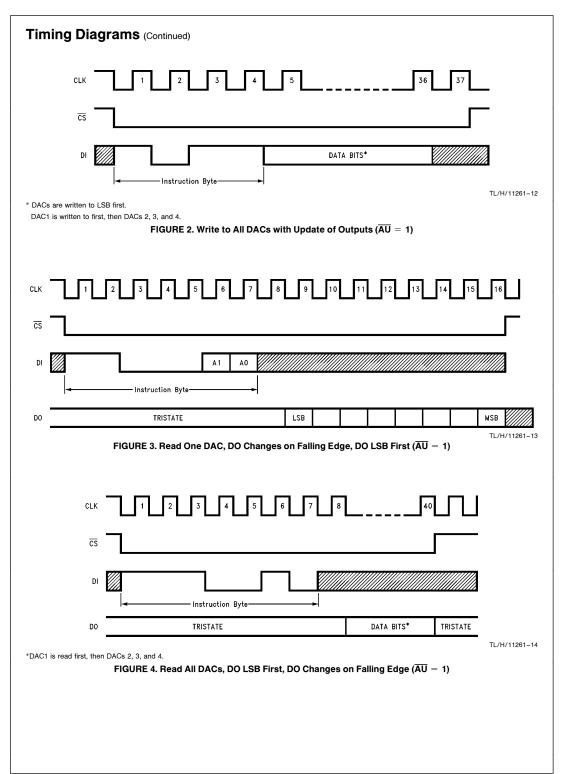

Table I lists the instruction set for the WRITE mode when writing to only a single DAC, and Table II lists the instruction set for a global write. The DACs are always written to LSB first. All DACs will be written to if the global bit (G) is high; DAC 1 is written to first, then DACs 2, 3 and 4 (in that order). If the update bit is high, then the DAC output will be updated on the rising edge of  $\overline{\text{CS}}$ ; otherwise, the new data byte will be placed only in the input register. Chip Select ( $\overline{\text{CS}}$ ) must remain low for at least one clock cycle after the last data bit has been entered. (See Figures 1 and 2)

TABLE I. WRITE Mode Instruction Set (Writing to a Single DAC)

| SB     | RD/WR  | G      | U      | A1     | Α0     | Description                                 |

|--------|--------|--------|--------|--------|--------|---------------------------------------------|

| Bit #1 | Bit #2 | Bit #3 | Bit #4 | Bit #5 | Bit #6 | Description                                 |

| 1      | 0      | 0      | 0      | 0      | 0      | Write DAC 1, no update of DAC outputs       |

| 1      | 0      | 0      | 0      | 0      | 1      | Write DAC 2, no update of DAC outputs       |

| 1      | 0      | 0      | 0      | 1      | 0      | Write DAC 3, no update of DAC outputs       |

| 1      | 0      | 0      | 0      | 1      | 1      | Write DAC 4, no update of DAC outputs       |

| 1      | 0      | 0      | 1      | 0      | 0      | Write DAC 1, update DAC 1 on CS rising edge |

| 1      | 0      | 0      | 1      | 0      | 1      | Write DAC 2, update DAC 2 on CS rising edge |

| 1      | 0      | 0      | 1      | 1      | 0      | Write DAC 3, update DAC 3 on CS rising edge |

| 1      | 0      | 0      | 1      | 1      | 1      | Write DAC 4, update DAC 4 on CS rising edge |

TABLE II. WRITE Mode Instruction Set (Writing to all DACs)

| SB      | RD/WR  | G      | U      | Description                                                              |

|---------|--------|--------|--------|--------------------------------------------------------------------------|

| Bit # 1 | Bit #2 | Bit #3 | Bit #4 | Description                                                              |

| 1       | 0      | 1      | 0      | Write all DACs, no update of outputs                                     |

| 1       | 0      | 1      | 1      | Write all DACs, update all outputs on $\overline{\text{CS}}$ rising edge |

# Digital Interface (Continued)

Table III lists the instruction set for the READ mode. By the appropriate setting of the global (G) and address (A1 and A0) bits, one can select a specific DAC to be read, or one can read all the DACs in succession, starting with DAC 1. The R/F bit determines whether the data changes on the rising or the falling edge of the system clock. With the R/F bit high, the data changes on the rising edge that occurs  $1\frac{1}{2}$  clock cycles after the end of the instruction byte. With the R/F bit low, the data changes on the falling edge that occurs

curs 1 clock cycle after the end of the instruction byte. One can choose to read the data back MSB first or LSB first by setting the  $M/\overline{L}$  bit. (See Figures 3 and 4)

An asynchronous update of all the DAC outputs can be achieved by taking  $\overline{AU}$  low. The contents of the input registers are loaded into the DAC registers, with the update occurring on the falling edge of  $\overline{AU}$ .  $\overline{CS}$  must be held high during an asynchronous update.

All DAC registers will have their contents reset to all zeros on power up.

#### **TABLE III. READ MODE Instruction Set**

| SB     | RD/WR  | G      | R/ <del>F</del> | M/L    | A1     | A0     | Description                                                |

|--------|--------|--------|-----------------|--------|--------|--------|------------------------------------------------------------|

| Bit #1 | Bit #2 | Bit #3 | Bit #4          | Bit #5 | Bit #6 | Bit #7 | Description                                                |

| 1      | 1      | 0      | 0               | 0      | 0      | 0      | Read DAC 1, LSB first, data changes on the falling edge    |

| 1      | 1      | 0      | 0               | 0      | 0      | 1      | Read DAC 2, LSB first, data changes on the falling edge    |

| 1      | 1      | 0      | 0               | 0      | 1      | 0      | Read DAC 3, LSB first, data changes on the falling edge    |

| 1      | 1      | 0      | 0               | 0      | 1      | 1      | Read DAC 4, LSB first, data changes on the falling edge    |

| 1      | 1      | 0      | 0               | 1      | 0      | 0      | Read DAC 1, MSB first, data changes on the falling edge    |

| 1      | 1      | 0      | 0               | 1      | 0      | 1      | Read DAC 2, MSB first, data changes on the falling edge    |

| 1      | 1      | 0      | 0               | 1      | 1      | 0      | Read DAC 3, MSB first, data changes on the falling edge    |

| 1      | 1      | 0      | 0               | 1      | 1      | 1      | Read DAC 4, MSB first, data changes on the falling edge    |

| 1      | 1      | 0      | 1               | 0      | 0      | 0      | Read DAC 1, LSB first, data changes on the rising edge     |

| 1      | 1      | 0      | 1               | 0      | 0      | 1      | Read DAC 2, LSB first, data changes on the rising edge     |

| 1      | 1      | 0      | 1               | 0      | 1      | 0      | Read DAC 3, LSB first, data changes on the rising edge     |

| 1      | 1      | 0      | 1               | 0      | 1      | 1      | Read DAC 4, LSB first, data changes on the rising edge     |

| 1      | 1      | 0      | 1               | 1      | 0      | 0      | Read DAC 1, MSB first, data changes on the rising edge     |

| 1      | 1      | 0      | 1               | 1      | 0      | 1      | Read DAC 2, MSB first, data changes on the rising edge     |

| 1      | 1      | 0      | 1               | 1      | 1      | 0      | Read DAC 3, MSB first, data changes on the rising edge     |

| 1      | 1      | 0      | 1               | 1      | 1      | 1      | Read DAC 4, MSB first, data changes on the rising edge     |

| 1      | 1      | 1      | 0               | 0      | 1      | 0      | Read all DACs, LSB first, data changes on the falling edge |

| 1      | 1      | 1      | 0               | 1      | 1      | 0      | Read all DACs, MSB first, data changes on the falling edge |

| 1      | 1      | 1      | 1               | 0      | 1      | 0      | Read all DACs, LSB first, data changes on the rising edge  |

| 1      | 1      | 1      | 1               | 1      | 1      | 0      | Read all DACs, MSB first, data changes on the rising edge  |

# **Power Fail Function**

If a power failure occurs on the system using the DAC0854 then the  $\overline{\text{INT}}$  pin will be pulled low on the next power-up cycle. To force this output high again and reset this flag, the  $\overline{\text{CS}}$  pin will have to be brought low. When this is done the  $\overline{\text{INT}}$  output will be pulled high again via an external 10  $k\Omega$  pull-up resistor. This feature may be used by the microprocessor to discard data whose integrity is in question.

# **Power Supplies**

The DAC0854 is designed to operate from a +5V (nominal) supply. There are two supply pins,  $AV_{CC}$  and  $DV_{CC}$ . These pins allow separate external bypass capacitors for the analog and digital portions of the circuit. To guarantee accurate conversions, the two supply pins should each be bypassed with a 0.1  $\mu$ F ceramic capacitor in parallel with a 10  $\mu$ F tantalum capacitor.

# **Typical Applications** 10.2k V<sub>OUT1</sub> V<sub>REF1</sub> ${\rm V}_{\rm REF}$ out **≸** 30.1k 10.0k 220 μF **≸** 10k DAC0854 11.3k TL/H/11261-18 FIGURE 7. Trimming the Offset of a 5V Op Amp Biased at Mid Supply $AV_{CC}$ V<sub>OUT1</sub> V<sub>REF1</sub> 1k V<sub>REF</sub> OUT 470k **≸ ≨** 215k 10.0k 220 μF **≸** 200k DAC0854 11.3k TL/H/11261-19 FIGURE 8. Trimming the Offset of a Dual Supply Op Amp Biased at Ground **≸** 10.0k

FIGURE 9. Bringing the Output Range Down to Ground

# NS Package Number N20A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tal: 1(800) 272-9959 National Semiconductor GmbH Livry-Gargan-Str. 10 D-82256 Fürstenfeldbruck Germany Tel: (81-41) 35-0 Telex: 527649 Fax: (81-41) 35-1 National Semiconductor Japan Ltd. Sumitomo Chemical Engineering Center Bidg. 7F 1-7-1, Nakase, Miharna-Ku Chiba-City. Ciba Prefecture 261 Tel: (043) 299-2300 Fax: (043) 299-2500

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductores Do Brazil Ltda. Rue Deputado Lacorda Franco 120-3A Sao Paulo-SP Brazil 05418-000 Tele: (55-11) 212-5066 Telex: 391-1131931 NSBR BR Fax: (55-11) 212-1181 National Semiconductor (Australia) Pty, Ltd. Building 16 Business Park Drive Monash Business Park Nottinghill, Melbourne Victoria 3168 Australia Tel: (3) 558-9999 Fax: (3) 558-9998