6.5 mW (max)

ADC16071/ADC16471 16-Bit Delta-Sigma 192 ks/s Analog-to-Digital Converters

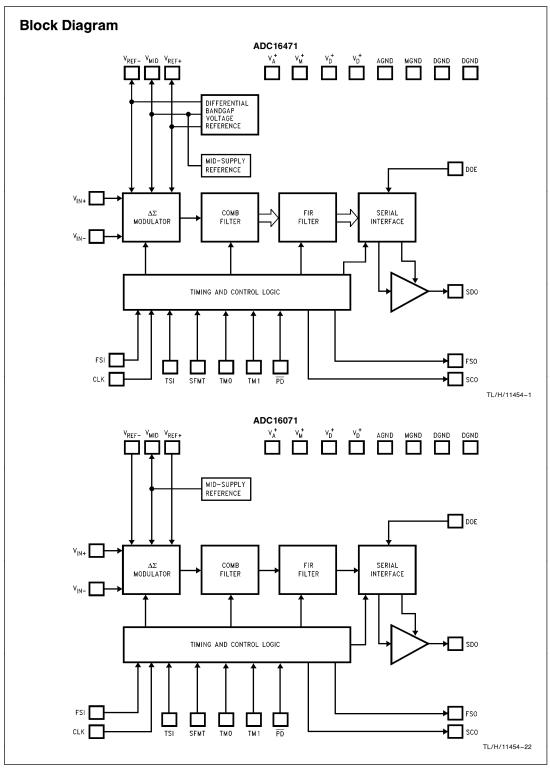

#### 12.288 MHz. A 5th-order comb filter and a 246 tap FIR decimation filter are used to achieve an output data rate of up to 192 kHz. The combination of oversampling and internal digital filtering greatly reduces the external anti-alias filter reguirements to a simple RC low pass filter. The FIR filters offer linear phase response, 0.005 dB passband ripple, and ≥90 dB stopband rejection. The ADC16071/ADC16471's analog fourth-order modulator uses switched capacitor technology. A built-in fully-differential bandgap voltage reference is also included in the ADC16471. The ADC16071 has no internal reference and requires externally applied reference voltages.

The ADC16071/ADC16471 use an advanced BiCMOS process for a low power consumption of 500 mW (max) while operating from a single 5V supply. A power-down mode reduces the power supply current from 100 mA (max) in the active mode to 1.3 mA (max).

The ADC16071/ADC16471 are ideal analog-to-digital front ends for signal processing applications. They provide a complete high resolution signal acquisition system that requires a minimal external anti-aliasing filter, reference, or interface logic.

The ADC16071/ADC16471's serial interface is compatible with the DSP56001, TMS320, and ADSP2100 digital signal

### **Key Specifications**

| <ul><li>Resolution</li></ul> | 16 DITS       |

|------------------------------|---------------|

| ■ Total harmonic distortion  |               |

| 48 kHz output data rate      | -94 dB (typ)  |

| 192 kHz output data rate     | -80 dB (typ)  |

| ■ Maximum output data rate   | 192 kHz (min) |

| ■ Power dissipation          |               |

| — Active                     |               |

| 192 kHz output data rate     | 500 mW (max)  |

| 48 kHz output data rate      | 275 mW (max)  |

## — Power-down **Key Features**

- Voltage reference (ADC16471 only)

- Fourth-order modulator

- lacksquare 64 imes oversampling with a 12.288 MHz sample rate

- Adjustable output data rate from 7 kHz to 192 kHz

- Linear-phase digital anti-aliasing filter:

- 0.005 dB passband ripple

- 90 dB stopband rejection

- Single +5V supply

- Power-down mode

- Serial data interface compatible with popular DSP devices

#### **Applications**

- Medical instrumentation

- Process control systems

- Test equipment

- High sample-rate audio

- Digital Signal Processing (DSP) analog front-end

- Vibration and noise analysis

**Ordering Information**

### **Connection Diagram**

| Part No.     | Package           | NS Package<br>No. |

|--------------|-------------------|-------------------|

| ADC16471CIN  | 24-Pin Molded DIP | N24C              |

| ADC16471CIWM | 24-Pin SOIC       | M24B              |

| ADC16071CIN  | 24-Pin Molded DIP | N24C              |

| ADC16071CIWM | 24-Pin SOIC       | M24B              |

|              |                   |                   |

TL/H/11454-2

#### Absolute Maximum Ratings (Notes 1 and 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage ( $V_A^+$ ,  $V_D^+$ , and  $V_M^+$ ) +6.5VLogic Control Inputs -0.3V to  $V_D^+ + 0.3V$ Voltage at Other Inputs and Outputs -0.3V to  $V_A^+ = V_M^+ + 0.3V$ Input Current at Any Pin (Note 3)  $\pm 25$  mA Package Input Current (Note 3)  $\pm 100$  mA Maximum Junction Temperature (Note 4)  $150^{\circ}\text{C}$ Storage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$

Lead Temperature

300°C

N Package (Soldering, 10 sec.)

300°C

WM Package (Infrared, 15 sec.)

220°C

WM Package (Vapor Phase, 60 sec.)

215°C

ESD Susceptibility (Note 5)

Human Body Model 4000V Machine Model 250V

See AN-450 "Surface Mounting Methods and Their Effect on Product Reliability" for other methods of soldering surface mount devices.

#### Operating Ratings (Notes 1 and 2)

Temperature Range  $\begin{array}{ll} (T_{min} \leq T_A \leq T_{max}) \\ ADC16471CIN, ADC16071CIN, -40^{\circ}C \leq T_A \leq +85^{\circ}C \\ ADC16471CIWM, ADC16071CIWM \\ \\ Supply Voltage \\ V_A^+, V_D^+, V_M^+ \\ \end{array}$

#### **Converter Electrical Characteristics**

The following specifications apply for  $V_M+=V_A+=V_D+=5.0V_{DC}$ ,  $V_{MID}=V_A+/2=2.50V$ ,  $V_{REF+}=V_{MID}+1.25V$ ,  $V_{REF-}=V_{MID}-1.25V$ ,  $V_{CLK}=24.576$  MHz, and dynamic tests are performed with an input signal magnitude set at -6 dB with respect to a full-scale input unless otherwise specified. **Boldface limits apply for T\_A=T\_J=T\_{min} to T\_{max}**; all other limits  $T_A=T_J=25^{\circ}C$ .

| Symbol                 | Parameter                          | Conditions                                                            | Typical<br>(Note 6) | Limits<br>(Note 7)     | Units<br>(Limit)     |

|------------------------|------------------------------------|-----------------------------------------------------------------------|---------------------|------------------------|----------------------|

|                        | Resolution                         |                                                                       |                     | 16                     | Bits                 |

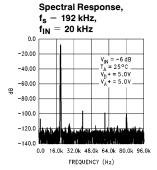

| <sub>CLK</sub> = 24.57 | 6 MHz (f <sub>s</sub> = 192 kHz)   |                                                                       |                     |                        |                      |

| S/(N+D)                | Signal-to-Noise + Distortion Ratio | Measurement bandwidth = $0.45f_s$<br>$f_{\text{IN}} = 19 \text{ kHz}$ | 76                  | 72                     | dB (min)             |

| THD                    | Total Harmonic Distortion          | f <sub>IN</sub> = 19 kHz                                              | 0.010               | 0.022                  | % (max)              |

| IMD                    | Intermodulation Distortion         | f <sub>1</sub> = 18.5 kHz, f <sub>2</sub> = 19.5 kHz                  | 0.010               | 0.017                  | % (max)              |

|                        | Converter Noise Floor (Note 8)     | Measurement Bandwidth = 0.45f <sub>s</sub>                            | -88                 | <b>-77</b>             | dBFS (min)           |

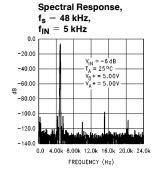

| CLK = 6.144            | MHz (f <sub>s</sub> = 48 kHz)      |                                                                       |                     |                        |                      |

| S/(N+D)                | Signal-to-Noise + Distortion Ratio | Measurement bandwidth = $0.45f_s$<br>$f_{ N} = 5 \text{ kHz}$         | 85                  | 80<br><b>73</b>        | dB (min)<br>dB (min) |

| THD                    | Total Harmonic Distortion          | f <sub>IN</sub> = 5 kHz                                               | 0.002               | 0.0055<br><b>0.008</b> | % (max)<br>% (max)   |

| IMD                    | Intermodulation Distortion         | f <sub>1</sub> = 4 kHz, f <sub>2</sub> = 5.5 kHz                      | 0.003               | 0.009<br><b>0.01</b>   | % (max)<br>% (max)   |

|                        | Converter Noise Floor (Note 8)     | Measurement Bandwidth = 0.45f <sub>s</sub>                            | -99                 | -92<br>- <b>89</b>     | dBFS (min)           |

| THER CON               | VERTER CHARACTERISTICS             |                                                                       |                     |                        | •                    |

| Z <sub>IN</sub>        | Input Impedance (Note 9)           |                                                                       | 34                  |                        | kΩ                   |

| $\Delta A_V$           | Gain Error                         |                                                                       | ±0.2                | ± 1.0                  | %FS (max)            |

| Vos                    | Input Offset Voltage               |                                                                       | 15                  |                        | mV                   |

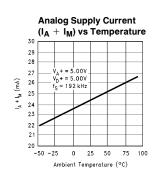

| I <sub>A</sub>         | Analog Power Supply Current        |                                                                       | 23                  | 31                     | mA (max)             |

| I <sub>M</sub>         | Modulator Power Supply Current     | f <sub>CLK</sub> = 24.576 MHz<br>f <sub>CLK</sub> = 6.144 MHz         | 1.6<br>0.4          | 2.4<br>0.8             | mA (max)             |

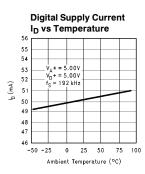

| I <sub>D</sub>         | Digital Power Supply Current       | $f_{CLK} = 24.576  MHz$ 50<br>$f_{CLK} = 6.144  MHz$ 13               |                     | 65<br>23               | mA (max)             |

| I <sub>SPD</sub>       | Power-Down Supply Current          | $I_A + I_D + I_M$                                                     | 0.25                | 1.3                    | mA                   |

| P <sub>D</sub>         | Power Dissipation                  |                                                                       | 0.375               | 0.5                    | W                    |

| V <sub>MID</sub>       |                                    |                                                                       | V <sub>A</sub> +/2  |                        | ٧                    |

Digital Filter Characteristics The following specifications apply for  $V_A{}^+ = V_D{}^+ = V_M{}^+ = 5V$  unless otherwise specified. Boldface limits apply for  $T_A = T_J = T_{min}$  to  $T_{max}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol | Parameter             | Conditions | Typical<br>(Note 6) | Limits<br>(Note 7) | Units<br>(Limit) |

|--------|-----------------------|------------|---------------------|--------------------|------------------|

|        | Stopband Rejection    |            | -90.0               |                    | dB               |

|        | Passband Ripple       |            | ±0.005              |                    | dB               |

|        | 3 dB Cutoff Frequency |            | 0.45                |                    | fs               |

|        | Data Latency          |            | 3,968               |                    | Clock Cycles     |

Reference Characteristics (ADC16471 Only) The following specifications apply for  $V_A{}^+ = V_D{}^+ = V_M{}^+ = 5V$ , unless otherwise specified. Boldface limits apply for  $T_A{}^- = T_J = T_{min}$  to  $T_{max}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol                                          | Parameter                                      | Conditions                                                                                                | Typical<br>(Note 6)     | Limits<br>(Note 7)                                   | Units<br>(Limit)   |

|-------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------|--------------------|

| V <sub>REF</sub> +                              | Positive Internal Reference<br>Output Voltage  |                                                                                                           | V <sub>MID</sub> + 1.25 | V <sub>MID</sub> + 1.175<br>V <sub>MID</sub> + 1.325 | V (min)<br>V (max) |

| V <sub>REF</sub> -                              | Negative Internal Reference<br>Output Voltage  |                                                                                                           | V <sub>MID</sub> - 1.25 | V <sub>MID</sub> — 1.325<br>V <sub>MID</sub> — 1.175 | V (min)<br>V (max) |

| Δ(V <sub>REF+</sub> –<br>V <sub>REF</sub> –)/ΔT | Internal Reference Temperature Coefficient     |                                                                                                           | 30                      |                                                      | ppm/°C             |

| $\Delta V_{REF+}/\Delta I$                      | Positive Internal Reference<br>Load Regulation | Sourcing (0 mA $\leq$ I $\leq$ +10 mA)<br>Sinking (-1 mA $\leq$ I $\leq$ 0 mA)                            | 3.4                     | 6.0                                                  | mV (max)           |

| $\Delta V_{REF} - /\Delta I$                    | Negative Internal Reference<br>Load Regulation | Sinking ( $-1 \text{ mA} \le I \le 0 \text{ mA}$ )<br>Sourcing ( $0 \text{ mA} \le I \le 10 \text{ mA}$ ) | 3.2                     | 6.0                                                  | iiiv (iiiax)       |

# Input Reference Characteristics (ADC16071 Only) The following specifications apply for $V_A{}^+ = V_D{}^+ = V_M{}^+ = 5V$ .

| Symbol                               | Parameter                  | Conditions | Typical<br>(Note 6) | Limits<br>(Note 7) | Units |

|--------------------------------------|----------------------------|------------|---------------------|--------------------|-------|

| V <sub>REF+</sub>                    | Positive Reference Voltage |            | 1                   |                    | V     |

|                                      |                            |            | V <sub>A</sub> +    |                    | V     |

| V <sub>REF</sub> _                   | Negative Reference Voltage |            | 0                   |                    | V     |

|                                      |                            |            | $V_A + - 1$         |                    | V     |

| V <sub>REF+</sub> -V <sub>REF-</sub> | Total Reference Voltage    |            | 1                   |                    | V     |

|                                      |                            |            | V <sub>A</sub> +    |                    | V     |

DC Electrical Characteristics The following specifications apply for  $V_A{}^+ = V_D{}^+ = V_M{}^+ = 5V$  unless otherwise specified. Boldface limits apply for  $T_A = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol             | Parameter                      | Conditions                                                  | Typical<br>(Note 6) | Limits<br>(Note 7)      | Units<br>(Limit)   |

|--------------------|--------------------------------|-------------------------------------------------------------|---------------------|-------------------------|--------------------|

| V <sub>IH</sub>    | Logic High Input Voltage       | $V_D^+ = 5.25V$                                             |                     | V <sub>D</sub> +<br>2.3 | V (max)<br>V (min) |

| V <sub>IL</sub>    | Logic Low Input Voltage        | $V_D^+ = 4.75V$                                             |                     | 0.8<br>- 0.3            | V (max)<br>V (min) |

| V <sub>OH</sub>    | Logic High Output Voltage      | Logic High Output Current = $-400 \mu A$ , $V_D^+ = 4.75 V$ |                     | 2.4                     | V (min)            |

| V <sub>OL</sub>    | Logic Low Output Voltage       | Logic Low Output Current = 2 mA, $V_D^+ = 5.25V$            |                     | 0.5                     | V (max)            |

| I <sub>IN(1)</sub> | Logical "1" Input Current      |                                                             | 1.0                 | 5.0                     | μΑ (max)           |

| I <sub>IN(0)</sub> | Logical "0" Input Current      |                                                             | -1.0                | -5.0                    | μA (max)           |

| I <sub>TSI</sub>   | SDO TRI-STATE® Leakage Current | $V_{IN} = 0.4V \text{ to } 2.4V$                            | 1.0                 | 5.0                     | μΑ (max)           |

| C <sub>IN</sub>    | Logic Input Capacitance        | $V_{IN} = 0 \text{ to } V_D^+$                              | 5                   |                         | pF                 |

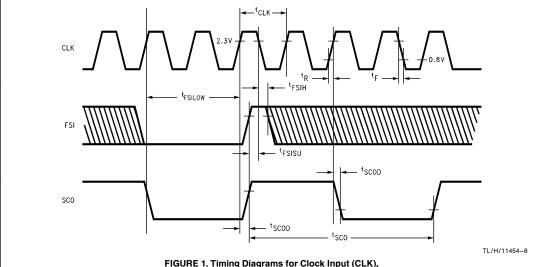

# AC Electrical Characteristics for Clock In (CLK), Serial Clock Out (SCO), and

Frame Sync In (FSI)

The following specifications apply for  $V_A^+ = V_D^+ = V_M^+ = 5V$  unless otherwise specified. Boldface limits apply for  $T_A$  =  $T_J$  =  $T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol              | Parameter                                                                     | Conditions | Typical<br>(Note 6) | Limits<br>(Note 7) | Units<br>(Limit)       |

|---------------------|-------------------------------------------------------------------------------|------------|---------------------|--------------------|------------------------|

| fCLK                | CLK Frequency Range<br>(f <sub>CLK</sub> = 1/t <sub>CLK</sub> )               |            |                     | 25<br>1            | MHz (max)<br>MHz (min) |

| t <sub>CLK</sub>    | CLK Period<br>(t <sub>CLK</sub> = 1/f <sub>CLK</sub> )                        |            |                     | 1000<br>40         | ns (max)<br>ns (min)   |

| t <sub>CLKL</sub>   | CLK Low Pulse Width                                                           |            |                     | 16                 | ns (min)               |

| t <sub>CLKH</sub>   | CLK High Pulse Width                                                          |            |                     | 14                 | ns (min)               |

| t <sub>R</sub>      | CLK Rise Time                                                                 |            |                     | 10<br>3            | ns (max)<br>ns (min)   |

| t <sub>F</sub>      | CLK Fall Time                                                                 |            |                     | 10<br>3            | ns (max)<br>ns (min)   |

| t <sub>FSILOW</sub> | Minimum Frame Sync Input<br>Low Time before Frame Sync<br>Input Asserted High |            | 2                   |                    | t <sub>CLK</sub> (min) |

| t <sub>FSISU</sub>  | Frame Sync Input Setup Time                                                   |            |                     | 10                 | ns (min)               |

| t <sub>FSIH</sub>   | Frame Sync Input Hold Time                                                    |            |                     | 10                 | ns (min)               |

| t <sub>SCOD</sub>   | Serial Clock Output Delay<br>Time from Rising Edge<br>of CLK                  |            | 12                  | 20<br>5            | ns (max)<br>ns (min)   |

| tsco                | Serial Clock Output Period                                                    |            |                     | 4                  | t <sub>CLK</sub>       |

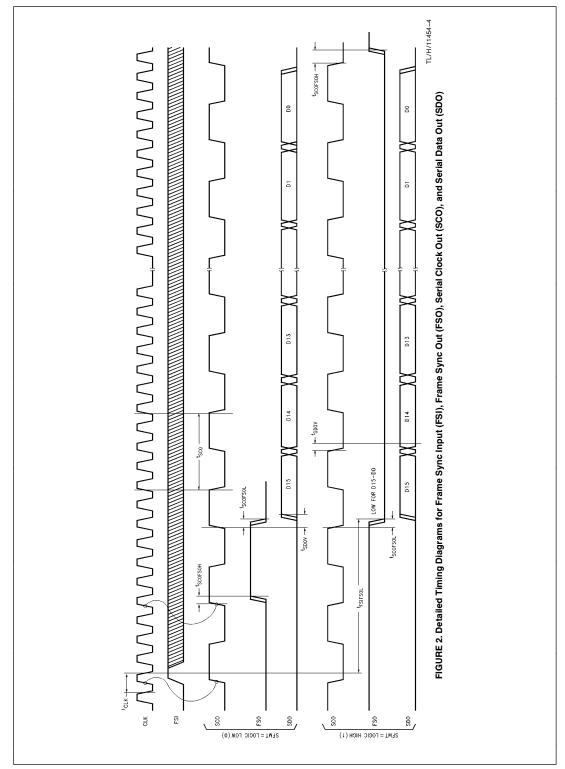

# AC Electrical Characteristics for Frame Sync Out (FSO), Serial Clock Out

(SCO), and Serial Data Out (SDO) The following specifications apply for  $V_A{}^+ = V_D{}^+ = V_M{}^+ = 5V$  unless otherwise specified. Boldface limits apply for  $T_A{}^- = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^{\circ}C$ .

| Symbol               | Parameter                                                  | Conditions | Typical<br>(Note 6) | Limits<br>(Note 7) | Units<br>(Limit)       |

|----------------------|------------------------------------------------------------|------------|---------------------|--------------------|------------------------|

| tscofsoн             | Delay from Serial Clock Out to<br>Frame Sync Output High   |            | 2                   | 5                  | ns (max)               |

| tscofsol             | Delay from Serial Clock Out to<br>Frame Sync Output Low    |            | 2                   | 5                  | ns (max)               |

| t <sub>SDOV</sub>    | Delay from Serial Clock Out to<br>Serial Data Output Valid |            | 3                   | 8                  | ns (max)               |

| t <sub>FSIFSOL</sub> | Delay from Frame Sync Input to<br>Frame Sync Output Low    |            |                     | 8                  | t <sub>CLK</sub> (max) |

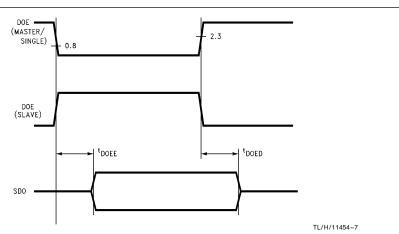

AC Electrical Characteristics for Data Output Enable (DOE) The following specifications apply for  $V_A{}^+ = V_D{}^+ = V_M{}^+ = 5V$  unless otherwise specified. Boldface limits apply for  $T_A{}^- = T_J = T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A = T_J = 25^\circ C$ .

| Symbol            | Parameter                      | Conditions | Typical<br>(Note 6) | Limits<br>(Note 7) | Units<br>(Limit) |

|-------------------|--------------------------------|------------|---------------------|--------------------|------------------|

| t <sub>DOEE</sub> | Data Output Enable Delay Time  |            | 20                  | 25                 | ns (max)         |

| t <sub>DOED</sub> | Data Output Disable Delay Time |            | 16                  | 20                 | ns (max)         |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not quarantee specific performance limits. For quaranteed specifications and test conditions, see the Electrical Characteristics. The quaranteed specifications apply for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: When the input voltage  $(V_{IN})$  at any pin exceeds the power supply rails  $(V_{IN} < GND \text{ or } V_{IN} > (V_A^+, V_M^+, \text{ or } V_D^+))$ , the current at that pin should be limited to 25 mA. The 100 mA maximum package input current rating allows the voltage at any four pins, with an input current of 25 mA each, to simultaneously exceed the

Note 4: The maximum power dissipation is a function of the maximum junction temperature  $(T_{J(MAX)})$ , total thermal resistance  $(\theta_{JA})$ , and ambient temperature  $(T_A)$ . The maximum allowable power dissipation at any ambient temperature is  $P_{D(max)} = (T_{J(max)} - T_{A})/\theta_{JA}$ . When board mounted, the ADC16071/ADC16471's typical thermal resistance is:

| Order Number               | $\theta_{JA}$ |

|----------------------------|---------------|

| ADC16071CIN, ADC16471CIN   | 47°C/W        |

| ADC16071CIWM, ADC16471CIWM | 72°C/W        |

Note 5: Human body model, 100 pF discharge through a 1.5 k $\Omega$  resistor. The machine model is a 200 pF capacitor discharged directly into each pin.

Note 6: Typicals are at  $T_A = 25^{\circ}C$  and represent most likely parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Output Quality Level).

Note 8: The  $V_{IN}^{\,+}$  pin is shorted to the  $V_{IN}^{\,-}$  pin.

Note 9: The input impedance between  $V_{IN+}$  and  $V_{IN-}$  due to the effective resistance of the switch capacitor input varies as follows:

$$Z_{IN} = \frac{10^{12}}{2.35^* \left(\frac{f_{CLK}}{2}\right)}$$

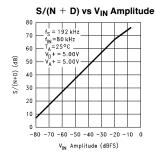

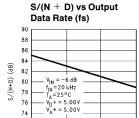

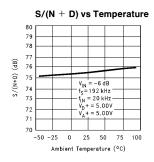

## **Typical Performance Characteristics**

192

72

70

TL/H/11454-24

FIGURE 1. Timing Diagrams for Clock Input (CLK), Frame Sync Input (FSI), and Serial Clock Output (SCO)

FIGURE 5. Timing Diagrams for Data Output Enable ( $\overline{\text{DOE}}$ ) and Serial Data Out (SDO)

| Pin Description                                  |                                                                                                                                                                                                                                                                                                                                                                           |                  |                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V <sub>REF</sub> <sup>+</sup> , V <sub>REF</sub> | These are the ADC16471's internal differential reference's bypass pins. Their nominal output voltage is $\pm 1.25$ V centered around the voltage at the V <sub>MID</sub> pin, typically V <sub>A</sub> +/2. V <sub>REF+</sub> , V <sub>MID</sub> , and V <sub>REF-</sub> should be bypassed with a parallel combination of 10 $\mu$ F and 0.1 $\mu$ F capacitors. For the | V <sub>M</sub> + | This is the modulator's supply pin. $V_M^+$ should be connected to the system analog voltage supply with a circuit board trace or connection that is separate from that used to supply $V_A^+$ . Best performance is achieved when this pin is bypassed with a parallel combination of 10 $\mu F$ and 0.1 $\mu F$ capacitors. |  |  |  |  |

|                                                  | ADC16071, these are the reference voltage inputs. $V_{REF+}$ and $V_{MID}$ should be bypassed with a parallel combination of 10 $\mu F$ and 0.1 $\mu F$ capacitors.                                                                                                                                                                                                       | V <sub>D</sub> + | This pin is the connection to the system digital voltage supply. Best performance is achieved when this pin is bypassed with a parallel combination of 10 $\mu$ F and 0.1 $\mu$ F capacitors.                                                                                                                                 |  |  |  |  |

| V <sub>MID</sub>                                 | This pin is the internal differential reference's $V_A^+/2$ output pin. $V_{MID}$ should be bypassed with a parallel combination of 10 $\mu F$ and 0.1 $\mu F$ capacitors.                                                                                                                                                                                                | SFMT             | This is the Serial Format pin. The logic level applied to the <b>SFMT</b> pin determines whether conversion data shifted out of the <b>SDO</b> pin is valid on the rising or falling edge of <b>SCO</b> . It also                                                                                                             |  |  |  |  |

| $V_{IN}^+, V_{IN}^-$                             | These are the ADC's differential input pins.<br>Signals applied to these pins can be single-<br>ended or differential with respect to the                                                                                                                                                                                                                                 |                  | controls the format of the Frame Sync Out <b>(FSO)</b> signal. See the <b>Serial Interface</b> section for details.                                                                                                                                                                                                           |  |  |  |  |

| PD                                               | V <sub>MID</sub> voltage.  This is the input pin used to activate the                                                                                                                                                                                                                                                                                                     | TM0, TM1         | Used to enabled test mode during production.  Connect both pins to DGND.                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                  | power-down mode. When a logic LOW (0) is applied to this pin the supply current drops from 100 mA (max) to 1.3 mA (max).                                                                                                                                                                                                                                                  | FSI              | This is the Frame Sync Input pin. <b>FSI</b> is an input used to synchronize the ADC16071/ADC16471's conversions to an external source.                                                                                                                                                                                       |  |  |  |  |

| AGND                                             | This is the connection to system analog ground. Internally, this ground is connected to the analog circuitry, including the fourth-                                                                                                                                                                                                                                       |                  | The state of <b>FSI</b> is sampled on the falling edge of <b>CLK</b> . See the <b>Serial Interface</b> section for details.                                                                                                                                                                                                   |  |  |  |  |

| DGND                                             | order modulator.  This is the connection to system digital ground. Internally, this ground is connected to all digital circuitry except the modulator's clock.                                                                                                                                                                                                            | CLK              | This is the clock signal input pin. The signal applied to this pin sets the sample rate of the ADC16071/ADC16471's modulator to f $_{\rm CLK}/2$ . The frequency range can be 1 MHz $\leq$ f $_{\rm CLK} \leq$ 25 MHz.                                                                                                        |  |  |  |  |

| MGND                                             | This is the ground pin for the modulator's clock. It should be connected to analog ground through its own connection that is separate from that used by AGND.                                                                                                                                                                                                             | SCO              | This is the Serial Clock Output pin. The ADC16071/ADC16471's serial data transmission is synchronous with the <b>SCO</b> signal. <b>SCO</b> has a frequency of f <sub>CLK</sub> /4. See the <b>Serial Interface</b> section for details.                                                                                      |  |  |  |  |

| V <sub>A</sub> +                                 | This pin is the connection to the system analog voltage supply. Best performance is achieved when this pin is bypassed with a parallel combination of 10 $\mu F$ and 0.1 $\mu F$ capacitors.                                                                                                                                                                              | SDO              | This is the Serial Data Output pin. The ADC16071/ADC16471's conversion data is shifted out from this pin synchronous to the SCO signal. See the Serial Interface section for details.                                                                                                                                         |  |  |  |  |

### Pin Description (Continued)

FSO This is the Frame Sync Output pin. FSO is used to synchronize an external device to the ADC16071/ADC16471's 32 SCO cycle data transmission frame. The format of the signal on FSO depends on the logic level applied to the SFMT pin. See the Serial Interface section for

TSI This is the Time Slot Input pin. TSI can be used to allow two ADC16071/ADC16471's to share a single serial data line. The logic level applied to TSI controls the active state of the ADC16071/ADC16471's DOE pin. See the Serial Interface and the Two Channel Multiplexed Operation sections for details.

DOE This is the Data Output Enable pin. **DOE** is used to control **SDO**'s TRI-STATE output buffer. The active state of **DOE** is controlled by the logic level applied to the **TSI** pin. See the **Serial Interface** and the **Two Channel Multiplexed Operation** sections for details.

### **Applications Information**

#### TYPICAL PERFORMANCE RESULTS

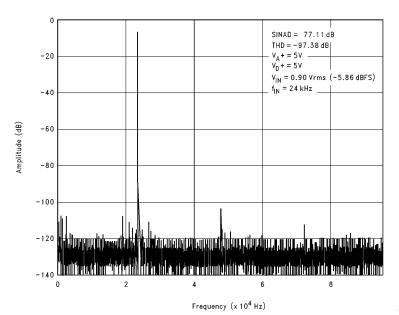

Figure 6 shows a 16k point FFT plot of the baseband output spectrum during conversion of a 24 kHz input signal.

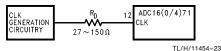

#### **CLOCK GENERATION**

The ADC16071/ADC16471 requires a sampling-clock signal that is free of ringing (over/undershoot of no more than  $100\ mV_{p-p}$ ) and has a rise and fall time in the range of 3 ns–  $10\ ns.$  We have tested and recommended crystal clock oscillators from Ecliptek (EC1100 series) and SaRonix (NCH060 and NCH080 series). Both of these families use HCMOS logic circuitry for very fast rise and fall times.

FIGURE 6. Typical Performance of the ADC16071/ADC16471 at f\_S  $=\,$  192 kHz, f\_{IN}  $=\,$  24 kHz

Overshoot and ringing can be reduced by adding a series damping resistor between the crystal oscillator's output (pin 8) and the ADC16071/ADC16471's CLK (pin 12), as shown in Figure 7. The actual resistor value is dependent on the board layout and trace length that connects the oscillator or CLK source to the ADC. A typical starting value is  $50\Omega$  with a range of  $27\Omega$  to  $150\Omega$ .

FIGURE 7. Damping Resistor Reduces Clock Signal Overshoot

#### **SERIAL INTERFACE**

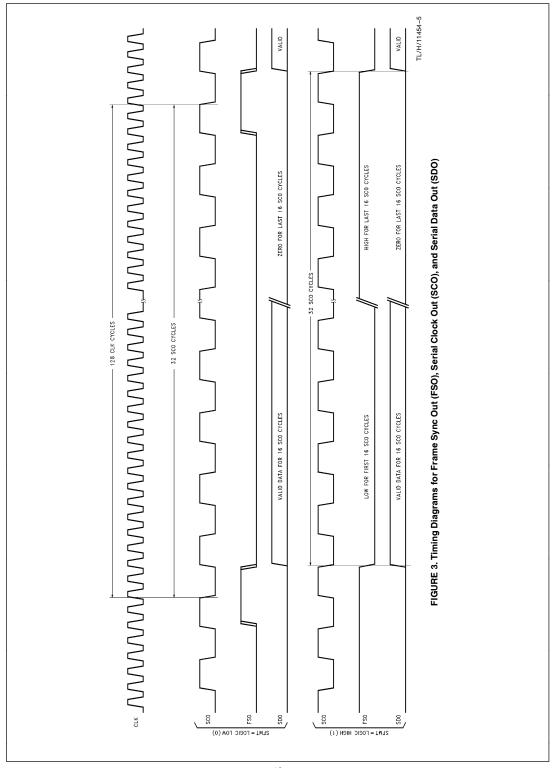

The ADC16071 and the ADC16471 have three serial interface output pins: Serial Data Output (SDO), Frame Sync Output (FSO), and Serial Clock Output (SCO). SCO has a frequency of  $f_{\rm CLK}/4$ . Each of the ADC16071/ADC16471's 16-bit conversions is transmitted within the first half of the data transmission frame. A data transmission frame is 32 SCO cycles in duration. Two's complement data shifts out on the SDO pin beginning with bit 15 (MSB) and ending with bit 0 (LSB), taking 16 SCO cycles. SDO then shifts out zeroes for the next 16 SCO cycles to maintain compatibility with two channel multiplexed operation.

The serial data that is shifted out of the SDO pin is synchronous with SCO. Depending on the logic level applied to the Serial Format pin (SFMT), the data on the SDO pin is valid on either the falling or rising edge of SCO. If a logic Low is applied to SFMT, then the data on SDO is valid on the falling edge of SCO. If a logic High is applied to SFMT, then the data on SDO is valid on the rising edge of SCO. See Figure 2.

The FSO signal is used to synchronize other devices to the ADC16071/ADC16471's data transmission frame. Depending on the logic level applied to SFMT, the signal on FSO is either a short pulse (approximately one SCO cycle in duration) ending just before the transmission of bit 15 on SDO, or a square wave with a period of 32 SCO cycles going low just before the transmission of bit 15 and going high just after the transmission of bit 0. If a logic Low is applied to SFMT, FSO will be high for approximately one SCO cycle and fall low just before the transmission of bit 15 and stay low for the remainder of the transmission frame. If a logic High is applied to SFMT, FSO will be low during the transmission of bits 15–0 and high during the next 16 SCO cycles. See Figure 3.

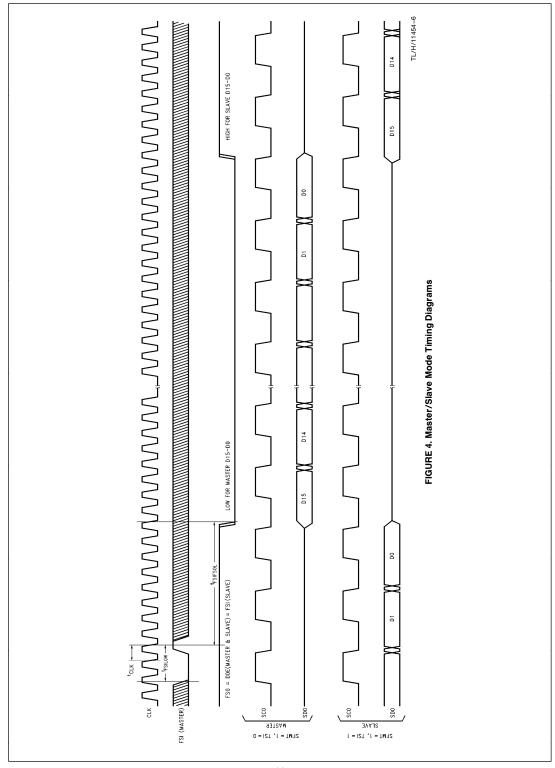

The Frame Sync Input (FSI), is used to synchronize the ADC16071/ADC16471's conversions to an external source. The logic state of FSI is captured by the ADC16071/ADC16471 on the falling edge of CLK. If an FSI low to high transition is sensed between adjacent CLK falling edges, the ADC16071/ADC16471 will interrupt its current data transmission frame and begin a new one. See Figure 4.

Due to the data latency of the ADC16071/ADC16471's digital filters, the first 31 conversions following a frame sync input signal will represent inaccurate data, unless the frame syncs are applied at constant 32 SCO cycle intervals. If no FSI signal is applied (FSI is kept High or Low), the ADC16071/ADC16471 will internally create a frame sync every 32 SCO cycles.

The Data Output Enable pin (DOE), is used to enable and disable the output of data on SDO. When DOE is deactivated, SDO stops driving the serial data line by entering a high impedance TRI-STATE. DOE's active state matches the logic level applied to the Time Slot Input pin (TSI). If a logic Low is applied to TSI, the ADC16071/ADC16471's SDO pin will shift out data when DOE is Low, and be in a high impedance TRI-STATE when DOE is High. If a logic High is applied to TSI, SDO will shift out data when DOE is High, and be in a high impedance TRI-STATE when DOE is Low.

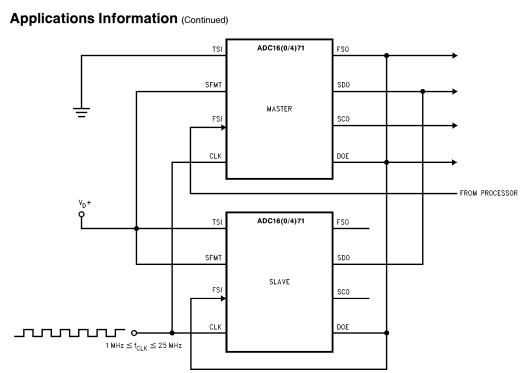

#### TWO CHANNEL MULTIPLEXED OPERATION

Two ADC16071/ADC16471's can easily be configured to share a single serial data line and operate in a "stereo", or two channel multiplexed mode. They share the serial data bus by alternating transmission of conversion data on their respective **SDO** pins. One of the ADC16071/ADC16471's, the Master, shifts its conversion data out of **SDO** during the first 16 SCO cycles of the data transmission frame. The other ADC16071/ADC16471, the Slave, shifts its data out during the second 16 SCO cycles of the data transmission frame.

The Slave is selected by applying a logic High to its **TSI** pin and a logic High to its **SFMT** pin. The Master is chosen by applying a logic Low to its **TSI** pin and a logic High to its **SFMT** pin. As shown in *Figure 8*, the Master's **FSO** is used to control the **DOE** of both the Master and the Slave as well as to synchronize the two ADC16071/ADC16471's by driving the Slave's Frame Sync Input pin, **FSI**. As the Master finishes transmitting its 16 bits of conversion data, its **FSO** goes High. This triggers the Slave's **FSI**, causing the Slave to begin transmitting its 16 bits of conversion data.

The Master's **DOE** is active Low and the Slave's **DOE** is active High. Since the same signal, the Master's **FSO**, is connected to both of the converters' **DOE** pins, one converter will shift out data on its **SDO** pin while the other is in TRI-STATE, allowing the two ADC16071/ADC16471's to share the same serial data transmission line.

#### POWER SUPPLY AND GROUNDING

The ADC16071/ADC16471 has on-chip 50 pF bypass capacitors between the supply-pin bonding pads and their corresponding grounds. There are 24 of these capacitors, 6 for the analog section and 18 for the digital, resulting in a total value of 1200 pF. They help control ringing on the on-chip power supply busses, especially in the digital section. Further, they help enhance the baseband noise performance of the analog modulator.

FIGURE 8. Two Channel Multiplexed Operation Connection Diagram

TL/H/11454-14

Best converter performance is achieved when these internal bypass capacitors are supplemented with additional external power-supply decoupling capacitors. This ensures the lowest ac-bypass impedance path for the ADC16071/ADC16471's dynamic current requirements. Each of the ADC16071/ADC16471's four supply pins should be individually bypassed, using a parallel combination of 10  $\mu F$  (tantalum) and 0.1  $\mu F$  (monolithic ceramic), to its corresponding ground pin:

$\begin{array}{ccc} V_A + & (\text{Pin 21}) & \longrightarrow & \text{AGND (Pin 4)} \\ V_M + & (\text{Pin 20}) & \longrightarrow & \text{MGND (Pin 5)} \\ V_D + & (\text{Pin 19}) & \longrightarrow & \text{DGND (Pin 6)} \\ V_D + & (\text{Pin 18}) & \longrightarrow & \text{DGND (Pin 7)} \end{array}$

Short lead lengths are mandatory. Therefore, surface mount capacitors are *strongly* recommended.

# POWER SUPPLY VOLTAGES FOR BEST PERFORMANCE

While adequate performance will be achieved by operating the ADC16071/ADC16471 with +5V connected to  $\text{V}_A+$ ,  $\text{V}_M+$  and  $\text{V}_D+$ , dynamic performance, as measured by S/(N + D), can be further enhanced by slightly raising the analog supply voltage and lowering the digital supply voltage.

#### **ANALOG INPUT**

The ADC16071 and the ADC16471 generate a two's complement output determined by the following equation:

Output Code =

$$\frac{(V_{IN} + - V_{IN} -) (32768)}{(V_{REF} + - V_{REF} -)}$$

Round off to the nearest integer value between -32768 and 32767.

The signals applied to  $V_{IN}^+$  and  $V_{IN}^-$  must be between  $V_A^+$  and analog ground. For accurate conversions, the absolute difference between  $V_{IN}^+$  and  $V_{IN}^-$  should be less than the difference between  $V_{REF}^+$  and  $V_{REF}^-$ . Best harmonic performance will result when a differential voltage is applied to  $V_{IN}^+$  and  $V_{IN}^-$  that has a common mode voltage at or below  $V_{MID}$ .

Due to overloading in the ADC16071/ADC16471's  $\Delta\Sigma$  modulator, performance degrades considerably as the input amplitude approaches full scale. With an input that peaks at -2 dB from full scale, S/(N+D) is about 2 dB worse than with a -6 dB input. With a -1 dB input, S/(N+D) can be 10 dB worse than with a -6 dB input.

#### **ANALOG SIGNAL CONDITIONING**

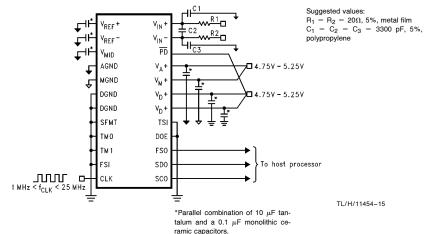

The ADC16071/ADC16471's digital comb and FIR filter combine to create the band-limiting anti-aliasing filter, generating a steep cutoff at the upper range of the sampled baseband. Additional external filtering is needed to ensure that the best conversion performance is maintained. The external filtering uses a simple R-C lowpass filter. A suggested circuit is shown in Figure 9. The values of R1, R2, C1, C2, and C3 are found using the following equation:

$$f_{\rm C (-3 dB)} = \frac{1}{6\pi RC}$$

where

$$R = R_1 = R_2$$

and  $C = C_1 = C_2 = C_3$ .

The effects of the external filter are minimized by choosing a minimum cutoff frequency equal to f<sub>CLK</sub>/32. As an example, for f<sub>CLK</sub> equal to 6.144 MHz, set R<sub>1</sub> = R<sub>2</sub> = 82.5 $\Omega$  and C<sub>1</sub> = C<sub>2</sub> = C<sub>3</sub> = 3300 pF. This sets the input network's cutoff frequency at 194 kHz. For f<sub>CLK</sub> equal to 24.576 MHz, set R<sub>1</sub> = R<sub>2</sub> = 20 $\Omega$  and C<sub>1</sub> = C<sub>2</sub> = C<sub>3</sub> = 3300 pF. This sets the input network's cutoff frequency at 803 kHz.

# RELATION BETWEEN CAPACITOR DIELECTRIC AND SIGNAL DISTORTION

For any capacitors connected to the ADC16071/ ADC16471's analog inputs, the dielectric plays an important role in determining the amount of distortion generated in the input signal. The capacitors used must have low dielectric absorption. This requirement is fulfilled using capacitors that have film dielectrics. Of these, polypropylene and polystyrene are the best. These are followed by polycarbonate and mylar. If ceramic capacitors are chosen, use only capacitors with NPO dielectrics.

#### INTERNAL DIFFERENTIAL BANDGAP REFERENCE

A fully differential bandgap reference generates local feedback voltages,  $V_{\rm REF}+$  and  $V_{\rm REF}-$ , for the analog modulator. The outputs of this reference are trimmed to be equal to  $V_{\rm MID}$  plus or minus 1.25V. This gives a differential reference voltage of 2.5V which results in a  $\pm 2.5V$  differential input range. The ADC16071 does not have the internal differential bandgap reference, allowing the user the flexibility to determine the full scale range by using an external voltage reference.

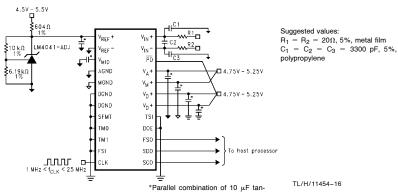

## EXTERNAL VOLTAGE REFERENCE FOR THE ADC16071

Figure 10 shows the suggested connection diagram for the ADC16071. The LM4041-ADJ is set to 2.0V and is applied to the ADC16071's  $V_{REF}+$  input.

The reference voltage must be free of noise. This is accomplished using the same capacitor combination used with the ADC16471's reference pins with the exception of  $\rm V_{REF}{}^-$ , which is connected to analog ground.

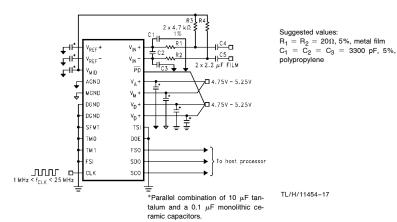

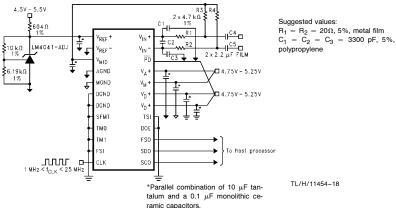

Figures 11 and 12 show the suggested circuits for ac-coupled applications.

FIGURE 9. Typical Connection Diagram for the ADC16471

talum and a 0.1  $\mu F$  monolithic ceramic capacitors.

TL/H/11454-16

### FIGURE 10. Typical Connection Diagram for the ADC16071

FIGURE 11. Typical Connection Diagram for the ADC16471 with AC-Coupled Inputs

FIGURE 12. Typical Connection Diagram for the ADC16071 with AC-Coupled Inputs

#### DSP INTERFACES

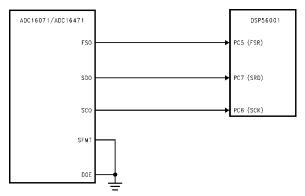

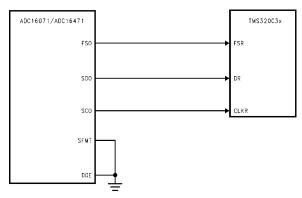

The ADC16071/ADC16471 was designed to connect to popular DSPs without intervening "glue logic". Figures 13, 14, and 15 show suggested connection schematics for the DSP56001, TMS320C3x, and the ADSP-2101 families.

FIGURE 13. Interface Connections between the ADC16071/ADC16471 and the Motorola DSP56001

FIGURE 14. Interface Connections between the ADC16071/ADC16471 and the Texas Instruments TMS320C3x

TL/H/11454-20

TL/H/11454-21

FIGURE 15. Interface Connections between the ADC16071/ADC16471 and the Analog Devices ADSP-2101

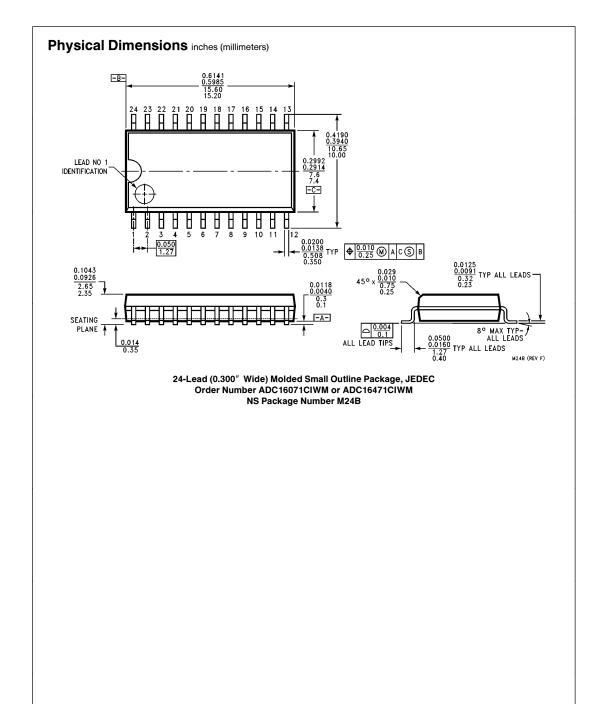

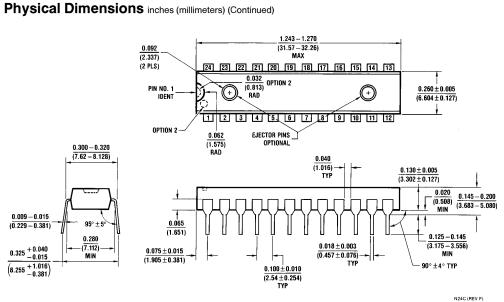

24-Lead (0.300" Wide) Molded Dual-In-Line Package Order Number ADC16071CIN or ADC16471CIN NS Package Number N24C

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tal: 1(800) 272-9959 National Semiconductor GmbH Livry-Gargan-Str. 10 D-82256 Fürstenfeldbruck Germany Tel: (81-41) 35-0 Telex: 527649 Fax: (81-41) 35-1 National Semiconductor Japan Ltd. Sumitomo Chemical Engineering Center Bldg. 7F 1-7-1, Nakase, Miharna-Ku Chiba-City. Ciba Prefecture 261 Tel: (043) 299-2300 Fax: (043) 299-2500

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tei: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductores Do Brazil Ltda. Rue Deputado Lacorda Franco 120-3A Sao Paulo-SP Brazil 05418-000 Tel: (55-11) 212-5066 Telex: 391-1131931 NSBR BR Fax: (55-11) 212-1181 National Semiconductor (Australia) Pty, Ltd. Building 16 Business Park Drive Monash Business Park Nottinghill, Melbourne Victoria 3168 Australia Tel: (3) 558-9999 Fax: (3) 558-9998