## MSM13Q/14Q000 0.35 µm Sea of Gates Arrays

November 1999

Oki Semiconductor

# Oki Semiconductor MSM13Q0000/14Q0000

0.35 µm Sea of Gates Arrays

## DESCRIPTION

Oki's  $0.35 \mu m$  ASIC products deliver ultra-high performance and high density at low power dissipation. The MSM13Q0000/14Q0000 series devices (referred to as "MSM13Q/14Q") are implemented with the industry-standard Cell-Based Array (CBA) architecture in a Sea-of-Gates (SOG) structure. Built in a 0.35  $\mu m$  drawn CMOS technology (with an L-Effective of 0.27  $\mu m$ ), these SOG devices are available in three layers (MSM13Q) and four layers (MSM14Q) of metal. The semiconductor process is adapted from Oki's production-proven 64-Mbit DRAM manufacturing process.

The MSM13Q/14Q Series contains 6 arrays each, offering over 1 million raw gates and 352 I/O pads. Up to 66% and 90% of the raw gates can be used for the 3-layer and 4-layer arrays, respectively. Oki's 0.35  $\mu$ m family is optimized for 3-V core operation with optimized 3-V I/O buffers and 5-V tolerant 3-V buffers. These SOG products are designed to fit the most popular plastic quad flat packs (QFPs), thin QFPs (TQFPs), and plastic ball grid array (PBGA) packages.

The MSM13Q/14Q Series uses the popular CBA architecture from Silicon Architects of Synopsys which mixes two types of cells (8-transistor compute cells and 4-transistor drive cells) on the same die to deliver high gate density and high drives. The CBA is supported by a rich macro library, optimized for synthesis. Memory blocks are efficiently created by Oki's memory compilers to generate single- and dual-port RAM's in high-density and low-power configurations with synchronous RAM options.

As such, the MSM13Q/14Q series is well suited to memory-intensive designs with high production volumes approaching the real estate and cost savings of standard cells. At the same time, its SOG architecture allows rapid prototyping turnaround times. Thus, Oki's MSM13Q/14Q family offers the best of two worlds: quick prototyping of a gate array and low production cost of a standard cell.

Oki's 0.35 µm ASIC products are supported by leading-edge CAD tools including a synthesis-linked floorplanner, motive static timing analyzer, and H-clock tree methodology. They are further supported by specialized macrocells including phase-locked loop (PLL), pseudo-emitter coupled logic (PECL), peripheral component interconnect (PCI), universal synchronous receiver/transmitter (UART) cells, and ARM7TDMI RISC cores.

## FEATURES

- + 0.35  $\mu m$  drawn 3- and 4-layer metal CMOS

- Optimized 3.3-V core

- Optimized 3-V I/O and 3-V I/O that is 5-V tolerant

- CBA SOG architecture

- Over 1.0M raw gates and 352 pads

- User-configurable I/O with V<sub>SS</sub>, V<sub>DD</sub>, TTL, 3state, and 1- to 24-mA options

- Slew-rate-controlled outputs for low-radiated noise

- H-clock tree cells which reduce the maximum skew for clock signals

- User-configurable single and dual-port; synchronous or asynchronous memories

- Specialized macrocells including PLL, PECL, PCI, UART, and ARM7TDMI

- Floorplanning for front-end simulation, backend layout controls, and link to synthesis

- Joint Test Action Group (JTAG) boundary scan and scan-path ATPG

- Support for popular CAE systems, including Cadence, IKOS, Mentor Graphics, Synopsys, Viewlogic, and Zycad

| MSM130/140 | M13Q/14Q Raw Gate Usable Gate Usable Gate | Usable Gate | Raw Gate  |           |     |        |

|------------|-------------------------------------------|-------------|-----------|-----------|-----|--------|

| Series     | PAD No.                                   | (Gates)     | M13Q(3LM) | M14Q(4LM) | Row | Column |

| 0150       | 144                                       | 157,192     | 105,319   | 143,045   | 196 | 802    |

| 0230       | 176                                       | 242,400     | 152,712   | 208,464   | 240 | 1,010  |

| 0340       | 208                                       | 346,176     | 204,244   | 276,941   | 288 | 1,202  |

| 0530       | 256                                       | 536,400     | 289,656   | 391,572   | 360 | 1,490  |

| 0840       | 320                                       | 847,048     | 415,054   | 567,522   | 452 | 1,874  |

| 1020       | 352                                       | 1,033,000   | 475,180   | 650,790   | 500 | 2,066  |

#### **MSM13Q/14Q FAMILY LISTING**

### ARRAY ARCHITECTURE

The primary components of a 0.35 µm MSM13Q/14Q circuit include:

- I/O base cells

- Configurable I/O pads for V<sub>DD</sub>, V<sub>SS</sub>, or I/O (optimized 3-V I/O and 3-V I/O that is 5-V tolerant)

- V<sub>DD</sub> and V<sub>SS</sub> pads dedicated to wafer probing

- Separate power bus for output buffers

- Separate power bus for internal core logic and input buffers

- Core base modules containing three compute cells for each drive cell

- · Isolated gate structure for reduced input capacitance and increased routing flexibility

Each array has 24 dedicated corner pads for power and ground use during wafer probing, with 4 pads per corner. The arrays also have separate power rings for the internal core functions ( $V_{DDC}$  and  $V_{SSC}$ ) and output drive transistors ( $V_{DDO}$  and  $V_{SSO}$ ).

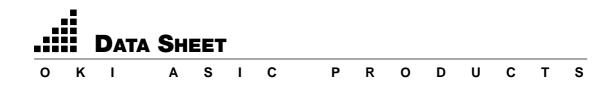

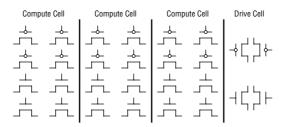

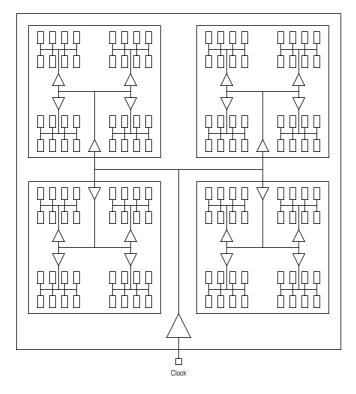

The array architecture uses optimally sized transistors to efficiently implement logic and memory in a metal programmable technology. CBA uses two types of cells: compute cells and drive cells. The compute cell employs four PMOS and four NMOS transistors whose sizes are optimized for logic and memory implementations as shown in *Figure 1*. The quantity and size of the transistors in a compute cell are carefully selected to maximize the efficiency of most commonly used functions in VLSI design. The drive cell consists of two large PMOS pull-up transistors and two large pull-down transistors. The compute and drive cells are tiled to create a channelless core array, with three comput cells for each drive cell as shown in *Figure 2*. The 3:1 ratio of compute to drive cells was selected for optimal implementation of emerging applications. Macrocells are created using either compute cells, drive cells, or combinations of compute and drive cells.

Figure 1. Base Cell Consisting of Three Compute Cells and One Drive Cell

Figure 2. Core Array with Base Cell Mirrored Horizontally and Vertically

## **ELECTRICAL CHARACTERISTICS**

| Parameter Power supply voltage |                | Symbol           | Conditions                                | Rated Value                  | Unit |  |

|--------------------------------|----------------|------------------|-------------------------------------------|------------------------------|------|--|

|                                |                | V <sub>DD</sub>  |                                           | -0.3 to +4.6                 | V    |  |

| Input voltage                  | Normal buffers | VI               |                                           | -0.3 to V <sub>DD</sub> +0.3 |      |  |

|                                | 5-V tolerant   | VI               |                                           | -0.3 to 6.0                  | – V  |  |

| Output voltage                 | Normal buffers | V <sub>0</sub>   |                                           | -0.3 to V <sub>DD</sub> +0.3 | v    |  |

|                                | 5-V tolerant   | V <sub>0</sub>   |                                           | -0.3 to 6.0                  |      |  |

| Input current                  | Normal buffers | I <sub>I</sub>   |                                           | -10 to +10                   |      |  |

|                                | 5-V tolerant   | I <sub>I</sub>   |                                           | -6 to +6                     | - mA |  |

| Output current per I/O         | Normal buffers | I <sub>O</sub>   | I <sub>0</sub> = 1, 2, 4, 6, 8, 12, 24 mA | -24 to +24                   |      |  |

|                                | 5-V tolerant   | I <sub>O</sub>   | l <sub>0</sub> = 2, 4, 6, 8, 12 mA        | -8 to +8                     | - mA |  |

| Storage temperature            |                | T <sub>stg</sub> | -                                         | -65 to +150                  | °C   |  |

## Absolute Maximum Ratings (V<sub>SS</sub> = 0 V, T<sub>j</sub> = 25°C) <sup>[1]</sup>

1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions in the other specifications of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Recommended Operating Conditions (V<sub>SS</sub> = 0 V)

| Parameter            | Symbol                | Rated Value  | Unit |

|----------------------|-----------------------|--------------|------|

| Power supply voltage | V <sub>DD</sub> (3 V) | +3.0 to +3.6 | V    |

| Junction temperature | Tj                    | -40 to +85   | °C   |

|                                  |               |                  |                                                                                    | R                     | ated Value         | [1]                   |      |

|----------------------------------|---------------|------------------|------------------------------------------------------------------------------------|-----------------------|--------------------|-----------------------|------|

| Parameter                        |               | Symbol           | Conditions                                                                         | Min.                  | Typ <sup>[2]</sup> | Max.                  | Unit |

| High-level input voltage         | Normal buffer | V <sub>IH</sub>  |                                                                                    | 2.0                   | -                  | V <sub>DD</sub> + 0.3 |      |

|                                  | 5-V tolerant  | V <sub>IH</sub>  |                                                                                    | 2.0                   | -                  | 5.5                   |      |

| Low-level input voltage          | Normal buffer | VIL              | V <sub>IL</sub> TTL input                                                          |                       | _                  | 0.8                   |      |

|                                  | 5-V tolerant  | V <sub>IL</sub>  | TTL input                                                                          | -0.3                  | -                  | 0.8                   |      |

| TTL- level Schmitt trigger input | Normal buffer | V <sub>t+</sub>  | TTI input                                                                          | -                     | 1.5                | 2.0                   |      |

| threshold voltage                |               | Vt-              |                                                                                    | 0.7                   | 1.0                | -                     |      |

|                                  |               | $\Delta V_t$     | V <sub>t+</sub> - V <sub>t-</sub>                                                  | 0.4                   | 0.5                | -                     |      |

| -                                | 5-V tolerant  | V <sub>t+</sub>  |                                                                                    | -                     | 1.5                | 2.0                   |      |

|                                  |               | V <sub>t</sub> - | - TTL 5-V tolerant input                                                           | 0.7                   | 1.0                | -                     | v    |

|                                  |               | ΔV <sub>t</sub>  | V <sub>t+</sub> - V <sub>t-</sub>                                                  | 0.4                   | 0.5                | -                     |      |

| High-level output voltage        | Normal buffer | V <sub>OH</sub>  | I <sub>OH</sub> = -100 μA                                                          | V <sub>DD</sub> - 0.2 | -                  | -                     |      |

|                                  |               |                  | I <sub>0H</sub> = -1, -2, -4, -6, -8, -12, -24 mA                                  | 2.4                   | -                  | -                     |      |

|                                  | 5-V tolerant  | V <sub>OH</sub>  | I <sub>OH</sub> = -100 μA                                                          | V <sub>DD</sub> - 0.2 | _                  | -                     |      |

|                                  |               |                  | I <sub>0H</sub> = -1, -2, -4, -6, -8, -12 mA                                       | 2.4                   | -                  | -                     |      |

| Low-level output voltage         | Normal buffer | V <sub>OL</sub>  | I <sub>OL</sub> = 100 μA                                                           | -                     | -                  | 0.2                   |      |

|                                  |               |                  | I <sub>0L</sub> = 1, 2, 4, 6, 8, 12, 24mA                                          | -                     | -                  | 0.4                   |      |

|                                  | 5-V tolerant  | V <sub>OL</sub>  | I <sub>OL</sub> = 100 μA                                                           | -                     | _                  | 0.2                   |      |

|                                  |               |                  | I <sub>0L</sub> = 1, 2, 4, 6, 8, 12 mA                                             | -                     | -                  | 0.4                   |      |

| High-level input current         | Normal buffer | I <sub>IH</sub>  | $V_{IH} = V_{DD}$                                                                  | -                     | 0.1                | 10                    |      |

|                                  |               |                  | $V_{IH} = V_{DD} (50-k\Omega \text{ pull-down})$                                   | 10                    | 66                 | 200                   |      |

|                                  | 5-V tolerant  | I <sub>IH</sub>  | V <sub>IH</sub> = V <sub>DD</sub>                                                  | -                     | 0.1                | 10                    |      |

|                                  |               |                  | $V_{IH} = V_{DD} (50 \text{-} \text{k}\Omega \text{ pull-down})$                   | 10                    | 66                 | 200                   | μA   |

| Low-level input current          | Normal buffer | I <sub>IL</sub>  | V <sub>IL</sub> = V <sub>SS</sub>                                                  | -10                   | -0.1               | -                     |      |

|                                  |               |                  | $V_{IL} = V_{SS} (50-k\Omega \text{ pull-up})$                                     | -200                  | -66                | -10                   |      |

|                                  |               |                  | $V_{IL} = V_{SS} (3-k\Omega \text{ pull-up})$                                      | -3.3                  | -1.1               | -0.3                  | mA   |

|                                  | 5-V tolerant  | I <sub>IL</sub>  | V <sub>IL</sub> = V <sub>SS</sub>                                                  | -10                   | -0.1               | -                     | μA   |

| 3-state output leakage current   | Normal buffer | I <sub>OZH</sub> | $V_{OH} = V_{DD}$                                                                  | -                     | 0.1                | 10                    |      |

|                                  |               |                  | $V_{OH} = V_{DD}$ (50-k $\Omega$ pull-down)                                        | 10                    | -66                | 200                   | μA   |

|                                  |               | I <sub>OZL</sub> | V <sub>OL</sub> = V <sub>SS</sub>                                                  | -10                   | -0.1               | -                     | μΛ   |

|                                  |               |                  | $V_{0L} = V_{SS} (50-k\Omega \text{ pull-up})$                                     | -200                  | -66                | -10                   |      |

|                                  |               |                  | $V_{0L} = V_{SS} (3-k\Omega \text{ pull-up})$                                      | -3.3                  | -1.1               | -0.3                  | mA   |

|                                  | 5-V tolerant  | I <sub>OZH</sub> | V <sub>OH</sub> = V <sub>DD</sub>                                                  | -                     | 0.1                | 10                    |      |

|                                  |               |                  | $V_{OH} = V_{DD}$ (50-k $\Omega$ pull-down)                                        | 10                    | 66                 | 200                   | μA   |

|                                  |               | I <sub>OZL</sub> | V <sub>0L</sub> = V <sub>SS</sub>                                                  | -10                   | -0.1               | -                     |      |

| Stand-by current <sup>[3]</sup>  |               | I <sub>DDQ</sub> | Output open, V <sub>IH</sub> = V <sub>DD</sub> , V <sub>IL</sub> = V <sub>SS</sub> | De                    | sign Depend        | ent                   | μA   |

## DC Characteristics (V<sub>DD</sub> = 3.0 to 3.6 V, V<sub>SS</sub> = 0 V, T<sub>j</sub> = -40°C to +85°C)

## AC Characteristics ( $V_{DD}$ = 3.3 V, $V_{SS}$ = 0 V, $T_j$ = 25°C)

| Parame                                           | eter                                 | Driving<br>Type | Conditions <sup>[1][2]</sup> | Rated Value [3]      | Unit |

|--------------------------------------------------|--------------------------------------|-----------------|------------------------------|----------------------|------|

| Internal gate                                    | Inverter                             | 1X              | F/O = 2, L = 0 mm            | 0.082                |      |

| propagation delay                                |                                      | 2X              | V <sub>DD</sub> = 3.3 V      | 0.068                |      |

|                                                  |                                      | 4X              |                              | 0.062                |      |

|                                                  | 2-input NAND                         | 1X              |                              | 0.14                 |      |

|                                                  |                                      | 2X              |                              | 0.13                 |      |

|                                                  | 2-input NOR                          | 1X              |                              | 0.16                 |      |

|                                                  |                                      | 2X              |                              | 0.14                 | ns   |

|                                                  | Inverter                             | 1X              | F/O = 2, L = 1 mm            | 0.19                 | 115  |

|                                                  |                                      | 2X              | $V_{DD} = 3.3 V$             | 0.13                 |      |

|                                                  |                                      | 4X              |                              | 0.097                |      |

|                                                  | 2-input NAND                         | 1X              |                              | 0.28                 |      |

|                                                  |                                      | 2X              |                              | 0.20                 |      |

|                                                  | 2-input NOR                          | 1X              |                              | 0.34                 |      |

|                                                  |                                      | 2X              |                              | 0.24                 |      |

| Toggle frequency                                 | ·                                    |                 | F/O= 1, L = 0 mm             | 1040                 | MHz  |

| Input buffer                                     | TTL level norma                      | al input buffer | F/O = 2,L = 1 mm             | 0.35                 |      |

| propagation delay                                | TTL level 5-V to                     | olerant buffer  |                              | 0.64                 |      |

| Output buffer                                    | Push-pull                            | 4 mA            | CL = 20pF                    | 2.15                 |      |

| propagation delay                                | Normal output<br>buffer              | 8 mA            | CL= 50 pF                    | 2.25                 |      |

|                                                  | builei                               | 12 mA           | CL = 100 pF                  | 2.82                 |      |

|                                                  | 3-state<br>5-V tolerant<br>buffer    | 4 mA            | CL = 20 pF                   | 2.41                 | ns   |

| Output buffer<br>transition times <sup>[4]</sup> | Push-pull<br>Normal output<br>buffer | 12 mA           | CL = 100 pF                  | 4.68 (r)<br>3.48 (f) |      |

|                                                  | 3-state<br>5-V tolerant<br>buffer    | 4 mA            | CL = 20 pF                   | 3.53 (r)<br>3.24 (f) |      |

1. Input transition time in 0.2 ns / 3.3 V.

2. Typical condition is  $V_{DD} = 3.3$  V and  $T_i = 25^{\circ}$ C.

3. Rated value is calculated as an average of the L-H and H-L delay times of each macro type on a typical process.

4. Output rising and falling times are both specified over a 10 to 90% range.

#### **MACRO LIBRARY**

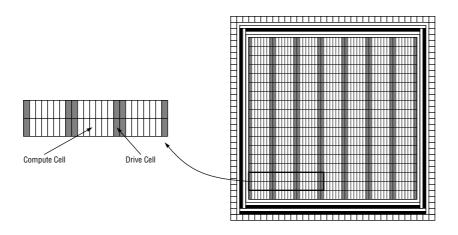

Oki Semiconductor supports a wide range of macrocells and macrofunctions, ranging from simple hard macrocells for basic Boolean operations to large, user-parameterizable macrofunctions. The following figure illustrates the main classes of macrocells and macrofunctions available.

Figure 3. Oki Macrocell and Macrofunction Library

#### **Macrocells for Driving Clock Trees**

Oki offers H-clock-tree drivers that minimize clock skew. The advanced layout software uses dynamic driver placement and sub-trunk allocation to optimize the clock-tree implementation for a particular circuit. Features of the H-clock-tree driver-macrocells include:

- True RC back annotation of the clock network

- Automatic fan-out balancing

- Dynamic sub-trunk allocation

- Single clock tree driver logic symbol

- Automatic branch length minimization

- Dynamic driver placement

- Allows multiple clock trees

Figure 4. H-Clock-Tree Structure

## **OKI ADVANCED DESIGN CENTER CAD TOOLS**

Oki's advanced design center CAD tools include support for the following:

- Floorplanning for front-end simulation, back-end layout control, and link to synthesis

- · Clock tree structures improve first-time silicon success by eliminating clock skew problems

- JTAG Boundary scan support

- Power calculation which predicts circuit power under simulation conditions to accurately model package requirements (in development)

#### Table 1: CAD Design Tools

| Vendor                                                   | Platform                                          | Operating System <sup>[1]</sup>            | Vendor Software/Revision <sup>[1]</sup>                                                                     | Description                                                                                                                                      |

|----------------------------------------------------------|---------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Cadence                                                  | HP9000, 7xx<br>IBM RS6000<br>Sun <sup>® [2]</sup> | HP-UX<br>AIX<br>SunOS, Solaris             | Composer™<br>Verilog™<br>Veritime™<br>Verifault™<br>Synergy™<br>Concept™ [3]<br>Leapfrog™                   | Design capture<br>Simulation<br>Timing analysis<br>Fault grading<br>Design synthesis<br>Design capture<br>VHDL simulation                        |

| IKOS                                                     | HP9000, 7xx,<br>Sun <sup>[2]</sup>                | HP-UX, SunOS, Solaris                      | NSIM<br>Gemini/Voyager                                                                                      | Simulation                                                                                                                                       |

| Mentor Graphics™                                         | HP9000, 7xx<br>Sun <sup>[2]</sup>                 | HP-UX<br>SunOS, Solaris                    | IDEA™<br>QuickVHDL<br>QuickSim II™<br>QuickPath™<br>QuickFault™<br>QuickGrade™<br>AutoLogic™<br>DFT Advisor | Design capture<br>VHDL simulation<br>Logic simulation<br>Timing analysis<br>Fault grading<br>Fault grading<br>Design synthesis<br>Test synthesis |

| Synopsys<br>(Interface to Mentor<br>Graphics, VIEWLogic) | IBM RS6000<br>HP9000, 7xx<br>Sun <sup>[2]</sup>   | AIX<br>HP-UX<br>SunOS, Solaris             | Design Compiler™<br>HDL/VHDL Compiler™<br>Test Compiler™<br>VSS™                                            | Compilation<br>Design synthesis<br>Test synthesis<br>VHDL simulation                                                                             |

| Model Technology, Inc.<br>(MTI)                          | HP9000, 7xx<br>Sun <sup>[2]</sup><br>PC           | HP-UX<br>SunOS, Solaris.<br>Win95/NT™      | V-System                                                                                                    | VHDL Simulation                                                                                                                                  |

| VIEWLogic                                                | PC<br>Sun <sup>[2]</sup>                          | Windows™,<br>Windows NT™<br>SunOS, Solaris | Workview Office™<br>Powerview™<br>Vantage Optium<br>Motive<br>ViewSim™ with VSO                             | Design capture<br>Simulation<br>VHDL simulation<br>Timing analysis<br>Design synthesis<br>Simulation                                             |

1. Contact Oki Application Engineering for current software versions.

2. Sun or Sun-compatible.

3. Sun and HP platform only.

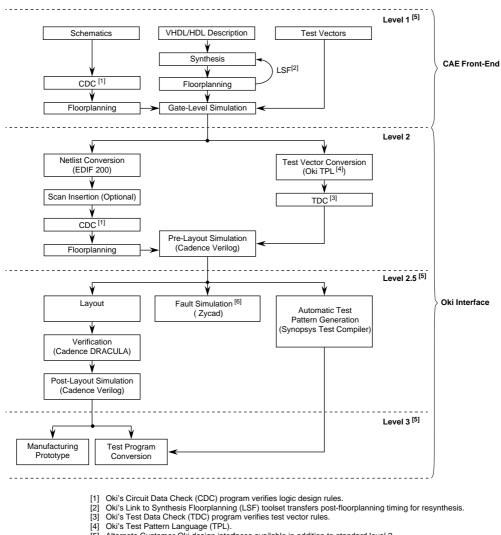

#### **Design Process**

The following figure illustrates the overall IC design process and shows the three main interface points between external design houses and Oki ASIC Application Engineering.

- [5] Alternate Customer-Oki design interfaces available in addition to standard level 2.

- [6] Standard design process includes fault simulation.

Figure 5. Oki's Design Process

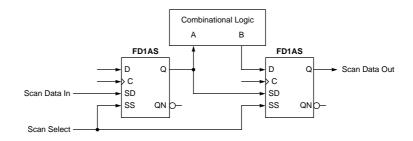

#### **Automatic Test Pattern Generation**

Oki's 0.35 µm ASIC technologies support Automatic Test Pattern Generation (ATPG) using full scanpath design techniques, including the following:

- Increases fault coverage  $\geq 95\%$

- Uses Synopsys Test Compiler

- Inserts scan structures automatically

- Connects scan chains

- Traces and reports scan chains

- Checks for rule violations

- Generates complete fault reports

- Allows multiple scan chains

- Supports vector compaction

ATPG methodology is described in detail in Oki's 0.35 µm Scan Path Application Note.

Figure 6. Full Scan Path Configuration

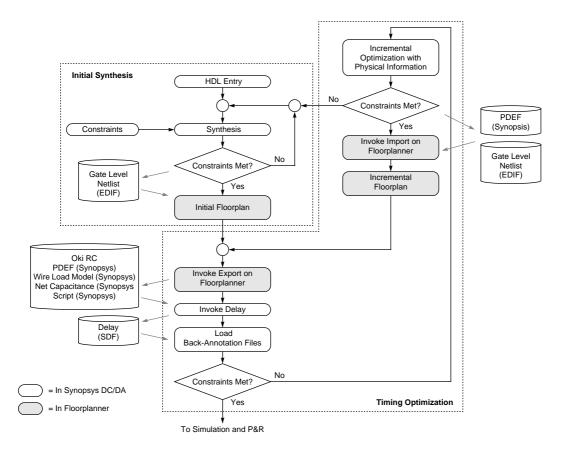

#### **Floorplanning Design Flow**

Oki offers three floorplanning tools for high-density ASIC design. The two main purposes for Oki's floorplanning tool are to:

- Ensure conformance of critical circuit performance specifications

- Shorten overall design turnaround time (TAT)

The supported floorplanners are: Cadence DP3, Gambit GFP, and Oki's internal floorplanner.

In a traditional design approach with synthesis tools, timing violations after prelayout simulation are fixed by manual editing of the netlist. This process is difficult and time consuming. Also, there is no physical cluster information provided in the synthesis tool, and so it is difficult to synthesize logic using predicted interconnection delay due to wire length. Therefore, synthesis tools may create over-optimized results.

To minimize these problems, Synopsys proposed a methodology called Links to Layout (LTL). Based on this methodology, Oki developed an interface between Oki's floorplanners and the Synopsys environment, called Link Synopsys to Floorplanner (LSF). Because not all Synopsys users have access to the Synopsys Floorplan Management tool, Oki developed the LSF system to support both users who can access

#### MSM13Q0000/14Q0000

Synopsys Floorplan Management and users who do not have access to Synopsys Floorplan Management.

More information on OKI's floorplanning capabilities is available in Oki's Application Note, Using Oki's Floorplanner: Standalone Operation and Links to Synopsys.

Figure 7. LSF System Design Flow

#### **IEEE JTAG Boundary Scan Support**

Boundary scan offers efficient board-level and chip-level testing capabilities. Benefits resulting from incorporating boundary-scan logic into a design include:

- Improved chip-level and board-level testing and failure diagnostic capabilities

- Support for testing of components with limited probe access

- Easy-to-maintain testability and system self-test capability with on-board software

- Capability to fully isolate and test components on the scan path

- Built-in test logic that can be activated and monitored

- An optional Boundary Scan Identification (ID) Register

Oki's boundary scan methodology meets the JTAG Boundary Scan standard, IEEE 1149.1-1990. Either the customer or Oki can perform boundary-scan insertion. More information is available in Oki's *JTAG Boundary Scan Application Note*. (Contact the Oki Application Engineering Department for interface options.)

## **PACKAGE OPTIONS**

#### **TQFP & LQFP Package Menu**

| Base Array      |                         |         | TQFP    |         | LQFP    |         |         |

|-----------------|-------------------------|---------|---------|---------|---------|---------|---------|

| MSM             | I/O Pads <sup>[1]</sup> | 64      | 80      | 100     | 144     | 176     | 208     |

| 13Q/14Q0150     | 144                     | •       | •       | •       | •       |         |         |

| 13Q/14Q0230     | 176                     | •       | •       | •       | •       | •       |         |

| 13Q/14Q0340     | 208                     | •       | •       | •       | •       | •       | •       |

| 13Q/14Q0530     | 256                     |         | •       | •       | •       | о       | •       |

| 13Q/14Q0840     | 320                     |         |         | •       | о       | •       | •       |

| 13Q/14Q1020     | 352                     |         |         |         | о       | •       | •       |

| Body Size (mm)  |                         | 10 x 10 | 12 x 12 | 14 x 14 | 20 x 20 | 24 x 24 | 28 x 28 |

| Lead Pitch (mm) |                         | 0.5     | 0.5     | 0.5     | 0.5     | 0.5     | 0.5     |

1. I/O Pads can be used for input, output, bi-directional, power, or ground.

• = Available now;  $\bigcirc$  = In development

#### **PQFP** Package Menu

| Base Array      |                         | PQFP (42 Alloy) |         | PQFP (Cu-Alloy) |         |

|-----------------|-------------------------|-----------------|---------|-----------------|---------|

| MSM             | I/O Pads <sup>[1]</sup> | 128             | 160     | 208             | 240     |

| 13Q/14Q0150     | 144                     | 0               |         |                 |         |

| 13Q/14Q0230     | 176                     | 0               | 0       |                 |         |

| 13Q/14Q0340     | 208                     | •               | •       |                 |         |

| 13Q/14Q0530     | 256                     | •               | •       | •               |         |

| 13Q/14Q0840     | 320                     | •               | •       | •               | о       |

| 13Q/14Q1020     | 352                     | о               | •       | •               | о       |

| Body Size (mm)  |                         | 28 x 28         | 28 x 28 | 28 x 28         | 32 x 32 |

| Lead Pitch (mm) |                         | 0.80            | 0.65    | 0.50            | 0.50    |

1. I/O Pads can be used for input, output, bi-directional, power, or ground.

• = Available now;  $\bigcirc$  = In development

#### **BGA Package Menu**

| Base Array<br>MSM | I/O Pads <sup>[1]</sup> | 256     | 352     |

|-------------------|-------------------------|---------|---------|

| 13Q/14Q0150       | 144                     |         |         |

| 13Q/14Q0230       | 176                     | •       |         |

| 13Q/14Q0340       | 208                     | •       |         |

| 13Q/14Q0530       | 256                     | •       |         |

| 13Q/14Q0840       | 320                     | •       | •       |

| 13Q/14Q1020       | 352                     | •       | •       |

| Body Size (mm)    | •                       | 27 x 27 | 35 x 35 |

| Ball Pitch (mm)   |                         | 1.27    | 1.27    |

1. I/O Pads can be used for input, output, bi-directional, power, or ground.

• = Available now;  $\bigcirc$  = In development

■ MSM13Q0000/14Q0000 ■ ---

Notes:

The information contained herein can change without notice owing to product and/or technical improvements.

Please make sure before using the product that the information you are referring to is up-to-date.

The outline of action and examples of application circuits described herein have been chosen as an explanation of the standard action and performance of the product. When you actually plan to use the product, please ensure that the outside conditions are reflected in the actual circuit and assembly designs.

Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters outside the specified maximum ratings or operation outside the specified operating range.

Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges, including but not limited to operating voltage, power dissipation, and operating temperature.

The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g.,office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property or death or injury to humans. Such applications include, but are not limited to: traffic control, automotive, safety, aerospace, nuclear power control, and medical, including life support and maintenance.

Certain parts in this document may need governmental approval before they can be exported to certain countries. The purchaser assumes the responsibility of determining the legality of export of these parts and will take appropriate and necessary steps, at their own expense, for export to another country.

Copyright 1999 Oki Semiconductor

Oki Semiconductor reserves the right to make changes in specifications at anytime and without notice. This information furnished by Oki Semiconductor in this publication is believed to be accurate and reliable. However, no responsibility is assumed by Oki Semiconductor for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Oki.

#### **Northwest Area**

Southwest Area

785 N. Mary Avenue Sunnyvale, CA 94086 Tel: 408/720-8940 Fax: 408/720-8965

#### **North Central Area**

300 Park Blvd. Suite 365 Itasca, IL 60143 Tel: 630/250-1313 Fax: 630/250-1414

#### **Northeast Area**

138 River Road Shattuck Office Center Andover, MA 01810 Tel: 978/688-8687 Fax: 978/688-8896 2302 Martin Street Suite 250 Irvine, CA 92715 Tel: 949/752-1843 Fax: 949/752-2423

#### Southeast Area

1590 Adamson Parkway Suite 220 Morrow, GA 30260 Tel: 770/960-9660 Fax: 770/960-9682

> Oki Web Site: http://www.okisemi.com

#### For Oki Literature:

*Call toll free 1-800-OKI-6388* (6 a.m. to 5 p.m. Pacific Time)

Oki Stock No: 030319-003

#### **Corporate Headquarters**

785 N. Mary Avenue Sunnyvale, CA 94086-2909 Tel: 408/720-1900 Fax: 408/720-1918