# **OKI** Semiconductor

# MSM6789A/6789L

**SBC Solid-State Recorder IC**

#### **GENERAL DESCRIPTION**

The MSM6789A/6789L, an improved version of MSM6788, is a solid-state recorder developed using the Sub Band Coding (SBC) method.

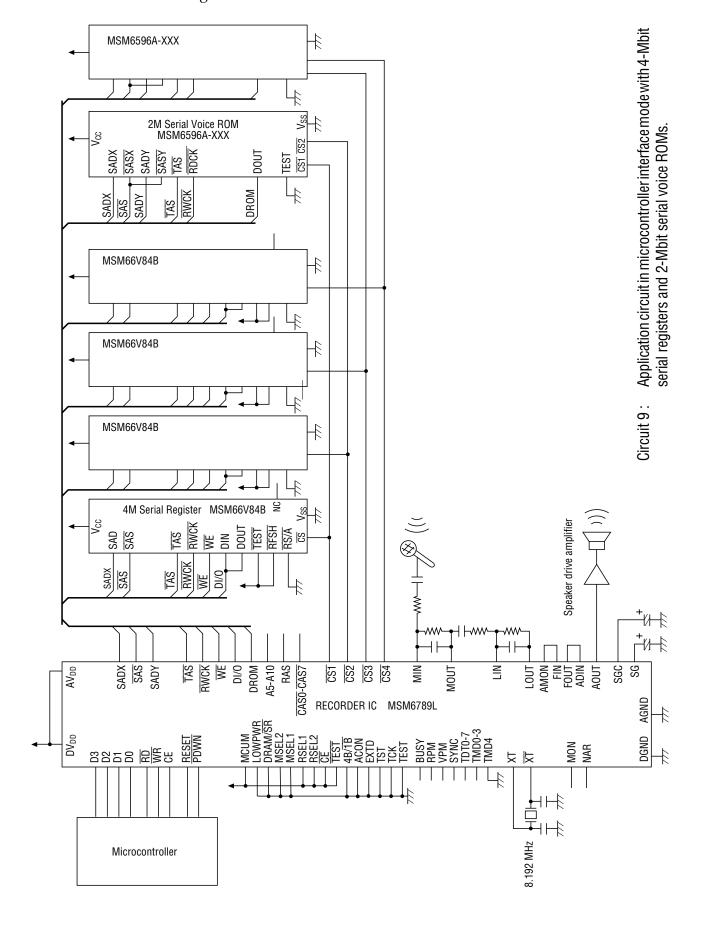

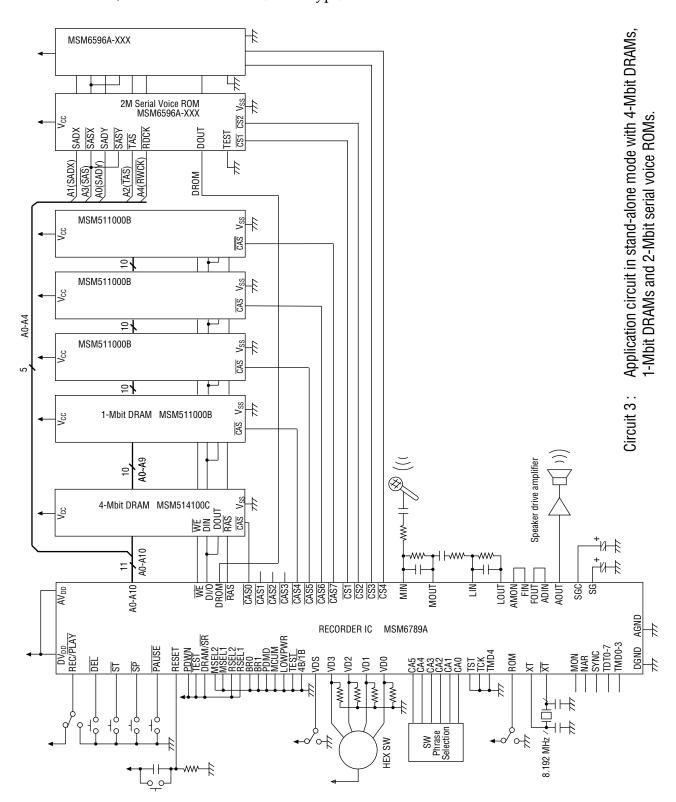

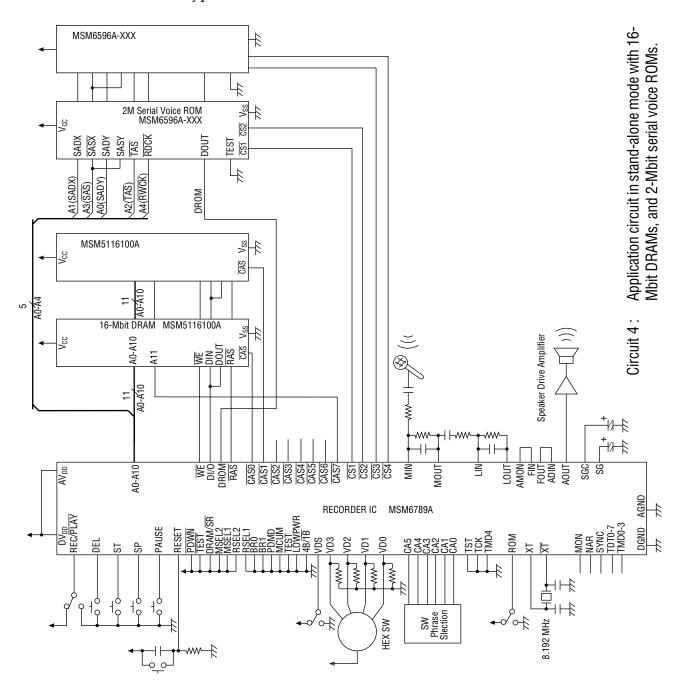

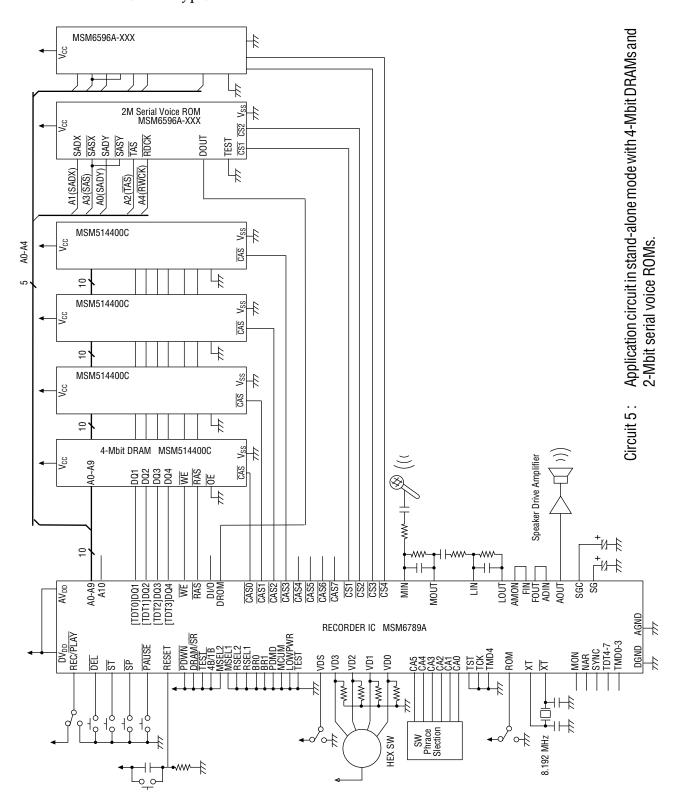

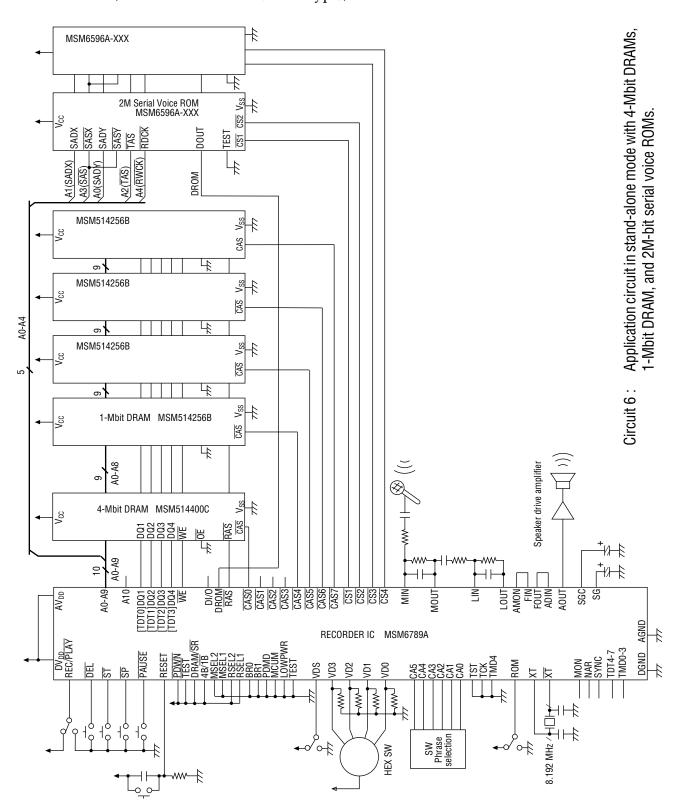

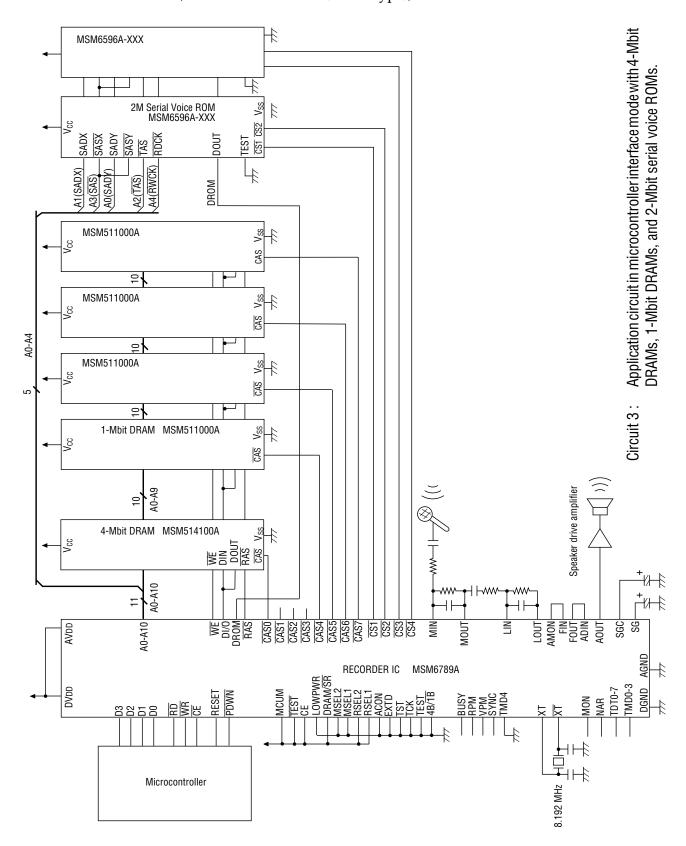

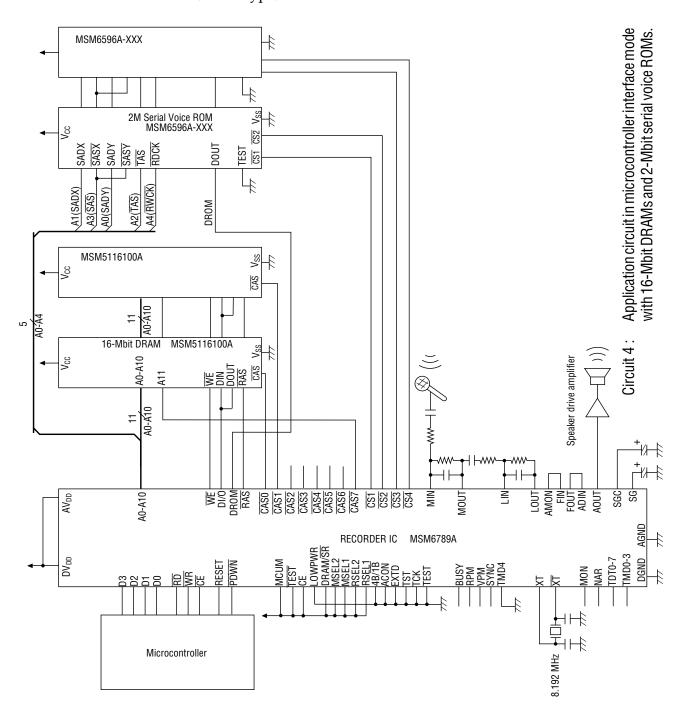

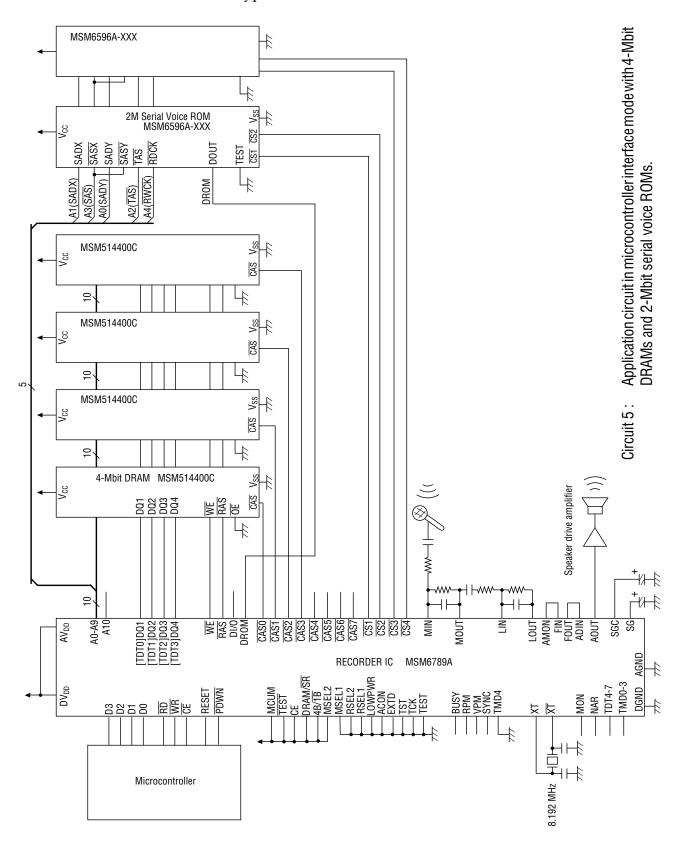

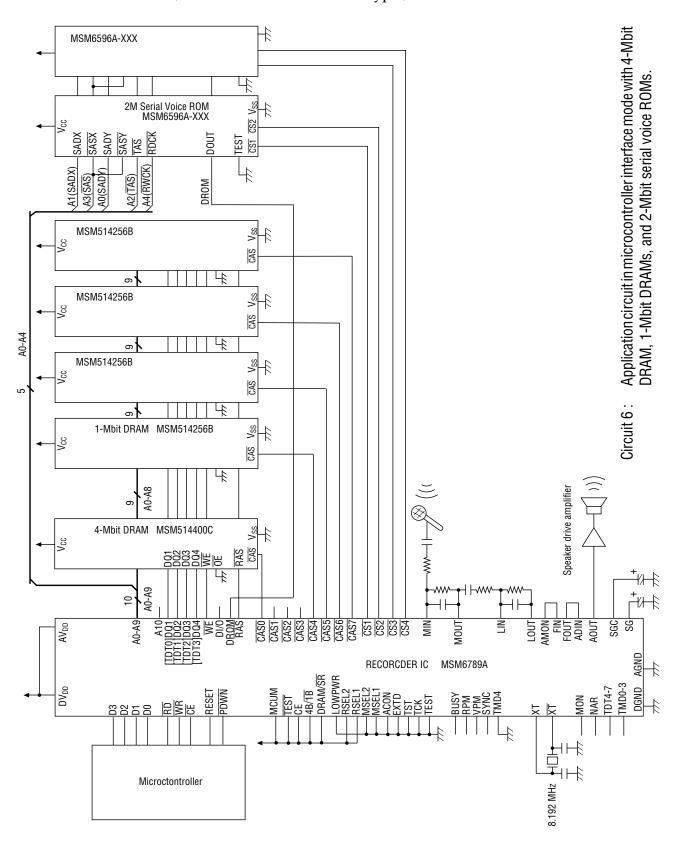

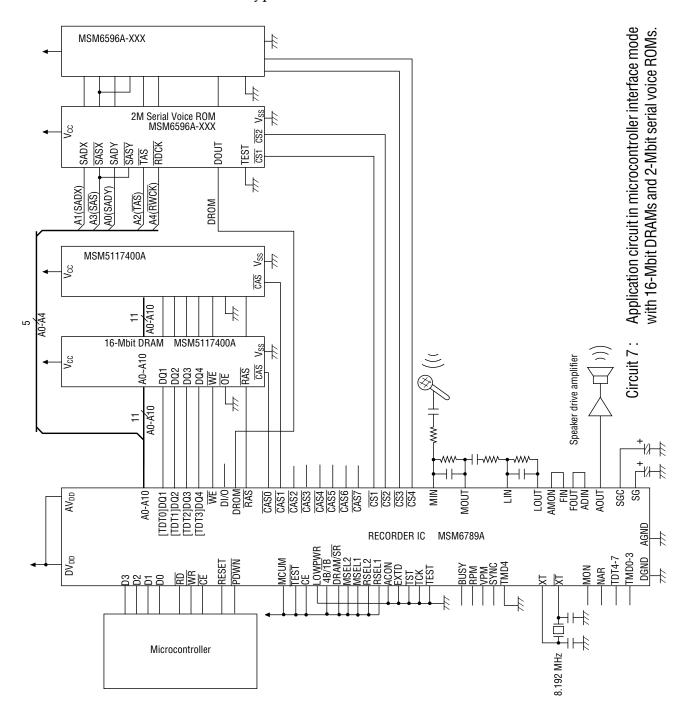

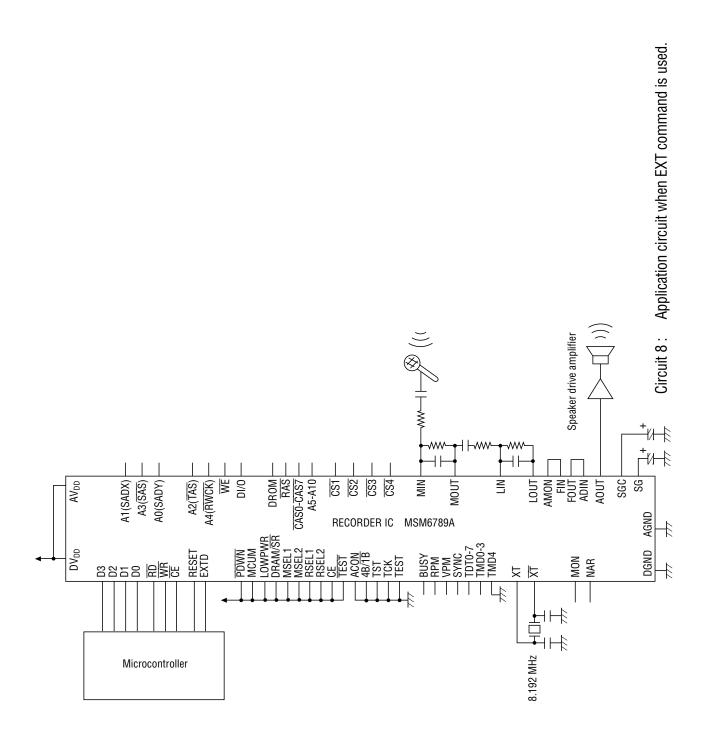

Just like MSM6788, the MSM6789A/6789L has a stand-alone mode and a microcontroller interface mode. In the stand-alone mode, record/playback conditions can be selected from pins and the MSM6789A/6789L can be controlled by a simple drive timing. In the microcontroller interface mode, record/playback can be controlled by commands from the microcontroller, and more functions are available than in the stand-alone mode.

The MSM6789A/6789L can directly drive serial voice ROM as external memory as well as serial register or general-purpose DRAM\* (1-bit × or 4-bit × type selectable) as external memories, which allows a recording and playback circuit with fixed messages to be built easily. The method from microcontroller is the same as the MSM6788.

\* Only for MSM6789A

• Difference between MSM6788 and MSM6789A

|                                    | MSM6788     | MSM6789A  |

|------------------------------------|-------------|-----------|

| General DRAM                       | Unavailable | Available |

| Unvoiced-part elimination function | No          | Yes       |

| PCM playback                       | No          | Yes       |

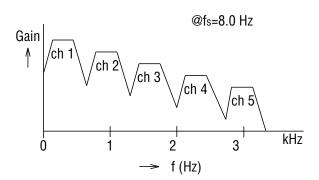

• SBC method:

The SBC method divides voice frequencies into five bands and codes the component for each of the bands separately, as shown below.

Note: This data sheet explains a stand-alone mode and a microcontroller interface mode, separately.

#### • Difference between MSM6789A and MSM6789L

| Parameter         | MSM6789A                                | MSM6789L            |

|-------------------|-----------------------------------------|---------------------|

| Operating voltage | 4.5 to 5.5 V                            | 3.0 to 3.6 V        |

| External memory   | General-purpose DRAM, 32 Mbits (max.)   | 16 Mbits (max.)     |

|                   | 1-Mbit DRAM (MSM514256B, MSM511000B)    | 4 Mbits (MSM66V84B) |

|                   | 4-Mbit DRAM (MSM514400C, MSM514100C)    |                     |

|                   | 16-Mbit DRAM (MSM511740CA, MSM5116100A) |                     |

|                   | ARAM*, 32 Mbits (max.)                  |                     |

|                   | Serial register, 32 Mbits (max.)        |                     |

|                   | 4 Mbits (MSM6684B)                      |                     |

|                   | 8 Mbits (MSM6685)                       |                     |

<sup>\*</sup> Use ARAM which has no failed bits in its first 64 Kbits.

#### STAND-ALONE MODE

#### **FEATURES**

- SBC method

- Built-in 12-bit AD converter

- Built-in 12-bit DA converter

- Built-in microphone amplifier

- Built-in low-pass filter

Attenuation characteristics -40 dB/oct

External memories

MSM6789A (5 V version)

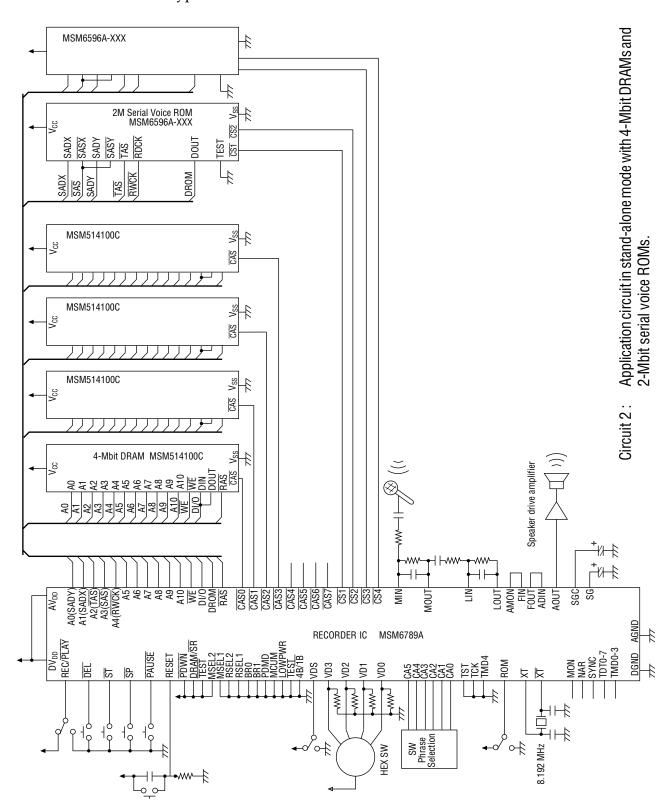

General-purpose DRAM, 32 Mbits maximum (for variable messages)

1-Mbit DRAM: Can be directly driven (MSM514256B, MSM511000B)

4-Mbit DRAM: Can be directly driven (MSM514400C, MSM514100C)

16-Mbit DRAM: Can be directly driven (MSM5117400A, MSM5116100A)

ARAM, 32 Mbits maximum (for variable messages)

Note: Use the first 64 Kbits with no failed bits for the ARAM.

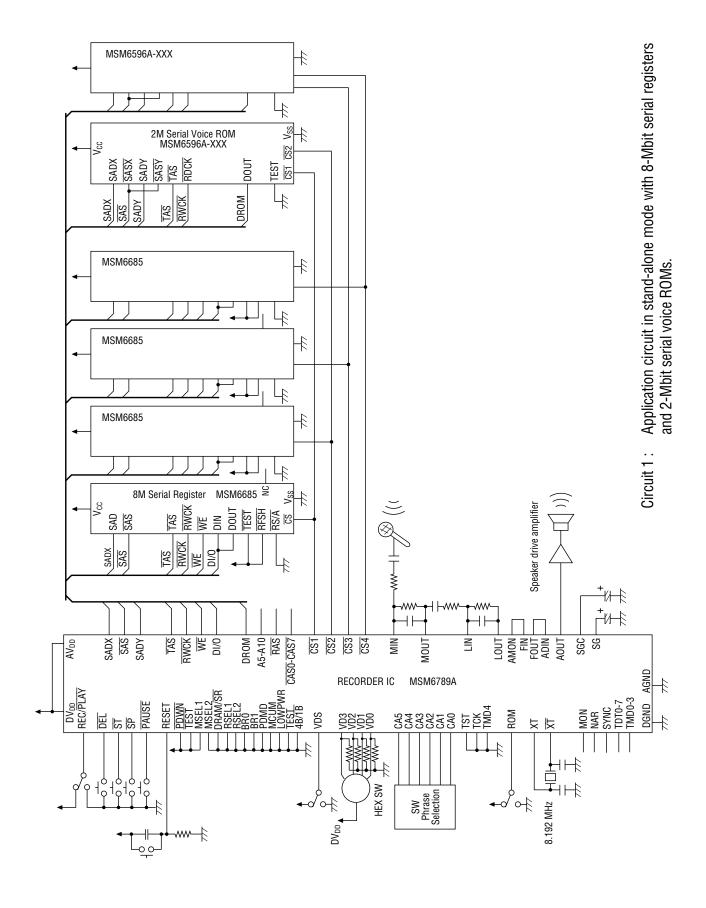

Serial register, 32 Mbits maximum (for variable messages)

4-Mbit serial register: Can be directly driven (MSM6684B)

8-Mbit serial register: Can be directly driven (MSM6685)

MSM6789L (3.3 V version)

Serial register, 16 Mbits maximum (for variable messages)

4-Mbit serial resister: Can be directly driven (MSM66V84B)

MSM6789A (5 V version) and MSM6789L (3.3 V version)

Serial voice ROM, 4 Mbits maximum (for fixed messages)

1-Mbit serial voice ROM: Can be directly driven (MSM6595A)

2-Mbit serial voice ROM: Can be directly driven (MSM6596A)

3-Mbit serial voice ROM: Can be directly driven (MSM6597A)

• Bit rate

10.0, 12.6, 16.0 kbps (at 8 kHz sampling freq.)

7.5, 9.5, 12.0 kbps (at 6 kHz sampling freq.)

Maximum recording time (when one 8-Mbit serial register is connected)

13.8 minutes (for 10.0 kbps SBC) 18.4 minutes (for 7.5 kbps SBC)

11.0 minutes (for 12.6 kbps SBC) 14.6 minutes (for 9.5 kbps SBC)

8.6 minutes (for 16.0 kbps SBC) 11.5 minutes (for 12.0 kbps SBC)

Number of phrases

63 phrases for variable messages

63 phrases for fixed messages

- Standard linear PCM playback or OKI nonlinear PCM playback can be selected.

- Voice triggered starting function (voice detect level can be set)

- Unvoiced-part elimination function (voice detect level can be set)

- Pausing function

Master clock frequency:

6.0 MHz to 8.192 MHz

• Power supply voltage:

MSM6789A: Single 5 V power supply MSM6789L: Single 3.3 V power supply

• Package options:

MSM6789A: 100-pin plastic QFP (QFP100-P-1420-BK) (Product name: MSM6789AGS-BK) MSM6789L: 100-pin plastic QFP (QFP100-P-1420-BK) (Product name: MSM6789LGS-BK)

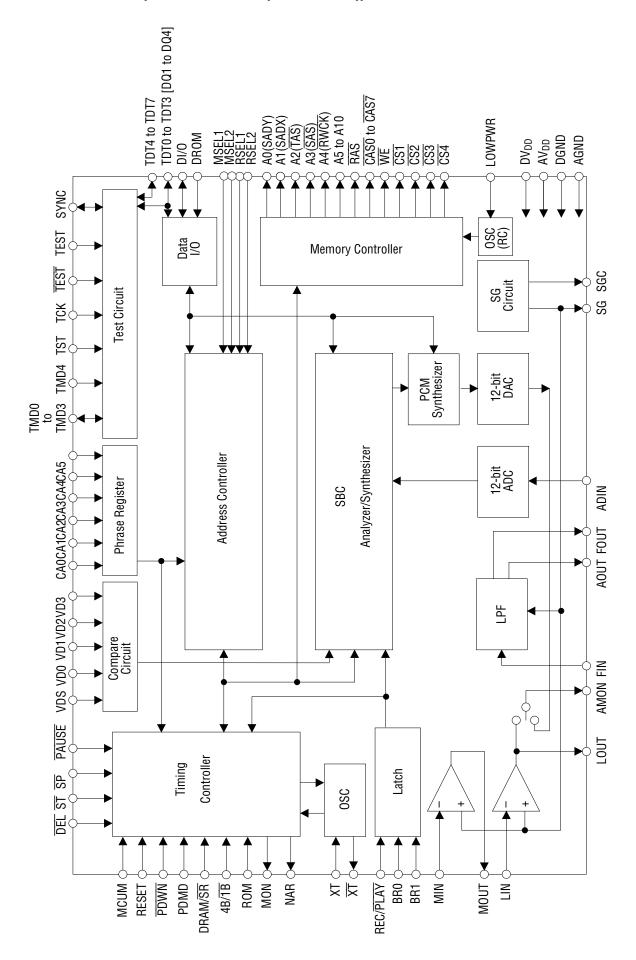

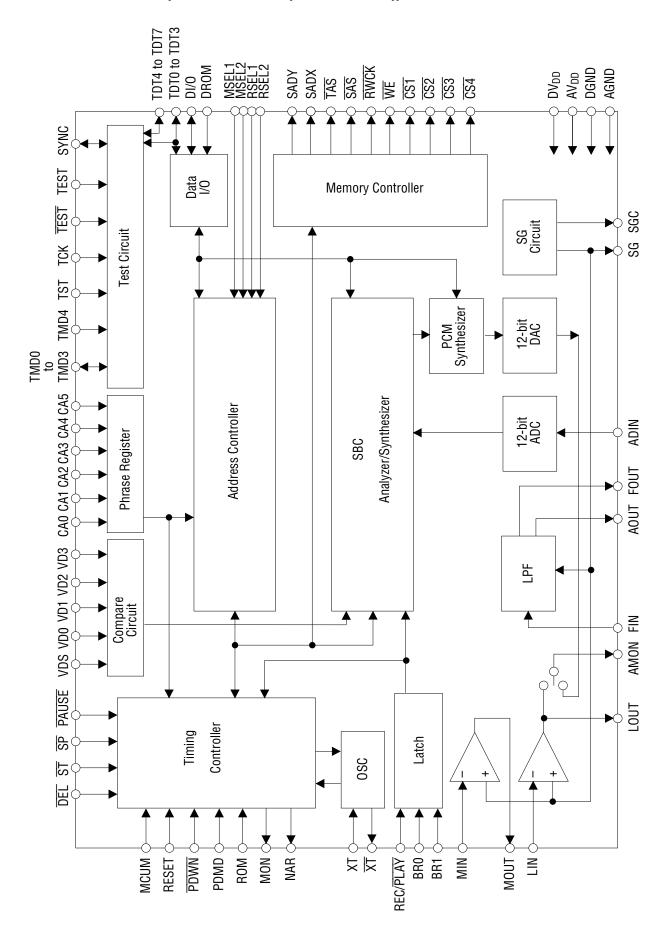

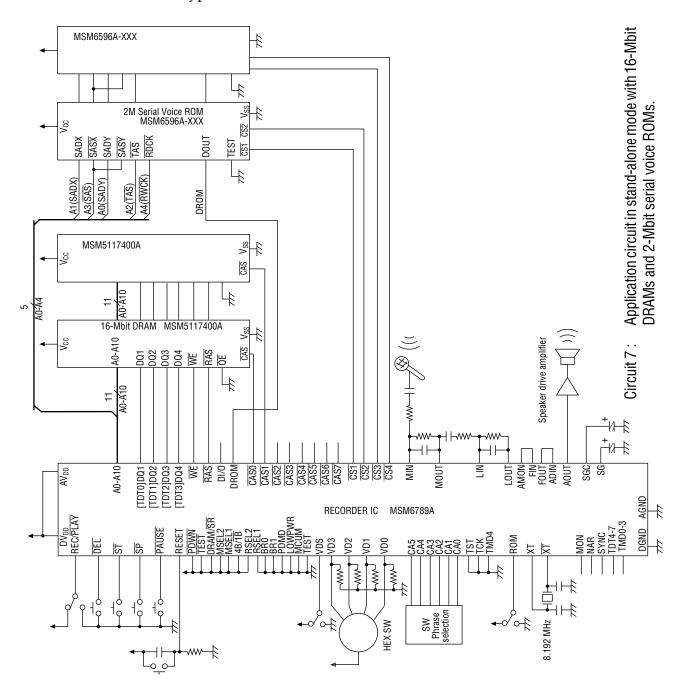

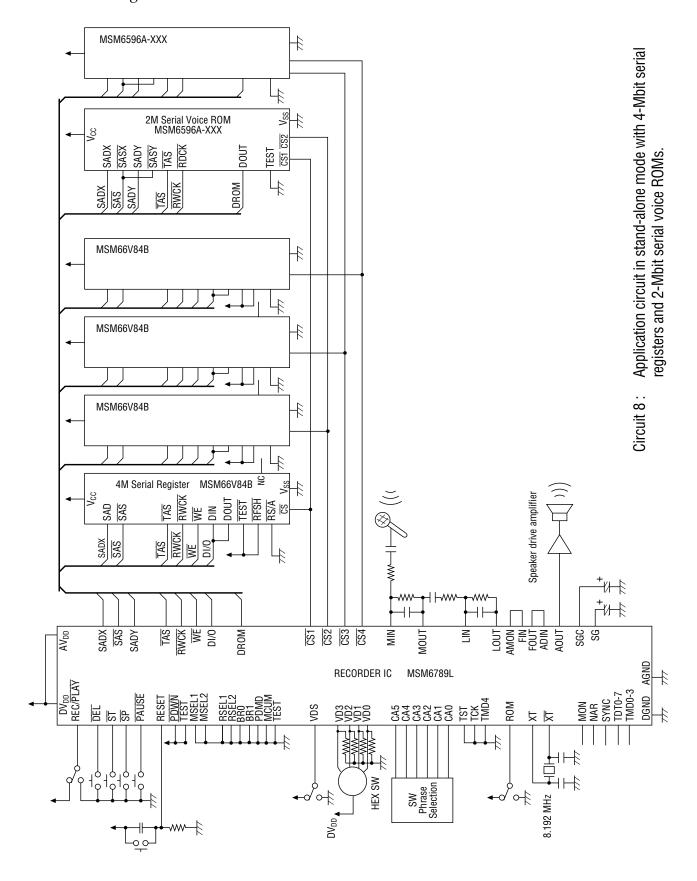

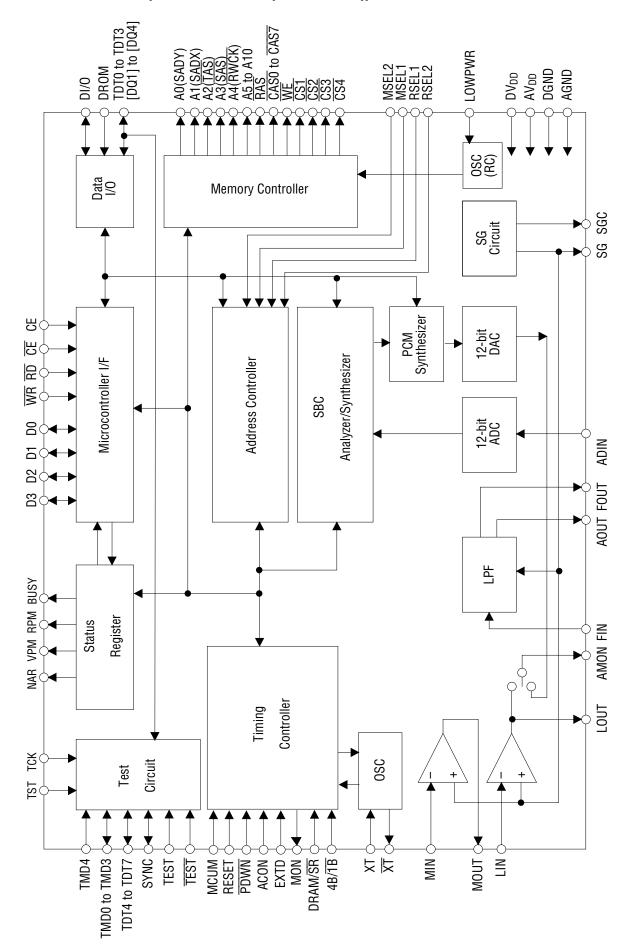

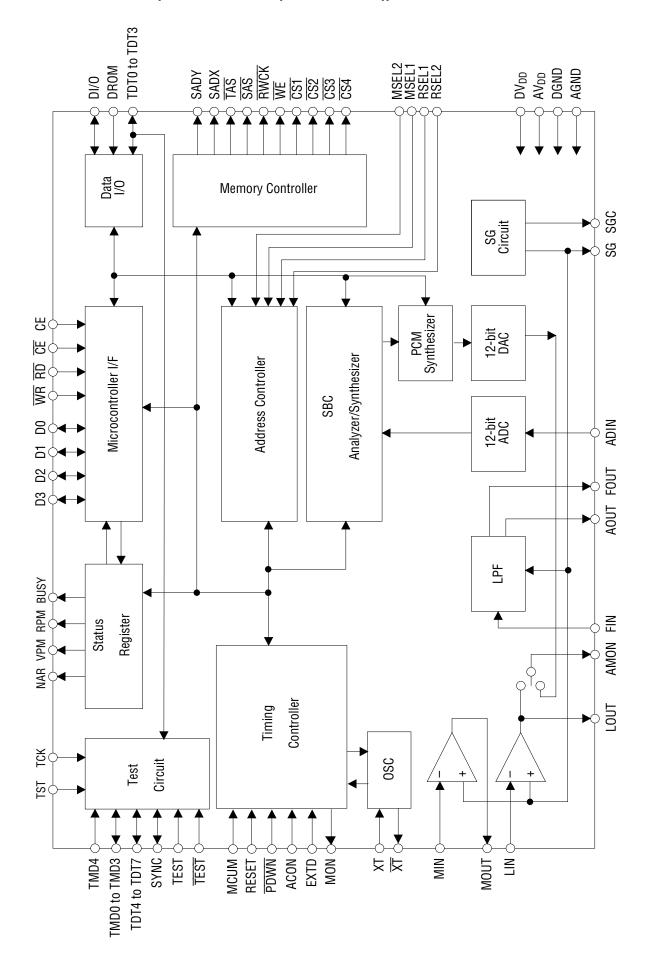

### **BLOCK DIAGRAM (for MSM6789A (5 V Version))**

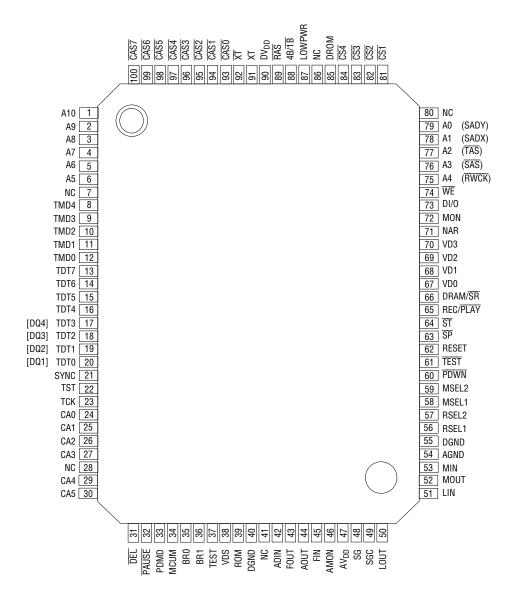

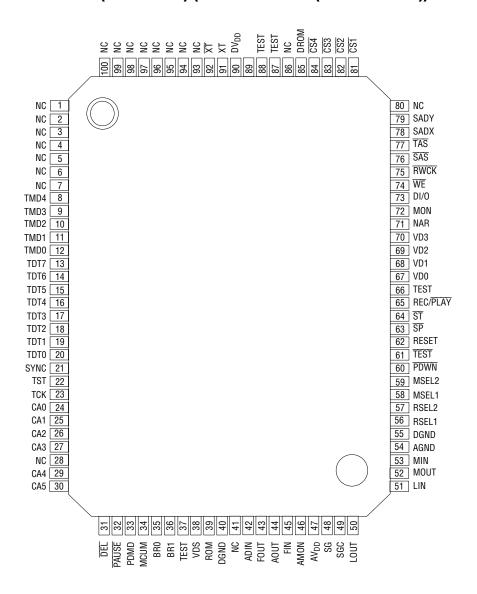

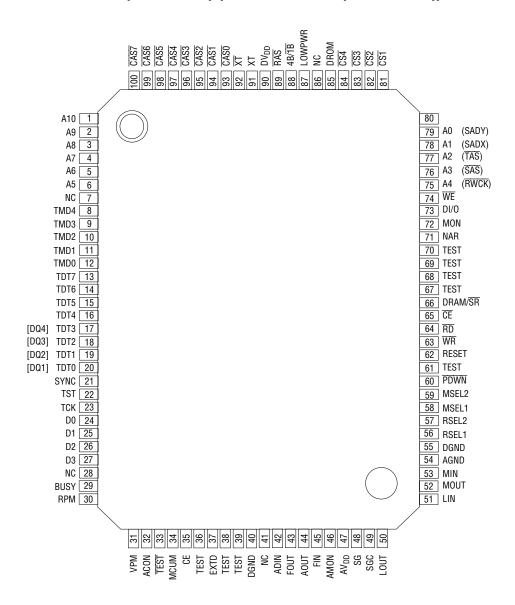

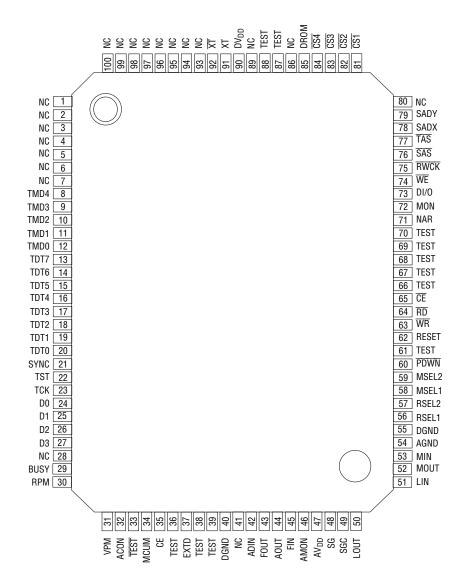

#### PIN CONFIGURATION (TOP VIEW) (for MSM6789A (5 V Version))

100-Pin Plastic QFP

( ): Pins for connecting serial voice ROM[ ]: Pins for connecting 4-bit × type DRAM

NC: No-connection pin

# PIN DESCRIPTIONS (for MSM6789A (5 V Version))

| Symbol                | Туре                                                                                                                              | Description                                                                                                                                                                                  |            |                   |          |                             |  |                                                                                        |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|----------|-----------------------------|--|----------------------------------------------------------------------------------------|

| DV                    |                                                                                                                                   | Digital power supply. Insert a bypass capacitor of 0.1 µF or more between this                                                                                                               |            |                   |          |                             |  |                                                                                        |

| DADD                  |                                                                                                                                   | pin and the DGND pin.                                                                                                                                                                        |            |                   |          |                             |  |                                                                                        |

| ۸۷٫۶۶                 |                                                                                                                                   | Analog power supply. Insert a bypass capacitor of 0.1 $\mu$ F or more between this                                                                                                           |            |                   |          |                             |  |                                                                                        |

| AVDD                  |                                                                                                                                   | pin and the AGND pin.                                                                                                                                                                        |            |                   |          |                             |  |                                                                                        |

| DGND                  | _                                                                                                                                 | Digital ground.                                                                                                                                                                              |            |                   |          |                             |  |                                                                                        |

| AGND                  | _                                                                                                                                 | Analog ground.                                                                                                                                                                               |            |                   |          |                             |  |                                                                                        |

| SG, SGC               | _                                                                                                                                 | Output for analog circuit reference voltage (signal ground).                                                                                                                                 |            |                   |          |                             |  |                                                                                        |

| MIN                   | 1                                                                                                                                 | Inverting input of the built-in OP amplifier. The non-inverting input pin is                                                                                                                 |            |                   |          |                             |  |                                                                                        |

| LIN                   | •                                                                                                                                 | internally connected to SG (signal ground).                                                                                                                                                  |            |                   |          |                             |  |                                                                                        |

| MOUT                  | 0                                                                                                                                 | Output of the built-in OP amplifier for MIN and LIN.                                                                                                                                         |            |                   |          |                             |  |                                                                                        |

| LOUT                  |                                                                                                                                   | output of the bunt-in of ampliner for white and Life.                                                                                                                                        |            |                   |          |                             |  |                                                                                        |

| ΔΜΩΝ                  | Ο                                                                                                                                 | Connected to the LOUT pin in the recording mode and to the DA converter                                                                                                                      |            |                   |          |                             |  |                                                                                        |

| AIVION                | 0                                                                                                                                 | output in the playback mode. This pin connects the built-in LPF input (FIN pin).                                                                                                             |            |                   |          |                             |  |                                                                                        |

| FIN                   | I                                                                                                                                 | Input of the built-in LPF.                                                                                                                                                                   |            |                   |          |                             |  |                                                                                        |

| FOUT                  | 0                                                                                                                                 | Output of the built-in LPF. This pin connects the AD converter input (ADIN pin).                                                                                                             |            |                   |          |                             |  |                                                                                        |

| ADIN                  | -                                                                                                                                 | Input of the built-in 12-bit AD converter.                                                                                                                                                   |            |                   |          |                             |  |                                                                                        |

| AOUT                  | 0                                                                                                                                 | Output of the built-in LPF. This pin outputs playback waveforms and connects                                                                                                                 |            |                   |          |                             |  |                                                                                        |

| AUUT                  | 0                                                                                                                                 | an external speaker drive amplifier.                                                                                                                                                         |            |                   |          |                             |  |                                                                                        |

| DRAM/SR               | 66 DRAM/SR                                                                                                                        | 66 DRAM/SR I                                                                                                                                                                                 | 66 DRAM/SR | 6 DRAM/SR         |          |                             |  | This pin selects whether memory to be connected externally is DRAM or serial register. |

|                       |                                                                                                                                   |                                                                                                                                                                                              |            |                   | RAM/SR I | Low level : Serial register |  |                                                                                        |

|                       |                                                                                                                                   |                                                                                                                                                                                              |            | High level : DRAM |          |                             |  |                                                                                        |

|                       |                                                                                                                                   | This pin selects either 1-bit $	imes$ type DRAM or 4-bit $	imes$ type DRAM.                                                                                                                  |            |                   |          |                             |  |                                                                                        |

| 4B/ <del>1B</del>     | 1                                                                                                                                 | Low level : 1-bit × type                                                                                                                                                                     |            |                   |          |                             |  |                                                                                        |

|                       |                                                                                                                                   | High level : 4-bit × type                                                                                                                                                                    |            |                   |          |                             |  |                                                                                        |

| 40 (SADV)             |                                                                                                                                   | These pins connect to A0 and A1 of DRAM at the time of DRAM selection. They also                                                                                                             |            |                   |          |                             |  |                                                                                        |

| , ,                   | 0                                                                                                                                 | connect to SAD pin of serial register and serial voice ROM at the time of serial                                                                                                             |            |                   |          |                             |  |                                                                                        |

| AT (SADA)             |                                                                                                                                   | register selection. These pins output leading addresses of read/write.                                                                                                                       |            |                   |          |                             |  |                                                                                        |

|                       |                                                                                                                                   | This pin connects to A2 of DRAM at the time of DRAM selection. It also connects                                                                                                              |            |                   |          |                             |  |                                                                                        |

| 42 ( <u>TAC</u> )     | 0                                                                                                                                 | to TAS pin of serial register and serial voice ROM at the time of serial register selection.                                                                                                 |            |                   |          |                             |  |                                                                                        |

| AZ (1A3)              | U                                                                                                                                 | This pin is used to set serial addresses from the SADX and SADY pins into the                                                                                                                |            |                   |          |                             |  |                                                                                        |

|                       |                                                                                                                                   | internal address counter of the serial register and serial voice ROM.                                                                                                                        |            |                   |          |                             |  |                                                                                        |

|                       |                                                                                                                                   | This pin connects to A3 of DRAM at the time of DRAM selection. It also connects                                                                                                              |            |                   |          |                             |  |                                                                                        |

| A3 ( <del>SAS</del> ) | 0                                                                                                                                 | to the SAS pin of the serial register and the SASX and SASY pins of the serial voice                                                                                                         |            |                   |          |                             |  |                                                                                        |

|                       |                                                                                                                                   | ROM at the time of serial register selection. Clock pin to write serial addresses.                                                                                                           |            |                   |          |                             |  |                                                                                        |

|                       |                                                                                                                                   | This pin connects to A4 of DRAM at the time of DRAM selection. It also connects                                                                                                              |            |                   |          |                             |  |                                                                                        |

| A4 (RWCK)             | 0                                                                                                                                 | to the RWCK pin of the serial register and the RDCK pin of the serial voice ROM at                                                                                                           |            |                   |          |                             |  |                                                                                        |

|                       | U                                                                                                                                 | the time of serial register selection. Clock pin to read data from and write data into                                                                                                       |            |                   |          |                             |  |                                                                                        |

|                       |                                                                                                                                   | the serial register.                                                                                                                                                                         |            |                   |          |                             |  |                                                                                        |

| ۸10-۸5                | 0                                                                                                                                 | This pin connects to pins A5-A10 of DRAM at the time of DRAM selection.                                                                                                                      |            |                   |          |                             |  |                                                                                        |

| A IU-AO               | U                                                                                                                                 | This pin outputs addresses of read/write.                                                                                                                                                    |            |                   |          |                             |  |                                                                                        |

|                       | DVDD  AVDD  DGND  AGND  SG, SGC  MIN  LIN  MOUT  LOUT  AMON  FIN  FOUT  ADIN  AOUT  DRAM/SR  4B/1B  A0 (SADY) A1 (SADX)  A2 (TAS) | DV <sub>DD</sub> —  AV <sub>DD</sub> —  DGND —  AGND —  SG, SGC —  MIN I  LIN O  AMON O  FIN I  FOUT O  ADIN I  AOUT O  DRAM/SR I   48/1B I  A0 (SADY) A1 (SADX) O  A3 (SAS) O   A4 (RWCK) O |            |                   |          |                             |  |                                                                                        |

| Symbol | Туре                                              | Description                                                                                                                                                                                                                    |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                         |  |

|--------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|

| WE     | 0                                                 | Write Enable.                                                                                                                                                                                                                  | This pin conn                               | ects to the WE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | pin of the seri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | al register and DRAM.                                                                                   |  |

| VVE    | U                                                 | This pin selects                                                                                                                                                                                                               | This pin selects either read or write mode. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                         |  |

| DIVO   | 1/0                                               | Data I/O. This                                                                                                                                                                                                                 | pin connects t                              | o the DIN and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DOUT pins of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | the serial register and                                                                                 |  |

| טווע   | 1/0                                               | DRAM. This pin                                                                                                                                                                                                                 | outputs write                               | data and inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | s read data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                         |  |

| DROM   | 1                                                 | Data ROM. Th                                                                                                                                                                                                                   | is pin connect                              | s to the DOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | pin of the seri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | al voice ROM.                                                                                           |  |

| RAS    | 0                                                 | This is a row add                                                                                                                                                                                                              | dress strobe pi                             | n of DRAM at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | the time of DR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AM selection.                                                                                           |  |

| CACO   |                                                   | These are the co                                                                                                                                                                                                               | lumn address                                | strobe pins of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DRAM at the t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ime of DRAM selection.                                                                                  |  |

|        | 0                                                 | CAS7, an addres                                                                                                                                                                                                                | ss output pin,                              | is connected t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | o pin A11 of D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RAM at the time 16-Mbit                                                                                 |  |

| UAS/   |                                                   | DRAM selection.                                                                                                                                                                                                                |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                         |  |

| CS1    |                                                   |                                                                                                                                                                                                                                |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                         |  |

| CS2    |                                                   | Chip Select. T                                                                                                                                                                                                                 | hese pins conr                              | nect to $\overline{CS}$ pin (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | of the serial req                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | gister and the $\overline{\text{CS}}$ ( $\overline{\text{CS1}}$ ,                                       |  |

| CS3    | U                                                 | $\overline{\text{CS2}}, \overline{\text{CS3}})$ pins of                                                                                                                                                                        | of the serial vo                            | ice ROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                         |  |

| CS4    |                                                   |                                                                                                                                                                                                                                |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                         |  |

| MSEL1  | 1                                                 | Those pine color                                                                                                                                                                                                               | t the consoity                              | of the memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | to he connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | and autornally                                                                                          |  |

| MSEL2  | I                                                 | These pins selec                                                                                                                                                                                                               | t the capacity                              | or the memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | to be connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | eu externally.                                                                                          |  |

|        |                                                   | •                                                                                                                                                                                                                              |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ŭ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | be connected externallly.                                                                               |  |

|        |                                                   | MSEL2                                                                                                                                                                                                                          | MSEL1                                       | RSEL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RSEL1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Memory capacity                                                                                         |  |

|        |                                                   | L                                                                                                                                                                                                                              | L                                           | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1M × 4                                                                                                  |  |

|        |                                                   | L                                                                                                                                                                                                                              | L                                           | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4M × 1                                                                                                  |  |

|        |                                                   | L                                                                                                                                                                                                                              | L                                           | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1M × 8                                                                                                  |  |

|        |                                                   | L                                                                                                                                                                                                                              | L                                           | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $1M \times 4 + 4M \times 1$                                                                             |  |

|        |                                                   | L                                                                                                                                                                                                                              | Н                                           | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4M × 2                                                                                                  |  |

|        |                                                   | L                                                                                                                                                                                                                              | Н                                           | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $4M \times 2$                                                                                           |  |

|        | l                                                 | L                                                                                                                                                                                                                              | Н                                           | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $4M \times 3$                                                                                           |  |

| RSEL2  | l                                                 | L                                                                                                                                                                                                                              | Н                                           | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $4M \times 3$                                                                                           |  |

|        |                                                   | Н                                                                                                                                                                                                                              | L                                           | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $4M \times 4$                                                                                           |  |

|        |                                                   | НН                                                                                                                                                                                                                             | L                                           | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16M × 1                                                                                                 |  |