# **OKI** semiconductor

# MSM5265

## 160-DOT LCD DRIVER

## **GENERAL DESCRIPTION**

The OKI MSM5265GS is an LCD driver which can directly drive up to 80 segments in the static display mode, while it can directly drive up to 160 segments in the 1/2 duty dynamic display mode.

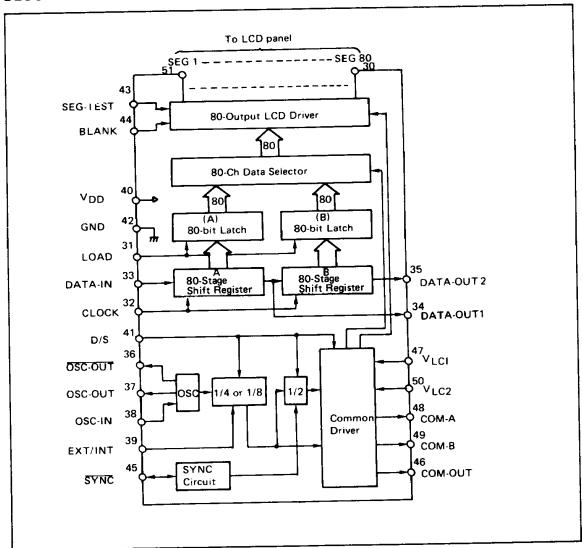

The MSM5265GS is fabricated by low power CMOS metal gate technology, consisting of 160-stage shift register, 160-bit latch, 80 sets of LCD driver and a common signal generator.

The display data is serially input from the DATA-IN terminal to the 160-stage shift register synchronized with the CLOCK pulse. The data is shifted to the 160-bit latch by the LOAD signal. Then the latched data is directly output to the LCD from the 80 sets of LCD driver as serial output,

The common signal can be generated by the on-chip generator, or can be externally input. The common synchronization circuit which is used in the dynamic display mode is integrated on the chip.

## **FEATURES**

- 80 segments display drive (in the static display mode)

- 160 segments display drive (in the dynamic display mode)

- Simple interface with microcomputer

- Bit-to-bit correspondence between input data and output data

- H : Display

- L : No display

- Cascade connection capability

- On-chip common signal generator

- Can be synchronized with the external common signal

- Testing terminals for all-on (SEG-TEST) and all-off (BLANK)

- Applicable as an output expander

- LCD driving voltage can be adjusted by the combination of V<sub>LC1</sub> and V<sub>LC2</sub>

- Supply voltage: 3.0 ∼ 6.0V

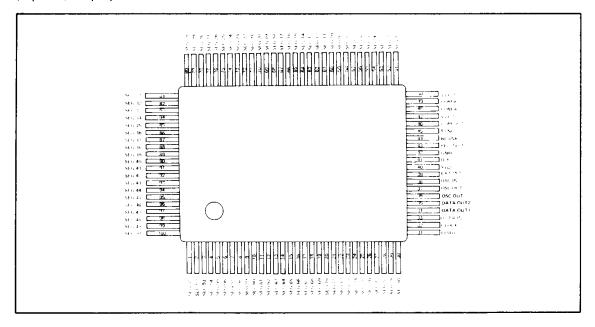

- 100 pin plastic QFP (QFP100-P-1420-K)

- 100 pin -VI plastic QFP (QFP100-P-1420-VIK)

## PIN CONFIGURATION

(Top view) 100 pin plastic QFP

# **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol           | Condition             | Limits                        | Unit |

|---------------------|------------------|-----------------------|-------------------------------|------|

| Supply voltage      | VDD              | $T_a = 25^{\circ}C$   | - 0.3 ~+ 6.5                  | ٧    |

| Input voltage       | Vı               | T <sub>a</sub> = 25°C | $GND - 0.3 \sim V_{DD} + 0.3$ | >    |

| Storage temperature | T <sub>stg</sub> | _                     | - 55 ~+ 150                   | °C   |

# **OPERATING RANGE**

| Parameter             | Symbol                             | Condition | Limits          | Unit |

|-----------------------|------------------------------------|-----------|-----------------|------|

| Supply voltage        | V <sub>DD</sub>                    |           | 3 ~ 6           | V    |

| Operating temperature | ТОР                                | _         | <b>-40 ∼85</b>  | °c   |

| LCD driving voltage   | V <sub>DD</sub> - V <sub>LC2</sub> | _         | $3 \sim V_{DD}$ | V    |

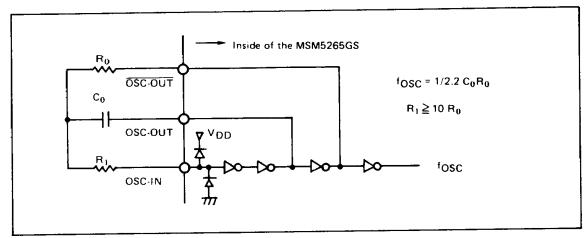

# RECOMMENDING OSCILLATION CIRCUIT CONDITION

| Parameter                  | Symbol         | Corresponding pin     | Condition        | MIN   | TYP | MAX   | Unit |

|----------------------------|----------------|-----------------------|------------------|-------|-----|-------|------|

| Oscillator resistance      | R <sub>0</sub> | 36 OSC-OUT            |                  | 56    | 100 | 220   | kΩ   |

| Oscillator capacitance     | Co             | 37 OSC-OUT            | Film capacitor   | 0.001 |     | 0.047 | μF   |

| Current limiter resistance | R <sub>1</sub> | 38 OSC-IN             | $R_1 \ge 10 R_0$ | 0.56  | 1   | 2.2   | мΩ   |

| Common signal frequency    | fсом           | 48 COM-A<br>49' COM-B | _                | 25    | _   | 150   | Hz   |

# D.C. CHARACTERISTICS

$(V_{DD} = 5.0V T_a = -40 \sim +85^{\circ}C)$

| Parameter                      | Symbol | Condition                                                                | MIN | TYP | MAX | Unit     | Applicable pin                                                    |  |

|--------------------------------|--------|--------------------------------------------------------------------------|-----|-----|-----|----------|-------------------------------------------------------------------|--|

| "H" Input<br>voltage           | VIH    |                                                                          | 3.6 |     | _   | ٧        | ļ                                                                 |  |

| "L" Input<br>voltage           | VIL    |                                                                          | -   | _   | 1.0 | ٧        | SEG-TEST, BLANK,<br>LOAD, DATA-IN, CLOCK,<br>D/S, EXT/INT, OSC-IN |  |

| Input<br>leakage<br>current    | ŀιι    | V <sub>I</sub> = 5.0V/0V                                                 | _   | _   | ±1  | μΑ       |                                                                   |  |

| "H" Output<br>voltage          | Vон    | Ι <sub>Ο</sub> = -100μΑ                                                  | 4.5 | -   | -   | V        | DATA-OUT1<br>DATA-OUT2<br>COM-OUT                                 |  |

|                                |        | I <sub>O</sub> = -200μΑ                                                  | 4.5 | _   | _   | <b>v</b> | OSC-OUT<br>OSC-OUT                                                |  |

|                                |        | V <sub>LC1</sub> = 2.5V V <sub>LC2</sub> = 0V<br>1 <sub>O</sub> = -30μΑ  | 4.8 | _   | _   | >        | SEG1 ~ SEG80                                                      |  |

|                                |        | V <sub>LC1</sub> = 2.5V V <sub>LC2</sub> = 0V<br>I <sub>O</sub> = 150µA  | 4.8 | _   | _   | ٧        | COM-A<br>COM-B                                                    |  |

| "M" Output<br>voltage          | Voм    | V <sub>LC1</sub> = 2.5V V <sub>LC2</sub> = 0V<br>I <sub>O</sub> = ±150µA | 2.3 | _   | 2.7 | ٧        | COM-A<br>COM-B                                                    |  |

| "L" Output<br>voltage          | VOL    | Ι <sub>Ο</sub> = 100μΑ                                                   | _   | _   | 0.5 | V        | DATA-OUT1<br>DATAOUT2<br>COM-OUT                                  |  |

|                                |        | ΙΟ = 200μΑ                                                               | _   | -   | 0.5 | ٧        | OSC-OUT<br>OCS-OUT                                                |  |

|                                |        | V <sub>LC1</sub> = 2.5V V <sub>LC2</sub> = 0V<br>I <sub>O</sub> = 30μA   | _   | -   | 0.2 | ٧        | SEG1 ~ SEG80                                                      |  |

| :                              |        | V <sub>LC1</sub> = 2.5V V <sub>LC2</sub> = 0V<br>I <sub>O</sub> = 150μΑ  | _   | -   | 0.2 | ٧        | COM-A<br>COM-B                                                    |  |

|                                |        | I <sub>O</sub> = 250μΑ                                                   | _   |     | 0.8 | V        | SYNC                                                              |  |

| Output<br>leakage<br>current   | lLO    | V <sub>O</sub> = 5V<br>when internal Tr is off                           | _   | _   | 5   | μΑ       | SYNC                                                              |  |

| Segment<br>output<br>impedance | RSEG   | $V_{LC1} = (5 + V_{LC2})/2$<br>$V_{LC2} = 0 \sim 2V$                     | -   | _   | 10  | kΩ       | SEG1 ~ SEG80                                                      |  |

# ■ STATIC LCD DRIVER · MSM5265 ■-

| Parameter                        | Symbol           | Condition                                                                                                   | MIN | TYP  | мах | Unit | Applicable Pin  |  |

|----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------|-----|------|-----|------|-----------------|--|

| Common output impedance          | RCOM             | $V_{LC1} = (5 + V_{LC2})/2$<br>$V_{LC2} = 0 \sim 2V$                                                        | _   | _    | 1.5 | kΩ   | COM-A<br>COM-B  |  |

| Static mode consumption current  | <sup>1</sup> DD1 | Set all input level either "H" or "L"                                                                       |     |      | 100 | μΑ   | Von             |  |

| Dynamic mode consumption current | <sup>1</sup> DD2 | No load oscillation.<br>$R_0 = 100 \text{ k}\Omega$ ,<br>$C_0 = 0.01 \mu\text{F}$ , $R_1 = 1\text{M}\Omega$ |     | 0.12 | 0.5 | mA   | V <sub>DD</sub> |  |

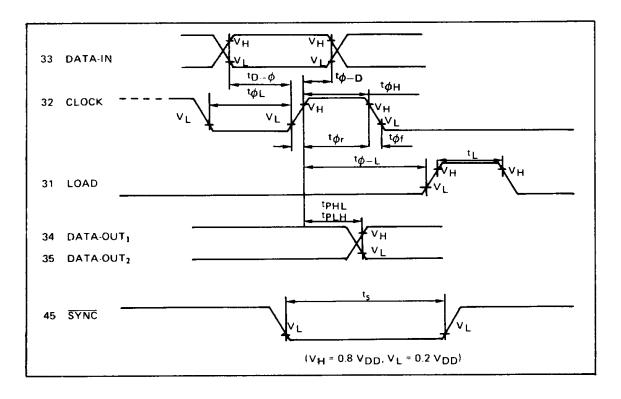

# **SWITCHING CHARACTERISTICS**

$(V_{DD} = 3.0 \sim 6.0 V T_a = -40 \sim +85^{\circ} C)$

| Parameter                       | Symbol                               | Condition                                          | MIN | MAX | Unit | Applicable Pin                  |

|---------------------------------|--------------------------------------|----------------------------------------------------|-----|-----|------|---------------------------------|

| Maximum clock frequency         | <sup>f</sup> φMAX                    |                                                    | 1   | -   | MHz  |                                 |

| Clock "H" time                  | tфн                                  | _                                                  | 0.3 | -   | μs   | CLOCK                           |

| Clock "L" time                  | tφ∟                                  |                                                    | 0.5 |     | μs   |                                 |

| Data setup time                 | tD-¢                                 | _                                                  | 0.1 | 1   | μs   | DATA—IN                         |

| Data hold time                  | t <b>ø</b> −D                        | <del>_</del>                                       | 0.1 | _   | μs   | CLOCK                           |

| "H", "L" propagation delay time | <sup>t</sup> PHL<br><sup>t</sup> PLH | When 15PF output capacitors are locaded 34 and 35. | -   | 0.8 | μs   | DATA-OUT1<br>DATA-OUT2<br>CLOCK |

| LOAD "H" time width             | tL                                   |                                                    | 0.2 | _   | μs   | LOAD                            |

| CLOCK → LOAD time               | <sup>t</sup> φ – L                   | _                                                  | 0.1 | -   | μs   | CLOCK<br>LOAD                   |

| OSC-IN Maximum input frequency  | foscmax                              | _                                                  | 5   | -   | kHz  | OSC-IN                          |

| SYNC "L" time width             | ts                                   | _                                                  | 0.2 | -   | μs   | SYNC                            |

## **FUNCTIONAL DESCRIPTION**

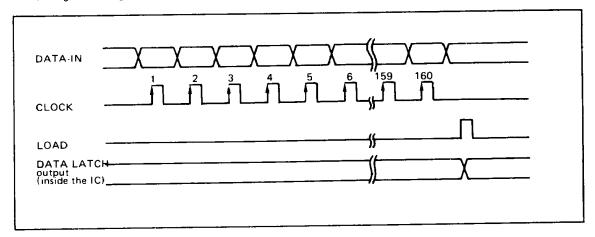

### Operational description

The MSM5265GS consists of 160-stage shift register, 160-bit latch, and 80 sets of LCD driver. The display data is input from the DATA-IN terminal to the 160-stage shift register at the rising edge of the

CLOCK pulse and it is shifted to the 160-bit latch when the LOAD signal is set at "H" level, then it is directly output to the LCD panel from the 80 sets of LCD driver.

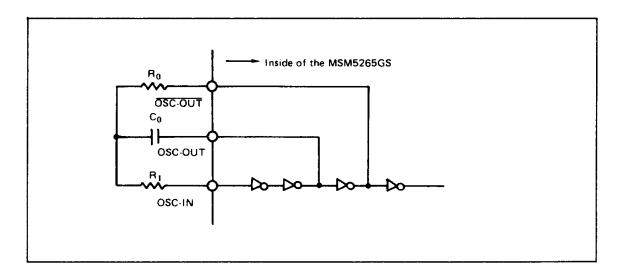

# OSC-IN, OSC-OUT, OSC-OUT

By connecting the external resistors  $R_0$ ,  $R_1$  and external capacitor  $C_1$  with OSC-IN, OSC-OUT and  $\overline{\text{OSC-OUT}}$  respectively as shown in the figure below, an oscillating circuit to generate the common signal is formed.

This frequency is divided into either 1/8 or 1/4 by the internal dividing circuit. The 1/8 divided frequency is used in the static display mode, while the 1/4 divided frequency is used as the common signal in the dynamic display mode which is output from the COM-OUT terminal. (EXT/INT should be set at low level.)

The resistor  $R_1$  is to limit the current on the OSC-IN terminal's protecting diodes. The value of the  $R_1$  should be 10 times more than that of  $R_0$ .

When the external common signal is used, the EXT/INT terminal should be set at high level and the external common signal should be input from the OSC-IN terminal.

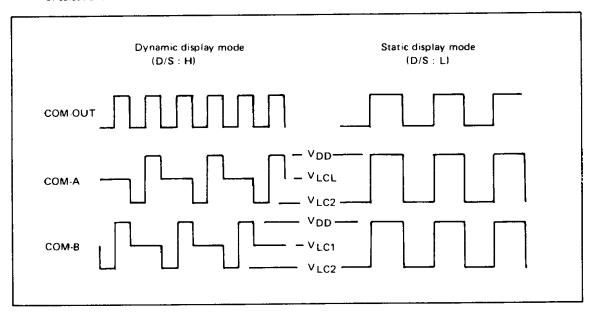

#### D/S

When this pin is set at high level, the MSM5265GS operates in the dynamic display mode, while it operates in the static display mode when this pin is set at low level.

#### EXT/INT

When the external common signal is used, this pin should be set at high level and the external common signal is to be input from the OSC-IN terminal. The input common signal is used same as the internal common signal and is output from the COM-OUT pin through the buffer.

When the on-chip common signal generator is used, this pin should be set at low level.

When the MSM5265GS is used as an output expander, this pin should be set at high level and the OSC-IN pin should be set at low level.

#### COM-OUT

When more than two MSM5265GSs are connected in a series (cascade connection), this pin should be connected with all of the slave MSM5265GS's OSC-IN terminal.

#### SYNC

This pin is an input/output pin which is used when more than two MSM5265GSs are used in a series (cascade connection) in the dynamic display mode. All of the involved MSM5265GS's SYNC pins should be connected in a same line so that they should be pulled up by the common resistor, which makes phase level of all involved MSM5265GS's COM-A terminals and COM-B terminals equal. When single MSM5265GS is used in the dynamic display mode, SYNC should be pulled up by the resistor.

In the static display mode including single MSM5265GS's operation, cascade connection and output expander operation, this pin should be set at ground level.

#### DATA-IN, CLOCK

The display data is serially input from the DATA-IN terminal to the 160-stage shift register at the rising edge of the CLOCK pulse. The high level of the display data is used to turn the display on, while low level of the display data is used to turn off the display.

#### DATA-OUT<sub>1</sub>

The 80th stage of the shift register contents is output from this pin.

When more than two MSM5265GSs are connected in a series (cascade connection) in the static display mode, this pin should be connected to the next MSM5265GS's DATA-IN terminal.

#### DATA-OUT<sub>2</sub>

The 160th stage of the shift register contents is output from this pin.

When more than two MSM5265GSs are connected in a series (cascade connection) in the dynamic display mode, this pin should be connected to the next MSM5265GS's DATA-IN terminal.

#### LOAD

The signal for latching the shift register contents is input from this pin.

When LOAD pin is set at high level, the shift register contents is shifted to the 80 sets of the LCD driver. When this pin is set at low level, the last display data, which was transferred to the 80 sets of LCD driver when LOAD pin was set at high level, is held.

### V<sub>LC2</sub>

Supply voltage pin for the 80 sets of LCD driver. The input level to this pin should be the low level output voltage of segment output (SEG1  $\sim$  SEG80) and common output (COM-A, COM-B).

In this case, the high level of segment output and common output is  $V_{DD}$  level, while low level of segment output and common output is  $V_{LC2}$  level.  $V_{LC2}$  should be set at more than ground level.

# VLC1

Supply voltage pin for the middle level voltage of the common output. The input level of this pin is the middle level output voltage of the common output (COM-A, COM-B) in the dynamic display mode.

The value of the  $V_{LC1}$  is calculated by the following formula

$$V_{LC1} = (V_{DD} + V_{LC2})/2$$

In the static display mode, this pin should be set at open level.

## COM-A, COM-B

LCD driving common signal is output from these pins and these pins should be connected to the common side of the LCD panel.

- In the static display mode

Same phase pulse as COM-OUT terminal is output from both of COM-A and COM-B. In this case high level is V<sub>DD</sub> level and low level is V<sub>LC2</sub> level.

- In the dynamic display mode

The COM-A and COM-B output signal are alternately changed within each COM-OUT output cycle, resulting in alternately repetition of select and non-select modes.

In the select mode the, same phase level as the COM-OUT signal is output.

In this case,  $V_{DD}$  or  $V_{LC2}$  is output at high level or low level respectively. In the non-select mode,  $V_{LC1}$  is output at the middle level. In the select mode of COM-A (non-select mode of COM-B), the 1st  $\sim$ 80th latched data contents are output from the 80 sets of LCD driver to the LCD panel.

In the select mode of COM-B (non-select mode of COM-A), the 81st  $\sim$  160th latched data contents are output from the 80 sets of LCD driver to the LCD panel.

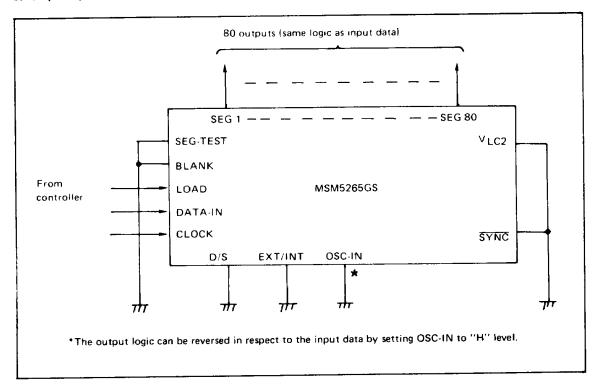

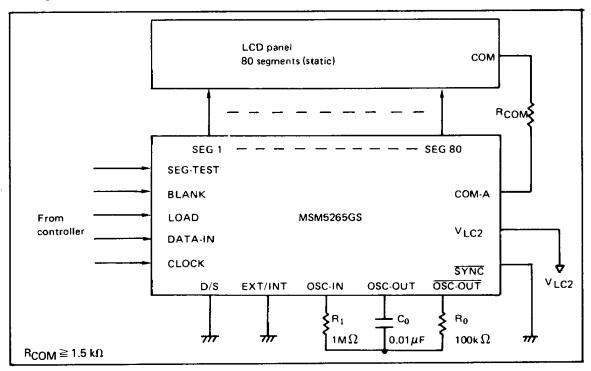

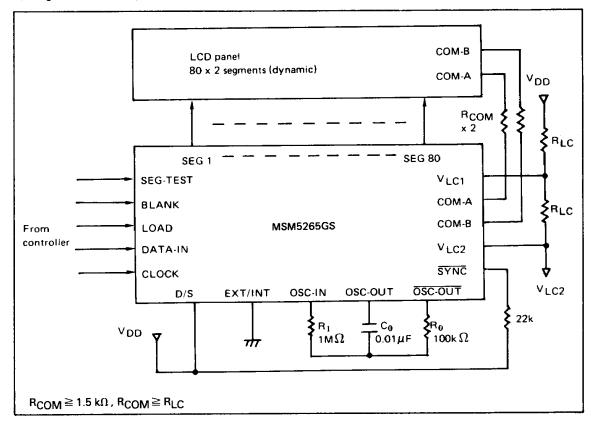

## **APPLICATION CIRCUIT**

1) Single MSM5265GS operation in the static display mode.

2) Single MSM5265GS operation in the dynamic display mode.

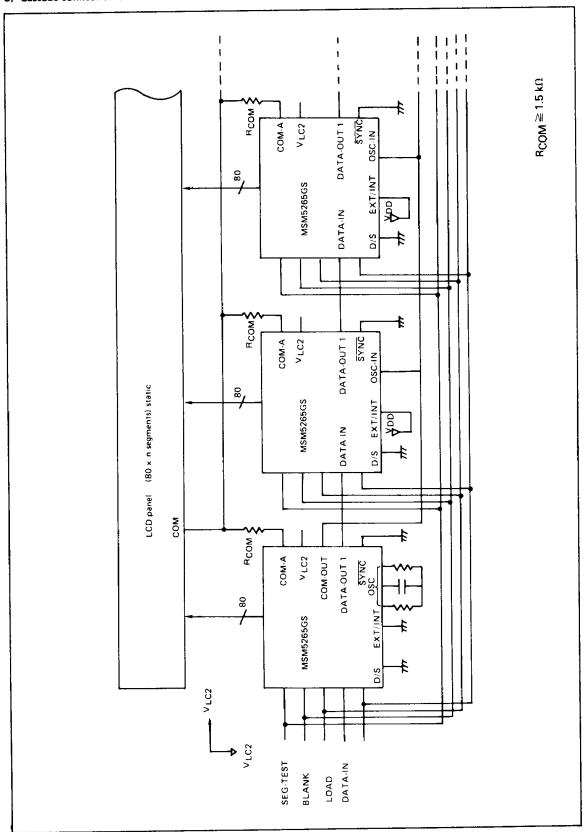

# 3) Cascade connection of MSM5265GSs in the static display mode.

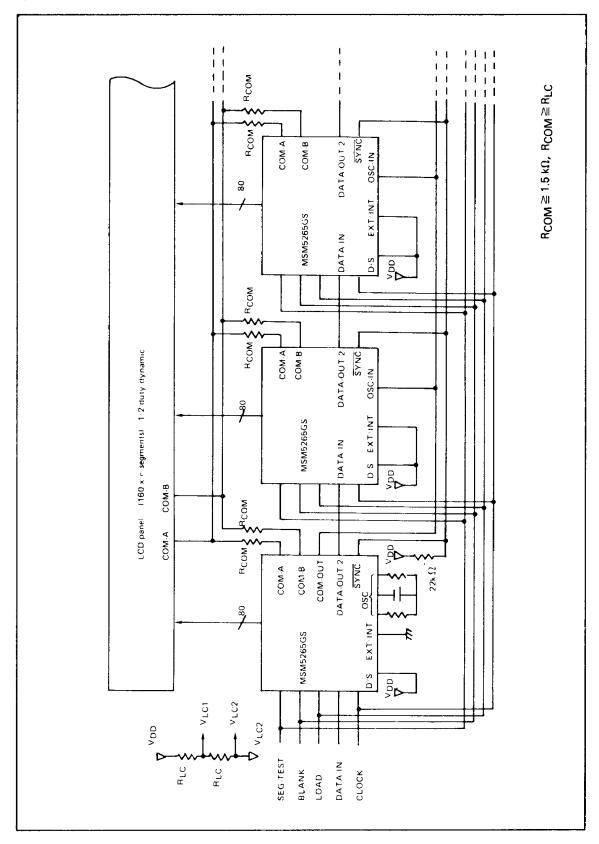

## 4) Cascade connection of MSM5265GSs in the dynamic display mode.

# 5) Output-expander