# Advance Information CMI Coder/Decoder

The MC100SX1230 device consists of a Binary to CMI Coder and CMI to Binary Decoder with integrated loop back capability. The device is designed for CMI (Code Mark Inversion) interfaces in transmission applications supporting either 139.26 Mbit/s E4 or 155.52 Mbit/s STM1 line rates.

- Binary-to-CMI Coder and CMI-to-Binary Decoder

- Internal Loop Back Test Capability

- Supports SDH or PDH Applications

- Low Power

- Fully Differential 100K Compatible I/O

- VBB Reference Available

- 75kΩ Input Pulldown Resistors

- +5V PECL or -5V ECL Operation

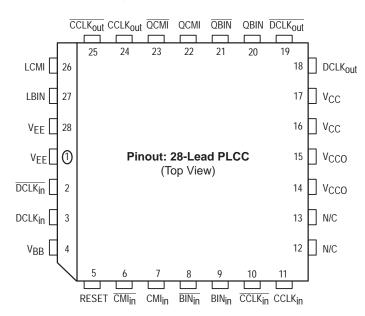

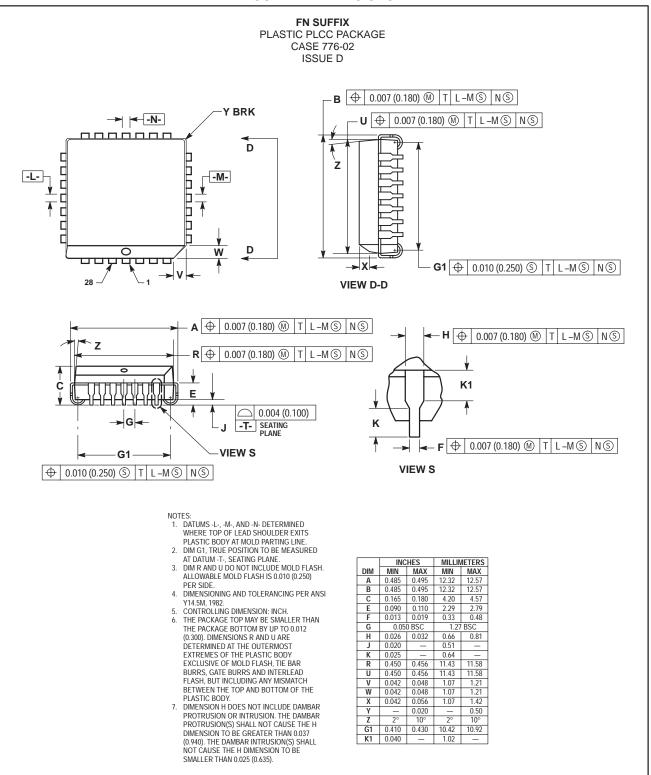

- 28-Pin Surface Mount PLCC Package

- Asynchronous Reset

In normal operation, the coder and decoder operate independently. Both the coder and decoder operate from a 2X line rate clock. The device incorporates test circuitry to support loop back bypass so either the coder input can be routed to the decoder output or the decoder input can be routed to the coder output. The part is fabricated using Motorola's proven MOSAIC III<sup>TM</sup> advanced bipolar process.

The device provides a V<sub>BB</sub> output for accepting single-ended inputs. The V<sub>BB</sub> pin should only be used as a bias for the MC100SX1230 as its current sink/source capability is limited. Whenever used, the V<sub>BB</sub> pin should be bypassed to ground via a  $0.01\mu$ F capacitor.

# **CMI CODER/DECODER**

#### **PIN NAMES**

| Pins                                            | Function                                                                                          |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------|

| CMI <sub>in</sub> , <u>CMI<sub>in</sub></u>     | CMI Input to Decoder                                                                              |

| DCLK <sub>in</sub> , <u>DCLK<sub>in</sub></u>   | Decoder Clock Input                                                                               |

| QBIN, <u>QBIN</u>                               | Binary Output From Decoder                                                                        |

| DCLK <sub>out</sub> , <u>DCLK<sub>out</sub></u> | Decoder Clock Output                                                                              |

| BIN <sub>in</sub> , BIN <sub>in</sub>           | Binary Input to Coder                                                                             |

| CCLK <sub>in</sub> , CCLK <sub>in</sub>         | Coder Clock Input                                                                                 |

| QCMI, QCMI                                      | CMI Output from Coder                                                                             |

| CCLK <sub>out</sub> , CCLK <sub>out</sub>       | Coder Clock Output                                                                                |

| RESET<br>LBIN<br>LCMI                           | Asynchronous Reset<br>Control Input for Binary<br>Loop Back<br>Control Input for CMI<br>Loop Back |

MOSAIC III is a trademark of Motorola, Inc.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

4/94

L

| FUNCTION TABL | Е |

|---------------|---|

|---------------|---|

| RESET | LBIN | LCMI | Function                                                                                      |

|-------|------|------|-----------------------------------------------------------------------------------------------|

| Н     | Х    | Х    | Reset, All Output Pairs Set to Logic Low State                                                |

| L     | L    | L    | Independent Coder and Decoder Operation                                                       |

| L     | L    | н    | CMI Input Routed to Coder Output                                                              |

| L     | Н    | L    | Binary Input and Clock Routed to Decoder Outputs<br>Alarm Indication Signal Output from Coder |

| L     | Н    | Н    | Illegal, Undefined Operation                                                                  |

#### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

| Symbol         | Parameter                            | Value       | Unit |

|----------------|--------------------------------------|-------------|------|

| VEE            | Power Supply (V <sub>CC</sub> = 0V)  | -8 to 0     | Vdc  |

| VI             | Input Voltage (V <sub>CC</sub> = 0V) | 0 to -6     | Vdc  |

| IOUT           | Output Current Continuou<br>Surg     |             | mA   |

| T <sub>A</sub> | Operating Temperature Range          | 0 to +85    | °C   |

| VEE            | Operating Range <sup>2</sup>         | -5.7 to 4.2 | V    |

1 Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

2 Parametric values specified at: -4.2 to 5.46V

| <b>DC CHARACTERISTICS</b> ( $V_{CC} = V_{CCO} = GND$ ; $V_{EE} = -4.2$ to |

|---------------------------------------------------------------------------|

|---------------------------------------------------------------------------|

|                 |                     |       | 0°C   |       |       | 25°C  | _     | 85°C  |       |       |      |                                                                |

|-----------------|---------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|----------------------------------------------------------------|

| Symbol          | Characteristic      | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit | Condition                                                      |

| VOH             | Output HIGH Voltage | -1025 | -955  | -880  | -1025 | -955  | -880  | -1025 | -955  | -880  | mV   | V <sub>in</sub> = V <sub>IH(max)</sub> or V <sub>IL(min)</sub> |

| VOL             | Output LOW Voltage  | -1810 | -1705 | -1620 | -1810 | -1705 | -1620 | -1810 | -1705 | -1620 | mV   | V <sub>in</sub> = V <sub>IH(max)</sub> or V <sub>IL(min)</sub> |

| VOHA            | Output HIGH Voltage | -1035 |       |       | -1035 |       |       | -1035 |       |       | mV   | $V_{in} = V_{IH(max)} \text{ or } V_{IL(min)}$                 |

| VOLA            | Output LOW Voltage  |       |       | -1610 |       |       | -1610 |       |       | -1610 | mV   | $V_{in} = V_{IH(max)} \text{ or } V_{IL(min)}$                 |

| VIH             | Input HIGH Voltage  | -1165 |       | -880  | -1165 |       | -880  | -1165 |       | -880  | mV   |                                                                |

| VIL             | Input LOW Voltage   | -1810 |       | -1475 | -1810 |       | -1475 | -1810 |       | -1475 | mV   |                                                                |

| V <sub>BB</sub> | Reference Voltage   | -1380 |       | -1260 | -1380 |       | -1260 | -1380 |       | -1260 | V    |                                                                |

| Ιн              | Input HIGH Current  |       |       | 200   |       |       | 200   |       |       | 200   | μΑ   |                                                                |

| ۱               | Input LOW Current   | 0.5   |       |       | 0.5   |       |       | 0.5   |       |       | μΑ   |                                                                |

| IEE             | Supply Current      | 61    |       | 122   | 61    |       | 122   | 70    |       | 141   | mA   |                                                                |

1. 100SX circuits are designed to meet the DC specifications shown in the table after thermal equilibrium has been established. The circuit is mounted in a test socket or mounted on a printed circuit board and transverse air greater than 500lfm is maintained.

2. All outputs are loaded with 50  $\Omega$  to V\_CC – 2V.

### AC CHARACTERISTICS ( $V_{CC} = V_{CCO} = GND$ ; $V_{EE} = -4.2$ to 5.46V)

|                                 |                      |                                                                                                                                                                                                                                                             | 0 to 85°C                                 |     | с                                            |      |                                                                                                                   |                                                                                                                                                                                  |

|---------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----|----------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                          | Cha                  | aracteristic                                                                                                                                                                                                                                                | Min                                       | Тур | Max                                          | Unit | Condition                                                                                                         | Notes                                                                                                                                                                            |

| F <sub>max</sub>                |                      |                                                                                                                                                                                                                                                             | 700                                       |     |                                              | MHz  |                                                                                                                   |                                                                                                                                                                                  |

| <sup>t</sup> pd                 | Propagation<br>Delay | CCLK <sub>in</sub> to CCLK <sub>out</sub><br>CCLK <sub>in</sub> to QCMI<br>DCLK <sub>in</sub> to DCLK <sub>out</sub><br>DCLK <sub>in</sub> to QBIN<br>CCLK <sub>in</sub> to DCLK <sub>out</sub><br>CCLK <sub>in</sub> to QBIN<br>DCLK <sub>in</sub> to QCMI | 650<br>1000<br>550<br>1000<br>1100<br>800 |     | 1550<br>1750<br>1700<br>1800<br>2700<br>1700 | ps   | LCMI=LBIN='L'<br>LCMI=LBIN='L'<br>LCMI=LBIN='L'<br>LCMI='L', LBIN='H'<br>LCMI='L', LBIN='L'<br>LCMI='H', LBIN='L' | Add 3 CCLK <sub>in</sub> -Cycles to Delay<br>Add 4 DCLK <sub>in</sub> -Cycles to Delay<br>Add 3 CCLK <sub>in</sub> -Cycles to Delay<br>Add 5 DCLK <sub>in</sub> -Cycles to Delay |

| ts                              | Setup Time           | BIN <sub>in</sub> to CCLK <sub>in</sub><br>CMI <sub>in</sub> to DCLK <sub>in</sub>                                                                                                                                                                          | –375<br>140                               |     |                                              | ps   |                                                                                                                   |                                                                                                                                                                                  |

| th                              | Hold Time            | CCLK <sub>in</sub> to BIN <sub>in</sub><br>DCLK <sub>in</sub> to CMI <sub>in</sub>                                                                                                                                                                          |                                           |     | 1000<br>120                                  | ps   |                                                                                                                   |                                                                                                                                                                                  |

| VPP                             | Minimum Input Swing  |                                                                                                                                                                                                                                                             | 250                                       |     |                                              | mV   |                                                                                                                   |                                                                                                                                                                                  |

| VCMR                            | Common Mod           | e Range                                                                                                                                                                                                                                                     | -0.4                                      |     | Note                                         | V    |                                                                                                                   |                                                                                                                                                                                  |

| t <sub>r</sub> , t <sub>f</sub> | Rise/Fall Time       | s                                                                                                                                                                                                                                                           | 150                                       |     | 700                                          | ps   | 20% - 80%                                                                                                         |                                                                                                                                                                                  |

1. 100SX circuits are designed to meet the AC specifications shown in the table after thermal equilibrium has been established. The circuit is mounted in a test socket or mounted on a printed circuit board and transverse air greater than 500lfm is maintained.

2. The CMR range is referenced to the most positive side of the differential input signal. Normal operation is obtained if the HIGH level falls within the specified range and the peak-to-peak voltage lies between Vppmin and 1V. The lower end of the CMR range is dependent on V<sub>EE</sub> and is equal to V<sub>EE</sub> + 3.0V.

# MC100SX1230

# **Applications Information**

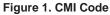

#### CMI Code

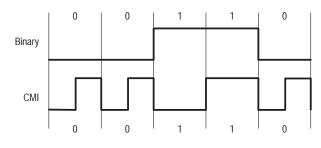

The CMI code is a 1B2B code. Each information bit is coded into two transmission bits. A binary 0 is coded to 01, and a binary 1 is coded alternately to a 00 or a 11, thus there is at least one transition during every bit period. A typical data pattern is illustrated in the figure below. Because of the coding, the data stream is not only DC balanced, but it contains a rich clock component which aids the clock recovery process at the receiver. A 2X clock is used by the MC100SX1230 to ensure that the mid-bit transition of the data 0 is ideally centered at the CMI encoded output.

#### **Typical Application**

In a traditional telecommunications application, the MC100SX1230 is resident on the line card interface which contains circuitry to implement the line transmitter and receiver functions. On the decoder side, a cable equalization filter followed by a clock recovery/decision circuit are required to compensate for the cable attenuation and distortion, extract the 2X clock signal and re-time the CMI data. On the coder side, a PLL is required to synthesize the 2X coder clock and a conditioning circuit is needed at the output of the coder to generate the appropriate signal to drive the cable.

#### **Device Operation**

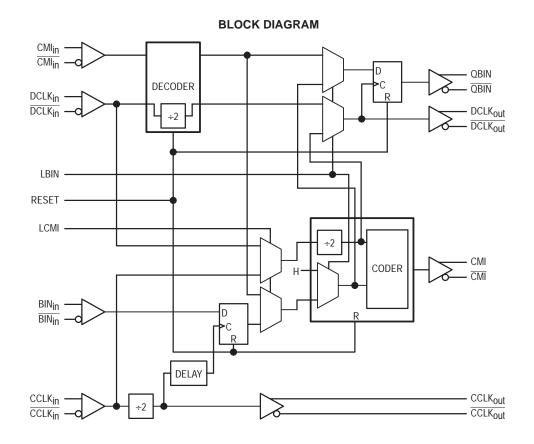

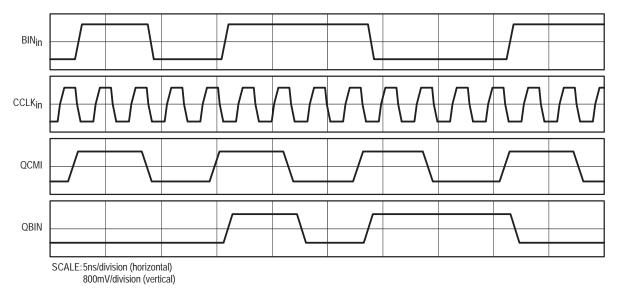

The circuit contains a complete CMI coder and decoder as well as the support circuitry necessary to perform loop back of either the Binary input or the CMI input. The operation is controlled by the LCMI and LBIN inputs. In addition, the device generates an AIS (Alarm Indication Signal) from the coder output when the binary loop back state is active (LBIN='H'). The AIS signal indicates to the receiver at the other end of the cable that 'real' data is not being sent. The device contains a Reset input which should normally be reset as part of the powering up sequence.

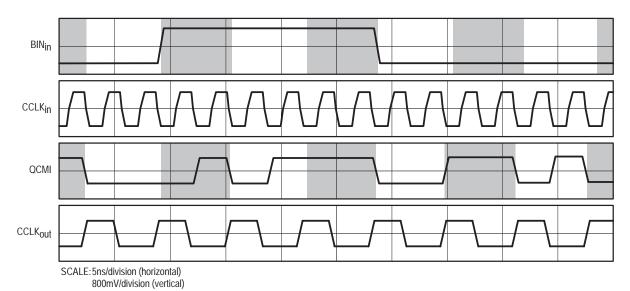

The coder accepts a differential data input (BIN<sub>in</sub>) as well as a differential clock (CCLK<sub>in</sub>). The clock signal must be twice the frequency of the input data signal, i.e. a 155 MBit/s binary signal requires a 310 MHz clock, for proper operation. Typical input and output waveforms are shown in Figure 2. The incoming clock signal is divided by 2 and supplied at the coder clock output (CLK<sub>OUt</sub>). The BINin signal is buffered before being driven into the input register which clocks in the binary data. This results in a negative setup time for the coder. The coded data is output from the coder 3 CCLK<sub>in</sub> clock cycles plus normal propagation delay after the binary data has been supplied.

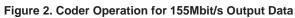

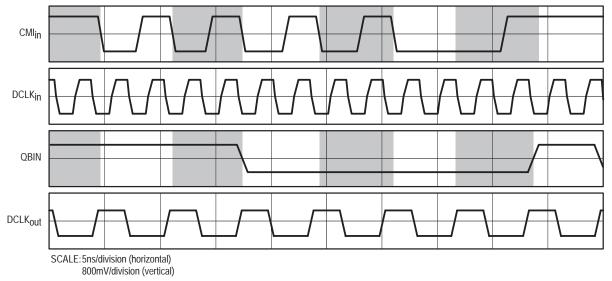

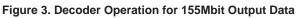

The decoder accepts a differential data input (CMI<sub>in</sub>) as well as a differential clock (DCLK<sub>in</sub>). The clock signal is supplied from the external clock extraction circuit and runs at the coded rate of either 280 MHz or 310 MHz depending on weather the application is for a PDH system or an SDH system. The decoder has a latency of 4 clock cycles so the decoded data is output 4 cycles plus the normal propagation delay after the input data is captured. Figure 3 illustrates the decoder operation.

Under certain conditions, the user may require that the binary data to be coded be routed back to the output of the decoder to verify proper system operation. This is accomplished through the use of the LBIN input control pin. When this signal is asserted (LBIN = 'H'), the BINin signal as well as a divided by 2 version of the CCLKin input is routed to the QBIN and DCLK<sub>OUt</sub> outputs respectively. The BINin to QBIN output has a latency of 3 CCLK<sub>in</sub> cycles plus internal propagation delays. In addition, the AIS signal is generated and output from the QCMI output. To the receiver the AIS signal is decoded as a constant logic 'H' signal. This operation is seen in Figure 4.

To complement the binary loop back feature, a CMI loop back function is also supported. This is accomplished by asserting the LCMI input control pin (LCMI ='H'). Under this condition, the CMI coded input is decoded, then routed through the coder block to the QCMI output. The CMIin to QCMI output has a latency of 5 DCLK<sub>in</sub> cycles plus internal propagation delays. Figure 5 shows the CMI loop back operation.

L

# MC100SX1230

## MC100SX1230

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death Motorola and Ware registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England. JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan. ASIA-PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

MC100SX1230/D

$\Diamond$