# 16M bit Synchronous Dynamic RAM 524,288-word × 16-bit × 2-bank 2,048 Refresh

P/N: MN4SV17160BT-80 MN4SV17160BT-90 MN4SV17160BT-10

The technical information described herein provides the typical characteristics and the application circuit of a respective product, not intended to guarantee or permit a license for the industrial property rights.

- Request for your special attention and precautions in using the technical information and semiconductors described in this book.

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this book and controlled under the "Foreign Exchange and Foreign Trade Control Law" is to be exported or taken out of Japan.

- (2) The Technical -information described in this book is limited to showing representative characteristics and applied circuit examples of the products. It does not constitute the warranting of industrial property, the granting of relative rights, or the granting of any license.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communication equipment, measuring instruments and household appliances). Consult one of our sales offices in advance for the following applications:

- Special applications (such as airplanes, aerospace, traffic control equipment, combustion equipment, life support systems and safety devices) in which special quality and reliability are required, and the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, redundant design is recommended, so that such equipment may not violate relevant laws or regulations because of the function of our products.

- (5) When vacuum packing is required for the products, make sure of the details of the warranty. Observe the conditions (including shelf life and after-unpacking standby time) in their use.

524,288-word × 16bit × 2-bank synchronous dynamic RAM

#### Description

The MN4SV17160BT is 16,777,216-bit CMOS synchronous dynamic random access memory, organized as 524,288-word  $\times$  16-bit  $\times$  2-bank.

With advanced CMOS process technology and circuit configuration,

high-speed data transfer and low power dissipation have been realized.

With high-frequency operation with wide data I/O bus, MN4SV17160BT is suitable for multimedia applications.

#### ■ Features

| Part Number     | Organization (word $\times$ bit $\times$ bank) | Clock Frequency (Max.) | Package                  |

|-----------------|------------------------------------------------|------------------------|--------------------------|

| MN4SV17160BT-80 |                                                | 125MHz                 |                          |

| -90             | $524,288 \times 16 \times 2$                   | 111MHz                 | 50 pin Plastic TSOP (II) |

| -10             |                                                | 100MHz                 | (400mil)                 |

• Single power supply :  $+3.3V \pm 0.3V$

• Interface : LVTTL compatible

• Refresh Cycle: 2,048 refresh cycles / 32 ms

• All Input and Output signals refer to rising edge of the clock (CLK) input

• Dual Internal banks can be controlled by A11 (Bank Select)

• CAS Latency: 2, 3

• Programmable Burst Length: 1, 2, 4, 8, full page (256)

• Wrap sequence: Sequential, Interleave

• Burst Read & Burst Write, Burst Read & Single Write

• Auto Precharge and All Banks Precharge can be controlled by A10 (Precharge Control)

Byte data can be controlled by LDQM and UDQM

• Two variations of refresh : CBR (Auto) refresh, Self Refresh

• DQ suspend and Power Down mode can be controlled by CKE (Clock Enable)

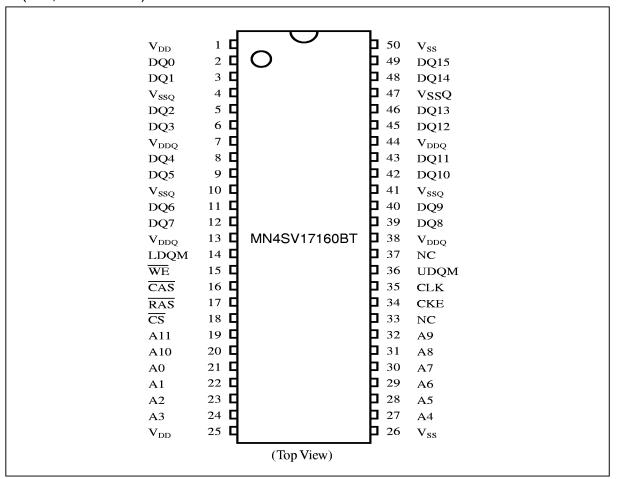

#### ■ Pin Assignment (524,288 × 16 × 2)

#### ■ Pin Names

| Name   | Function                                                       | Name               | Function                      |  |

|--------|----------------------------------------------------------------|--------------------|-------------------------------|--|

| A0~11  | Address Inputs                                                 | WE                 | Write Enable                  |  |

|        | A0 ~ 10 : Row Address Inputs<br>A0 ~ 7 : Column Address Inputs | UDQM               | Upper Byte DQ Mask            |  |

|        | A11 : Bank Select                                              | LDQM               | Lower Byte DQ Mask            |  |

| DQ0~15 | Data Inputs / Outputs                                          | $V_{ m DD}$        | Supply Voltage (+3.3V)        |  |

| CLK    | Clock Input                                                    | $V_{SS}$           | Ground (0V)                   |  |

| CKE    | Clock Enable                                                   | $V_{\mathrm{DDQ}}$ | Supply Voltage for DQ (+3.3V) |  |

| CS     | Chip Select                                                    | $ m V_{SSQ}$       | Ground for DQ (0V)            |  |

| RAS    | Row Address Strobe                                             | NC                 | No Connection                 |  |

| CAS    | Column Address Strobe                                          | I NC               | Two Connection                |  |

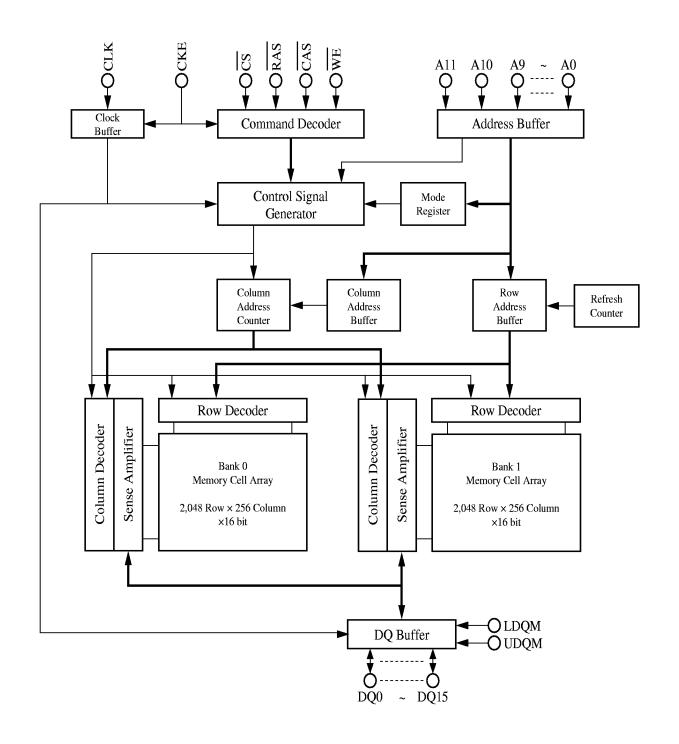

#### ■ Block Diagram

#### ■ Pin Functions

● Clock Input: CLK (Input pin)

CLK is the reference clock for SDRAM operations.

All Inputs and Outputs are synchronized to the rising edge of CLK.

●Chip Select Input: CS (Input pin)

$\overline{\text{CS}}$  enables all command inputs defined by  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$ ,  $\overline{\text{WE}}$ , and address inputs. When  $\overline{\text{CS}}$  is high level, all input commands are ignored, but operations started at previous cycles are continued.

●Row Address Strobe : RAS (Input pin)

Column Address Strobe : CAS (Input pin)

Write Enable : WE (Input pin)

Operation commands are defined by the levels of these pins.

RAS signal is related to the commands of Bank Active, Bank Precharge, Refresh and Mode Register Set.

CAS signal is related to the commands of Read, Write, Refresh and Mode Register Set.

WE signal is related to the commands of Write, Bank Precharge, ModeRegister Set.

Details are described in command operation section.

#### •Address Inputs : A0~A10 (Input pin)

The memory cell to be accessed is pointed by Row and Column addresses. Row address is determined by  $A0 \sim A10$  at Bank Active command cycle. Column address is determined by  $A0 \sim A7$  at Read or Write command cycles.

|              | Row Address | Column Address |  |  |

|--------------|-------------|----------------|--|--|

| MN4SV17160BT | A0 ~A10     | A0 ~A7         |  |  |

A0 ~ A9 inputs are latched as set data of the internal mode register at Mode Register Set cycle.

Also, A10 input controls the Precharge operation. When A10 is high at Precharge Bank command cycle, All Banks Precharge is performed (Precharge All Banks Command). When A10 is high at Read/Write command cycles, Auto Precharge is performed after Read/Write operation (Read with Auto Precharge/Write with Auto Precharge).

#### •Bank Select : A11 (Input pin)

A11 input selects the bank for operation. If A11 is "low", bank 0 is selected, and if A11 is "high", bank 1 is selected.

• Clock Enable : CKE (Input pin)

CKE enables the internal clock. If CKE is "high", CLK of next cycle is validated. If CKE is "low", CLK of next cycle is invalidated and Burst Read/Write is suspended or the Self Refresh mode is activated or the Power Down mode is activated.

Upper Byte DQ MaskUDQM (Input pin)Lower Byte DQ MaskLDQM (Input pin)

UDQM and LDQM mask the upper byte (DQ8 ~ DQ15) and lower byte (DQ0 - DQ7) of DQ data respectively.

In Read command cycle, outputs set to high-impedance at two cycles after asserting (U/L)DQM. In Write command cycle, input data on the DQ pins are masked at the same cycle of asserting (U/L)DQM.

- Data Input/Output: DQ0 ~ DQ15 (Input/Output pin)

Data Inputs/Outputs through the DQ0 ~ DQ15 pins are synchronized with the rising edges of CLK.

- Power Supply:  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{SS}$ ,  $V_{SSQ}$  (Power supply pin) +3.3V is supplied by  $V_{DD}$  and  $V_{DDQ}$  pins.  $V_{DD}$  is the power supply or internal circuit, and  $V_{DDQ}$  is power supply for output buffer.

Ground level is supplied by  $V_{SS}$  and  $V_{SSQ}$  pins.  $V_{SS}$  is the ground for internal circuit, and  $V_{SSQ}$  is ground for output buffer.

#### ■ Command Operation

All operations are performed by the command inputs at the rising edge of CLK. Commands are set by the  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and address pins.

#### Command Truth Table

| Command                   | Current         | CF  | ΚE | <del>C</del> S | DAG | S CAS | $\overline{ m WE}$ | A 1 1 | A 10 | A9~0          | Symbol |

|---------------------------|-----------------|-----|----|----------------|-----|-------|--------------------|-------|------|---------------|--------|

| Command                   | State           | n-1 |    | KASICAS        | CAS | WE    | AII                | AIU   | A9~0 | Symbol        |        |

| Device Deselect           | ANY             | Н   | ×  | Н              | ×   | ×     | ×                  | ×     | ×    | ×             | DESL   |

| No Operation              | ANY             | Н   | ×  | L              | Н   | Н     | Н                  | ×     | ×    | ×             | NOP    |

| Burst Stop                | READ,<br>WRITE  | Н   | ×  | L              | Н   | Н     | L                  | ×     | ×    | ×             | BST    |

| Read                      | ACTIVE          | Н   | ×  | L              | Н   | L     | Н                  | BS    | L    | Col.          | READ   |

| Read with Auto Precharge  | ACTIVE          | Н   | ×  | L              | Н   | L     | Н                  | BS    | Н    | Col.          | READA  |

| Write                     | ACTIVE          | Н   | ×  | L              | Н   | L     | L                  | BS    | L    | Col.          | WRIT   |

| Write with Auto Precharge | ACTIVE          | Н   | ×  | L              | Н   | L     | L                  | BS    | Н    | Col.          | WRITA  |

| Bank Active               | IDLE            | Н   | ×  | L              | L   | Н     | Н                  | BS    |      | Address<br>1) | ACT    |

| Precharge Select Bank     | ANY             | Н   | ×  | L              | L   | Н     | L                  | BS    | L    | ×             | PRE    |

| Precharge All Banks       | ANY             | Н   | ×  | L              | L   | Н     | L                  | ×     | Н    | ×             | PALL   |

| Mode Register Set (3)     | IDLE            | Н   | ×  | L              | L   | L     | L                  | OP.   | CODI | E (2)         | MRS    |

| CBR Refresh (3)           | IDLE            | Н   | Н  | L              | L   | L     | Н                  | ×     | ×    | ×             | REF    |

| Self Refresh Entry (3)    | IDLE            | Н   | L  | L              | L   | L     | Н                  | ×     | ×    | ×             | SELF   |

| Self Refresh Exit         | Self Ref.       | L   | Н  | L              | Н   | Н     | Н                  | ×     | ×    | ×             |        |

|                           |                 |     |    | Н              | ×   | ×     | ×                  | ×     | ×    | ×             |        |

| Clock Suspend Mode Entry  | READ,<br>WRITE  | Н   | L  | ×              | ×   | ×     | ×                  | ×     | ×    | ×             | SUSP   |

| Clock Suspend Mode Exit   | Suspend         | L   | Н  | ×              | ×   | ×     | ×                  | ×     | ×    | ×             |        |

| Power Down Mode Entry     | IDLE,<br>ACTIVE | Н   | L  | L              | Н   | Н     | Н                  | ×     | ×    | ×             |        |

|                           |                 |     |    | Н              | ×   | ×     | ×                  | ×     | ×    | ×             |        |

| Power Down Mode Exit      | Power<br>Down   | L   | Н  | L              | Н   | Н     | Н                  | ×     | ×    | ×             |        |

|                           |                 |     |    | Н              | ×   | ×     | ×                  | ×     | ×    | ×             |        |

$H: High\ level\ ,\ L:\ Low\ level\ ,\ \times:\ Don't\ care\ ,\ BS:\ Bank\ select\ address\ ,\ Col.:\ Column\ address$

<sup>(1)</sup> Row address input. (2) Operation code input. (3) Valid when all banks are idle state.

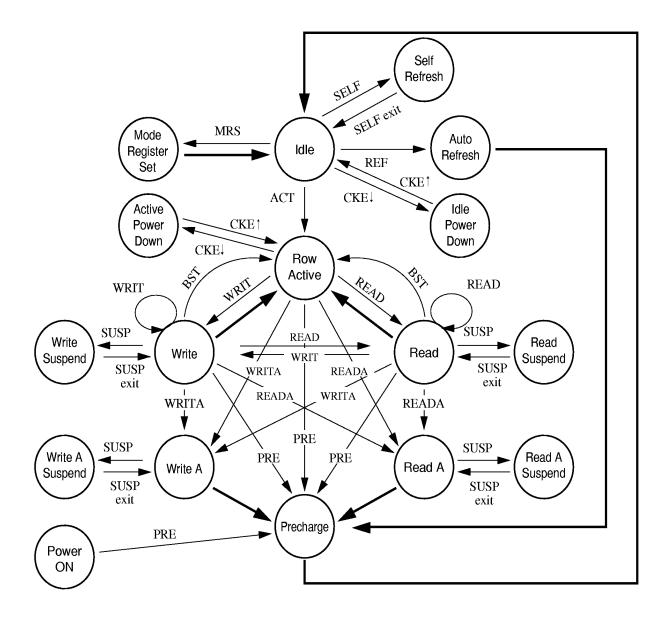

#### ■ State Diagram

Transit with command input

Automatic transition after command completion

Note: After the auto-refresh is performed, precharge is performed automatically, and transit to idle state.

#### ■ Command Functions

• Device Deselect [DESL]

$$(\overline{CS} = "H")$$

Any inputs are ignored. The device keeps previous internal state.

• No Operation [NOP]

$$(\overline{CS} = "L", \overline{RAS}, \overline{CAS}, \overline{WE} = "H")$$

No internal operation is performed by this command. The device keeps previous internal state.

Burst Stop [BST]

$$(\overline{CS} = "L", \overline{RAS}, \overline{CAS} = "H", \overline{WE} = "L")$$

Burst Read/Write operation is stopped by this command. If Burst Length is full page, data Inputs/ Outputs don't stop without this command or Precharge [PRE] command.

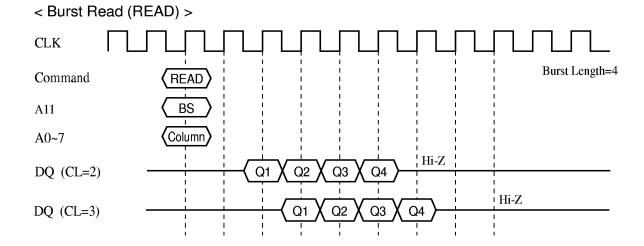

• Read [READ]

$$(\overline{CS} = "L", \overline{RAS} = "H", \overline{CAS} = "L", \overline{WE} = "H", A11 = "Bank Select", A10 = "L", A7 \sim A0 = "Column Address")$$

Burst Read operation starts with this command. Internal bank and column address are selected by A11 and A7 ~ A0 respectively. Latency from this command input to first Read data output is defined by CAS Latency which is set at Mode Register Set cycle. Burst output length are defined by Burst Length which is set at Mode Register Set cycle. Output turns high-impedance after this operation.

A9 ~ A8 inputs are "don't care" at MN4SV17160BT series.

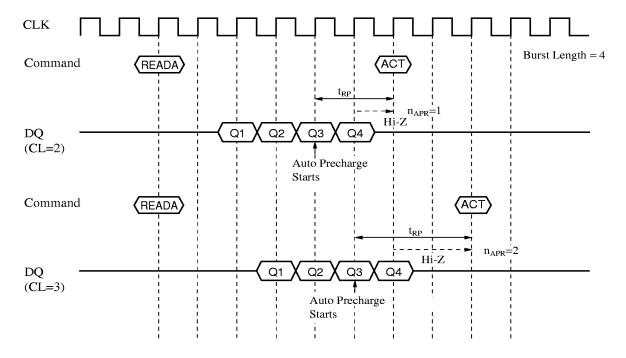

• Read with Auto Precharge [READA]

$$(\overline{CS} = "L", \overline{RAS} = "H", \overline{CAS} = "L", \overline{WE} = "H", A11 = "Bank Select", A10 = "H", A7 \sim A0 = "Column Address")$$

If A10 is "high" at READ command, the bank selected by A11 is precharged automatically after internal Read operation is finished. But, this command is not allowed for full page Burst Read operation.

A9 ~ A8 inputs are "don't care" at MN4SV17160BT series.

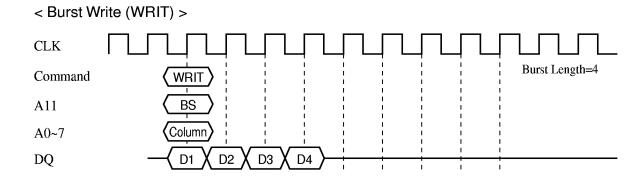

• Write [WRIT]

(

$$\overline{\text{CS}}$$

="L",  $\overline{\text{RAS}}$  ="H",  $\overline{\text{CAS}}$ ,  $\overline{\text{WE}}$  ="L", A11 ="Bank Select", A10 ="L", A7 ~ A0 ="Column Address")

Burst Write operation starts with this command. Internal bank and column address are selected by A11 and A7 ~ A0 respectively. Burst data input length are defined by Burst Length which is set at Mode Register Set cycle.

A9 ~ A8 inputs are "don't care" at MN4SV17160BT series.

• Write with Auto Precharge [WRITA]

$$(\overline{CS} = "L", \overline{RAS} = "H", \overline{CAS}, \overline{WE} = "L", A11 = "Bank Select", A10 = "H", A7 \sim A0 = "Column Address")$$

If A10 is "high" at WRIT command, the bank selected by A11 is precharged automatically after internal Write operation is finished. But, this command is not allowed for full page Burst Write operation.

A9 ~ A8 inputs are "don't care" at MN4SV17160BT series.

#### ● Bank Active [ACT]

$(\overline{CS}, \overline{RAS} = "L", \overline{CAS}, \overline{WE} = "H", A11 = "Bank Select", A10 \sim A0 = "Row Address")$

This command activates the internal bank selected by A11 and the row address selected by A0  $\sim$  A10. If A11 is "low", bank 0 is selected, and if A11 is "high", bank 1 is selected.

#### • Precharge Select Bank [PRE]

$$(\overline{CS}, \overline{RAS} = "L", \overline{CAS} = "H", \overline{WE} = "L", A11 = "Bank Select", A10 = "L")$$

The internal bank selected by A11 is precharged by this command. After Precharge operation is performed, the selected bank turns to be idle state automatically. If A11 is "low", bank 0 is selected, and if A11 is "high", bank 1 is selected.

#### • Precharge All Banks [PALL]

$$(\overline{CS}, \overline{RAS} = "L", \overline{CAS} = "H", \overline{WE} = "L", A10 = "H")$$

If A10 is "high" at PRE command, all internal banks are precharged. After Precharge operation is performed, all banks turn to be idle state automatically.

#### Mode Register Set [MRS]

$$(\overline{CS}, \overline{RAS}, \overline{CAS}, \overline{WE} = "L", A11 \sim A0 = "Operation Code")$$

The mode register is set by this command. The data on the  $A0 \sim A11$  pins in this command cycle are set as the operation code. But,  $A11 \sim A10$  inputs are "don't care" at MN4SV17160BT series. After power-on and All Banks Precharge, Mode Register Set command must be executed.

The mode register can be set during device operation, but all banks must be idle state before this command execution.

#### • CBR (Auto) Refresh [REF]

$$(\overline{CS}, \overline{RAS}, \overline{CAS} = "L", \overline{WE} = "H")$$

This command starts CBR (Auto) refresh operation. Row address is generated by internal refresh address counter. The refresh address is incremented by this command input.

MN4SV17160BT series need 2,048 times input of this command to refresh all memory cells.

All internal banks must be idle state before this command input. After refresh operation is performed, precharge operation is performed automatically, then all banks return to idle state. Any next commands cannot input during  $t_{\rm RC}$  period after this command execution.

#### • Self Refresh Entry [SELF]

$$(CKE, \overline{CS}, \overline{RAS}, \overline{CAS} = "L", \overline{WE} = "H")$$

Self Refresh operation starts with this command execution. All banks must be idle state before this command execution. Self Refresh operation continues while CKE is low after this command execution, and any commands cannot be accepted. Self Refresh mode is terminated when CKE is high (Self Refresh Exit command).

#### Self Refresh Exit

(CKE ="H",

$$\overline{CS}$$

="L",  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  ="H" or CKE,  $\overline{CS}$  ="H")

Self Refresh mode is terminated by this command execution. After this command execution, internal state is returned to idle state. Any next commands cannot input during  $t_{RC}$  period after this command execution.

#### ● Clock Suspend Mode Entry [SUSP]

(CKE = "L")

When CKE is negated ( CKE is set to "low" ), internal clock is suspended from next CLK rising.

If CKE is negated during Read/Write operation, internal state entries Clock Suspend mode. The variety of Clock Suspend mode depends on the state of previous cycle as follows.

[ Previous cycle ] [ Clock Suspend Mode ]

READ READ Suspend

READA READA Suspend

WRIT WRIT Suspend

WRITA WRITA Suspend

#### • READ Suspend / READA Suspend

If CKE is negated during READ/READA mode, the output of next cycle is suspended. And it is continued until the next cycle of asserting CKE (Clock Suspend Mode Exit).

Internal state and Read address don't change.

#### • WRIT Suspend / WRITA Suspend

If CKE is negated during WRIT/WRITA mode, the input of next cycle is not accepted. And it is continued until the next cycle of asserting CKE (Clock Suspend Mode Exit).

Internal state and Write address don't change.

#### Clock Suspend Mode Exit

(CKE = "H")

If CKE is asserted ( CKE is set to "high" ) during Clock Suspend mode, internal clock restarts from next CLK rising. And internal state exit Clock Suspend mode.

#### Power Down Mode Entry

(CKE,

$$\overline{CS} = "L"$$

,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE} = "H"$  or CKE = "L",  $\overline{CS} = "H"$ )

If CKE is negated (CKE is set to "low") when no READ/READA or WRIT/WRITA command is in progress, the device enters Power Down mode. The device has two Power Down mode for the state of device when Power Down mode is entered.

[ Previous cycle ] [ Power Down Mode ]

Idle Idle Power Down

Row Active Active Power Down

#### • Idle Power Down

If CKE is negated during Idle mode, the input buffers are disabled of next cycle and power consumption is reduced to the minimum.

#### • Active Power Down

If CKE is negated during active mode, the input buffers are disabled of next cycle and power consumption is reduced.

#### Power Down Mode Exit

$$(CKE = "H", \overline{CS} = "L", \overline{RAS}, \overline{CAS}, \overline{WE} = "H" \text{ or } CKE, \overline{CS} = "H")$$

If CKE is asserted (CKE is set to "high" ) during Power Down mode, internal clock restarts from CLK rising. And internal state exit Power Down mode.

#### ■ I/O Control

The data of DQ0  $\sim$  DQ7 (lower byte) pins and DQ8  $\sim$  DQ15 (upper byte) pins can be masked by LDQM pin and UDQM pin respectively.

I/O control can be executed with command operations.

DQM Truth Table

| Function                                  |     | CKE |   | )M | Symbol |  |

|-------------------------------------------|-----|-----|---|----|--------|--|

| T direction                               | n-1 | n   | U | L  | Symbol |  |

| Upper byte Write Enable / Output Enable   | Н   | ×   | L | ×  | ENBU   |  |

| Lower byte Write Enable / Output Enable   | Н   | ×   | × | L  | ENBL   |  |

| Upper byte Write Inhibit / Output Disable | Н   | ×   | Н | ×  | MASKU  |  |

| Lower byte Write Inhibit / Output Disable | Н   | ×   | × | Н  | MASKL  |  |

H: High level, L: Low level, x: Don't care

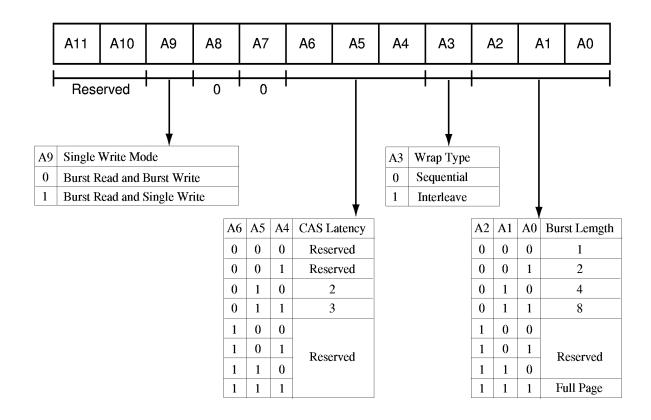

#### ■ Mode Register

The data on the  $A0 \sim A11$  pins in Mode Register Set command cycle are set as the operation code. Mode register consists of following parts.

● A2, A1, A0 : BL (Burst Length)

Burst Length = 1, 2, 4, 8, full page

(Full page length : 256 bits)

• A3 : WT (Wrap Type)

Wrap Type: Sequential, Interleave ● A6, A5, A4: CL (CAS Latency) CAS Latency = 2, 3

• A9 : Read/Write mode

Burst Read and Burst Write, Burst Read and Single Write

### ■ Burst Length and Wrap Type

● BL =2

| Starting Address (Column Address A0,binary) | Sequential Addressing (decimal) | Interleave Addressing (decimal) |

|---------------------------------------------|---------------------------------|---------------------------------|

| 0                                           | 0,1                             | 0,1                             |

| 1                                           | 1,0                             | 1,0                             |

$\bullet$  BL =4

| Starting Address | Sequential | Interleave |

|------------------|------------|------------|

| (Column Address  | Addressing | Addressing |

| A1~A0,binary)    | (decimal)  | (decimal)  |

| 00               | 0,1,2,3    | 0,1,2,3    |

| 01               | 1,2,3,0    | 1,0,3,2    |

| 10               | 2,3,0,1    | 2,3,0,1    |

| 11               | 3,0,1,2    | 3,2,1,0    |

●BL =8

| Starting Address (Column Address A2~A0,binary) | Sequential Addressing (decimal) | Interleave Addressing (decimal) |

|------------------------------------------------|---------------------------------|---------------------------------|

| 000                                            | 0,1,2,3,4,5,6,7                 | 0,1,2,3,4,5,6,7                 |

| 001                                            | 1,2,3,4,5,6,7,0                 | 1,0,3,2,5,4,7,6                 |

| 010                                            | 2,3,4,5,6,7,0,1                 | 2,3,0,1,6,7,4,5                 |

| 011                                            | 3,4,5,6,7,0,1,2                 | 3,2,1,0,7,6,5,4                 |

| 100                                            | 4,5,6,7,0,1,2,3                 | 4,5,6,7,0,1,2,3                 |

| 101                                            | 5,6,7,0,1,2,3,4                 | 5,4,7,6,1,0,3,2                 |

| 110                                            | 6,7,0,1,2,3,4,5                 | 6,7,4,5,2,3,0,1                 |

| 111                                            | 7,0,1,2,3,4,5,6                 | 7,6,5,4,3,2,1,0                 |

#### ●BL =Full Page

Only Sequential Addressing is executed. Burst Read/Write operation continues until Burst Stop command or Precharge command input. And the address of Input/Output data return to first access address if full page data access is completed.

Full page data length = 256 bits

#### ■ Command Operations

#### [Read command (READ)]

Bank and first column address are selected by A11 and A0  $\sim$  A7 respectively. Latency from this command input to first Read data output is defined by CAS Latency which is set at Mode Register Set cycle. Burst output length is defined by the Burst Length which is set at Mode Register Set cycle. Output turns high-impedance after this operation.

Following operation mode can be programmed in Mode Register Set command cycle.

Burst Length = 1, 2, 4, 8, full page (256)

When Burst Length is full page, only Sequential Addressing is executed. Burst Read/Write operation continues until Burst Stop command or Precharge command input. And the address of Input/Output data return to the first access address if full page data access is completed.

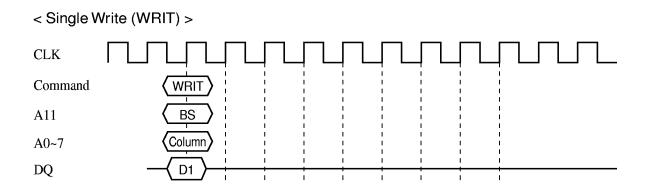

#### [Write command (WRIT)]

If you selected A9 = 0 at the Mode Register Set command cycle, Write mode is Burst Write mode. If you selected A9 = 1, Write mode is Single Write mode. (Read mode is Burst Read mode in both case.)

#### 1. Burst Write Mode

Bank and first column address are selected by A11 and A0 ~ A7 respectively. Latency from Write command input to first Write data input is zero.

Burst Write data input length are defined by the Burst Length which is set in the mode register. Following operation mode can be programmed in Mode Register Set command cycle.

Burst Length = 1, 2, 4, 8, full page (256)

#### 2. Single Write Mode

Bank and first column address are selected by A11 and A0  $\sim$  A7 respectively. Write data is inputted at the only WRIT or WRITA command cycle. So, Write data input length is 1 without reference to the Burst Length in mode resister.

[Auto Precharge command (READA [Read with Auto Precharge] /

WRITA [Write with Auto Precharge] )]

#### 1. Read with Auto Precharge (READA)

If A10 is "high" at READ command, the bank selected by A11 is precharged automatically after internal Read operation is finished. So, Precharge command (PRE) need not to be executed for the selected bank after Read operation.

After READA command is executed, an interval defined by  $n_{APR}$  (Last data-out to Bank Active command delay) cycle is required before Bank Active command (ACT) execution for the same bank. Minimum  $n_{APR}$  depends on CAS Latency. This command is not allowed for full page Burst Read operation.

#### < READ with Auto Precharge Command (READA) >

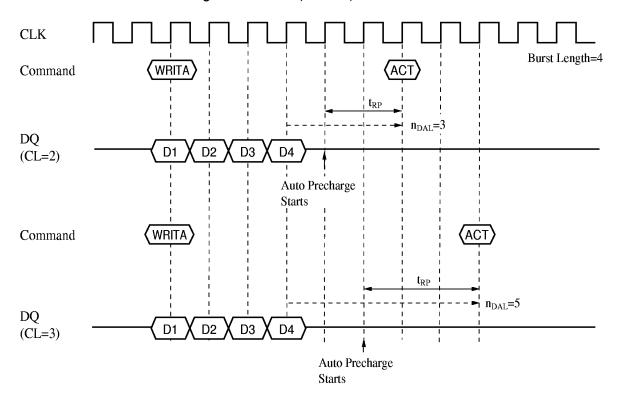

#### 2. Write with Auto Precharge (WRITA)

If A10 is "high" at WRIT command, the bank selected by A11 is precharged automatically after internal Write operation is finished. So, Precharge command (PRE) need not to be executed for the selected bank after Write operation.

After WRITA command is executed, an interval defined by  $n_{DAL}$  (Last data-in to Bank Active command delay) cycle is required before Bank Active command (ACT) execution for the same bank. Minimum  $n_{DAL}$  depends on CAS Latency. This command is not allowed for full page Burst Read operation.

#### < WRITE with Auto Precharge Command (WRITA) >

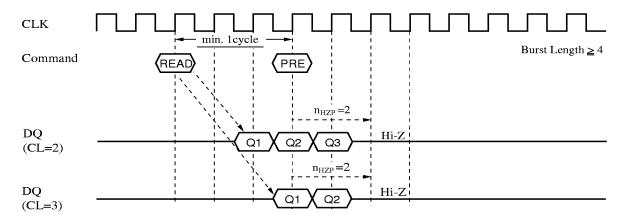

#### [Burst Stop command (BST)]

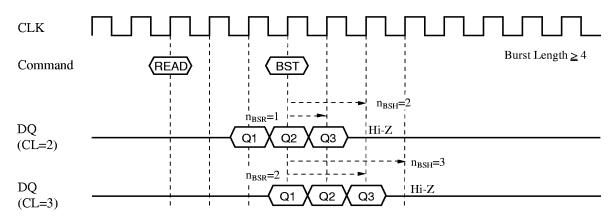

#### 1. Burst Read Stop

Burst data output can be terminated by Burst Stop command (BST). An interval from Burst Stop command execution to last valid data output are defined by  $n_{BSR}$  (Burst Stop command to last valid data-out delay) cycle. Output buffer turned to Hi-Z at  $n_{BSH}$  (Burst Stop command to output buffer turn off delay) cycle after Burst Stop command input or when Burst Read operation is completed. Minimum  $n_{BSR}$  and  $n_{BSH}$  depend on CAS Latency.

#### < Burst Stop Command (Burst READ Stop) >

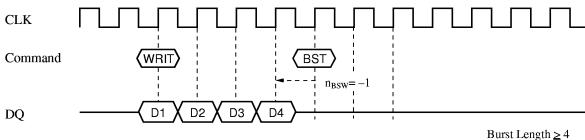

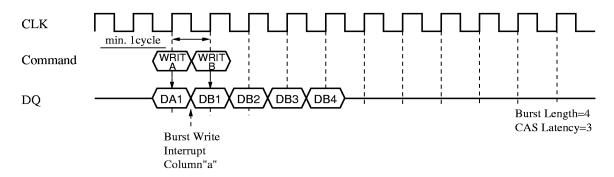

#### 2. Burst Write Stop

Burst data-input can be terminated by Burst Stop command (BST). Data-in at the same and following cycles are ignored.

# < Burst Stop Command (Burst WRITE Stop) >

Burst Length  $\ge 4$ CAS Latency = 2,3

#### ■ Command Interval

[READ to READ command interval]

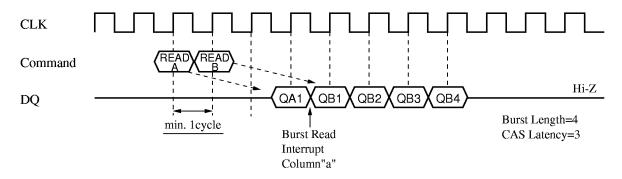

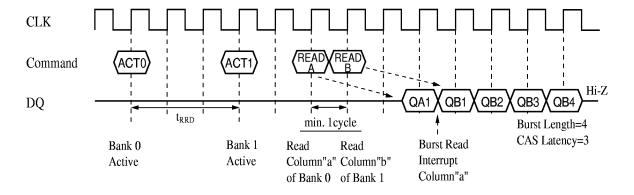

#### [Case 1] Same row address in same bank

When a Read command (READ) is issued for the same row address in the same bank with previous Read command (READ), a minimum interval from READ to READ is 1 cycle. Although previous Burst Read operation is not completed, subsequent Read operation is started after CAS Latency cycles. Then the previous Burst Read operation is interrupted.

#### < READ to READ Command Interval (same ROW address in same bank) >

#### [Case 2] Different row address in same bank

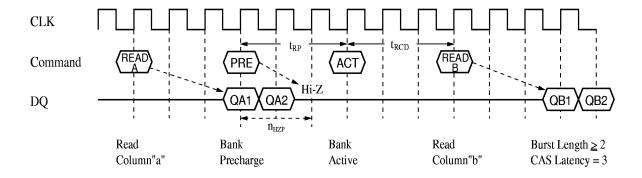

When subsequent Read command (READ) is issued for a different row address in the same bank, Precharge command (PRE) and Bank Active command (ACT) must be executed before executing subsequent Read command.

#### < READ to READ Command Interval (different ROW address in same bank) >

#### [Case 3] Different bank

When a Read command (READ) is issued for a different bank from the previous Read command (READ), a minimum interval from READ to READ is 1 cycle. Although previous Burst Read operation is not completed, subsequent Read operation is started after CAS Latency cycles. Then the previous Burst Read operation is interrupted.

If another bank is not activated, Bank Active command (ACT) need to be executed before subsequent Read command execution.

#### < READ to READ Command Interval (different bank) >

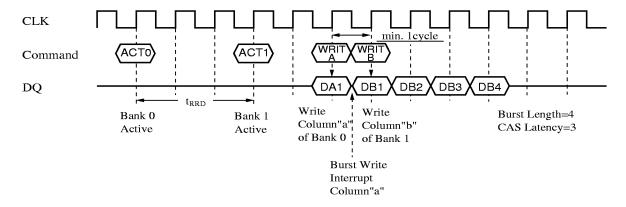

#### [WRIT to WRIT command interval]

#### [Case 1] Same row address in same bank

When a Write command (WRIT) is issued for the same row address in the same bank with previous Write command (WRIT), a minimum interval from WRIT to WRIT is 1 cycle. Although previous Burst Write operation is not completed, subsequent Write operation is started. Then the previous Burst Write operation is interrupted.

#### < WRIT to WRIT Command Interval (same ROW address in same bank) >

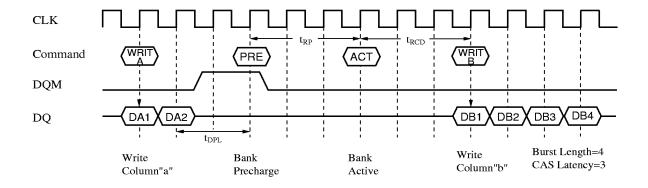

#### [Case 2] Different row address in same bank

When subsequent Write command (WRIT) is issued for a different row address in the same bank, Precharge command (PRE) and Bank Active command (ACT) must be executed before executing subsequent Write command.

#### < WRIT to WRIT Command Interval (different ROW address in same bank) >

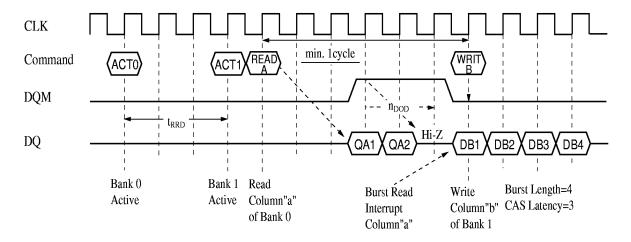

#### [Case 3] Different bank

When subsequent Write command (WRIT) is issued for a different bank from the previous bank, a minimum interval from WRIT to WRIT is 1 cycle. Although previous Burst Write operation is not completed, subsequent Write operation is started. Then the previous Burst Write operation is interrupted.

If another bank is not activated, Bank Active command (ACT) need to be executed before subsequent Write command execution.

#### < WRIT to WRIT Command Interval (different bank) >

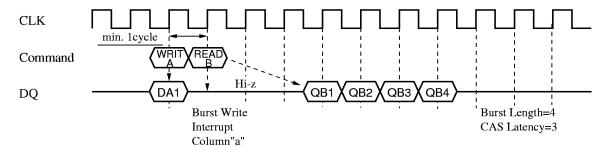

#### [WRIT to READ command interval]

#### [Case 1] Same row address in same bank

When a Read command (READ) is issued for the same row address in the same bank with previous Write command (WRIT), a minimum interval from WRIT to READ is 1 cycle. Although previous Burst Write operation is not completed, data-input is interrupted by next Read command. Only the data before READ command is written.

Data bus must be high-impedance at least one cycle before first Read data-out.

#### < WRIT to READ Command Interval (same ROW address in same bank) >

#### [Case 2] Different row address in same bank

When subsequent Read command (READ) is issued for a different row address in the same bank, Precharge command (PRE) and Bank Active command (ACT) must be executed before executing subsequent Read command.

#### < WRIT to READ Command Interval (different ROW address in same bank) >

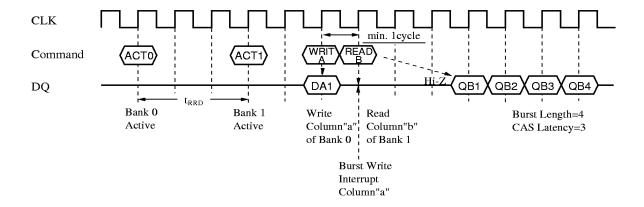

#### [Case 3] Different bank

When a Read command (READ) is issued for a different bank from the previous bank, a minimum interval from WRIT to READ is 1 cycle. Although previous Burst Write operation is not completed, data-input is interrupted by next Read command. Only the data before READ command is written.

If another bank is not activated, Bank Active command (ACT) need to be executed before subsequent Read command execution.

Data bus must be high-impedance at least one cycle before first Read data out.

#### < WRIT to READ Command Interval (different bank) >

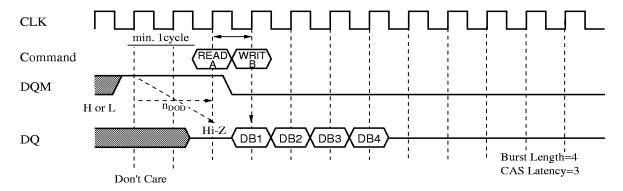

#### [READ to WRIT command interval]

#### [Case 1] Same row address in same bank

When a Write command (WRIT) is issued for the same row address in the same bank with previous Read command (READ), a minimum interval from READ to WRIT is 1 cycle. Although previous Burst Read operation is not completed, data output is interrupted by next Write command.

Output buffer must be high-impedance at least one cycle before Write command by asserting DQM(U/L) to avoid data conflict. The latency from DQM(U/L) assert to output buffer turn-off  $(n_{DOD})$  is 2 cycles, so DQM (U/L) must be asserted at least 3 cycles before Write command.

#### < READ to WRITE Command Interval (same ROW address in same bank) >

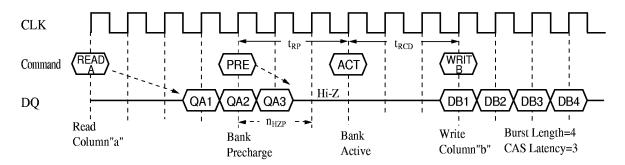

#### [Case 2] Different row address in same bank

When subsequent Write command (WRIT) is issued for a different row address in the same bank, Precharge command (PRE) and Bank Active command (ACT) must be executed before executing subsequent Write command.

#### < READ to WRIT Command Interval (different ROW address in same bank) >

#### [Case 3] Different bank

When a Write command (WRIT) is issued for a different bank from the previous bank, an minimum interval from READ to WRIT is 1 cycle. Although previous Burst Read operation is not completed, data output is interrupted by next Write command. Only the Read data before WRIT command are put out.

If another bank is not activated, Bank Active command (ACT) need to be executed before Write command execution.

Output buffer must be high-impedance at least one cycle before Write command by asserting DQM(U/L) to avoid data conflict. The latency from DQM(U/L) assert to output buffer turn-off  $(n_{DOD})$  is 2 cycles, so DQM(U/L) must be asserted at least 3 cycles before Write command.

#### < READ to WRIT Command Interval (different bank) >

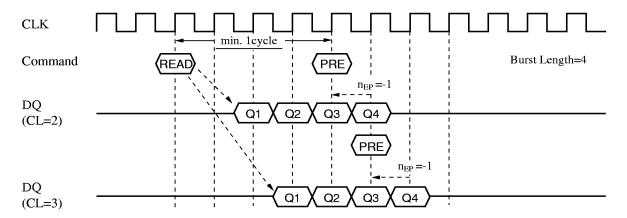

[READ to PRE [ Precharge Select Bank ] command interval (Same bank)]

When a Precharge command (PRE) is issued for the same bank with previous Read command (READ), a minimum interval from READ to PRE is 1 cycle. Although previous Burst Read operation is not completed, output buffer turn to high-impedance  $n_{HZP}$  (Precharge command to output buffer turn-off delay) cycles after executing Precharge command. Then the previous Burst Read operation is interrupted.

An interval defined by  $n_{EP}$  (last data-out to Precharge command delay) is required to complete Burst Read operation.

#### Burst READ Interrupt

< READ to PRE Command Interval (same bank, Burst READ Interrupt) >

#### Burst READ Complete

< READ to PRE Command Interval (same bank, Burst READ Complete) >

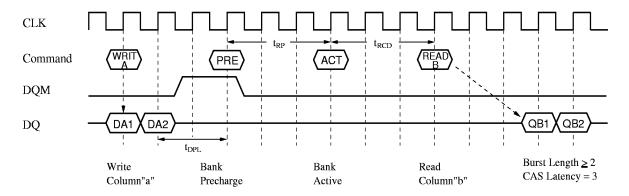

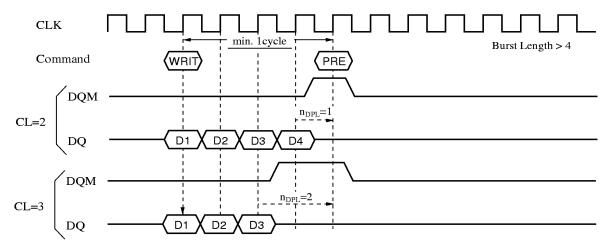

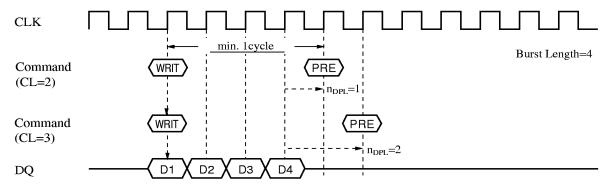

[WRIT to PRE [ Precharge Select Bank ] command interval (Same bank)]

When a Precharge command (PRE) is issued for the same bank with previous Write command (WRIT), a minimum interval from WRIT to PRE is 1 cycle. Although previous Burst Write operation is not completed, precharge operation starts. Then the previous Burst Write operation is interrupted.

An interval defined by  $n_{DPL}$  (last data-in to Precharge command period ) is required from last data-in to Precharge command.

#### ● Burst WRITE Interrupt

< WRIT to PRE Command Interval (same bank, Burst WRITE Interrupt) >

#### ● Burst WRITE Complete

< WRIT to PRE Command Interval (same bank, Burst WRITE Complete) >

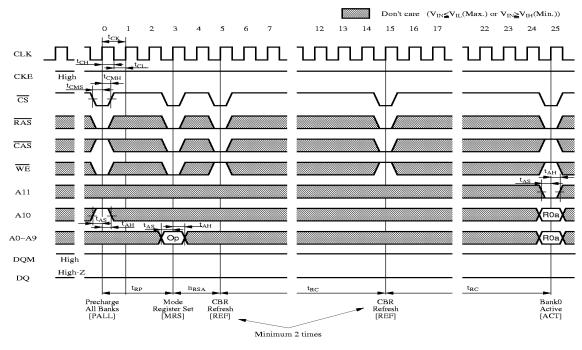

#### ■ Power-On Sequence

- Apply power and clock with NOP or DESL command input.

Maintain stable power, stable clock, and NOP or DESL input conditions for a minimum of 100μs.

During above operation, CKE and DQM(U/L) inputs must be held "high".

- 2. Execute All Banks Precharge by issuing PRE or PALL commands.

- 3. After minimum t<sub>RP</sub> period from last Precharge command execution, issue Mode Register Set (MRS ) command to initialize mode register.

- 4. With the interval of nRSA after MRS command, issue CBR (auto) refresh command (REF) at least two times with  $t_{RC}$  interval.

After executing above power-on sequence, the device is in the idle state. And command input is possible at any cycle.

(The sequence of Mode Register Set and CBR refresh can be transposed.)

#### ■ Note For Self Refresh

Before Self Refresh Entry command input and after Self Refresh Exit command input, execute CBR refresh at least 2,048 times at maximum 15.6 µs interval.

#### ■ Electrical Specifications

[Absolute Maximum Ratings]  $(V_{SS} = 0V)$

| Item                          | Symbol                   | Rating      | Unit                   |

|-------------------------------|--------------------------|-------------|------------------------|

| Supply Voltage (1)            | $V_{DD,}V_{DDQ}$         | -0.5 ~ +4.6 | V                      |

| Input/Output Voltage (1)      | $V_{\rm IN,}V_{\rm OUT}$ | -0.5 ~ +4.6 | V                      |

| Short Circuit Output Current  | $I_{OS}$                 | 20          | mA                     |

| Power Dissipation             | Pd                       | 1           | W                      |

| Operating Ambient Temperature | Topr                     | 0 ~ +70     | $^{\circ}\!\mathrm{C}$ |

| Storage Temperature           | Tstg                     | -55 ~ +125  | °C                     |

#### Notes

#### (1) $V_{SS}$ terminal reference

Stresses greater than those listed under "Absolute Maximum Ratings" (ex. excess voltage input or reverse insertion) may affect reliability of the device and cause unusual heat, deterioration of characteristics or breakdown of the device.

[Recommended Operating Conditions] (Ta =  $0 \sim +70^{\circ}$ C)

| Item                    | Symbol                                        | Min. | Тур. | Max.                 | Unit |

|-------------------------|-----------------------------------------------|------|------|----------------------|------|

| Supply Voltage          | $egin{array}{c} V_{DD} \ V_{DDQ} \end{array}$ | 3.0  | 3.3  | 3.6                  | V    |

|                         | $egin{array}{c} V_{SS} \ V_{SSQ} \end{array}$ | 0    | 0    | 0                    | V    |

| Input Voltage "H" Level | $V_{\mathrm{IH}}$                             | 2.0  |      | V <sub>DD</sub> +0.3 | V    |

| Input Voltage "L" Level | $V_{ m IL}$                                   | -0.3 |      | 0.8                  | V    |

### [Terminal Capacitance] ( $V_{DD}$ = 3.3V ± 0.3V, Ta = 0 ~ +70°C, 1MHz)

| Item              |         | Symbol   | Min. | Тур. | Max. | Unit |

|-------------------|---------|----------|------|------|------|------|

| Input             | Address | $C_{I1}$ |      |      | 6    | pF   |

|                   | Clock   | $C_{12}$ |      |      | 6    | pF   |

| Data Input/Output |         | $C_{IO}$ |      |      | 8    | pF   |

### [DC Characteristics] ( $V_{DD}$ = 3.3V $\pm$ 0.3V, Ta = 0 ~ +70°C)

| Item                     | Symbol            | Min. | Тур. | Max. | Unit | Note |

|--------------------------|-------------------|------|------|------|------|------|

| Input Leakage Current    | ${ m I_{LI}}$     | -5   | 0.1  | 5    | μΑ   | (1)  |

| Output Leakage Current   | $I_{LO}$          | -5   | 0.1  | 5    | μΑ   | (2)  |

| Output Voltage "H" level | $V_{\mathrm{OH}}$ | 2.4  |      |      | V    | (3)  |

| Output Voltage "L" level | $V_{OL}$          |      |      | 0.4  | V    | (4)  |

#### Notes

- (1)  $0V \le V_{\rm IN} \le 3.6V$ , Input pins other than measurement pins are at 0V, or  $V_{\rm DD}$ .

- (2)  $0V \le V_{OUT} \le 3.6V$ , Output is in a high-impedance state.

- (3)  $I_{OH} = -2mA$

- (4)  $I_{OL} = 2mA$

[DC Operating Conditions] (V<sub>DD</sub>=  $3.3V \pm 0.3V$ , Ta =  $0 \sim +70^{\circ}C$ )

| Item                                      | Symbol                      | Condition                                                                                   | Grade | Max. | Unit | Note |

|-------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------|-------|------|------|------|

| Operating Current                         | $I_{CC1}$                   | Burst Length=1                                                                              | -80   | 100  |      |      |

| (1 bank active)                           |                             | t <sub>RC</sub> =Min.                                                                       | -90   | 90   | mA   | 2,3  |

|                                           |                             |                                                                                             | -10   | 80   |      |      |

| Standby Current (All banks inactive)      | $I_{CC2P}$                  | $\begin{array}{c} CKE \leq V_{IL} \\ t_{CK} = Min. \\ (Power Down mod\\ \end{array}$        | de)   | 2    | mA   | 2    |

|                                           | $I_{CC2PS}$                 | $\begin{array}{c} CKE \leq V_{IL} \\ t_{CK} = V_{IL} \text{ or } V_{IH} \\ (Power Down mod$ | de)   | 1    | mA   |      |

|                                           | $I_{CC2N}$                  | CKE≥V <sub>IH</sub>                                                                         | -80   | 28   | mA   | 2    |

|                                           |                             | t <sub>CK</sub> =Min.                                                                       | -90   | 25   |      |      |

|                                           |                             |                                                                                             | -10   | 22   |      |      |

| Standby Current (All banks active)        | $I_{CC3P}$                  | $\begin{array}{l} CKE \leq V_{IL} \\ t_{CK} = Min. \\ (Power Down mod) \end{array}$         | 2     | mA   | 2    |      |

|                                           | $I_{CC3N}$ $CKE \ge V_{IH}$ |                                                                                             | -80   | 28   |      |      |

|                                           |                             | t <sub>CK</sub> =Min.                                                                       | -90   | 25   | mA   | 2    |

|                                           |                             |                                                                                             | -10   | 22   |      |      |

| Burst Operating Current (Bank interleave) | $I_{CC4}$                   | t <sub>CK</sub> =Min.                                                                       | -80   | 150  |      | 2,3  |

| (Bank Inteneave)                          |                             |                                                                                             | -90   | 135  | mA   |      |

|                                           |                             |                                                                                             | -10   | 120  |      |      |

| Refresh Current                           | $I_{CC5}$                   | t <sub>RC</sub> =Min.                                                                       | -80   | 120  |      | 2    |

|                                           |                             |                                                                                             | -90   | 105  | mA   |      |

|                                           |                             |                                                                                             | -10   | 90   |      |      |

| Self Refresh Current                      | $I_{CC6}$                   | $CKE \le V_{IL}$                                                                            |       | 2    | mA   |      |

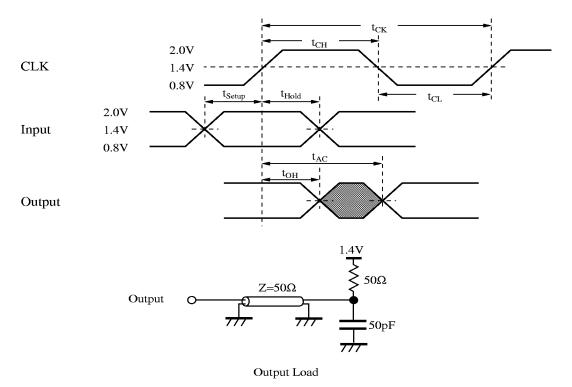

[Electrical Characteristics and Recommended AC Operating Conditions (Synchronous)]  $(V_{DD} = 3.3V \pm 0.3V, Ta = 0 \sim +70^{\circ}C)$

| Item                                      |      | Symbol             | -80  |      | -90  |      | -10  |      | T.L:4 | None |

|-------------------------------------------|------|--------------------|------|------|------|------|------|------|-------|------|

|                                           |      | Syllibor           | Min. | Max. | Min. | Max. | Min. | Max. | Unit  | Note |

| CLK Cycle Time                            | CL=3 | $t_{CK}$           | 8    |      | 9    |      | 10   |      | ns    | 4    |

|                                           | CL=2 |                    | 12   |      | 13.5 |      | 15   |      | 118   | _    |

| Access Time from CLK                      | CL=3 | t <sub>AC</sub>    |      | 6.5  |      | 7    |      | 8    |       | 1.5  |

|                                           | CL=2 |                    |      | 9    |      | 10.5 |      | 12   | ns    | 4,5  |

| CLK High Level Width                      |      | t <sub>CH</sub>    | 3    |      | 3    |      | 3.5  |      | ns    | 4,6  |

| CLK Low Level Width                       |      | $t_{\mathrm{CL}}$  | 3    |      | 3    |      | 3.5  |      | ns    | 4,6  |

| Data-out Hold Time                        |      | t <sub>OH</sub>    | 2    |      | 2.5  |      | 2.5  |      | ns    | 4    |

| Data-out Low-impedance Time               |      | t <sub>LZ</sub>    | 0    |      | 0    |      | 0    |      | ns    | 4    |

| Data-out High-impedance Time              |      | t <sub>HZ</sub>    |      | 10   |      | 10   |      | 10   | ns    | 4    |

| Data-in Setup Time                        |      | $t_{DS}$           | 2.5  |      | 3    |      | 3    |      | ns    | 4,6  |

| Data-in Hold Time                         |      | t <sub>DH</sub>    | 1    |      | 1    |      | 1    |      | ns    | 4,6  |

| Address Setup Time                        |      | t <sub>AS</sub>    | 2.5  |      | 3    |      | 3    |      | ns    | 4,6  |

| Address Hold Time                         |      | t <sub>AH</sub>    | 1    |      | 1    |      | 1    |      | ns    | 4,6  |

| CKE Setup Time                            |      | $t_{CKS}$          | 2.5  |      | 3    |      | 3    |      | ns    | 4,6  |

| CKE Hold Time                             |      | t <sub>CKH</sub>   | 1    |      | 1    |      | 1    |      | ns    | 4,6  |

| Command Setup Time<br>(CS,RAS,CAS,WE,DQM) |      | $t_{\mathrm{CMS}}$ | 2.5  |      | 3    |      | 3    |      | ns    | 4,6  |

| Command Hold Time<br>(CS,RAS,CAS,WE,DQM)  |      | $t_{CMH}$          | 1    |      | 1    |      | 1    |      | ns    | 4,6  |

[Electrical Characteristics and Recommended AC Operating Conditions (Asynchronous)]  $(V_{DD} = 3.3V \pm 0.3V, Ta = 0 \sim +70^{\circ}C)$

| Item                                                       |      | Symbol-          | -80         |         | -90         |         | -10         |         | TT!  | NT 4 |

|------------------------------------------------------------|------|------------------|-------------|---------|-------------|---------|-------------|---------|------|------|

|                                                            |      | Symbol           | Min.        | Max.    | Min.        | Max.    | Min.        | Max.    | Unit | Note |

| ACT (REF) to ACT (REF) Command Period (Same Bank)          |      | t <sub>RC</sub>  | 80          |         | 90          |         | 100         |         | ns   | 4,7  |

| ACT to PRE Command Period (Same Bank)                      |      | t <sub>RAS</sub> | 56          | 120,000 | 63          | 120,000 | 70          | 120,000 | ns   | 4,7  |

| PRE to ACT Command Period (Same Bank)                      |      | t <sub>RP</sub>  | 24          |         | 27          |         | 30          |         | ns   | 4,7  |

| ACT to READ/WRIT<br>Command Period (Same Bank)             |      | t <sub>RCD</sub> | 24          |         | 27          |         | 30          |         | ns   | 4,7  |

| ACT to ACT Command Period (Different Bank)                 |      | t <sub>RRD</sub> | 24          |         | 27          |         | 30          |         | ns   | 4,7  |

| Data-in to PRE<br>Command Period                           | CL=3 | t <sub>DPL</sub> | 1CLK<br>+8  |         | 1CLK<br>+9  |         | 1CLK<br>+10 |         | ns   | 4,7  |

|                                                            | CL=2 |                  | 8           |         | 9           |         | 10          |         | ns   |      |

| Data-in to ACT (REF)<br>Command Period<br>(Auto Precharge) | CL=3 | t <sub>DAL</sub> | 2CLK<br>+24 |         | 2CLK<br>+27 |         | 2CLK<br>+30 |         | ns   | 4,7  |

|                                                            | CL=2 |                  | 1CLK<br>+24 |         | 1CLK<br>+27 |         | 1CLK<br>+30 |         | ns   |      |

| Transition Time                                            |      | $t_{\mathrm{T}}$ | 1           | 30      | 1           | 30      | 1           | 30      | ns   |      |

| Refresh Time                                               |      | $t_{ m REF}$     |             | 32      |             | 32      |             | 32      | ms   |      |

## [Correlation Between Frequency and Minimum Latency]

| Speed Version                                           | -80 |    | -90 |      | -10 |    | UNIT  |

|---------------------------------------------------------|-----|----|-----|------|-----|----|-------|

| CLK Cycle Time                                          | 8   | 12 | 9   | 13.5 | 10  | 15 | ns    |

| Frequency                                               | 125 | 83 | 111 | 74   | 100 | 66 | MHz   |

| CAS Latency                                             | 3   | 2  | 3   | 2    | 3   | 2  | cycle |

| n <sub>RCD</sub>                                        | 3   | 2  | 3   | 2    | 3   | 2  | cycle |

| RAS Latency [t <sub>RCD</sub> +CAS Latency]             | 6   | 4  | 6   | 4    | 6   | 4  | cycle |

| $n_{RC}$                                                | 10  | 7  | 10  | 7    | 10  | 7  | cycle |

| $n_{RAS}$                                               | 7   | 5  | 7   | 5    | 7   | 5  | cycle |

| $n_{RRD}$                                               | 3   | 2  | 3   | 2    | 3   | 2  | cycle |

| n <sub>RP</sub>                                         | 3   | 2  | 3   | 2    | 3   | 2  | cycle |

| n <sub>DPL</sub>                                        | 2   | 1  | 2   | 1    | 2   | 1  | cycle |

| n <sub>DAL</sub>                                        | 5   | 3  | 5   | 3    | 5   | 3  | cycle |

| n <sub>RSA</sub> MRS to ACT Command Period              | 2   | 2  | 2   | 2    | 2   | 2  | cycle |

| n <sub>DOD</sub> DQM to data-out Hi-Z<br>Command period | 2   | 2  | 2   | 2    | 2   | 2  | cycle |

| n <sub>DID</sub> DQM to data-in<br>Command period       | 0   | 0  | 0   | 0    | 0   | 0  | cycle |

| n <sub>HZP</sub> PRE to Data-out Hi-Z<br>Command Period | 2   | 2  | 2   | 2    | 2   | 2  | cycle |

| n <sub>EP</sub> Last Data-out to PRE<br>Command Period  | -1  | -1 | -1  | -1   | -1  | -1 | cycle |

| Last Data-out to ACT n <sub>APR</sub> Command Period    | 2   | 1  | 2   | 1    | 2   | 1  | cycle |

| n <sub>CLE</sub> CKE to CLK Disable Period              | 1   | 1  | 1   | 1    | 1   | 1  | cycle |

| n <sub>CDD</sub> DESEL to Command<br>Disable Period     | 0   | 0  | 0   | 0    | 0   | 0  | cycle |

# **Panasonic**

## [Correlation Between Frequency and Minimum Latency]

| Speed Version      |                                                 | -80 |    | -90 |      | -10 |    | UNIT  |

|--------------------|-------------------------------------------------|-----|----|-----|------|-----|----|-------|

| CLK Cycle Time     |                                                 | 8   | 12 | 9   | 13.5 | 10  | 15 | ns    |

| Freque             | ency                                            | 125 | 83 | 111 | 74   | 100 | 66 | MHz   |

| CAS Latency        |                                                 | 3   | 2  | 3   | 2    | 3   | 2  | cycle |

| $n_{\mathrm{BSR}}$ | BST to Last Valid Data-out<br>Period            | 2   | 1  | 2   | 1    | 2   | 1  | cycle |

| $n_{BSH}$          | BST to Output Buffer<br>Turn-off Period         | 3   | 2  | 3   | 2    | 3   | 2  | cycle |

| $n_{ m BSW}$       | BST to Last Valid Data-in<br>Period             | -1  | -1 | -1  | -1   | -1  | -1 | cycle |

| $n_{PEC}$          | Power down mode Exit to<br>Command Input Period | 1   | 1  | 1   | 1    | 1   | 1  | cycle |

#### [NOTES]

- 1. All voltages are referenced to  $V_{\text{SS}}$ .

- 2. These parameters depend on cycle rates. These values are measured under the value of  $t_{CK}(Min.)$  and  $t_{RC}(Min.)$ . And input signals are changed only one time during  $t_{CK}(Min.)$ .

- 3. These parameters depend on output loading. These values are measured with the output open.

- 4. AC measurement assumes  $t_T$ =1ns. Reference level for measuring timing of input signals is 1.4V. Transition times are measured between  $V_{\rm IH}$  and  $V_{\rm IL}$ .

- 5. AC access time is measured at 1.4V.

- 6. If  $t_T$  is longer than 1ns, reference level for measuring timing of input signals is  $V_{IH}$  and  $V_{IL}$ .

- 7. These parameters account for the number of clock cycle and depend on the operating frequency of the clock, as follows:

the number of clock cycle = specified value of timing/clock period ( count fraction as a whole number )

See "Correlation Between Frequency and Minimum Latency".

#### [AC Test Conditions]

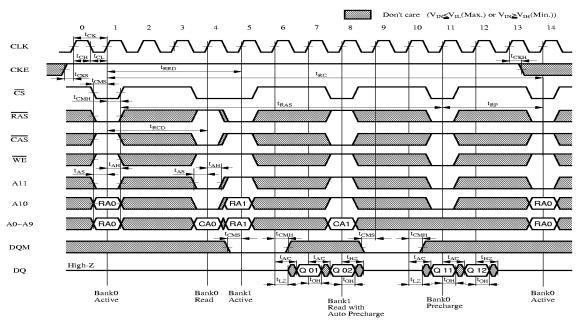

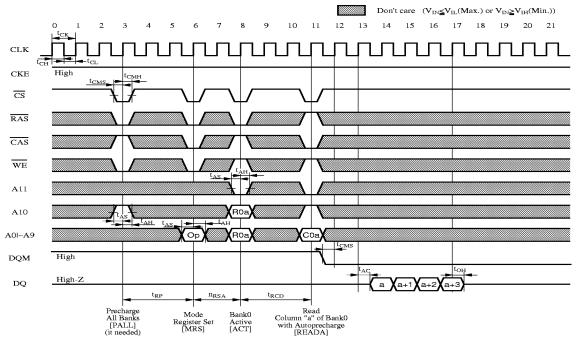

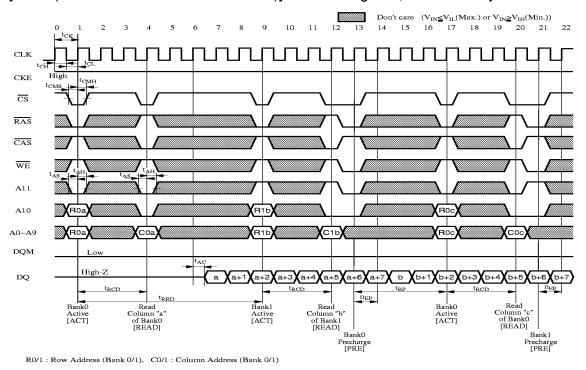

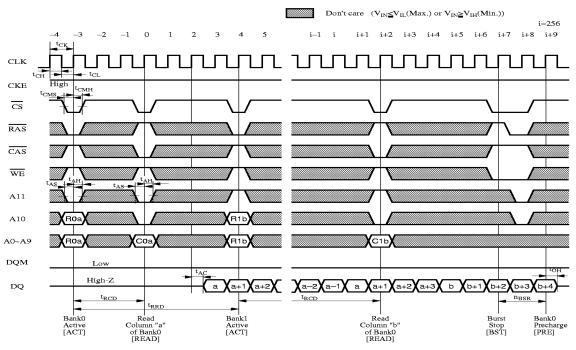

## [AC Timing (Read)] Burst Length=2, CAS Latency=3

$RA0/1: Row\ Address\ (Bank\ 0/1),\quad CA0/1: Column\ Address\ (Bank\ 0/1),\quad Q0\times/1\times: Output\ Data\ (Bank\ 0/1)$

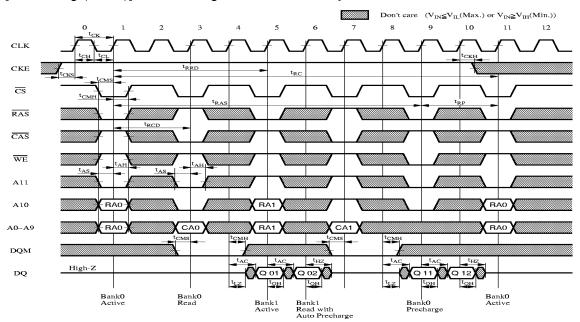

#### [AC Timing (Read)] Burst Length=2, CAS Latency=2

$RA0/1: Row\ Address\ (Bank\ 0/1),\quad CA0/1: Column\ Address\ (Bank\ 0/1),\quad Q0\times/1\times: Output\ Data\ (Bank\ 0/1)$

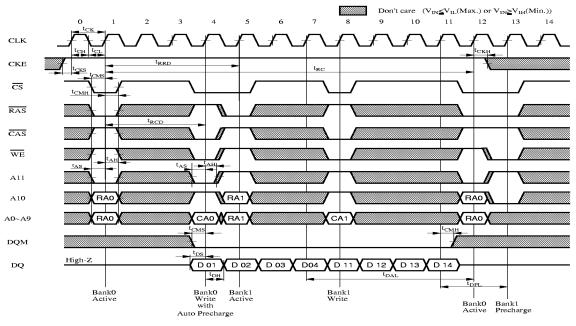

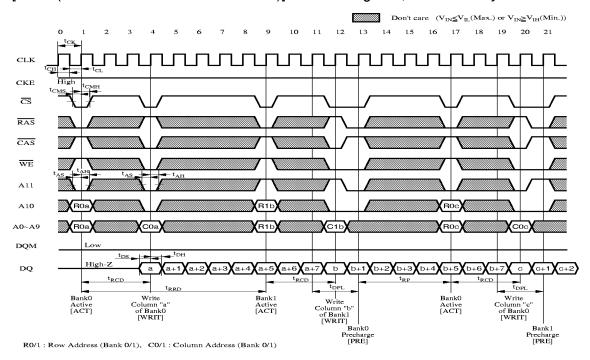

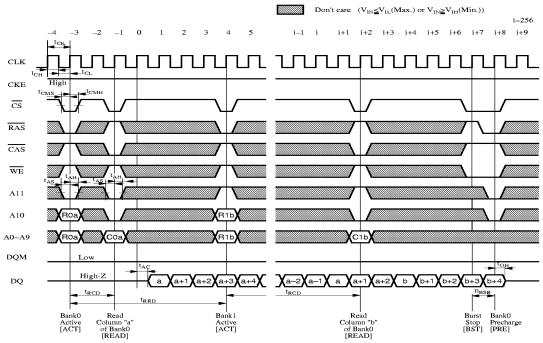

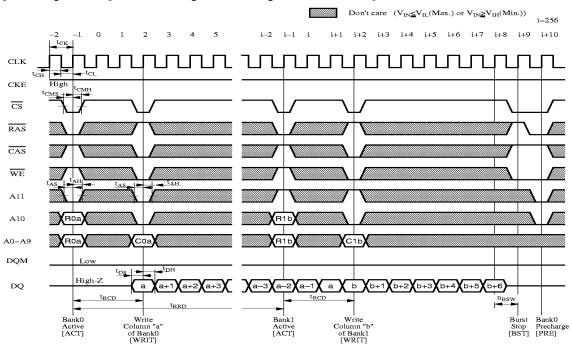

#### [AC Timing (Write)] Burst Length=4, CAS Latency=3

$RA0/l: Row\ Address\ (Bank\ 0/l),\quad CA0/l: Column\ Address\ (Bank\ 0/l),\quad Q0\times/l\times: Output\ Data\ (Bank\ 0/l)$

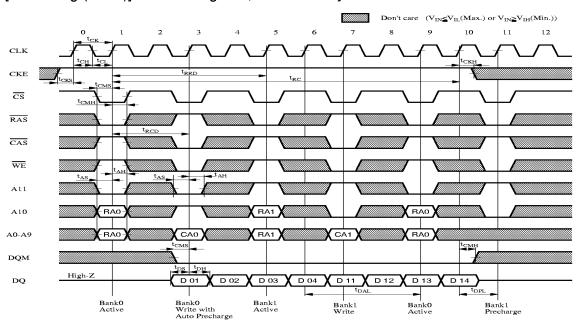

## [AC Timing (Write)] Burst Length=4, CAS Latency=2

$RA0/1: Row\ Address\ (Bank\ 0/1),\quad CA0/1: Column\ Address\ (Bank\ 0/1),\quad Q0\times/1\times: Output\ Data\ (Bank\ 0/1)$

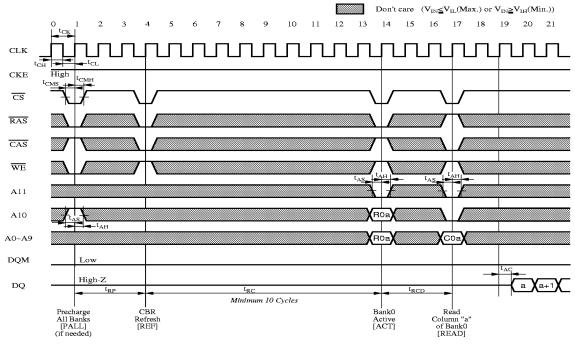

#### [Power On Sequence]

OP: Operation Code, R0: Row Address (Bank 0)

#### [Mode Register Set during operation] Burst Length=4, CAS Latency=3

OP: Operation Code, R0: Row Address (Bank 0), C0: Column Address (Bank 0)

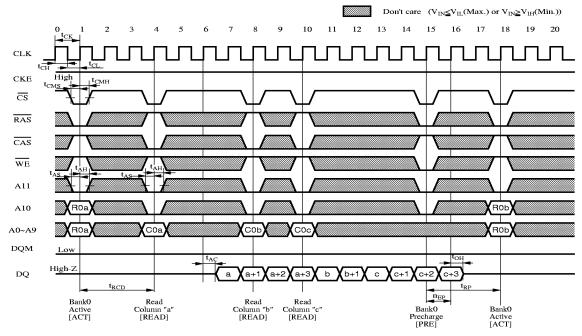

#### [Read (Same Row & Random Column)] Burst Length=4, CAS Latency=3

RA0/1: Row Address (Bank 0), C0: Column Address (Bank 0)

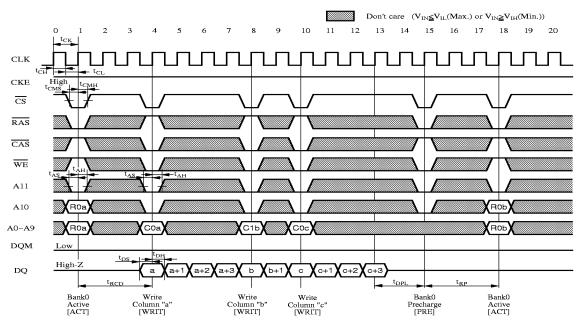

## [Write (Same Row & Random Column)] Burst Length=4, CAS Latency=3

R0: Row Address (Bank 0), C0: Column Address (Bank 0)

#### [Read (Random Row & Bank Interleave)] Burst Length=8, CAS Latency=3

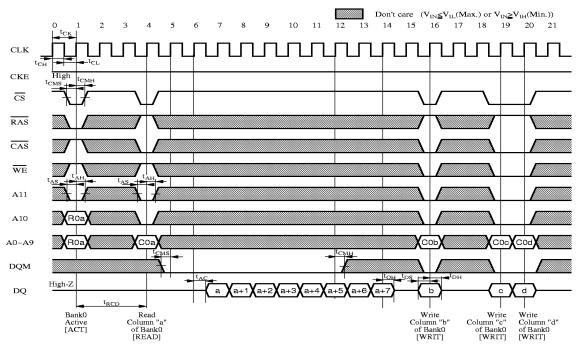

#### [Write (Random Row & Bank Interleave)] Burst Length=8, CAS Latency=3

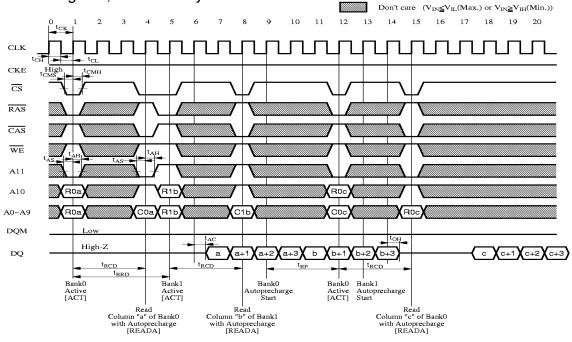

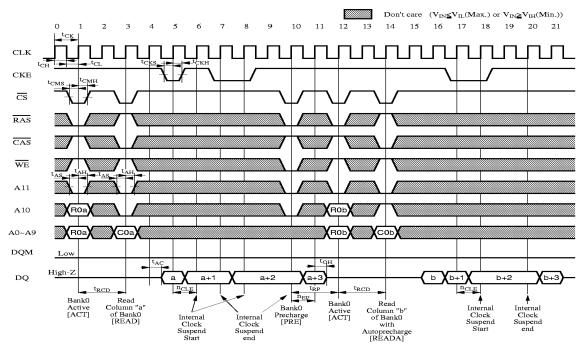

# [Read with Autoprecharge (Random Row & Bank Interleave)] Burst Length=4, CAS Latency=3

R0/1: Row Address (Bank 0/1), C0/1: Column Address (Bank 0/1)

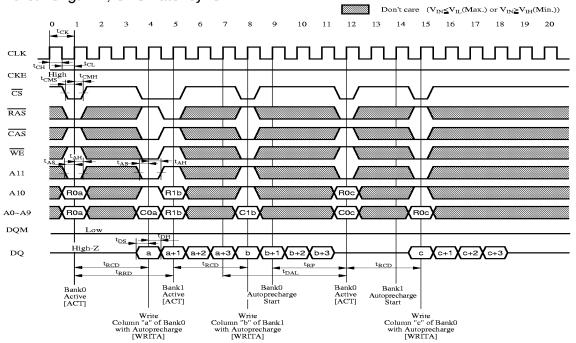

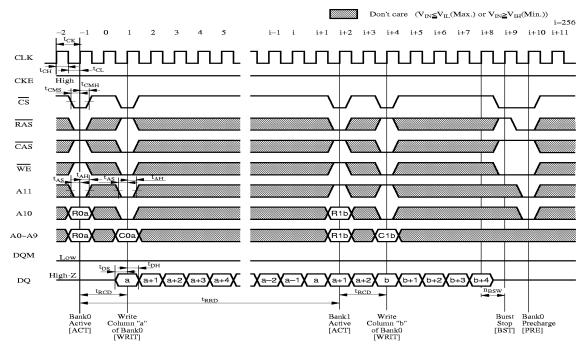

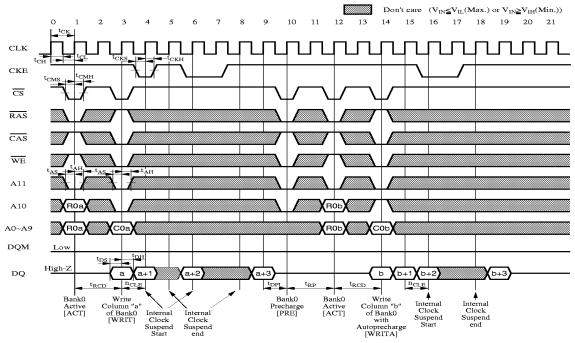

# [Write with Autoprecharge (Random Row & Bank Interleave)] Burst Length=4, CAS Latency=3

R0/1: Row Address (Bank 0/1), C0/1: Column Address (Bank 0/1)

#### [Full Page Read] Burst Length= Full Page, CAS Latency=3

R0/1: Row Address (Bank 0/1), C0/1: Column Address (Bank 0/1)

#### [Full Page Read] Burst Length= Full Page, CAS Latency=2

R0/1: Row Address (Bank 0/1), C0/1: Column Address (Bank 0/1)

#### [Full Page Write] Burst Length=Full Page, CAS Latency=3

$R0/1: Row\ Address\ (Bank\ 0/1),\ C0/1: Column\ Address\ (Bank\ 0/1)$

#### [Full Page Write] Burst Length=Full Page, CAS Latency=2

R0/1: Row Address (Bank 0/1), C0/1: Column Address (Bank 0/1)

#### [CBR (Auto) Refresh] CAS Latency=3

R0: Row Address (Bank 0), C0: Column Address (Bank 0)

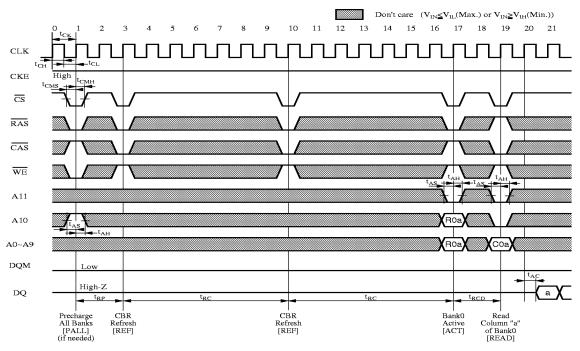

#### [CBR (Auto) Refresh] CAS Latency=2

$R0: Row\ Address\ (Bank\ 0),\ \ C0: Column\ Address\ (Bank\ 0)$

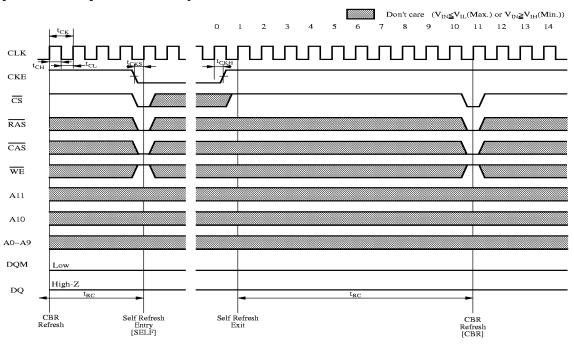

## [Self Refresh] CAS Latency=3

R0: Row Address (Bank 0), C0: Column Address (Bank 0)

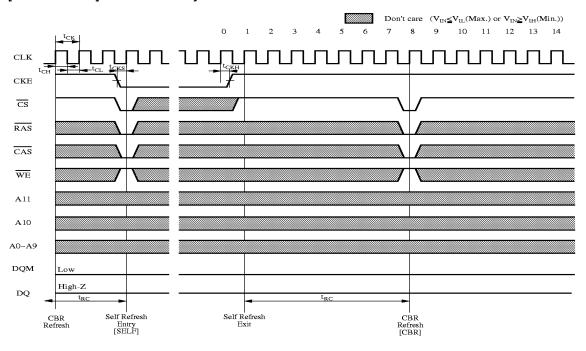

## [Self Refresh] CAS Latency=2

R0: Row Address (Bank 0), C0: Column Address (Bank 0)

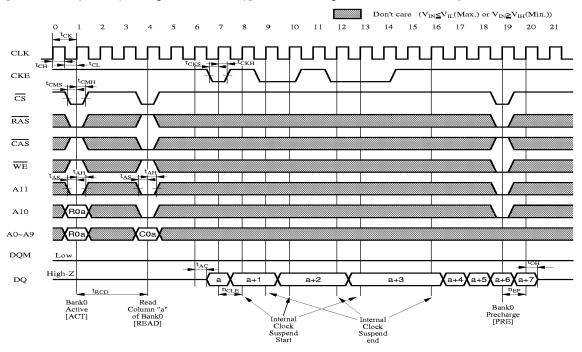

#### [Clock Suspend (during Burst Read)] Burst Length=8, CAS Latency=3

R0: Row Address (Bank0), C0: Column Address (Bank0)

#### [Clock Suspend (during Burst Read)] Burst Length=4, CAS Latency=2

$R0: Row\ Address\ (Bank0),\ C0: Column\ Address\ (Bank0)$

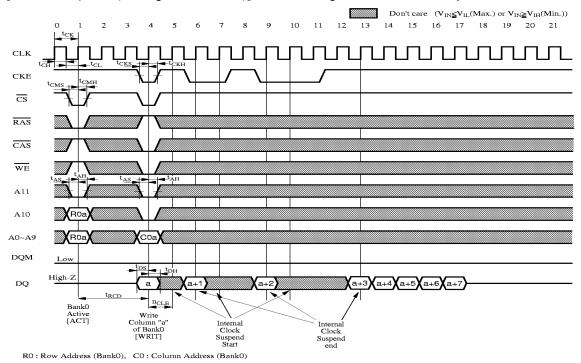

#### [Clock Suspend (during Burst Write)] Burst Length=8, CAS Latency=3

## [Clock Suspend (during Burst Write)] Burst Length=4, CAS Latency=2

R0: Row Address (Bank0), C0: Column Address (Bank0)

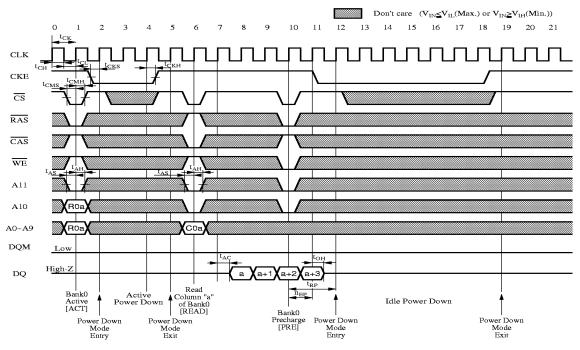

#### [Power Down Mode] Burst Length=4, CAS Latency=2

R0: Row Address (Bank0), C0: Column Address (Bank0)

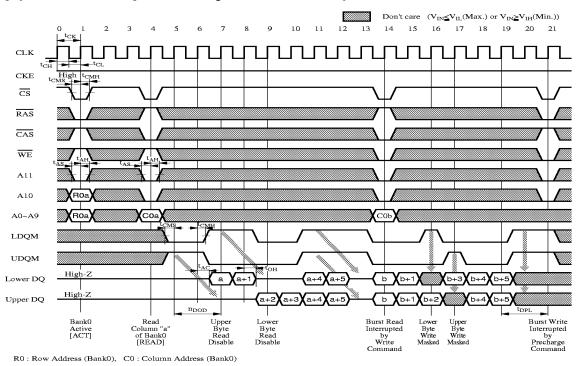

#### [Byte Mask Control] Burst Length≥8, CAS Latency=3

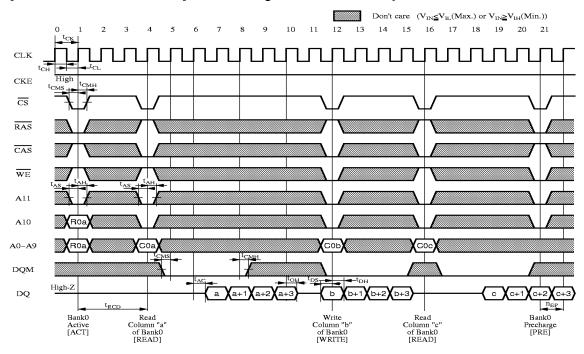

#### [Burst Read & Burst Write] Burst Length=4, CAS Latency=3

R0: Row Address (Bank 0), C0: Column Address (Bank 0)

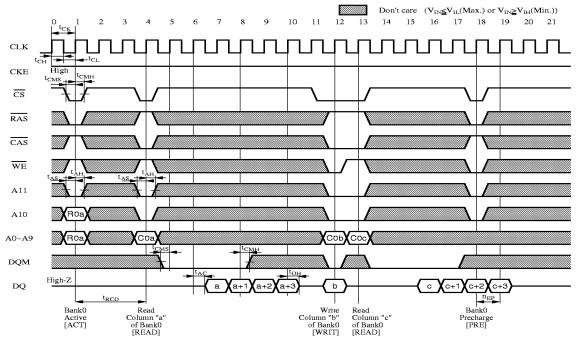

## [Burst Read & Single Write] Burst Length=4, CAS Latency=3

P0: Row Address (Bank 0), C0: Column Address (Bank 0)

## [Burst Read & Single Write] Burst Length=8, CAS Latency=3

R0: Row Address (Bank 0), C0: Column Address (Bank 0)