# AN8725FH

# Semiconductor laser power control IC

# Overview

The AN8725FH is a laser driver IC that can set a laser emitting level to a maximum precision in recording and playback of an optical recording equipment such as PD, and can modulate a laser light in tune with the external signal.

# Features

- Digital setting of playback current, peak current, bias current and abnormal light emitting level

- Peak current and bias current can be modulated by the external signal.

- Driving current set-up (digital set-up) For playback: 8-bit + 4-bit (0 mA to 80 mA) 5-bit + 4-bit (0 mA to 150 mA)

For peak: 4-bit + 8-bit (0 mA to 150 mA) For bias: 4-bit + 8-bit (0 mA to 150 mA)

- Laser output light monitoring circuit built-in

- Abnormal light emitting detecting function built-in: Possible to set up excessive and insufficient light emitting levels with 4-bit DAC for playback and recording, respectively.

- Supply voltage abnormality detection: Voltage down (3.9 V or less), voltage up (6.1 V or more)

### Applications

• Optical disk drive

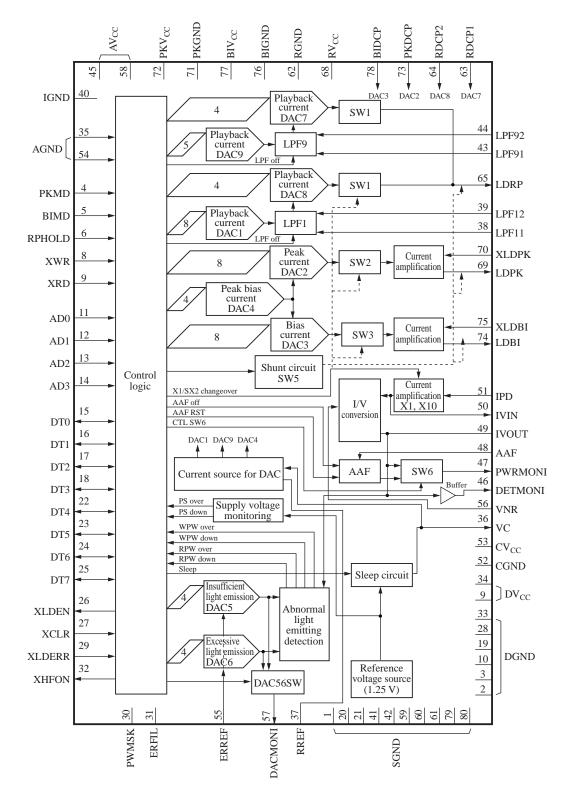

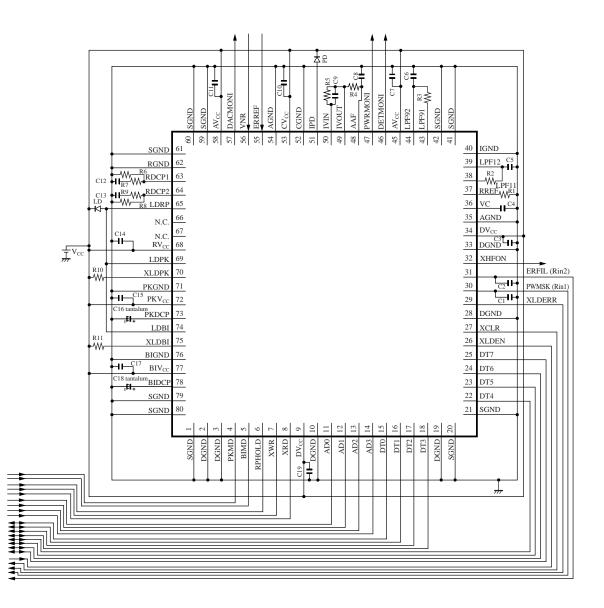

# Block Diagram

# Pin Descriptions

Note) Description on notations of "Category" in the following list:

- IN : Input pin

- I/O  $\,$  : Input/output pin (pull-down with 100 k  $\Omega$ ) IND : Input pin (pull-down with 100 k $\Omega$ ) PS : Power supply/GND pin

- INU : Input pin (pull-up with 100 k $\Omega$ )

- OUT: Output pin

- A: Analog function

D: Digital function

MSC: Parts connecting pin, etc.

|         | log function     |      |      | D. Digital function                                                                                                                                                                                                 |  |  |

|---------|------------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin No. | Symbol           | Cate | gory | Description                                                                                                                                                                                                         |  |  |

| 1       | SGND             | PS   | D    | Pin connected to the chip substrate.<br>Must be used in the same potential as other GND pins.                                                                                                                       |  |  |

| 2       | DGND             | PS   | D    | GND pin exclusive for a logic circuit.                                                                                                                                                                              |  |  |

| 3       | DGND             | PS   | D    | Must be used in the same potential as other GND pins.                                                                                                                                                               |  |  |

| 4       | PKMD             | IND  | D    | Peak current modulation signal input pin.<br>In high-level, the current set up with DAC2 is superimposed on LD.                                                                                                     |  |  |

| 5       | BIMD             | IND  | D    | Bias current modulation signal input pin.<br>In high-level, the current set up with DAC3 is superimposed on LD.                                                                                                     |  |  |

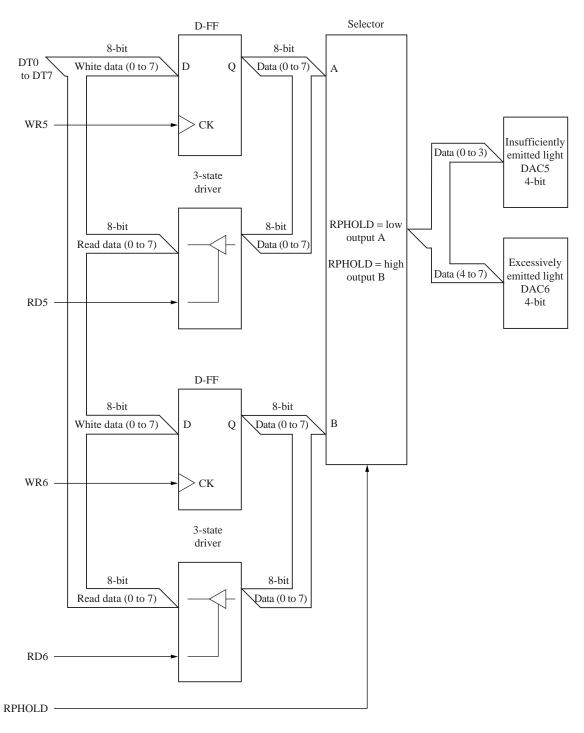

| 6       | RPHOLD           | IND  | D    | Record gate signal input pin.<br>Inputs a low-level in playback and a high-level in recording.<br>Switches an amp. of light monitoring signal, abnormally emitted light<br>detection level and on/off of HF module. |  |  |

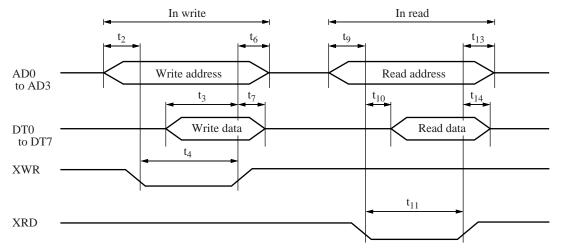

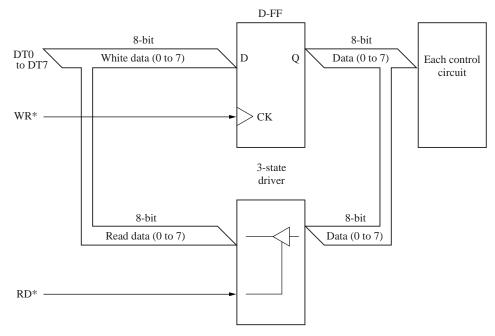

| 7       | XWR              | INU  | D    | Register writing signal pin.<br>Selects a register specified by address in a fall edge and writes a bus data<br>on the register of the address specified in the rise edge.                                          |  |  |

| 8       | XRD              | INU  | D    | Register read-out signal pin.<br>Register data of the address specified in low appears on the bus.                                                                                                                  |  |  |

| 9       | DV <sub>CC</sub> | PS   | D    | Power supply pin exclusive for a logic circuit.<br>Must be used in the same potential as other power supply pins.                                                                                                   |  |  |

| 10      | DGND             | PS   | D    | GND pin exclusive for a logic circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                     |  |  |

| 11      | AD0              | IND  | D    | 4-bit address pin for registers.                                                                                                                                                                                    |  |  |

| 12      | AD1              | IND  | D    | Selects the register to be accessed.                                                                                                                                                                                |  |  |

| 13      | AD2              | IND  | D    |                                                                                                                                                                                                                     |  |  |

| 14      | AD3              | IND  | D    |                                                                                                                                                                                                                     |  |  |

| 15      | DT0              | I/O  | D    | Data I/O 8-bit bus pin.                                                                                                                                                                                             |  |  |

| 16      | DT1              | I/O  | D    | The bus to set the data to be written on a register and to read out the da                                                                                                                                          |  |  |

| 17      | DT2              | I/O  | D    | of a register.                                                                                                                                                                                                      |  |  |

| 18      | DT3              | I/O  | D    | 1                                                                                                                                                                                                                   |  |  |

| 19      | DGND             | PS   | D    | GND pin exclusive for a logic circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                     |  |  |

| Pin No. | Symbol | Cate | gory | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20      | SGND   | PS   | D    | Pin connected to the chip substrate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 21      | SGND   | PS   | D    | Must be used in the same potential as other GND pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 22      | DT 4   | I/O  | D    | Data I/O 8-bit bus pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23      | DT 5   | I/O  | D    | The bus to set the data to be written on a register and to read out the data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 24      | DT 6   | I/O  | D    | of a register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 25      | DT 7   | I/O  | D    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 26      | XLDEN  | INU  | D    | LD enable input pin.<br>In a high-level or open mode, LD becomes off and open. This state is suited<br>to check the LD characteristics in keeping a connection to the IC. At the<br>time power off, both ends of LD are short-circuited by the IC for protection.<br>In the low-level, it returns to a normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 27      | XCLR   | IND  | D    | Clear signal input pin.<br>Sets an LDDENB register to "0" in the low-level and presets the status of<br>each DAC and each switch to an initial state as defined separately.<br>But six registers for an abnormal detection are not cleared. In this state,<br>each output of a current amplification 1, 2, 3 are in the off state and a<br>shunt circuit becomes on to continue to protect LD.<br>Setting this pin to the high-level and the LDDENB register to "1", it returns<br>to a normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 28      | DGND   | PS   | D    | GND pin exclusive for a logic circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 29      | XLDERR | OUT  | D    | Laser abnormality detection output pin.<br>When a supply voltage or a laser light emission exceeds a fixed range, it<br>goes to low-level. A supply voltage abnormality is detected for the volt-<br>age drop (3.9 V or less) or voltage rise (6.1 V or more). And an abnormal<br>light emission is detected for an excessive or weaker light emission set up<br>by 4-bit DAC5 and DAC6. This abnormality detection is latched so as to<br>prevent it from being reset until ERRCLR register is set to "1".<br>Further, each DAC output of a playback current, a peak current and a bias<br>current can be set to off, a shunt circuit be set to on and LD between anode<br>and GND be short-circuited by 100 $\Omega$ so that LD can be protected. This<br>protection function is latched to keep it from being reset until ERRCLR is<br>set to "1". Selection of either operation or non-operation for this opera-<br>tion can be made by an STPMSK register. |

| 30      | PWMSK  | MSC  | D    | The pin to set up the mask time for a transitional response output that<br>comes out at switching a detection level of excessive or insufficient light<br>emission by RPHOLD. Set a mask time by an external capacitor between<br>PWMSK and DGND and the resistor (10 k $\Omega$ ) inside the IC. This pin is for<br>a schmitt-trigger input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Pin No. | Symbol           | Cate | gory | Description                                                                                                                                                                                                                                                              |  |  |  |

|---------|------------------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 31      | ERFIL            | MSC  | D    | Filter setting pin to avoid a detection error of laser abnormality caused<br>by noise.<br>Connect an external capacitor between ERFIL and DGND, and set a filter<br>together with a resistor (10 k $\Omega$ ) inside the IC. This pin is for schmitt-trigger<br>input.   |  |  |  |

| 32      | XHFON            | OUT  | D    | HF module on/off control signal output pin.<br>High corresponds to off and low to on.                                                                                                                                                                                    |  |  |  |

| 33      | DGND             | PS   | D    | GND pin exclusive to a logic circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                           |  |  |  |

| 34      | DV <sub>CC</sub> | PS   | D    | Power supply pin exclusive to a logic circuit.<br>Must be used in the same potential as other power supply pins.                                                                                                                                                         |  |  |  |

| 35      | AGND             | PS   | A    | GND pin exclusive to a analog circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                          |  |  |  |

| 36      | VC               | MSC  | А    | Output pin for reference voltage (1.25 V).<br>Connects a capacitor C between this pin and AGND for de-coupling.                                                                                                                                                          |  |  |  |

| 37      | RREF             | MSC  | A    | Reference resistor connecting pin to determine an output current for each DAC.<br>Connect a resistor of 10 k $\Omega$ between RREF and AGND.                                                                                                                             |  |  |  |

| 38      | LPF11            | MSC  | Α    | LPF characteristic setting pin for DAC1 and DAC8.                                                                                                                                                                                                                        |  |  |  |

| 39      | LPF12            | MSC  | А    | Connect an external resistor between LPF11 and LPF12, and then capacitor between LPF12 and IGND to set up a cutoff frequency.                                                                                                                                            |  |  |  |

| 40      | IGND             | PS   | A    | <ul><li>GND pin for playback power supply setting DAC1, DAC9 and disturbance reduction LPF.</li><li>Must be used in the same potential as other GND pins.</li></ul>                                                                                                      |  |  |  |

| 41      | SGND             | PS   | D    | Pin connected to the chip substrate.                                                                                                                                                                                                                                     |  |  |  |

| 42      | SGND             | PS   | D    | Must be used in the same potential as other GND pins.                                                                                                                                                                                                                    |  |  |  |

| 43      | LPF91            | MSC  | А    | LPF characteristic setting pin for DAC9 and DAC7.                                                                                                                                                                                                                        |  |  |  |

| 44      | LPF92            | MSC  | A    | Connect an external resistor between LPF91 and LPF92 and then capacitor between LPF92 and IGND to set a cutoff frequency.                                                                                                                                                |  |  |  |

| 45      | AV <sub>CC</sub> | PS   | А    | Power supply pin for an analog circuit, a reference supply voltage circuit, et<br>Must be used in the same potential as other power supply pins.                                                                                                                         |  |  |  |

| 46      | DETMONI          | OUT  | A    | Pin to monitor a signal for detecting abnormally emitted light.<br>In a playback mode, the signal output is five times that in recording<br>(ten times is posisible by a register setting). Has offset to VNR due to<br>being outputted through a buffer of transistors. |  |  |  |

| 47      | PWRMONI          | OUT  | A    | Laser emitting light monitor signal.<br>In a low-level of RPHOLD, the amplifier output has 10 times gain<br>compared with recording, and is equipped with AFF.                                                                                                           |  |  |  |

| Pin No. | Symbol           | Cate | gory | Description                                                                                                                                                                                                                                                                                                 |

|---------|------------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48      | AAF              | MSC  | А    | AAF characteristic setting pin for optical monitor circuit.<br>Connect an external resistor, capacitor between AAF and IVOUT and set<br>up a cutoff frequency.                                                                                                                                              |

| 49      | IVOUT            | OUT  | А    | I to V conversion signal output pin.<br>Connect an external variable resistor between IVIN and IVOUT.                                                                                                                                                                                                       |

| 50      | IVIN             | MSC  | А    | I to V conversion resistor connection pin.<br>Connect an external variable resistor between IVIN and IVOUT.                                                                                                                                                                                                 |

| 51      | IPD              | MSC  | A    | <ul> <li>Pin photo diode (PD) connection pin.</li> <li>Connect a pin photo diode for detecting a semiconductor laser emitting light. Connect anode to this pin.</li> <li>Applicable to a source-type PD which has a typical value of 40 μA to 160 μA output in object lens output power of 1 mW.</li> </ul> |

| 52      | CGND             | PS   | А    | GND pin in an optical monitor circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                                                             |

| 53      | CV <sub>CC</sub> | PS   | А    | Power supply pin in an optical monitor circuit.<br>Must be used in the same potential as other power supply pins.                                                                                                                                                                                           |

| 54      | AGND             | PS   | А    | GND pin exclusive to a analog circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                                                             |

| 55      | ERREF            | IN   | A    | Abnormally emitting light detecting range setting pin.<br>Sets a full scale voltage of DAC5 and DAC6.<br>A setting range is VNR or more and input range of an external ADC<br>or less.                                                                                                                      |

| 56      | VNR              | IN   | А    | Reference level input pin for PWRMONI output.<br>Input a reference voltage of 1.25 V of an external ADC.                                                                                                                                                                                                    |

| 57      | DACMONI          | OUT  | А    | DAC5, DAC6 monitor pin.<br>DAC5 voltage is outputted when DAC56 SW register is low, DAC6<br>voltage is outputted when DAC6 voltage is high.                                                                                                                                                                 |

| 58      | AV <sub>CC</sub> | PS   | А    | Power supply pin for an analog circuit, a reference supply voltage circuit, etc.<br>Must be used in the same potential as other power supply pins.                                                                                                                                                          |

| 59      | SGND             | PS   | D    | Pin connected to the chip substrate.                                                                                                                                                                                                                                                                        |

| 60      | SGND             | PS   | D    | Must be used in the same potential as other GND pins.                                                                                                                                                                                                                                                       |

| 61      | SGND             | PS   | D    |                                                                                                                                                                                                                                                                                                             |

| 62      | RGND             | PS   | А    | GND pin for the lead current setting DAC7 and DAC8.<br>Must be used in the same potential as other GND pins.                                                                                                                                                                                                |

| 63      | RDCP1            | MSC  | A    | Pin to connect a de-coupling capacitor to protect the output current of DAC7, the read current setting circuit, from disturbance by a switching noise such as peak current.<br>(Connects a capacitor between RDCP1 and RGND.)                                                                               |

| Pin No. | Symbol            | Cate | gory | Description                                                                                                                                                                                                                               |

|---------|-------------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64      | RDCP2             | MSC  | A    | Pin to connect a de-coupling capacitor to protect the output current of DAC7, the read current setting circuit, from disturbance by a switching noise such as peak current.<br>(Connects a capacitor between RDCP2 and RGND.)             |

| 65      | LDRP              | OUT  | A    | Source type read current (DAC1, DAC7, DAC8, DAC9) output pin.<br>Possible to set up the range of 0 mA to 150 mA in the precision of 8-bit<br>+ 4-bit + 5-bit + 4-bit.<br>Output voltage range is 1.0 V to 3.5 V.                          |

| 66      | N.C.              | _    |      | N.C. pin.                                                                                                                                                                                                                                 |

| 67      | N.C.              | -    | —    | Open the pin or connect to GND.                                                                                                                                                                                                           |

| 68      | RV <sub>CC</sub>  | PS   | A    | Power supply pin for read current setting DAC7, DAC8.<br>Consumes approximately a quarter of the necessary read current.<br>Must be used in the same potential as other power supply pins.                                                |

| 69      | LDPK              | OUT  | А    | Source-type peak current (DAC2) output pin.<br>Possible to set the range of 0 mA to 150 mA in the accuracy of 8-bit.<br>The output voltage range is 1.0 V to 3.2 V.                                                                       |

| 70      | XLDPK             | IN   | A    | Sink-type peak current output pin.<br>Approximately three fourths of LDRK output current are outputted from<br>this pin.                                                                                                                  |

| 71      | PKGND             | PS   | А    | GND pin of DAC2 in the peak current setting circuit.<br>Must be used in the same potential as other GND pins.                                                                                                                             |

| 72      | PKV <sub>CC</sub> | PS   | A    | DAC2 power supply pin in the peak current setting circuit.<br>Consumes approximately a quarter of the setting current.<br>Must be used in the same potential as other power supply pins.                                                  |

| 73      | PKDCP             | MSC  | A    | Pin to connect a de-coupling capacitor to avoid the output current disturbance,<br>which is caused by a switching noise such as peak current, in peak current<br>setting circuit DAC2.<br>(Connects a capacitor between PKDCP and PKGND.) |

| 74      | LDBI              | OUT  | A    | Source-type bias current (DAC3) output pin.<br>Possible to set the range of 0 mA to 150 mA in the accuracy of 8-bit.<br>Output voltage range is 1.0 V to 3.2 V.                                                                           |

| 75      | XLDBI             | IN   | A    | Sink-type peak current output pin.<br>Approximately three fourths of LDBI output current are outputted from<br>this pin.                                                                                                                  |

| 76      | BIGND             | PS   | А    | GND pin of a bias current setting circuit DAC3.<br>Must be used in the same potential as other GND pins.                                                                                                                                  |

| 77      | BIV <sub>CC</sub> | PS   | А    | Power supply pin of a bias current setting circuit DAC3.<br>Consumes approximately one fourth of a setting current.<br>Must be used in the same potential as other power supply pins.                                                     |

| Pin No. | Symbol | Category |   | Description                                                                                                                                                                                                                                 |

|---------|--------|----------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 78      | BIDCP  | MSC      | A | Pin to connect a de-coupling capacitor to avoid the output current disturbance,<br>which is caused by a switching noise such as bias current, of a bias current<br>setting circuit DAC3.<br>(Connects a capacitor between BIDCP and BIGND.) |

| 79      | SGND   | PS       | D | Pin connected to the chip substrate.                                                                                                                                                                                                        |

| 80      | SGND   | PS       | D | Must be used in the same potential as other GND pins.                                                                                                                                                                                       |

### Absolute Maximum Ratings

| Parameter                        | Symbol           | Rating                        | Unit |

|----------------------------------|------------------|-------------------------------|------|

| Supply voltage                   | V <sub>CC</sub>  | 7.0                           | V    |

| Input voltage                    | V <sub>IN</sub>  | -0.4 to V <sub>CC</sub> +0.4  | V    |

| Outoput voltage                  | V <sub>OUT</sub> | -0.4 to V <sub>CC</sub> +0.4  | V    |

| Parts connecting pin voltage     | V <sub>MSC</sub> | – 0.4 to V <sub>CC</sub> +0.4 | V    |

| Supply current                   | I <sub>CC</sub>  | 80                            | mA   |

| Pin current                      | I <sub>PIN</sub> | -100 to +100                  | mA   |

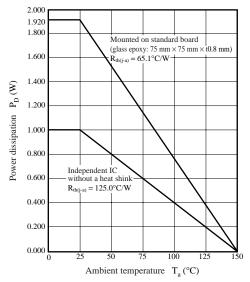

| Power dissipation *2             | P <sub>D</sub>   | 600                           | mW   |

| Operating ambient temperature *1 | T <sub>opr</sub> | -20 to +75                    | °C   |

| Storage temperature *1           | T <sub>stg</sub> | -55 to +150                   | °C   |

Note) \*1: Except for the operating ambient temperature and storage temperature, all ratings are for  $T_a = 25^{\circ}C$ .

\*2: The power dissipation shown is for the IC package in single unit at  $T_a = 75^{\circ}C$ .

Refer to "■ Application Notes, 1. P<sub>D</sub> — T<sub>a</sub> curves of QFP080-P-1212".

#### Recommended Operating Range

| Parameter      | Symbol          | Range        | Unit |

|----------------|-----------------|--------------|------|

| Supply voltage | V <sub>CC</sub> | 4.50 to 5.50 | V    |

# Electrical Characteristics at $V_{CC} = 5.0 \text{ V}, \text{ T}_a = 25^{\circ}\text{C}$

| Parameter                   | Symbol           | Conditions                                                                                                                                        | Min  | Тур  | Max  | Unit |

|-----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Supply current              |                  |                                                                                                                                                   |      |      |      |      |

| Supply current              | I <sub>CC</sub>  | $\label{eq:clr} \begin{array}{l} \text{XCLR} = \text{low, digital I/O pin} = \text{open,} \\ \text{I}_{\text{PD}} = 0 \; \mu\text{A} \end{array}$ |      | 20   | 30   | mA   |

| Sleep mode supply current   | I <sub>SLP</sub> | Sleep = 1, $I_{PD} = 0 \ \mu A$                                                                                                                   | —    | 3    | 4    | mA   |

| Reference voltage block     |                  |                                                                                                                                                   |      |      |      |      |

| Reference voltage output    | V <sub>REF</sub> |                                                                                                                                                   | 1.20 | 1.25 | 1.30 | V    |

| Reference voltage variation | $\Delta V_{REF}$ | $V_{CC} = 4.5 \text{ V} \text{ to } 5.5 \text{ V}, I_{REF} = 0 \text{ mA}$                                                                        |      | _    | ±15  | mV   |

|                             |                  | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V}$<br>$I_{REF} = -1 \text{ mA to } +1 \text{ mA}$                                                         |      | _    | ± 20 |      |

| Maximum output current      | $\Delta V_{OM}$  | $I_{REF} = -1.5 \text{ mA},$<br>difference from $I_{REF} = 0 \text{ mA}$                                                                          | _    | _    | ± 50 | mV   |

| Parameter                                           | Symbol                      | Conditions                                                                                            | Min                                                 | Тур                  | Max                 | Unit  |

|-----------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------|---------------------|-------|

| Digital block                                       |                             |                                                                                                       |                                                     |                      |                     |       |

| High-level input voltage                            | V <sub>IH</sub>             | To be applied to a digital input pin                                                                  | $\begin{array}{c} 0.8 \times \\ V_{CC} \end{array}$ |                      |                     | V     |

| Low-level input voltage                             | V <sub>IL</sub>             | To be applied to a digital input pin                                                                  |                                                     |                      | $0.2 \times V_{CC}$ | V     |

| High-level input voltage<br>(Schmitt-trigger input) | V <sub>IHSHC</sub>          | To be applied to PWMSK, ERFIL pin                                                                     | $0.8 \times V_{CC}$                                 |                      |                     | V     |

| Low-level input voltage<br>(Schmitt-trigger input)  | V <sub>ILSHC</sub>          | To be applied to PWMSK, ERFIL pin                                                                     |                                                     |                      | $0.2 \times V_{CC}$ | V     |

| High-level output voltage                           | V <sub>OH</sub>             | $I_{OH} = -2 \text{ mA}$                                                                              | $0.8 \times V_{CC}$                                 |                      |                     | V     |

| Low-level output voltage                            | V <sub>OL1</sub>            | $I_{OL} = +2 \text{ mA}$                                                                              |                                                     |                      | $0.2 \times V_{CC}$ | V     |

|                                                     | V <sub>OL2</sub>            | $I_{OL} = +0.5 \text{ mA}$                                                                            |                                                     |                      | 0.4                 |       |

| Input pull-up, pull-down resistance                 | R <sub>PD</sub>             | Pull-up: $V_{IL} = 0 V$<br>Pull-down: $V_{IH} = 5.0 V$                                                | 75                                                  | 100                  | 125                 | kΩ    |

| Input leak                                          | I <sub>LKH</sub>            | To be applied to a digital input pin, $V_{OH} = 5.25 \text{ V}$                                       |                                                     |                      | 80                  | μA    |

|                                                     | I <sub>LKL</sub>            | To be applied to a digital input pin, $V_{OL} = 0 V$                                                  |                                                     |                      | 10                  |       |

| Entire optical monitor                              |                             |                                                                                                       |                                                     |                      |                     |       |

| Offset voltage at playback                          | V <sub>PMOFR</sub>          | $VR1 = 1 k\Omega$ , $I_{PD} = 0 mA$                                                                   | -15                                                 |                      | 15                  | mV    |

|                                                     |                             | VR1 = 1 k $\Omega$ , difference from an ideal value at I <sub>PD</sub> = 100 $\mu$ A to 200 $\mu$ A   | -40                                                 | 0                    | 40                  |       |

| Offset voltage at recording                         | V <sub>PMOFW</sub>          | $VR1 = 1 k\Omega$ , $I_{PD} = 0 mA$                                                                   | -15                                                 |                      | 15                  | mV    |

|                                                     |                             | VR1 = 1 k $\Omega$ , difference from an ideal value at I <sub>PD</sub> = 100 $\mu$ A to 2 000 $\mu$ A | -20                                                 | 0                    | 20                  |       |

| Gain ratio                                          | GR                          | $G_{PMR}/G_{PMW}$ ,<br>output = VNR +0.6 V to 2.0 V                                                   | 9.0                                                 | 10.0                 | 11.0                | times |

| Maximum output voltage                              | V <sub>PM max</sub>         |                                                                                                       | $V_{CC} \times 0.73$                                | $V_{CC} \times 0.78$ |                     | V     |

| Minimum output voltage                              | V <sub>PM min</sub>         |                                                                                                       |                                                     |                      | VNR-<br>0.015       | V     |

| f characteristics at playback                       | f <sub>PMR AAF</sub><br>OFF | AAF-off VR1 = 1 k $\Omega$ ,<br>-3 dB, I <sub>PD</sub> = 100 $\mu$ A to 200 $\mu$ A                   | 4                                                   | 6                    |                     | MHz   |

| f characteristics at recording                      | f <sub>PMW</sub>            | VR1 = 1 kΩ,<br>-3 dB, $I_{PD}$ = 100 μA to 2 000 μA                                                   | 6                                                   | 7.5                  |                     | MHz   |

| Settling time at playback                           | t <sub>PMSETR</sub>         | VR1 = 1 k $\Omega$ , error ±0.5%,<br>output variation: Range of 0 V to 2 V                            | _                                                   | 200                  | 400                 | ns    |

| Settling time at recording                          | t <sub>PMSETW</sub>         | VR1 = 1 k $\Omega$ , error ±0.5%,<br>output variation: Range of 0 V to 2 V                            | —                                                   | 200                  | 400                 | ns    |

# Electrical Characteristics at $V_{CC} = 5.0 \text{ V}$ , $T_a = 25^{\circ}C$ (continued)

| Parameter                        | Symbol            | Conditions                                                                                                                     | Min  | Тур  | Max  | Unit  |  |

|----------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| Current amplification changeover |                   |                                                                                                                                |      |      |      |       |  |

| Gain at playback                 | G <sub>IPDR</sub> | Reg7 = "80h", $I_{PD}$ = 40 $\mu A$ to 240 $\mu A$                                                                             | 9.0  | 10.0 | 11.0 | times |  |

| Gain at recording                | G <sub>IPDW</sub> | Reg7 = "C0h", $I_{PD}$ = 200 $\mu A$ to 3 200 $\mu A$                                                                          | 0.9  | 1.0  | 1.1  | times |  |

| Gain ratio                       | GR <sub>IPD</sub> | G <sub>IPDR</sub> /G <sub>IPDW</sub>                                                                                           | 9.0  | 10.0 | 11.0 | times |  |

| I to V conversion block          |                   |                                                                                                                                |      |      |      |       |  |

| Offset voltage                   | V <sub>IVOF</sub> | $VR1 = 0 \Omega, I_{PD} = 0 mA$                                                                                                | -15  |      | 15   | mV    |  |

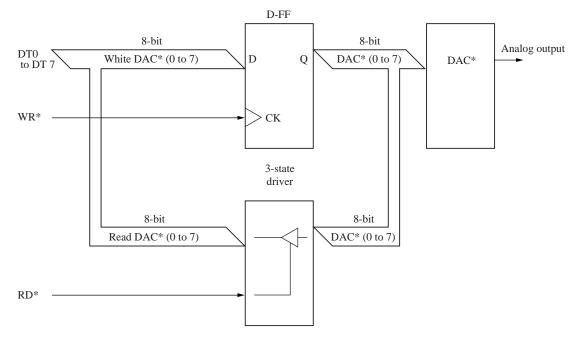

| DAC1 block                       |                   |                                                                                                                                |      |      |      |       |  |

| Resolution                       | RES1              |                                                                                                                                | _    | 8    |      | bit   |  |

| Integral linearity error         | EL1               |                                                                                                                                | -1.0 | _    | 10.0 | LSB   |  |

| Differential linearity error     | ED1               |                                                                                                                                | -1.0 |      | 1.5  | LSB   |  |

| Maximum output current           | I <sub>1max</sub> | DAC1 = "FFh", DAC8 [Fh],<br>DAC7 [0h], DAC9 [00h]                                                                              | 70   | 80   | 90   | mA    |  |

| Offset current                   | I <sub>10F1</sub> | "00h" LPF-on, DAC8 [Fh],<br>DAC7 [0h], DAC9 [00h],<br>DAC7, DAC8 characteristics included                                      | -1   |      | 1    | mA    |  |

|                                  | I <sub>10F2</sub> | "00h" LPF-off, DAC8 [Fh],<br>DAC7 [0h], DAC9 [00h]                                                                             | -250 |      | 250  | μA    |  |

| LPF on/off gain ratio            | GR <sub>DAL</sub> | $G_{LPFON} / G_{LPFOFF}$ , input amplitude 0 V to 2 V                                                                          | 0.95 | 1    | 1.05 | times |  |

| Settling time                    | t <sub>SDA1</sub> | XWR ↑ to DAC1 [10h to 8Fh],<br>±2 LSB range, DAC7 [0h], DAC8 [Fh],<br>DAC9 [00h] LPF-off,<br>LPF11 pin open,<br>RDCP2 pin open |      | 400  | 800  | ns    |  |

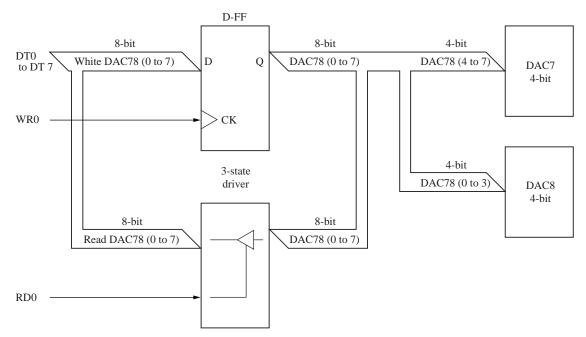

#### DAC7 block

| Resolution                   | RES7              |                                                                             | —     | 4   | —   | bit |

|------------------------------|-------------------|-----------------------------------------------------------------------------|-------|-----|-----|-----|

| Integral linearity error     | EL7               |                                                                             | -1.0  | _   | 1.0 | LSB |

| Differential linearity error | ED7               |                                                                             | - 0.5 |     | 0.5 | LSB |

| Maximum output current       | I <sub>7max</sub> | Set to DAC7 = "Fh",<br>DAC9 [1Fh], DAC1 [00h], DAC8 [0h]                    | 133   | 150 | 170 | mA  |

| Minimum output current       | I <sub>7min</sub> | Set to DAC7 = "0h",<br>DAC9 [1Fh], DAC1 [00h], DAC8 [0h]                    | - 0.1 | 0   | 0.1 | mA  |

| Settling time                | t <sub>SDA7</sub> | XWR ↑ to DAC7 [0h to Fh],<br>DAC9 [1Fh], ±0.5 LSB,<br>DAC1 [00h], DAC8 [0h] |       | 50  | 500 | ns  |

### DAC8 block

| Resolution                   | RES8 |       | 4 |     | bit |

|------------------------------|------|-------|---|-----|-----|

| Integral linearity error     | EL8  | -1.0  | _ | 1.0 | LSB |

| Differential linearity error | ED8  | - 0.5 |   | 0.5 | LSB |

| Parameter                    | Symbol            | Conditions                                                                  | Min   | Тур | Max | Unit |

|------------------------------|-------------------|-----------------------------------------------------------------------------|-------|-----|-----|------|

| DAC8 block (continued)       |                   |                                                                             |       |     |     |      |

| Maximum output current       | I <sub>8max</sub> | Set to DAC8 = "Fh",<br>DAC1 [FFh], DAC9 [1Fh], DAC7 [0h]                    | 70    | 80  | 90  | mA   |

| Minimum output current       | I <sub>8min</sub> | Set to DAC8 = "0h",<br>DAC1 [FFh], DAC9 [1Fh], DAC7 [0h]                    | 4     | 5   | 6   | mA   |

| Settling time                | t <sub>SDA8</sub> | XWR ↑ to DAC8 [0h to Fh],<br>DAC1 [80h], ±0.5 LSB,<br>DAC9 [00h], DAC7 [0h] |       | 50  | 250 | ns   |

| DAC2 block                   | I                 |                                                                             |       |     |     |      |

| Resolution                   | RES2              |                                                                             |       | 8   |     | bit  |

| Integral linearity error     | EL2               |                                                                             | -1.0  |     | 5.0 | LSB  |

| Differential linearity error | ED2               |                                                                             | -1.0  |     | 1.0 | LSB  |

| Maximum output current       | I <sub>2max</sub> | DAC2 = "FFh", DAC4 [Fh]                                                     | 133   | 150 | 170 | mA   |

| Offset current               | I <sub>2OF</sub>  | DAC2 = "00h", DAC4 [Fh]                                                     | - 0.1 |     | 0.1 | mA   |

| Settling time                | t <sub>SDA2</sub> | XWR ↑ to DAC2 [10h to FFh],<br>±2.0 LSB, DAC4 [Fh]                          | —     | 100 | 250 | ns   |

| DAC3 block                   | ·                 |                                                                             |       |     |     |      |

| Resolution                   | RES3              |                                                                             |       | 8   | _   | bit  |

| Integral linearity error     | EL3               |                                                                             | -1.0  |     | 5.0 | LSB  |

| Differential linearity error | ED3               |                                                                             | -1.0  |     | 1.0 | LSB  |

| Maximum output current       | I <sub>3max</sub> | DAC3 = "FFh", DAC4 [Fh]                                                     | 133   | 150 | 170 | mA   |

| Offset current               | I <sub>3OF</sub>  | DAC3 = "00h", DAC4 [Fh]                                                     | - 0.1 | _   | 0.1 | mA   |

| Settling time                | t <sub>SDA3</sub> | XWR ↑ to DAC3 [10h to FFh],<br>±2.0 LSB, DAC4 [Fh]                          | —     | 200 | 450 | ns   |

| DAC4 block                   |                   |                                                                             |       |     |     |      |

| Resolution                   | RES4              |                                                                             | —     | 4   |     | bit  |

| Integral linearity error     | EL4               |                                                                             | -1.0  |     | 1.0 | LSB  |

| Differential linearity error | ED4               |                                                                             | -1.0  | _   | 1.0 | LSB  |

| Maximum output current       | I <sub>4max</sub> | DAC2 = "FFh", DAC4 [Fh]                                                     | 133   | 150 | 170 | mA   |

| Offset current               | I <sub>4OF</sub>  | DAC2 = "00h", DAC4 [Fh]                                                     | - 0.1 |     | 0.1 | mA   |

| Settling time                | t <sub>SDA4</sub> | XWR ↑ to DAC4 [0h to Fh],<br>±0.5 LSB, DAC2 [FFh]                           |       | 300 | 600 | ns   |

| DAC9 block                   |                   |                                                                             |       |     |     |      |

| Resolution                   | RES9              |                                                                             |       | 5   |     | bit  |

| Integral linearity error     | EL9               |                                                                             | -1.0  | _   | 1.0 | LSB  |

| Differential linearity error | ED9               |                                                                             | -1.0  |     | 1.0 | LSB  |

| Maximum output current       | I <sub>9max</sub> | DAC9 = "1Fh", DAC7 [Fh],<br>DAC1 [00h], DAC8 [0h]                           | 133   | 150 | 170 | mA   |

| Parameter                    | Symbol            | Conditions                                                                                                            | Min    | Тур | Max  | Unit  |

|------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------|--------|-----|------|-------|

| DAC9 block (continued)       |                   |                                                                                                                       |        |     |      |       |

| Offset current               | I <sub>9OF1</sub> | "00h" LPF-on, DAC7 [Fh],<br>DAC8 [0h], DAC1 [00h],<br>DAC7, DAC8 characteristics included                             | -2.0   |     | 2.0  | mA    |

|                              | I <sub>9OF2</sub> | "00h" LPF-off, DAC7 [Fh],<br>DAC8 [0h], DAC9 [00h],<br>DAC7, DAC8 characteristics included                            | - 0.85 |     | 0.85 |       |

| LPF on/off gain ratio        | GR <sub>DA9</sub> | $G_{LPFON} / G_{LPFOFF}$ , input amplitude 0 V to 2 V                                                                 | 0.95   | 1   | 1.05 | times |

| Settling time                | t <sub>SDA9</sub> | XWR ↑ to DAC9 [00h to 1Fh]<br>±2 LSB range,<br>DAC7[Fh], DAC8 [0h],<br>LPF9-off,<br>LPF91 pin open,<br>RDCP1 pin open |        | 400 | 800  | ns    |

| Supply voltage monitoring b  | lock              |                                                                                                                       |        |     |      |       |

| Abnormality release supply   | V <sub>PSDL</sub> | Sweep $V_{CC}$ from low to high                                                                                       | 3.9    | 4.2 | 4.5  | V     |

| voltage                      | V <sub>PSOL</sub> | Sweep $V_{CC}$ from high to low                                                                                       | 5.5    | 5.8 | 6.1  |       |

| Abnormality supply voltage   | V <sub>PSDH</sub> | Sweep $V_{CC}$ from high to low                                                                                       | 3.6    | 3.9 | 4.2  | V     |

|                              | V <sub>PSOH</sub> | Sweep $V_{CC}$ from low to high                                                                                       | 5.8    | 6.1 | 6.4  |       |

| Abnormally emitted light det | ection DA         | C5                                                                                                                    |        |     |      |       |

| Resolution                   | RES5              |                                                                                                                       |        | 4   |      | bit   |

| Integral linearity error     | EL5               |                                                                                                                       | - 0.5  |     | 0.5  | LSB   |

| Differential linearity error | ED5               |                                                                                                                       | - 0.5  |     | 0.5  | LSB   |

| Offset voltage               | V <sub>50F1</sub> | DAC5 = set to "Fh" and difference to<br>ERREF pin                                                                     | -20    | —   | 20   | mV    |

|                              | V <sub>50F2</sub> | DAC5 = set to "0h" and difference to<br>VNR pin, at ERREF – VNR = 2.0 V                                               | 105    | 125 | 145  |       |

| Settling time                | t <sub>SDA5</sub> | XWR ↑ to DAC5 [0h to Fh],<br>±0.5 LSB                                                                                 | —      | 0.5 | 1.5  | μs    |

| Abnormally emitted light det | ection DA         | C6                                                                                                                    |        |     |      |       |

| Resolution                   | RES6              |                                                                                                                       | _      | 4   | _    | bit   |

| Integral linearity error     | EL6               |                                                                                                                       | - 0.5  |     | 0.5  | LSB   |

| Differential linearity error | ED6               |                                                                                                                       | - 0.5  | _   | 0.5  | LSB   |

| Offset voltage               | V <sub>6OF1</sub> | DAC6 = set to "Fh" and difference to<br>ERREF pin                                                                     | -20    | _   | 20   | mV    |

|                              | V <sub>6OF2</sub> | DAC6 = set to "0h" and difference to<br>VNR pin, at ERREF – VNR = 2.0 V                                               | 105    | 125 | 145  |       |

| Settling time                | t <sub>SDA6</sub> | XWR ↑ to DAC6 [0h to Fh]<br>±0.5 LSB                                                                                  | —      | 0.5 | 1.5  | μs    |

| Parameter                                     | Symbol                     | Conditions                                                                                                                | Min | Тур  | Max  | Unit  |

|-----------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| Abnormally emitted light deter                | ction opti                 | cal monitor block                                                                                                         |     |      |      |       |

| Offset voltage                                | V <sub>EROFR</sub>         | In playback, DETMONI pin, $I_{PD} = 0 \ \mu A$                                                                            | -40 |      | 60   | mV    |

|                                               | V <sub>EROFW</sub>         | In recording, DETMONI pin,<br>$I_{PD} = 0 \ \mu A$                                                                        | -50 |      | 50   |       |

| Gain                                          | G <sub>ERR1</sub>          | In playback, addr. "9": D4 = "0",<br>$I_{PD} = 100 \ \mu A \text{ to } 200 \ \mu A$                                       | 9.0 | 10.0 | 11.0 | times |

|                                               | G <sub>ERR2</sub>          | In playback, addr. "9": D4 = "1",<br>I <sub>PD</sub> = 100 $\mu$ A to 200 $\mu$ A                                         | 4.5 | 5.0  | 5.5  |       |

|                                               | G <sub>ERW</sub>           | In recording, DETMONI pin,<br>$I_{PD} = 100 \ \mu A \text{ to } 2 \ 000 \ \mu A$                                          | 0.9 | 1.0  | 1.1  |       |

| Gain ratio                                    | $\frac{G_{ERR1}}{G_{ERW}}$ |                                                                                                                           | 9.0 | 10.0 | 11.0 | times |

|                                               | $\frac{G_{ERR2}}{G_{ERW}}$ |                                                                                                                           | 4.5 | 5.0  | 5.5  |       |

| f characteristics at playback                 | f <sub>ERR</sub>           | $\label{eq:VR1} \begin{split} &VR1 = 1 \ k\Omega, \ -3 \ dB, \\ &I_{PD} = 100 \ \mu A \ to \ 200 \ \mu A \end{split}$     | 2.5 |      |      | MHz   |

| f characteristics at recording                | $f_{\text{ERW}}$           | $\label{eq:VR1} \begin{split} &VR1 = 1 \ k\Omega, \ -3 \ dB, \\ &I_{PD} = 100 \ \mu A \ to \ 2 \ 000 \ \mu A \end{split}$ | 5.0 |      |      | MHz   |

| Control operation response                    |                            |                                                                                                                           |     |      |      |       |

| Data write to XLDERR $\downarrow$             | t <sub>203</sub>           | XWR $\uparrow$ to XLDERR $\downarrow$                                                                                     |     | 20   | 60   | ns    |

| Data write to XLDERR ↑                        | t <sub>204</sub>           | XWR $\uparrow$ to XLDERR $\uparrow$                                                                                       | _   | 25   | 60   | ns    |

| Data write to sleep mode                      | t <sub>205</sub>           | XWR ↑ to sleep mode                                                                                                       |     | 4    | 9    | μs    |

| Data write to normal mode                     | t <sub>206</sub>           | XWR ↑ to normal mode                                                                                                      |     | 3    | 8    | μs    |

| RPHOLD $\uparrow$ to DAC5 R $\rightarrow$ W   | t <sub>39</sub>            | RPHOLD ↑ to DAC5 W,<br>at having reached ±0.5 LSB                                                                         | _   | 0.40 | 2.5  | μs    |

| RPHOLD $\downarrow$ to DAC5 W $\rightarrow$ R | t <sub>40</sub>            | RPHOLD $\downarrow$ to DAC5 R,<br>at having reached ±0.5 LSB                                                              |     | 0.40 | 2.5  | μs    |

| RPHOLD $\uparrow$ to DAC6 R $\rightarrow$ W   | t <sub>41</sub>            | RPHOLD ↑ to DAC6 W,<br>at having reached ±0.5 LSB                                                                         | _   | 0.40 | 2.5  | μs    |

| RPHOLD $\downarrow$ to DAC6 W $\rightarrow$ R | t <sub>42</sub>            | RPHOLD $\downarrow$ to DAC6 R,<br>at having reached ±0.5 LSB                                                              | _   | 0.40 | 2.5  | μs    |

| <b>RPHOLD</b> $\uparrow$ to HF module signal  | t <sub>43</sub>            | RPHOLD ↑ to XHFON ↑                                                                                                       | _   | 18   | 30   | ns    |

| RPHOLD $\downarrow$ to HF module signal       | t <sub>44</sub>            | RPHOLD $\downarrow$ to XHFON $\downarrow$                                                                                 |     | 17   | 30   | ns    |

# Electrical Characteristics at $V_{CC} = 5.0 \text{ V}$ , $T_a = 25^{\circ}C$ (continued)

| Parameter                          | Symbol           | Conditions                                       | Min                 | Тур                 | Max                 | Unit |

|------------------------------------|------------------|--------------------------------------------------|---------------------|---------------------|---------------------|------|

| Recording Modulation               |                  |                                                  |                     |                     |                     |      |

| Peak modulation signal response *1 | t <sub>113</sub> | PKMD $\uparrow$ to LDPK $\uparrow$ 50% delay     |                     | 18                  | 30                  | ns   |

|                                    | t <sub>114</sub> | PKMD $\downarrow$ to LDPK $\downarrow$ 50% delay |                     | 17                  | 30                  |      |

|                                    | t <sub>115</sub> | LDPK $\uparrow$ 50% to LDPK $\downarrow$ 50%     | t <sub>112</sub> -3 | t <sub>112</sub> -1 | t <sub>112</sub> +1 |      |

|                                    | t <sub>116</sub> | LDPK ↑ 10% to LDPK ↑ 90%                         | _                   | 6                   | 9                   |      |

|                                    | t <sub>117</sub> | LDPK $\downarrow$ 90% to LDPK $\downarrow$ 10%   | _                   | 4                   | 6                   |      |

| Bias modulation signal response *1 | t <sub>123</sub> | BIMD ↑ to LDBI ↑ 50% delay                       | _                   | 18                  | 30                  | ns   |

|                                    | t <sub>124</sub> | BIMD $\downarrow$ to LDBI $\downarrow$ 50% delay | _                   | 17                  | 30                  |      |

|                                    | t <sub>125</sub> | LDBI $\uparrow$ 50% to LDBI $\downarrow$ 50%     | t <sub>122</sub> -3 | $t_{122} - 1$       | t <sub>122</sub> +1 |      |

|                                    | t <sub>126</sub> | LDBI $\uparrow$ 10% to LDBI $\uparrow$ 90%       | _                   | 6                   | 9                   |      |

|                                    | t <sub>127</sub> | LDBI $\downarrow$ 90% to LDBI $\downarrow$ 10%   | _                   | 5                   | 8                   |      |

Note) \*1: Resistive load (at 15  $\Omega$ )

Conditions of  $t_{113}$  to  $t_{117}$ Measure at approximately 1.75 V of LDPK pin voltage. DAC1 [FFh], DAC8 [7h] DAC9 [1Fh], DAC7 [7h], DAC4 [Fh] DAC2 [00h to 80f] Conditions of  $t_{123}$  to  $t_{127}$ Measure at approximately 1.75 V of LDPK pin voltage. DAC1 [FFh], DAC8 [7h] DAC9 [1Fh], DAC7 [7h], DAC4 [Fh] DAC3 [00h to 80f]

#### • Design reference data

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                                                          | Symbol                              | Conditions                                                                                                            | Min | Тур | Max | Unit                      |  |  |

|--------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------------------|--|--|

| Reference voltage block                                            |                                     |                                                                                                                       |     |     |     |                           |  |  |

| Reference voltage temperature characteristics *2                   | $\Delta V_{\text{TEM}}$             | $V_{REF} = 0 V, T_a = -20^{\circ}C \text{ to } +75^{\circ}C$                                                          |     |     | ±30 | mV                        |  |  |

| Digital block                                                      |                                     |                                                                                                                       |     |     |     |                           |  |  |

| Low $\rightarrow$ high input hysteresis<br>(Schmidt trigger input) | V <sub>LHHYS</sub>                  | To be applied to PWMSK, ERFIL pin                                                                                     |     | 1.0 |     | V                         |  |  |

| High $\rightarrow$ low input hysteresis<br>(Schmidt trigger input) | V <sub>HLHYS</sub>                  | To be applied to PWMSK, ERFIL pin                                                                                     |     | 1.0 |     | V                         |  |  |

| Entire optical monitor                                             |                                     |                                                                                                                       |     |     |     |                           |  |  |

| Offset voltage temperature variation                               | $\frac{\Delta V_{PMOFR}}{\Delta T}$ | In playback, VR1 = 1 k $\Omega$<br>I <sub>PD</sub> = 10 $\mu$ A to 200 $\mu$ A<br>T <sub>a</sub> = -20°C to +75°C     |     | 55  | 200 | $\frac{\mu V}{^{\circ}C}$ |  |  |

|                                                                    | $\frac{\Delta V_{PMOFW}}{\Delta T}$ | In recording, VR1 = 1 k $\Omega$<br>I <sub>PD</sub> = 100 $\mu$ A to 2 000 $\mu$ A<br>T <sub>a</sub> = -20°C to +75°C |     | 30  | 150 |                           |  |  |

Note) \*2: Difference between  $V_{REF}$  min. and  $V_{REF}$  max. within the range of  $T_a = -20^{\circ}$ C to  $+75^{\circ}$ C.

• Design reference data (continued)

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                               | Symbol                      | Conditions                                                                                                                                      | Min | Тур  | Max | Unit                      |

|-----------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|---------------------------|

| Entire optical monitor (contin          | ued)                        |                                                                                                                                                 |     |      |     |                           |

| Gain ratio variation to temperature     | $d\frac{G_{PMR}}{G_{PMW}}$  | $T_a = -20^{\circ}C \text{ to } +75^{\circ}C$                                                                                                   | -3  |      | 3   | %                         |

| Slew rate                               | S1 <sub>PMR</sub>           | In playback, AAF-off rise                                                                                                                       | 13  | 18   | _   | V/µs                      |

|                                         | S1 <sub>PMW</sub>           | In recording, rise                                                                                                                              | 35  | 45   | —   |                           |

| Signal changeover response              | t <sub>PMSW1</sub>          | $\times 10 \rightarrow \times 1$ , at having reached ±0.5%                                                                                      | _   | 100  | 300 | ns                        |