# P4C168, P4C169, P4C170 ULTRA HIGH SPEED 4K x 4 STATIC CMOS RAMS

## **FEATURES**

- **■** Full CMOS, 6T Cell

- High Speed (Equal Access and Cycle Times)

- 12/15/20/25ns (Commercial)

- 20/25/35ns (P4C168 Military)

- Low Power Operation (Commercial)

- 715 mW Active

- 193 mW Standby (TTL Input) P4C168

- 83 mW Standby (CMOS Input) P4C168

- Single 5V±10% Power Supply

- Fully TTL Compatible, Common I/O Ports

- Three Options

- P4C168 Low Power Standby Mode

- P4C169 Fast Chip Select Control

- P4C170 Fast Chip Select, Output Enable Controls

- Standard Pinout (JEDEC Approved)

- P4C168: 20-pin DIP, SOJ and SOIC

- P4C169: 20-pin DIP and SOIC

- P4C170: 22-pin DIP

### **DESCRIPTION**

The P4C168, P4C169 and P4C170 are a family of 16,384-bit ultra high-speed static RAMs organized as 4K x 4. All three devices have common input/output ports. The P4C168 enters the standby mode when the chip enable  $(\overline{CE})$  control goes high; with CMOS input levels, power consumption is only 83mW in this mode. Both the P4C169 and the P4C170 offer a fast chip select access time that is only 67% of the address access time. In addition, the P4C170 includes an output enable  $(\overline{OE})$  control to eliminate data bus contention. The RAMs operate from a single  $5V \pm 10\%$  tolerance power supply.

Access times as fast as 12 nanoseconds are available, permitting greatly enhanced system operating speeds. CMOS is used to reduce power consumption to a low 715 mW active, 193 mW standby.

The P4C168 and P4C169 are available in 20-pin (P4C170 in 22-pin) 300 mil DIP packages providing excellent board level densities. The P4C168 is also available in 20-pin 300 mil SOIC and SOJ packages.

The P4C169 is also available in a 20-pin 300 mil SOIC package. The P4C170 is also available in a 22-pin 300 mil SOJ package.

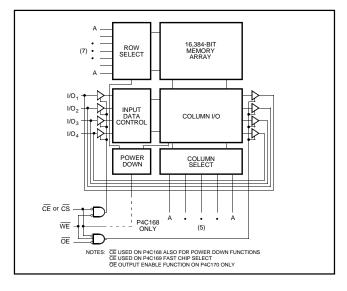

### **FUNCTIONAL BLOCK DIAGRAM**

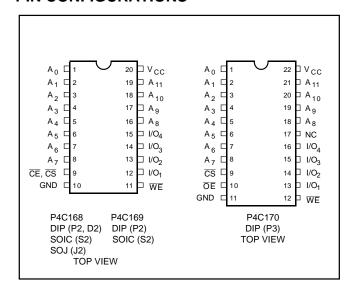

### **PIN CONFIGURATIONS**

Means Quality, Service and Speed

# MAXIMUM RATINGS(1)

| Symbol            | Parameter                                               | Value                           | Unit |

|-------------------|---------------------------------------------------------|---------------------------------|------|

| V <sub>cc</sub>   | Power Supply Pin with Respect to GND                    | -0.5 to +7                      | V    |

| V <sub>TERM</sub> | Terminal Voltage with<br>Respect to GND<br>(up to 7.0V) | -0.5 to<br>V <sub>cc</sub> +0.5 | V    |

| T <sub>A</sub>    | Operating Temperature                                   | -55 to +125                     | °C   |

| Symbol            | Parameter                 | Value       | Unit |

|-------------------|---------------------------|-------------|------|

| T <sub>BIAS</sub> | Temperature Under<br>Bias | -55 to +125 | °C   |

| T <sub>STG</sub>  | Storage Temperature       | -65 to +150 | °C   |

| P <sub>T</sub>    | Power Dissipation         | 1.0         | W    |

| I <sub>OUT</sub>  | DC Output Current         | 50          | mA   |

# **RECOMMENDED OPERATING CONDITIONS**

| Grade <sup>(2)</sup> | Ambient Temp    | Gnd | V <sub>cc</sub> |

|----------------------|-----------------|-----|-----------------|

| Commercial           | 0°C to 70°C     | 0V  | 5.0V ± 10%      |

| Military             | –55°C to +125°C | 0V  | 5.0V ± 10%      |

# CAPACITANCES<sup>(4)</sup>

$(V_{CC} = 5.0V, T_A = 25^{\circ}C, f = 1.0MHz)$

| Symbol           | Parameter          | Conditions            | Тур. | Unit |

|------------------|--------------------|-----------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{IN} = 0V$         | 5    | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V | 7    | рF   |

# DC ELECTRICAL CHARACTERISTICS

|                  | _                                                                     | P4C168                                                                                                                                                                                                                                                                                                      |                      |                      |      |  |

|------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|--|

| Symbol           | Parameter                                                             | Test Conditions                                                                                                                                                                                                                                                                                             | Min                  | Max                  | Unit |  |

| V <sub>IH</sub>  | Input High Voltage                                                    |                                                                                                                                                                                                                                                                                                             | 2.2                  | V <sub>cc</sub> +0.5 | V    |  |

| V <sub>IL</sub>  | Input Low Voltage                                                     |                                                                                                                                                                                                                                                                                                             | -0.5(3)              | 0.8                  | V    |  |

| V <sub>HC</sub>  | CMOS Input High Voltage                                               |                                                                                                                                                                                                                                                                                                             | V <sub>CC</sub> -0.2 | V <sub>cc</sub> +0.5 | V    |  |

| V <sub>LC</sub>  | CMOS Input Low Voltage                                                |                                                                                                                                                                                                                                                                                                             | -0.5(3)              | 0.2                  | V    |  |

| V <sub>CD</sub>  | Input Clamp Diode Voltage                                             | $V_{CC} = Min., I_{IN} = -18 \text{ mA}$                                                                                                                                                                                                                                                                    |                      | -1.2                 | V    |  |

| V <sub>OL</sub>  | Output Low Voltage<br>(TTL Load)                                      | $I_{OL} = +8 \text{ mA}, V_{CC} = \text{Min}.$                                                                                                                                                                                                                                                              |                      | 0.4                  | V    |  |

| V <sub>OLC</sub> | Output Low Voltage<br>(CMOS Load)                                     | $I_{OLC} = +100 \mu A, V_{CC} = Min.$                                                                                                                                                                                                                                                                       |                      | 0.2                  | V    |  |

| V <sub>OH</sub>  | Output High Voltage<br>(TTL Load)                                     | $I_{OH} = -4 \text{ mA}, V_{CC} = \text{Min}.$                                                                                                                                                                                                                                                              | 2.4                  |                      | V    |  |

| V <sub>OHC</sub> | Output High Voltage<br>(CMOS Load)                                    | $I_{OHC} = -100 \mu A$ , $V_{CC} = Min$ .                                                                                                                                                                                                                                                                   | V <sub>cc</sub> -0.2 |                      | V    |  |

| I <sub>LI</sub>  | Input Leakage Current                                                 | $V_{CC} = Max., V_{IN} = GND \text{ to } V_{CC}$ Mil. Comm'l                                                                                                                                                                                                                                                | –10<br>–5            | +10<br>+5            | μА   |  |

| I <sub>LO</sub>  | Output Leakage Current                                                | $V_{CC} = Max., \overline{CS} = V_{IH},$ Mil. $V_{OUT} = GND \text{ to } V_{CC}$ Comm'l                                                                                                                                                                                                                     | -10<br>-5            | +10<br>+5            | μА   |  |

| I <sub>cc</sub>  | Dynamic Operating Current                                             | V <sub>cc</sub> = Max., f = Max., Outputs Open                                                                                                                                                                                                                                                              |                      | 130                  | mA   |  |

| I <sub>SB</sub>  | Standby Power Supply<br>Current (TTL Input Levels)<br>P4C168 only     | CE ≥ V <sub>IH</sub> , V <sub>CC</sub> = Max., f = Max.,<br>Outputs Open                                                                                                                                                                                                                                    |                      | 35                   | mA   |  |

| I <sub>SB1</sub> | Standby Power<br>Supply Current<br>(CMOS Input Levels)<br>P4C168 only | $\label{eq:continuous_continuous_continuous} \begin{split} \overline{\text{CE}} &\geq \text{V}_{\text{HC}},  \text{V}_{\text{CC}} = \text{Max., f} = 0, \\ \text{Outputs Open} \\ \text{V}_{\text{IN}} &\leq \text{V}_{\text{LC}}   \text{or}   \text{V}_{\text{IN}} \geq \text{V}_{\text{HC}} \end{split}$ |                      | 15                   | mA   |  |

# **AC CHARACTERISTICS—READ CYCLE**

$(V_{CC}$  = 5V  $\pm$  10%, All Temperature Ranges)<sup>(2)</sup>

| Sym.                         | Parameter                          |     | 12  |     | 15  | -20 |     | -25 |     | -35 |     | Unit  |

|------------------------------|------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| Sylli.                       | i didilietei                       | Min | Max | Oiiit |

| t <sub>RC</sub>              | Read Cycle Time                    | 12  |     | 15  |     | 20  |     | 25  |     | 35  |     | ns    |

| t <sub>AA</sub>              | Address Access Time                |     | 12  |     | 15  |     | 20  |     | 25  |     | 35  | ns    |

| t <sub>AC</sub> §            | Chip Enable Access Time            |     | 12  |     | 15  |     | 20  |     | 25  |     | 35  | ns    |

| t <sub>AC</sub> <sup>‡</sup> | Chip Select Access Time            |     | 8   |     | 9   |     | 12  |     | 15  |     | 20  | ns    |

| t <sub>oh</sub>              | Output Hold from Address Change    | 2   |     | 2   |     | 2   |     | 2   |     | 2   |     | ns    |

| $t_{LZ}^{^{\ddagger}}$       | Chip Enable to Output in Low Z     | 2   |     | 2   |     | 2   |     | 2   |     | 2   |     | ns    |

| t <sub>HZ</sub> †            | Chip Disable to Output in High Z   |     | 6   |     | 7   |     | 9   |     | 10  |     | 15  | ns    |

| t <sub>oe</sub> †            | Output Enable to Data Valid        |     | 8   |     | 10  |     | 12  |     | 15  |     | 15  | ns    |

| $t_{OLZ}^{\dagger}$          | Output Enable to Output in Low Z   | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns    |

| t <sub>OHZ</sub> †           | Output Disable to Output in High Z |     | 6   |     | 7   |     | 9   |     | 11  |     | 15  | ns    |

| t <sub>RCS</sub>             | Read Command Setup Time            | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns    |

| t <sub>RCH</sub>             | Read Command Hold Time             | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns    |

| t <sub>PU</sub> §            | Chip Enable to Power Up Time       | 0   |     | 0   |     | 0   |     | 0   |     | 0   |     | ns    |

| t <sub>PD</sub> §            | Chip Disable to Power Down Time    |     | 12  |     | 15  |     | 20  |     | 25  |     | 35  | ns    |

<sup>§</sup> P4C168 only

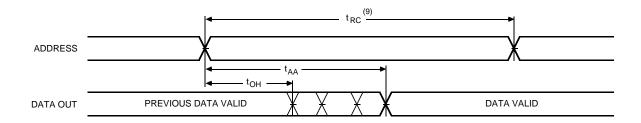

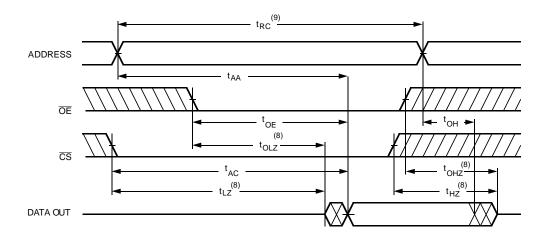

# TIMING WAVEFORM OF READ CYCLE NO. 1 (ADDRESS CONTROLLED)(5,6)

<sup>†</sup> P4C170 only

<sup>‡</sup> Chip Select/Deselect for P4C169 and P4C170

Notes:

5. WE is HIGH for READ cycle.

6. CE/CS and OE are LOW for READ cycle.

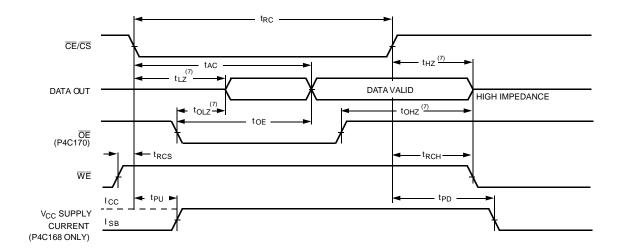

# TIMING WAVEFORM OF READ CYCLE NO. 2 (CE/CS CONTROLLED)(5,7)

# TIMING WAVEFORM OF READ CYCLE NO. 3—P4C170 ONLY (OE CONTROLLED)(5)

#### Notes:

- 7. ADDRESS must be valid prior to, or coincident with  $\overline{\text{CE}/\text{CS}}$  transition low. For Fast  $\overline{\text{CS}}$ ,  $t_{\text{AA}}$  must still be met.

- 8. Transition is measured ±200mV from steady state voltage prior to change, with loading as specified in Figure 1.

- 9. Read Cycle Time is measured from th 1521 05 valid address to the first transitioning address.

## **AC ELECTRICAL CHARACTERISTICS - WRITE CYCLE**

$(V_{CC}$  = 5V  $\pm$  10%, All Temperature Ranges)<sup>(2)</sup>

| Cum             | Doromotor                          | <u> </u> | 12  | -1  | 15  | -:  | 20  | -2  | 25  | -:  | 35  | Unit |

|-----------------|------------------------------------|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|

| Sym.            | Parameter                          | Min      | Max | Min | Max | Min | Max | Min | Max | Min | Max | Onit |

| t <sub>wc</sub> | Write Cycle Time                   | 12       |     | 15  |     | 18  |     | 20  |     | 35  |     | ns   |

| t <sub>cw</sub> | Chip Enable Time to End of Write   | 12       |     | 15  |     | 18  |     | 20  |     | 30  |     | ns   |

| t <sub>AW</sub> | Address Valid to<br>End of Write   | 12       |     | 15  |     | 18  |     | 20  |     | 30  |     | ns   |

| t <sub>AS</sub> | Address Set-up Time                | 0        |     | 0   |     | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>wP</sub> | Write Pulse Width                  | 12       |     | 15  |     | 18  |     | 20  |     | 30  |     | ns   |

| t <sub>AH</sub> | Address Hold Time                  | 0        |     | 0   |     | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>DW</sub> | Data Valid to End of Write         | 7        |     | 8   |     | 10  |     | 10  |     | 15  |     | ns   |

| t <sub>DH</sub> | Data Hold Time                     | 0        |     | 0   |     | 0   |     | 0   |     | 0   |     | ns   |

| t <sub>wz</sub> | Write Enable to Output in High Z   |          | 4   |     | 5   |     | 7   |     | 7   |     | 13  | ns   |

| t <sub>ow</sub> | Output Active from<br>End of Write | 0        |     | 0   |     | 0   |     | 0   |     | 0   |     | ns   |

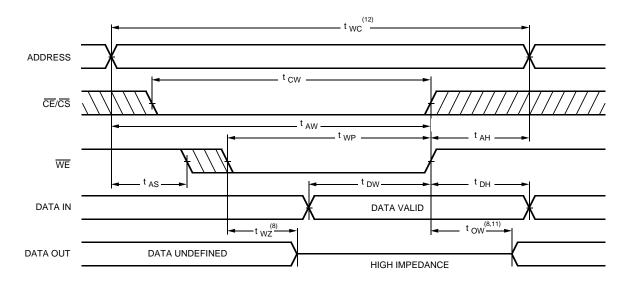

# TIMING WAVEFORM OF WRITE CYCLE NO. 1 (WE CONTROLLED)(10)

#### Notes:

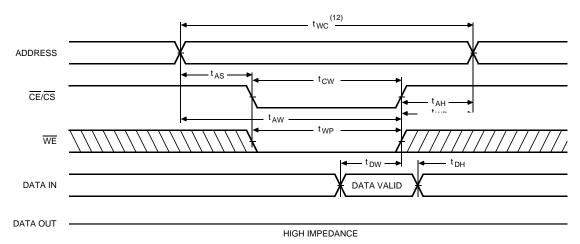

- 10.  $\overline{\text{CE}/\text{CS}}$  and  $\overline{\text{WE}}$  must be LOW for WRITE cycle.

- 11. If CE/CS goes HIGH simultaneously with WE HIGH, the output remains in a high impedance state.

- 12. Write Cycle Time is measured from the last valid address to the first transitioning address.

# TIMING WAVEFORM OF WRITE CYCLE NO. 2 (CE/CS CONTROLLED)(10)

#### **TRUTH TABLES**

P4C168 (P4C169)

| Mode               | CE (CS) | WE | Output           |

|--------------------|---------|----|------------------|

| Standby (Deselect) | Н       | Х  | High Z           |

| Read               | L       | Н  | D <sub>out</sub> |

| Write              | L       | L  | High Z           |

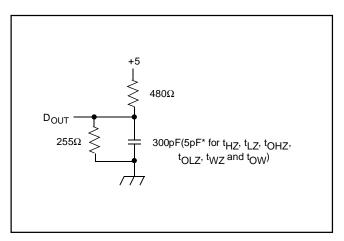

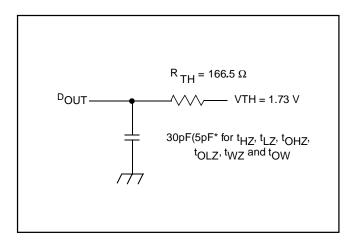

#### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V         |

|-------------------------------|---------------------|

| Input Rise and Fall Times     | 3ns                 |

| Input Timing Reference Level  | 1.5V                |

| Output Timing Reference Level | 1.5V                |

| Output Load                   | See Figures 1 and 2 |

#### P4C170

| Mode           | CE | WE | ŌĒ | Output           |

|----------------|----|----|----|------------------|

| Deselect       | Н  | Х  | Х  | High Z           |

| Read           | L  | Н  | L  | D <sub>OUT</sub> |

| Output Inhibit | L  | Н  | Н  | High Z           |

| Write          | L  | L  | Х  | High Z           |

Figure 1. Output Load

#### Note:

Because of the ultra-high speed of the P4C168, P4C169 AND P4C170 care must be taken when testing these devices; an inadequate setup can cause a normal functioning part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the  $V_{\rm CC}$  and ground planes directly up to the contactor fingers. A 0.01  $\mu F$

Figure 2. Thevenin Equivalent

high frequency capacitor is also required between V $_{\rm CC}$  and ground. To avoid signal reflections, proper termination must be used; for example, a  $50\Omega$  test environment should be terminated into a  $50\Omega$  load with 1.73V (Thevenin Voltage) at the comparator input, and a  $116\Omega$  resistor must be used in series with D $_{\rm OUT}$  to match  $166\Omega$  (Thevenin Resistance).

<sup>\*</sup> including scope and test fixture.

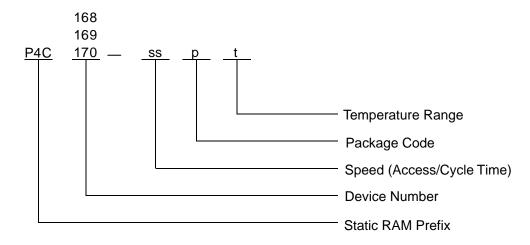

### **PACKAGE SUFFIX**

| Package<br>Suffix | Description                         |

|-------------------|-------------------------------------|

| Р                 | Plastic DIP, 300 mil wide standard  |

| S                 | Plastic SOIC, 300 mil wide standard |

| J                 | Plastic SOJ, 300 mil wide standard  |

| D                 | CERDIP, 300 mil wide standard       |

### **TEMPERATURE RANGE SUFFIX**

| Temperature<br>Range Suffix | Description                                     |

|-----------------------------|-------------------------------------------------|

| С                           | Commercial Temperature Range,<br>0°C – +70°C.   |

| М                           | Military Temperature Range,                     |

| МВ                          | Mil. Temp. with MIL-STD-883D Class B compliance |

## **ORDERING INFORMATION**

ss = Speed (access/cycle time in ns), e.g., 15, 20

p = Package code, i.e., P, S,D, J.

t = Temperature range, i.e., C, M, MB.

The P4C168 is also available per SMD #5962-86705

#### **SELECTION GUIDE**

The P4C168, P4C169 and P4C170 are available in the following temperature, speed and package options.

| Temperature<br>Range                    | Speed (ns) Package                      | 12                      | 15                      | 20                      | 25                      | 35                |

|-----------------------------------------|-----------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------|

| Commercial                              | Plastic DIP Plastic SOIC† Plastic SOJ†† | -12PC<br>-12SC<br>-12JC | -15PC<br>-15SC<br>-15JC | -20PC<br>-20SC<br>-20JC | -25PC<br>-25SC<br>-25JC | N/A<br>N/A<br>N/A |

| Military Temp.<br>(P4C168 only)         | CERDIP                                  | N/A                     | N/A                     | -20DM                   | -25DM                   | -35DM             |

| Military<br>Processed*<br>(P4C168 only) | CERDIP                                  | N/A                     | N/A                     | -20DMB                  | -25DMB                  | -35DMB            |

<sup>†</sup> P4C168 and P4C169 only.

N/A = Not available

<sup>††</sup> P4C168

<sup>\*</sup> Military temperature range with MIL-STD-883, Class B processing.