### **INTEGRATED CIRCUITS**

### DATA SHEET

### SAA55xx Enhanced TV microcontrollers with On-Screen Display (OSD)

Preliminary specification Supersedes data of 1999 Aug 02 File under Integrated Circuits, IC02 2000 Feb 23

## **Enhanced TV microcontrollers with On-Screen Display (OSD)**

SAA55xx

| CONTE        | NTS                                                  | 17               | MEMORY INTERFACE                                                   |

|--------------|------------------------------------------------------|------------------|--------------------------------------------------------------------|

| 1            | FEATURES                                             | 17.1<br>17.2     | Memory structure Memory mapping                                    |

| 2            | GENERAL DESCRIPTION                                  | 17.2             | Addressing memory                                                  |

| 3            | QUICK REFERENCE DATA                                 | 17.4             | Page clearing                                                      |

| 4            | ORDERING INFORMATION                                 | 18               | DATA CAPTURE                                                       |

| 5            | BLOCK DIAGRAM                                        | 18.1             | Data Capture features                                              |

| 6            | PINNING INFORMATION                                  | 19               | DISPLAY                                                            |

| 6.1          | Pinning                                              | 19.1             | Display features                                                   |

| 6.2          | Pin description                                      | 19.2             | Display modes                                                      |

| 7            | MICROCONTROLLER                                      | 19.3             | Display feature descriptions                                       |

| 7.1          | Microcontroller features                             | 19.4<br>19.5     | Character and attribute coding Screen and global controls          |

| 8            | MEMORY ORGANIZATION                                  | 19.6             | Screen colour                                                      |

| 8.1          | ROM bank switching                                   | 19.7             | Text display controls                                              |

| 8.2          | Security bits - program and verify                   | 19.8             | Soft scroll action                                                 |

| 8.3          | RAM organisation                                     | 19.9             | Display positioning                                                |

| 8.4          | Data memory                                          | 19.10            | Character set                                                      |

| 8.5          | SFR memory                                           | 19.11            | ROM addressing                                                     |

| 8.6          | Character set feature bits                           | 19.12            | Redefinable characters                                             |

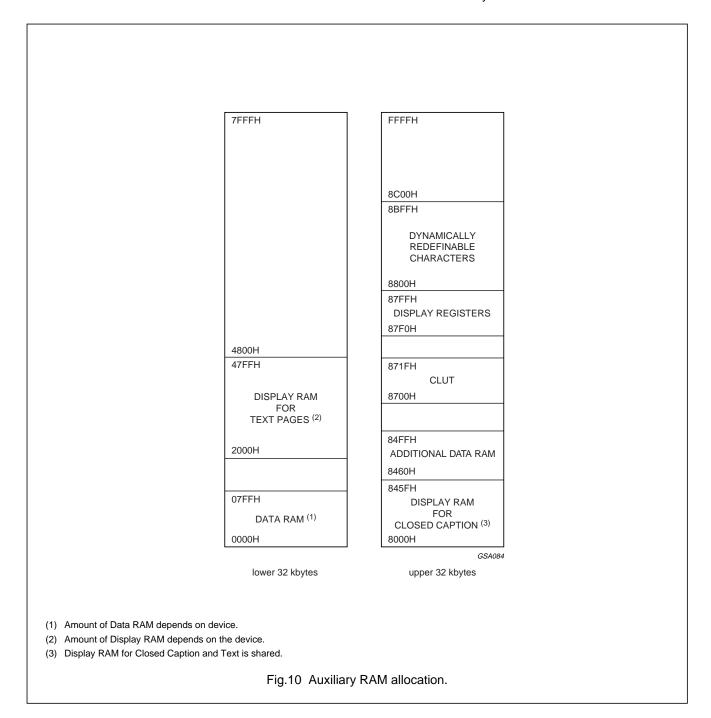

| 8.7          | External (Auxiliary) memory                          | 19.13<br>19.14   | Display synchronization Video/data switch (Fast Blanking) polarity |

| 9            | POWER-ON RESET                                       | 19.15            | Video/Data switch adjustment                                       |

| 10           | REDUCED POWER MODES                                  | 19.16            | RGB brightness control                                             |

| 10.1         | Idle mode                                            | 19.17            | Contrast reduction                                                 |

| 10.2         | Power-down mode                                      | 20               | MEMORY MAPPED REGISTERS (MMR)                                      |

| 10.3         | Standby mode                                         | 21               | LIMITING VALUES                                                    |

| 11           | I/O FACILITY                                         | 22               | CHARACTERISTICS                                                    |

| 11.1         | I/O ports                                            | 23               | QUALITY AND RELIABILITY                                            |

| 11.2         | Port type                                            | 23.1             | Group A                                                            |

| 11.3         | Port alternative functions                           | 23.2             | Group B                                                            |

| 11.4         | LED support                                          | 23.3             | Group C                                                            |

| 12           | INTERRUPT SYSTEM                                     | 24               | APPLICATION INFORMATION                                            |

| 12.1<br>12.2 | Interrupt enable structure Interrupt enable priority | 25               | EMC GUIDELINES                                                     |

| 12.3         | Interrupt vector address                             | 26               | REFERENCES                                                         |

| 12.4         | Level/edge interrupt                                 | 27               | PACKAGE OUTLINE                                                    |

| 13           | TIMER/COUNTER                                        | 28               | SOLDERING                                                          |

| 14           | WATCHDOG TIMER                                       | 28.1             | Introduction to soldering through-hole mount                       |

| 14.1         | Watchdog Timer operation                             |                  | packages                                                           |

| 15           | PULSE WIDTH MODULATORS                               | 28.2             | Soldering by dipping or by solder wave                             |

| 15.1         | PWM control                                          | 28.3<br>28.4     | Manual soldering Suitability of through-hole mount IC packages     |

| 15.2         | Tuning Pulse Width Modulator (TPWM)                  | 20. <del>4</del> | for dipping and wave soldering methods                             |

| 15.3         | Software ADC (SAD)                                   | 29               | DEFINITIONS                                                        |

| 16           | I <sup>2</sup> C-BUS SERIAL I/O                      |                  |                                                                    |

| 16.1         | I <sup>2</sup> C-bus port selection                  | 30               | LIFE SUPPORT APPLICATIONS                                          |

|              |                                                      | 31               | PURCHASE OF PHILIPS I2C COMPONENTS                                 |

### Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

#### 1 FEATURES

- Single-chip microcontroller with integrated OSD

- Versions available with integrated data capture

- OTP memory for both program ROM and character sets

- Single power supply: 3.0 to 3.6 V

- 5 V tolerant digital inputs and I/O

- 29 I/O ports via individual addressable controls

- Programmable I/O for push-pull, open-drain and quasi-bidirectional

- Two port lines with 8 mA sink (at <0.4 V) capability, for direct drive of LED

- Single crystal oscillator for microcontroller, OSD and data capture

- Power reduction modes: Idle, Power-down and Standby

- Byte level I<sup>2</sup>C-bus interface with dual port I/O

- 32 Dynamically Redefinable Characters for OSDs

- Special graphic characters allowing four colours per character

- Selectable character height 9, 10, 13 and 16 TV lines

- · Pin compatibility throughout family

- Operating temperature: -20 to +70 °C.

#### 2 GENERAL DESCRIPTION

The SAA55xx family of microcontrollers are a derivative of the Philips industry-standard 80C51 microcontroller and are intended for use as the central control mechanism in a television receiver. They provide control functions for the television system, On-Screen Display (OSD) and some versions include an integrated data capture and display function.

The data capture hardware has the capability of decoding and displaying both 525 and 625-line World System Teletext (WST), Closed Caption (CC) information, Video Programming Information (VPS) and Wide Screen Signalling (WSS) information. The same display hardware is used both for Teletext, Closed Caption and On-Screen Display, which means that the display features available give greater flexibility to differentiate the TV set.

The SAA55xx family offers a range of functionality from non-text, 16-kbyte program ROM and 256-byte RAM, to a 10 page text version, 128-kbyte program ROM and 2.25-kbyte RAM.

### 3 QUICK REFERENCE DATA

| SYMBOL                | PARAMETER                                                | MIN.     | TYP. | MAX. | UNIT |

|-----------------------|----------------------------------------------------------|----------|------|------|------|

| Supply                |                                                          | <u> </u> | -    |      | •    |

| $V_{DDX}$             | any supply voltage (V <sub>DD</sub> to V <sub>SS</sub> ) | 3.0      | 3.3  | 3.6  | V    |

| I <sub>DDP</sub>      | periphery supply current                                 | 1        | _    | _    | mA   |

| I <sub>DDC</sub>      | core supply current                                      | _        | 15   | 18   | mA   |

| I <sub>DDC(id)</sub>  | Idle mode core supply current                            | _        | 4.6  | 6    | mA   |

| I <sub>DDC(pd)</sub>  | Power-down mode core supply current                      | _        | 0.76 | 1    | mA   |

| I <sub>DDC(stb)</sub> | standby mode core supply current                         | _        | 5.1  | 9    | mA   |

| I <sub>DDA</sub>      | analog supply current                                    | _        | 45   | 48   | mA   |

| I <sub>DDA(id)</sub>  | Idle mode analog supply current                          | _        | 0.87 | 1.0  | mA   |

| I <sub>DDA(stb)</sub> | standby mode analog supply current                       | _        | 809  | 950  | μΑ   |

| I <sub>DDA(pd)</sub>  | Power-down mode analog supply current                    | _        | 0.45 | 0.7  | mA   |

| f <sub>xtal</sub>     | crystal frequency                                        | _        | 12   | _    | MHz  |

| T <sub>amb</sub>      | ambient temperature                                      | -20      | _    | +70  | °C   |

| T <sub>stg</sub>      | storage temperature                                      | -55      | _    | +125 | °C   |

### Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

### 4 ORDERING INFORMATION

| TYPE NUMBER <sup>(1)</sup> |        | PACKAGE <sup>(2)</sup>               | ROM      | RAM       | TEXT      |       |

|----------------------------|--------|--------------------------------------|----------|-----------|-----------|-------|

| I TPE NUMBER               | NAME   | DESCRIPTION                          | VERSION  | KOW       | KAW       | PAGES |

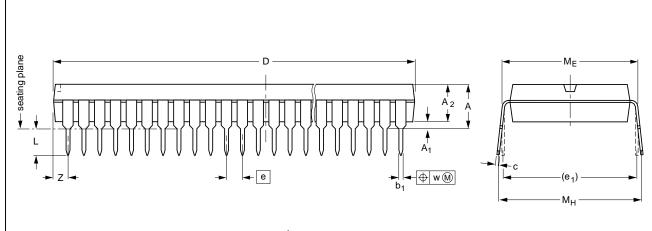

| SAA5530PS/nnnn             | SDIP52 | plastic shrink dual in-line package; | SOT247-1 | 16-kbyte  | 256-byte  | 1     |

| SAA5531PS/nnnn             |        | 52 leads (600 mil)                   |          | 32-kbyte  | 512-byte  | 1     |

| SAA5532PS/nnnn             |        |                                      |          | 48-kbyte  | 750-byte  | 1     |

| SAA5533PS/nnnn             |        |                                      |          | 64-kbyte  | 1-kbyte   | 1     |

| SAA5561PS/nnnn             |        |                                      |          | 32-kbyte  | 750-byte  | 10    |

| SAA5562PS/nnnn             |        |                                      |          | 48-kbyte  | 1-kbyte   | 10    |

| SAA5563PS/nnnn             |        |                                      |          | 64-kbyte  | 1.2-kbyte | 10    |

| SAA5564PS/nnnn             |        |                                      |          | 96-kbyte  | 1.5-kbyte | 10    |

| SAA5565PS/nnnn             |        |                                      |          | 128-kbyte | 2-kbyte   | 10    |

### **Notes**

- 1. 'nnnn' is a four digit number uniquely referencing the microcontroller program mask.

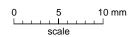

- 2. For details of the LQFP100 package, please contact your local regional sales office for availability.

### Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

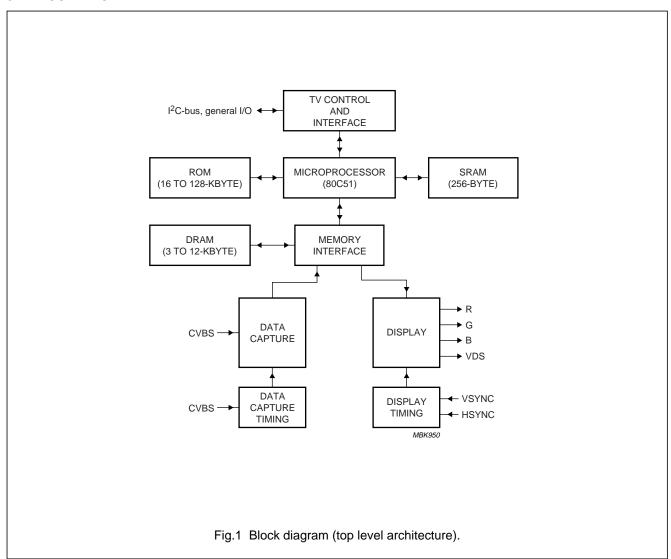

### 5 BLOCK DIAGRAM

### Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

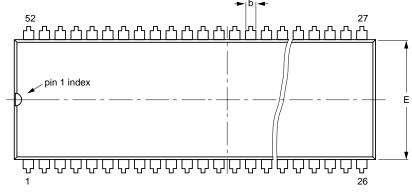

#### 6 PINNING INFORMATION

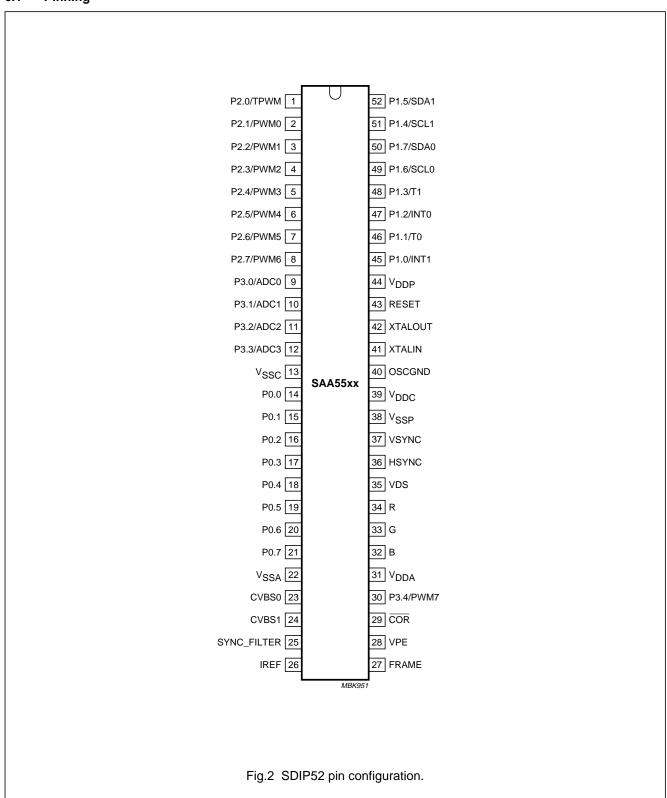

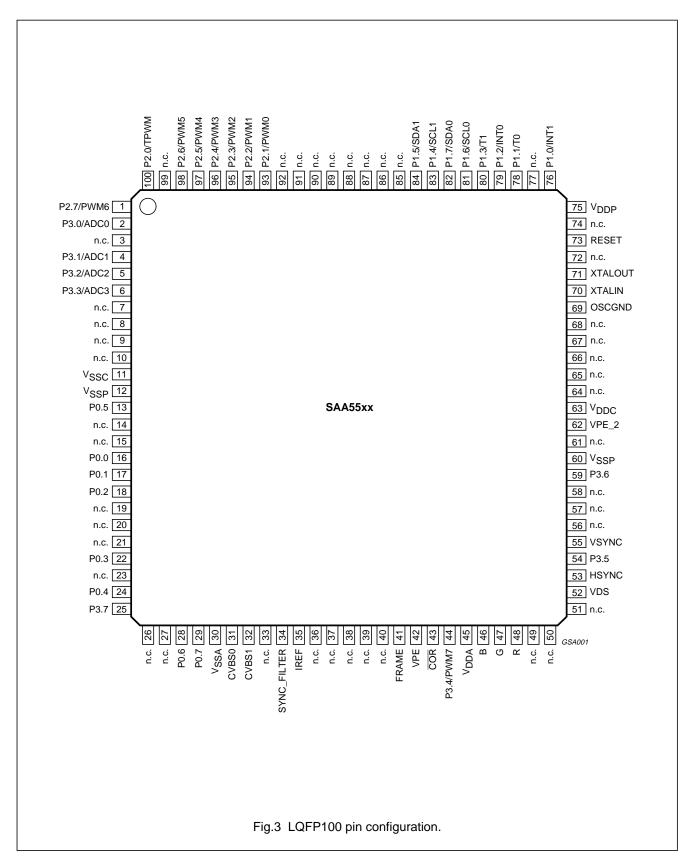

### 6.1 Pinning

### Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

# Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

### 6.2 Pin description

Table 1 SDIP52 and LQFP100 packages

| CVMDOL           |                | PIN | TVDE | DECORIDATION                                                                                                                                 |  |  |  |

|------------------|----------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SYMBOL           | SDIP52 LQFP100 |     | TYPE | DESCRIPTION                                                                                                                                  |  |  |  |

| P2.0/TPWM        | 1              | 100 | I/O  | Port 2. 8-bit programmable bidirectional port with                                                                                           |  |  |  |

| P2.1/PWM0        | 2              | 93  | I/O  | alternative functions.                                                                                                                       |  |  |  |

| P2.2/PWM1        | 3              | 94  | I/O  | P2.0/TPWM is the output for the 14-bit high                                                                                                  |  |  |  |

| P2.3/PWM2        | 4              | 95  | I/O  | precision PWM; P2.1/PWM0 to P2.7/PWM6 are the                                                                                                |  |  |  |

| P2.4/PWM3        | 5              | 96  | I/O  | outputs for the 6-bit PWMs 0 to 6.                                                                                                           |  |  |  |

| P2.5/PWM4        | 6              | 97  | I/O  |                                                                                                                                              |  |  |  |

| P2.6/PWM5        | 7              | 98  | I/O  |                                                                                                                                              |  |  |  |

| P2.7/PWM6        | 8              | 1   | I/O  |                                                                                                                                              |  |  |  |

| P3.0/ADC0        | 9              | 2   | I/O  | Port 3. 8-bit programmable bidirectional port with                                                                                           |  |  |  |

| P3.1/ADC1        | 10             | 4   | I/O  | alternative functions.                                                                                                                       |  |  |  |

| P3.2/ADC2        | 11             | 5   | I/O  | P3.0/ADC0 to P3.3/ADC3 are the inputs for the                                                                                                |  |  |  |

| P3.3/ADC3        | 12             | 6   | I/O  | software ADC facility and P3.4/PWM7 is the output                                                                                            |  |  |  |

| P3.4/PWM7        | 30             | 44  | I/O  | for the 6-bit PWM7. P3.5 to P3.7 have no alternative functions and are only available with the LQFP100                                       |  |  |  |

| P3.5             | -              | 54  | I/O  | package.                                                                                                                                     |  |  |  |

| P3.6             | -              | 59  | I/O  |                                                                                                                                              |  |  |  |

| P3.7             | _              | 25  | I/O  |                                                                                                                                              |  |  |  |

| V <sub>SSC</sub> | 13             | 11  | _    | core ground                                                                                                                                  |  |  |  |

| P0.0             | 14             | 16  | I/O  | Port 0. 8-bit programmable bidirectional port.                                                                                               |  |  |  |

| P0.1             | 15             | 17  | I/O  | P0.5 and P0.6 have 8 mA current sinking capability                                                                                           |  |  |  |

| P0.2             | 16             | 18  | I/O  | for direct drive of LEDs.                                                                                                                    |  |  |  |

| P0.3             | 17             | 22  | I/O  |                                                                                                                                              |  |  |  |

| P0.4             | 18             | 24  | I/O  |                                                                                                                                              |  |  |  |

| P0.5             | 19             | 13  | I/O  |                                                                                                                                              |  |  |  |

| P0.6             | 20             | 28  | I/O  |                                                                                                                                              |  |  |  |

| P0.7             | 21             | 29  | I/O  |                                                                                                                                              |  |  |  |

| V <sub>SSA</sub> | 22             | 30  | _    | analog ground                                                                                                                                |  |  |  |

| CVBS0            | 23             | 31  | I    | Composite video input. A positive-going 1 V (peak-to-peak) input is required.                                                                |  |  |  |

| CVBS1            | 24             | 32  | I    | connected via a 100 nF capacitor                                                                                                             |  |  |  |

| SYNC_FILTER      | 25             | 34  | I    | CVBS sync filter input. This pin should be connected to V <sub>SSA</sub> via a 100 nF capacitor.                                             |  |  |  |

| IREF             | 26             | 35  | I    | Reference current input for analog circuits, connected to $V_{SSA}$ via a 24 k $\Omega$ resistor.                                            |  |  |  |

| FRAME            | 27             | 41  | 0    | De-interlace output synchronized with the VSYNC pulse to produce a non-interlaced display by adjustment of the vertical deflection circuits. |  |  |  |

| VPE              | 28             | 42  | I    | OTP programming voltage                                                                                                                      |  |  |  |

|                  |                |     |      | L                                                                                                                                            |  |  |  |

# Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

| OVALDOL   |                | PIN                                                                                                                           | T)/DE | DECODINE ION                                                                                                                                                                                             |  |  |

|-----------|----------------|-------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SYMBOL    | SDIP52 LQFP100 |                                                                                                                               | TYPE  | DESCRIPTION                                                                                                                                                                                              |  |  |

| COR       | 29 43          |                                                                                                                               | 0     | Open-drain, active LOW output which allows selective contrast reduction of the TV picture to enhance a mixed mode display.                                                                               |  |  |

| $V_{DDA}$ | 31             | 45                                                                                                                            | _     | +3.3 V analog power supply                                                                                                                                                                               |  |  |

| В         | 32             | 46                                                                                                                            | 0     | pixel rate output of the BLUE colour information                                                                                                                                                         |  |  |

| G         | 33             | 47                                                                                                                            | 0     | pixel rate output of the GREEN colour information                                                                                                                                                        |  |  |

| R         | 34             | 48                                                                                                                            | 0     | pixel rate output of the RED colour information                                                                                                                                                          |  |  |

| VDS       | 35             | 52                                                                                                                            | 0     | video/data switch push-pull output for dot rate fast blanking                                                                                                                                            |  |  |

| HSYNC     | 36             | 53                                                                                                                            | I     | Schmitt triggered input for a TTL-level version of the horizontal sync pulse; the polarity of this pulse is programmable by register bit TXT1.H POLARITY.                                                |  |  |

| VSYNC     | 37             | 55                                                                                                                            | I     | Schmitt triggered input for a TTL-level version of the vertical sync pulse; the polarity of this pulse is programmable by register bit TXT1.V POLARITY.                                                  |  |  |

| $V_{SSP}$ | 38             | 12, 60                                                                                                                        | _     | periphery ground                                                                                                                                                                                         |  |  |

| $V_{DDC}$ | 39             | 63                                                                                                                            | _     | +3.3 V core power supply                                                                                                                                                                                 |  |  |

| OSCGND    | 40             | 69                                                                                                                            | _     | crystal oscillator ground                                                                                                                                                                                |  |  |

| XTALIN    | 41             | 70                                                                                                                            | I     | 12 MHz crystal oscillator input                                                                                                                                                                          |  |  |

| XTALOUT   | 42             | 71                                                                                                                            | 0     | 12 MHz crystal oscillator output                                                                                                                                                                         |  |  |

| RESET     | 43             | 73                                                                                                                            | I     | If the reset input is HIGH for at least 2 machine cycles (24 oscillator periods) while the oscillator is running, the device is reset; this pin should be connected to V <sub>DDP</sub> via a capacitor. |  |  |

| $V_{DDP}$ | 44             | 75                                                                                                                            | _     | +3.3 V periphery power supply                                                                                                                                                                            |  |  |

| P1.0/INT1 | 45             | 76                                                                                                                            | I/O   | Port 1. 8-bit programmable bidirectional port with                                                                                                                                                       |  |  |

| P1.1/T0   | 46             | 78                                                                                                                            | I/O   | alternative functions.                                                                                                                                                                                   |  |  |

| P1.2/INT0 | 47             | 79                                                                                                                            | I/O   | P1.0/INT1 is external interrupt 1 which can be                                                                                                                                                           |  |  |

| P1.3/T1   | 48             | 80                                                                                                                            | I/O   | triggered on the rising and falling edge of the pulse.                                                                                                                                                   |  |  |

| P1.6/SCL0 | 49             | 81                                                                                                                            | I/O   | P1.1/T0 is the Counter/Timer 0. P1.2/INT0 is external interrupt 0. P1.3/T1 is the Counter/Timer 1.                                                                                                       |  |  |

| P1.7/SDA0 | 50             | 82                                                                                                                            | I/O   | P1.6/SCL0 is the serial clock input for the I <sup>2</sup> C-bus                                                                                                                                         |  |  |

| P1.4/SCL1 | 51             | 83                                                                                                                            | I/O   | and P1.7/SDA0 is the serial data port for the                                                                                                                                                            |  |  |

| P1.5/SDA1 |                |                                                                                                                               | I/O   | $I^2C$ -bus. P1.4/SCL1 is the serial clock input for the $I^2C$ -bus and P1.5/SDA1 is the serial data port for the $I^2C$ -bus.                                                                          |  |  |

| VPE-2     | _              | 62                                                                                                                            | I     | OTP programming voltage                                                                                                                                                                                  |  |  |

| n.c.      | -              | 3, 7 to 10,14, 15, 19 to 21,<br>23, 26, 27, 33, 36 to 40,<br>49 to 51, 56 to 58, 61,<br>64 to 68, 72, 74, 77,<br>85 to 92, 99 | -     | not connected                                                                                                                                                                                            |  |  |

### Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

#### 7 MICROCONTROLLER

The functionality of the microcontroller used on this device is described here with reference to the industry standard 80C51 microcontroller. A full description of its functionality can be found in "Handbook IC20, 80C51-Based 8-bit Microcontrollers".

### 7.1 Microcontroller features

- 80C51 microcontroller core standard instruction set and timing

- 1 µs machine cycle

- Maximum 128K × 8-bit Program ROM

- Maximum of 12K × 8-bit Auxiliary RAM

- Interrupt Controller for individual enable/disable with two level priority

- Two 16-bit Timer/Counter registers

- · Watchdog Timer

- · Auxiliary RAM page pointer

- 16-bit Data pointer

- · Idle and Power-down mode

- 29 general I/O lines

- Eight 6-bit Pulse Width Modulator (PWM) outputs for control of TV analog signals

- One 14-bit PWM for Voltage Synthesis Tuner (VST) control

- 8-bit ADC with 4 multiplexed inputs

- 2 high current outputs for directly driving LEDs etc.

- I<sup>2</sup>C byte level bus interface with dual ports.

### 8 MEMORY ORGANIZATION

The device has the capability of a maximum of 128-kbyte Program ROM and 12-kbyte Data RAM internally.

### 8.1 ROM bank switching

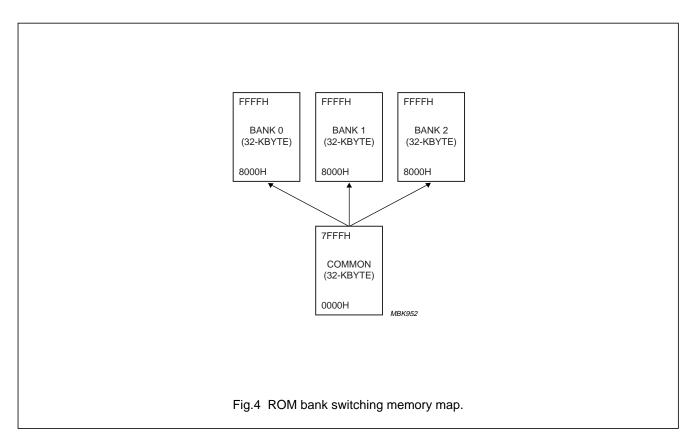

The 64-kbyte device has a continuous address space from 0 to 64 kbytes. The 128-kbyte memory is arranged in four banks of 32 kbytes. One of the 32-kbyte banks is common and is always addressable. The other three banks (Bank 0, Bank 1 and Bank 2) can be accessed by selecting the right bank via the SFR ROMBK bits; see Table 2.

The ROM bank switching is handled and supported by the compiler and linker development tools.

Table 2 ROM bank selection

| ROMBK1 | ROMBK0 | 0 TO 32-kbyte | 32 TO 64-kbyte |

|--------|--------|---------------|----------------|

| 0      | 0      | common        | Bank 0         |

| 0      | 1      | common        | Bank 1         |

| 1      | 0      | common        | Bank 2         |

| 1      | 1      | reserved      | reserved       |

### 8.2 Security bits - program and verify

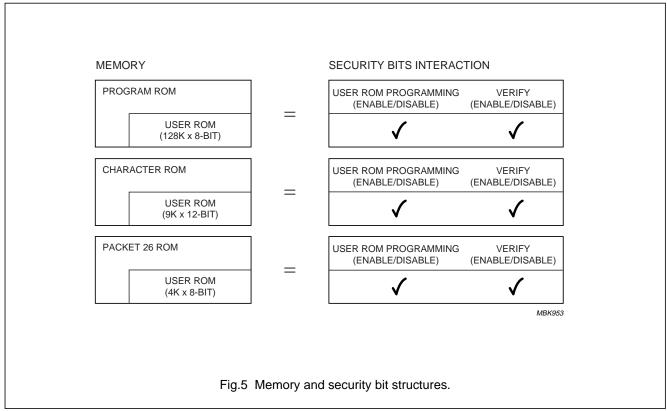

SAA55xx devices have a set of security bits allied with each section of the device, i.e. Program ROM, Character ROM and Packet 26 ROM. The security bits are used to prevent the ROM from being overwritten once programmed, and also the contents being verified once programmed. The security bits are one-time programmable and **cannot** be erased.

The SAA55xx memory and security bits are structured as shown in Fig.5. The SAA55xx security bits are set as shown in Fig.6 for production programmed devices and are set as shown in Fig.7 for production blank devices.

### 8.3 RAM organisation

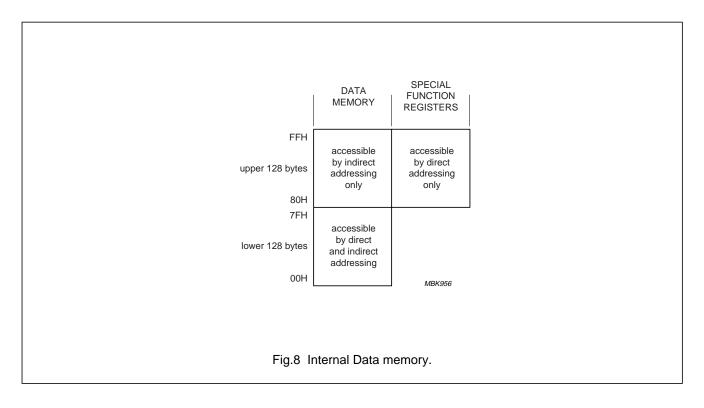

The internal Data RAM is organised into two areas, Data memory and Special Function Registers (SFRs) as shown in Fig.8.

### 8.4 Data memory

The Data memory is  $256 \times 8$  bits and occupies the address range 00H to FFH when using indirect addressing and 00H to 7FH when using direct addressing. The SFRs occupy the address range 80H to FFH and are accessible using direct addressing only.

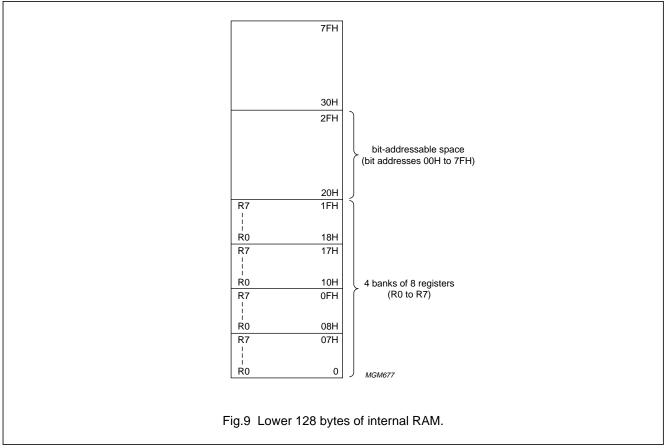

The lower 128 bytes of Data memory are mapped as shown in Fig.9. The lowest 24 bytes are grouped into 4 banks of 8 registers, the next 16 bytes above the register banks form a block of bit addressable memory space.

The upper 128 bytes is not allocated for any special area or functions.

Table 3 Bank selection

| RS1 | RS0 | BANK   |

|-----|-----|--------|

| 0   | 0   | Bank 0 |

| 0   | 1   | Bank 1 |

| 1   | 0   | Bank 2 |

| 1   | 1   | Bank 3 |

### Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

# Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

| MEMORY        |                                             | SECURITY BITS SET                        |                            |  |  |  |  |  |

|---------------|---------------------------------------------|------------------------------------------|----------------------------|--|--|--|--|--|

|               |                                             | USER ROM PROGRAMMING<br>(ENABLE/DISABLE) | VERIFY<br>(ENABLE/DISABLE) |  |  |  |  |  |

| PROGRAM ROM   | =                                           | DISABLED                                 | ENABLED                    |  |  |  |  |  |

| CHARACTER ROM | =                                           | DISABLED                                 | ENABLED                    |  |  |  |  |  |

| PACKET 26 ROM | =                                           | DISABLED                                 | ENABLED                    |  |  |  |  |  |

|               |                                             |                                          | MBK954                     |  |  |  |  |  |

|               |                                             |                                          |                            |  |  |  |  |  |

|               |                                             |                                          |                            |  |  |  |  |  |

| Fig.6         | Fig.6 Security bits for production devices. |                                          |                            |  |  |  |  |  |

| MEMORY        |                                                   | SECURITY BITS SET                        |                            |  |  |  |  |  |

|---------------|---------------------------------------------------|------------------------------------------|----------------------------|--|--|--|--|--|

|               |                                                   | USER ROM PROGRAMMING<br>(ENABLE/DISABLE) | VERIFY<br>(ENABLE/DISABLE) |  |  |  |  |  |

| PROGRAM ROM   | =                                                 | ENABLED                                  | ENABLED                    |  |  |  |  |  |

| CHARACTER ROM | =                                                 | ENABLED                                  | ENABLED                    |  |  |  |  |  |

| PACKET 26 ROM | =                                                 | ENABLED                                  | ENABLED                    |  |  |  |  |  |

|               |                                                   |                                          | MBK955                     |  |  |  |  |  |

|               |                                                   |                                          |                            |  |  |  |  |  |

|               |                                                   |                                          |                            |  |  |  |  |  |

| Fig.7 Se      | Fig.7 Security bits for production blank devices. |                                          |                            |  |  |  |  |  |

### Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

4

Philips Semiconductors

Preliminary specification

#### 8.5 SFR memory

The Special Function Register (SFR) space is used for port latches, timer, peripheral control, acquisition control, display control, etc. These registers can only be accessed by direct addressing. Sixteen of the addresses in the SFR space are both bit and byte addressable. The bit addressable SFRs are those whose address ends in 0H or 8H. A summary of the SFR map in address order is shown in Table 4.

A description of each of the SFR bits is shown in Table 5 which presents the SFRs in alphabetical order.

Table 4 SFR memory map

| ADD | R/W | NAME   | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       | RESET |

|-----|-----|--------|---------|---------|---------|---------|---------|---------|---------|---------|-------|

| 80H | R/W | P0     | P07     | P06     | P05     | P04     | P03     | P02     | P01     | P00     | FFH   |

| 81H | R/W | SP     | SP7     | SP6     | SP5     | SP4     | SP3     | SP2     | SP1     | SP0     | 07H   |

| 82H | R/W | DPL    | DPL7    | DPL6    | DPL5    | DPL4    | DPL3    | DPL2    | DPL1    | DPL0    | 00H   |

| 83H | R/W | DPH    | DPH7    | DPH6    | DPH5    | DPH4    | DPH3    | DPH2    | DPH1    | DPH0    | 00H   |

| 87H | R/W | PCON   | 0       | ARD     | RFI     | WLE     | GF1     | GF0     | PD      | IDL     | 00H   |

| 88H | R/W | TCON   | TF1     | TR1     | TF0     | TR0     | IE1     | IT1     | IE0     | IT0     | 00H   |

| 89H | R/W | TMOD   | GATE    | C/T     | M1      | M0      | GATE    | C/T     | M1      | MO      | 00H   |

| 8AH | R/W | TL0    | TL07    | TL06    | TL05    | TL04    | TL03    | TL02    | TL01    | TL00    | 00H   |

| 8BH | R/W | TL1    | TL17    | TL16    | TL15    | TL14    | TL13    | TL12    | TL11    | TL10    | 00H   |

| 8CH | R/W | TH0    | TH07    | TH06    | TH05    | TH04    | TH03    | TH02    | TH01    | TH00    | 00H   |

| 8DH | R/W | TH1    | TH17    | TH16    | TH15    | TH14    | TH13    | TH12    | TH11    | TH10    | 00H   |

| 90H | R/W | P1     | P17     | P16     | P15     | P14     | P13     | P12     | P11     | P10     | FFH   |

| 96H | R/W | P0CFGA | P0CFGA7 | P0CFGA6 | P0CFGA5 | P0CFGA4 | P0CFGA3 | P0CFGA2 | P0CFGA1 | P0CFGA0 | FFH   |

| 97H | R/W | P0CFGB | P0CFGB7 | P0CFGB6 | P0CFGB5 | P0CFGB4 | P0CFGB3 | P0CFGB2 | P0CFGB1 | P0CFGB0 | 00H   |

| 98H | R/W | SADB   | 0       | 0       | 0       | DC_COMP | SAD3    | SAD2    | SAD1    | SAD0    | 00H   |

| 9EH | R/W | P1CFGA | P1CFGA7 | P1CFGA6 | P1CFGA5 | P1CFGA4 | P1CFGA3 | P1CFGA2 | P1CFGA1 | P1CFGA0 | FFH   |

| 9FH | R/W | P1CFGB | P1CFGB7 | P1CFGB6 | P1CFGB5 | P1CFGB4 | P1CFGB3 | P1CFGB2 | P1CFGB1 | P1CFGB0 | 00H   |

| A0H | R/W | P2     | P27     | P26     | P25     | P24     | P23     | P22     | P21     | P20     | FFH   |

| A6H | R/W | P2CFGA | P2CFGA7 | P2CFGA6 | P2CFGA5 | P2CFGA4 | P2CFGA3 | P2CFGA2 | P2CFGA1 | P2CFGA0 | FFH   |

| A7H | R/W | P2CFGB | P2CFGB7 | P2CFGB6 | P2CFGB5 | P2CFGB4 | P2CFGB3 | P2CFGB2 | P2CFGB1 | P2CFGB0 | 00H   |

| A8H | R/W | IE     | EA      | EBUSY   | ES2     | ECC     | ET1     | EX1     | ET0     | EX0     | 00H   |

| ВОН | R/W | P3     | P37     | P36     | P35     | P34     | P33     | P32     | P31     | P30     | FFH   |

| S     |  |

|-------|--|

| ≯     |  |

| A55xx |  |

| ADD | R/W | NAME   | 7                   | 6                       | 5             | 4                           | 3                             | 2                 | 1                       | 0                | RESET |

|-----|-----|--------|---------------------|-------------------------|---------------|-----------------------------|-------------------------------|-------------------|-------------------------|------------------|-------|

| В2Н | R/W | TXT18  | NOT3                | NOT2                    | NOT1          | NOT0                        | 0                             | 0                 | BS1                     | BS0              | 00H   |

| взн | R/W | TXT19  | TEN                 | TC2                     | TC1           | TC0                         | 0                             | 0                 | TS1                     | TS0              | 00H   |

| В4Н | R/W | TXT20  | DRCS<br>ENABLE      | OSD<br>PLANES           | 0             | 0                           | OSD LANG<br>ENABLE            | OSD LAN2          | OSD LAN1                | OSD LAN0         | 00H   |

| В5Н | R/W | TXT21  | DISP<br>LINES1      | DISP<br>LINES0          | CHAR SIZE1    | CHAR<br>SIZE0               | I <sup>2</sup> C PORT 1       | CC ON             | I <sup>2</sup> C PORT 0 | CC/TXT           | 02H   |

| В6Н | R   | TXT22  | GPF7                | GPF6                    | GPF5          | GPF4                        | GPF3                          | GPF2              | GPF1                    | 1                | XXH   |

| В7Н | R/W | CCLIN  | 0                   | 0                       | 0             | CS4                         | CS3                           | CS2               | CS1                     | CS0              | 15H   |

| B8H | R/W | IP     | 0                   | PBUSY                   | PES2          | PCC                         | PT1                           | PX1               | PT0                     | PX0              | 00H   |

| В9Н | R/W | TXT17  | 0                   | FORCE<br>ACQ1           | FORCE<br>ACQ0 | FORCE<br>DISP1              | FORCE<br>DISP0                | SCREEN<br>COL2    | SCREEN<br>COL1          | SCREEN<br>COL0   | 00H   |

| BAH | R   | WSS1   | 0                   | 0                       | 0             | WSS<3:0><br>ERROR           | WSS3                          | WSS2              | WSS1                    | WSS0             | 00H   |

| ввн | R   | WSS2   | 0                   | 0                       | 0             | WSS<7:4><br>ERROR           | WSS7                          | WSS6              | WSS5                    | WSS4             | 00H   |

| ВСН | R   | WSS3   | WSS<13:11><br>ERROR | WSS13                   | WSS12         | WSS11                       | WSS<10:8><br>ERROR            | WSS10             | WSS9                    | WSS8             | 00H   |

| BEH | R/W | P3CFGA | 1                   | 1                       | 1             | P3CFGA4                     | P3CFGA3                       | P3CFGA2           | P3CFGA1                 | P3CFGA0          | FFH   |

| BFH | R/W | P3CFGB | 0                   | 0                       | 0             | P3CFGB4                     | P3CFGB3                       | P3CFGB2           | P3CFGB1                 | P3CFGB0          | 00H   |

| C0H | R/W | TXT0   | X24 POSN            | DISPLAY<br>X24          | AUTO<br>FRAME | DISABLE<br>HEADER<br>ROLL   | DISPLAY<br>STATUS<br>ROW ONLY | DISABLE<br>FRAME  | VPS ON                  | INV ON           | 00H   |

| C1H | R/W | TXT1   | EXT PKT<br>OFF      | 8-BIT                   | ACQ OFF       | X26 OFF                     | FULL<br>FIELD                 | FIELD<br>POLARITY | H<br>POLARITY           | V<br>POLARITY    | 00H   |

| C2H | R/W | TXT2   | ACQ BANK            | REQ3                    | REQ2          | REQ1                        | REQ0                          | SC2               | SC1                     | SC0              | 00H   |

| СЗН | W   | TXT3   | -                   | -                       | -             | PRD4                        | PRD3                          | PRD2              | PRD1                    | PRD0             | 00H   |

| C4H | R/W | TXT4   | OSD BANK<br>ENABLE  | QUAD<br>WIDTH<br>ENABLE | EAST/WEST     | DISABLE<br>DOUBLE<br>HEIGHT | B MESH<br>ENABLE              | C MESH<br>ENABLE  | TRANS<br>ENABLE         | SHADOW<br>ENABLE | 00H   |

| C5H | R/W | TXT5   | BKGND OUT           | BKGND IN                | COR OUT       | COR IN                      | TEXT OUT                      | TEXT IN           | PICTURE<br>ON OUT       | PICTURE<br>ON IN | 03H   |

2000 Feb 23

15

2000 Feb 23

SAA55xx

| ADD | R/W | NAME   | 7                 | 6                  | 5               | 4                  | 3                  | 2               | 1                 | 0                          | RESET        |

|-----|-----|--------|-------------------|--------------------|-----------------|--------------------|--------------------|-----------------|-------------------|----------------------------|--------------|

| C6H | R/W | TXT6   | BKGND OUT         | BKGND IN           | COR OUT         | COR IN             | TEXT OUT           | TEXT IN         | PICTURE<br>ON OUT | PICTURE<br>ON IN           | 03H          |

| C7H | R/W | TXT7   | STATUS<br>ROW TOP | CURSOR<br>ON       | REVEAL          | BOTTOM<br>/TOP     | DOUBLE<br>HEIGHT   | BOX ON 24       | BOX ON<br>1-23    | BOX ON 0                   | 00H          |

| C8H | R/W | TXT8   | (reserved)<br>0   | FLICKER<br>STOP ON | (reserved)<br>0 | DISABLE<br>SPANISH | PKT 26<br>RECEIVED | WSS<br>RECEIVED | WSS ON            | CVBS1/<br>CVBS0            | 00H          |

| C9H | R/W | TXT9   | CURSOR<br>FREEZE  | CLEAR<br>MEMORY    | A0              | R4                 | R3                 | R2              | R1                | R0                         | 00H          |

| CAH | R/W | TXT10  | 0                 | 0                  | C5              | C4                 | C3                 | C2              | C1                | C0                         | 00H          |

| СВН | R/W | TXT11  | D7                | D6                 | D5              | D4                 | D3                 | D2              | D1                | D0                         | 00H          |

| ССН | R   | TXT12  | 525/625<br>SYNC   | SPANISH            | ROM VER3        | ROM VER2           | ROM VER1           | ROM VER0        | 1                 | VIDEO<br>SIGNAL<br>QUALITY | XXXX<br>XX1X |

| CDH | R/W | TXT14  | 0                 | 0                  | 0               | -                  | PAGE3              | PAGE2           | PAGE1             | PAGE0                      | 00H          |

| CEH | R/W | TXT15  | 0                 | 0                  | 0               | -                  | BLOCK3             | BLOCK2          | BLOCK1            | BLOCK0                     | 00H          |

| D0H | R/W | PSW    | С                 | AC                 | F0              | RS1                | RS0                | OV              | -                 | Р                          | 00H          |

| D2H | R/W | TDACL  | TD7               | TD6                | TD5             | TD4                | TD3                | TD2             | TD1               | TD0                        | 00H          |

| D3H | R/W | TDACH  | TPWE              | 1                  | TD13            | TD12               | TD11               | TD10            | TD9               | TD8                        | 40H          |

| D4H | R/W | PWM7   | PW7E              | 1                  | PW7V5           | PW7V4              | PW7V3              | PW7V2           | PW7V1             | PW7V0                      | 40H          |

| D5H | R/W | PWM0   | PW0E              | 1                  | PW0V5           | PW0V4              | PW0V3              | PW0V2           | PW0V1             | PW0V0                      | 40H          |

| D6H | R/W | PWM1   | PW1E              | 1                  | PW1V5           | PW1V4              | PW1V3              | PW1V2           | PW1V1             | PW1V0                      | 40H          |

| D7H | R   | CCDAT1 | CCD17             | CCD16              | CCD15           | CCD14              | CCD13              | CCD12           | CCD11             | CCD10                      | 00H          |

| D8H | R/W | S1CON  | CR2               | ENSI               | STA             | STO                | SI                 | AA              | CR1               | CR0                        | 00H          |

| D9H | R   | S1STA  | STAT4             | STAT3              | STAT2           | STAT1              | STAT0              | 0               | 0                 | 0                          | F8H          |

| DAH | R/W | S1DAT  | DAT7              | DAT6               | DAT5            | DAT4               | DAT3               | DAT2            | DAT1              | DAT0                       | 00H          |

| DBH | R/W | S1ADR  | ADR6              | ADR5               | ADR4            | ADR3               | ADR2               | ADR1            | ADR0              | GC                         | 00H          |

| DCH | R/W | PWM3   | PW3E              | 1                  | PW3V5           | PW3V4              | PW3V3              | PW3V2           | PW3V1             | PW3V0                      | 40H          |

| DDH | R/W | PWM4   | PW4E              | 1                  | PW4V5           | PW4V4              | PW4V3              | PW4V2           | PW4V1             | PW4V0                      | 40H          |

| DEH | R/W | PWM5   | PW5E              | 1                  | PW5V5           | PW5V4              | PW5V3              | PW5V2           | PW5V1             | PW5V0                      | 40H          |

| DFH | R/W | PWM6   | PW6E              | 1                  | PW6V5           | PW6V4              | PW6V3              | PW6V2           | PW6V1             | PW6V0                      | 40H          |

| E0H | R/W | ACC    | ACC7              | ACC6               | ACC5            | ACC4               | ACC3               | ACC2            | ACC1              | ACC0                       | 00H          |

Enhanced TV microcontrollers with On-Screen Display (OSD)

2000 Feb 23

ADD R/W

E4H R/W

E7H R

E8H R/W

F0H R/W

F8H R/W

FAH

FBH R/W

FEH

FFH R/W

R/W

R

NAME

PWM2

CCDAT2

SAD

В

TXT13

XRAMP

ROMBK

WDTKEY

WDT

7

PW2E

CCD27

VHI

В7

VPS

RECEIVED

XRAMP7

STANDBY

WKEY7

WDV7

5

PW2V5

CCD25

CH0

B5

525 DISPLAY

XRAMP5

0

WKEY5

WDV5

4

PW2V4

CCD24

ST

В4

525 TEXT

XRAMP4

0

WKEY4

WDV4

6

1

CCD26

CH1

В6

PAGE

CLEARING

XRAMP6

0

WKEY6

WDV6

2

PW2V2

CCD22

SAD6

B2

PKT 8/30

XRAMP2

0

WKEY2

WDV2

1

PW2V1

CCD21

SAD5

В1

FASTEXT

XRAMP1

ROMBK1

WKEY1

WDV1

3

PW2V3

CCD23

SAD7

ВЗ

625 TEXT

XRAMP3

0

WKEY3

WDV3

SAA55xx

Enhanced TV microcontrollers with On-Screen Display (OSD)

RESET

40H

00H

00H

00H

XXXX XXX0

00H

00H

00H

00H

0

PW2V0

CCD20

SAD4

B0

0

XRAMP0

ROMBK0

WKEY0

WDV0

|   | _   |  |

|---|-----|--|

| • | - 1 |  |

# Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

Table 5 SFR bit description

| BIT                              | FUNCTION                                                                            |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| Accumulator (ACC)                |                                                                                     |  |  |  |

| ACC7 to ACC0                     | accumulator value                                                                   |  |  |  |

| B Register (B)                   |                                                                                     |  |  |  |

| B7 to B0                         | B register value                                                                    |  |  |  |

| CC data byte 1 (CCDAT1)          |                                                                                     |  |  |  |

| CCD17 to CCD10                   | closed caption first data byte                                                      |  |  |  |

| CC data byte 2 (CCDAT2)          |                                                                                     |  |  |  |

| CCD26 to CCD20                   | closed caption second data byte                                                     |  |  |  |

| CC line (CCLIN)                  |                                                                                     |  |  |  |

| CS4 to CS0                       | closed caption slice line using 525-line number                                     |  |  |  |

| Data Pointer High byte (DPH)     |                                                                                     |  |  |  |

| DPH7 to DPH0                     | data pointer high byte, used with DPL to address auxiliary memory                   |  |  |  |

| Data Pointer Low byte (DPL)      |                                                                                     |  |  |  |

| DPL7 to DPL0                     | data pointer low byte, used with DPH to address auxiliary memory                    |  |  |  |

| Interrupt Enable Register (IE)   |                                                                                     |  |  |  |

| EA                               | disable all interrupts (logic 0), or use individual interrupt enable bits (logic 1) |  |  |  |

| EBUSY                            | enable BUSY interrupt                                                               |  |  |  |

| ES2                              | enable I <sup>2</sup> C-bus interrupt                                               |  |  |  |

| ECC                              | enable Closed Caption interrupt                                                     |  |  |  |

| ET1                              | enable Timer 1 interrupt                                                            |  |  |  |

| EX1                              | enable external interrupt 1                                                         |  |  |  |

| ET0                              | enable Timer 0 interrupt                                                            |  |  |  |

| EX0                              | enable external interrupt 0                                                         |  |  |  |

| Interrupt Priority Register (IP) |                                                                                     |  |  |  |

| PBUSY                            | priority EBUSY interrupt                                                            |  |  |  |

| PES2                             | priority ES2 interrupt                                                              |  |  |  |

| PCC                              | priority ECC interrupt                                                              |  |  |  |

| PT1                              | priority Timer 1 interrupt                                                          |  |  |  |

| PX1                              | priority external interrupt 1                                                       |  |  |  |

| PT0                              | priority Timer 0 interrupt                                                          |  |  |  |

| PX0                              | priority external interrupt 0                                                       |  |  |  |

| Port 0 (P0)                      |                                                                                     |  |  |  |

| P07 to P00                       | Port 0 I/O register connected to external pins                                      |  |  |  |

# Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

| BIT                                                                 | FUNCTION                                                                                                                                                                                    |  |  |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Port 1 (P1)                                                         |                                                                                                                                                                                             |  |  |

| P17 to P10                                                          | Port 1 I/O register connected to external pins                                                                                                                                              |  |  |

| Port 2 (P2)                                                         |                                                                                                                                                                                             |  |  |

| P27 to P20                                                          | Port 2 I/O register connected to external pins                                                                                                                                              |  |  |

| Port 3 (P3)                                                         |                                                                                                                                                                                             |  |  |

| P37 to P30                                                          | Port 3 I/O register connected to external pins; P37 to P35 are only available with the LQFP100 package.                                                                                     |  |  |

| Port 0 Configuration A (P0CFGA)                                     | and Port 0 Configuration B (P0CFGB)                                                                                                                                                         |  |  |

| P0CFGA<7:0> and P0CFGB<7:0>                                         | These two registers are used to configure Port 0 pins. For example, the configuration of Port 0 pin 3 is controlled by using bit 3 in both P0CFGA and P0CFGB. P0CFGB <x>/P0CFGA<x>:</x></x> |  |  |

|                                                                     | 00 = P0.x in open-drain configuration                                                                                                                                                       |  |  |

|                                                                     | 01 = P0.x in quasi-bidirectional configuration                                                                                                                                              |  |  |

|                                                                     | 10 = P0.x in high-impedance configuration                                                                                                                                                   |  |  |

|                                                                     | 11 = P0.x in push-pull configuration                                                                                                                                                        |  |  |

| Port 1 Configuration A (P1CFGA)                                     | and Port 1 Configuration B (P1CFGB)                                                                                                                                                         |  |  |

| P1CFGA<7:0> and P1CFGB<7:0>                                         | These two registers are used to configure Port 1 pins. For example, the configuration of Port 1 pin 3 is controlled by using bit 3 in both P1CFGA and P1CFGB. P1CFGB                        |  |  |

|                                                                     | 00 = P1.x in open-drain configuration                                                                                                                                                       |  |  |

|                                                                     | 01 = P1.x in quasi-bidirectional configuration                                                                                                                                              |  |  |

|                                                                     | 10 = P1.x in high-impedance configuration                                                                                                                                                   |  |  |

|                                                                     | 11 = P1.x in push-pull configuration                                                                                                                                                        |  |  |

| Port 2 Configuration A (P2CFGA)                                     | and Port 2 Configuration B (P2CFGB)                                                                                                                                                         |  |  |

| P2CFGA<7:0> and P2CFGB<7:0>                                         | These two registers are used to configure Port 2 pins. For example, the configuration of Port 2 pin 3 is controlled by using bit 3 in both P2CFGA and P2CFGB. P2CFGB                        |  |  |

|                                                                     | 00 = P2.x in open-drain configuration                                                                                                                                                       |  |  |

|                                                                     | 01 = P2.x in quasi-bidirectional configuration                                                                                                                                              |  |  |

|                                                                     | 10 = P2.x in high-impedance configuration                                                                                                                                                   |  |  |

|                                                                     | 11 = P2.x in push-pull configuration                                                                                                                                                        |  |  |

| Port 3 Configuration A (P3CFGA) and Port 3 Configuration B (P3CFGB) |                                                                                                                                                                                             |  |  |

| P3CFGA<7:0> and P3CFGB<7:0>                                         | These two registers are used to configure Port 3 pins. For example, the configuration of Port 3 pin 3 is controlled by using bit 3 in both P3CFGA and P3CFGB. P3CFGB <x>/P3CFGA<x>:</x></x> |  |  |

|                                                                     | 00 = P3.x in open-drain configuration                                                                                                                                                       |  |  |

|                                                                     | 01 = P3.x in quasi-bidirectional configuration                                                                                                                                              |  |  |

|                                                                     | 10 = P3.x in high-impedance configuration                                                                                                                                                   |  |  |

|                                                                     | 11 = P3.x in push-pull configuration                                                                                                                                                        |  |  |

# Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

| BIT                                             | FUNCTION                                                                         |  |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

| Power Control Register (PCON)                   |                                                                                  |  |  |  |

| ARD                                             | auxiliary RAM disable bit, all MOVX instructions access the external data memory |  |  |  |

| RFI                                             | disable ALE during internal access to reduce radio frequency interference        |  |  |  |

| WLE                                             | Watchdog Timer enable                                                            |  |  |  |

| GF1                                             | general purpose flag 1                                                           |  |  |  |

| GF0                                             | general purpose flag 0                                                           |  |  |  |

| PD                                              | Power-down mode activation bit                                                   |  |  |  |

| IDL                                             | Idle mode activation bit                                                         |  |  |  |

| Program Status Word (PSW)                       |                                                                                  |  |  |  |

| С                                               | carry bit                                                                        |  |  |  |

| AC                                              | auxiliary carry bit                                                              |  |  |  |

| F0                                              | flag 0                                                                           |  |  |  |

| RS1 to RS0                                      | register bank selector bits RS<1:0>:                                             |  |  |  |

|                                                 | 00 = Bank 0 (00H to 07H)                                                         |  |  |  |

|                                                 | 01 = Bank 1 (08H to 0FH)                                                         |  |  |  |

|                                                 | 10 = Bank 2 (10H to 17H)                                                         |  |  |  |

|                                                 | 11 = Bank 3 (18H to 1FH)                                                         |  |  |  |

| OV                                              | overflow flag                                                                    |  |  |  |

| P                                               | parity bit                                                                       |  |  |  |

| Pulse Width Modulator 0 Control                 | Register (PWM0)                                                                  |  |  |  |

| PW0E                                            | activate this PWM and take control of respective port pin (logic 1)              |  |  |  |

| PW0V5 to PW0V0                                  | pulse width modulator high time                                                  |  |  |  |

| Pulse Width Modulator 1 Control                 | Register (PWM1)                                                                  |  |  |  |

| PW1E                                            | activate this PWM (logic 1)                                                      |  |  |  |

| PW1V5 to PW1V0                                  | pulse width modulator high time                                                  |  |  |  |

| Pulse Width Modulator 2 Control                 | Register (PWM2)                                                                  |  |  |  |

| PW2E                                            | activate this PWM (logic 1)                                                      |  |  |  |

| PW2V5 to PW2V0                                  | pulse width modulator high time                                                  |  |  |  |

| Pulse Width Modulator 3 Control Register (PWM3) |                                                                                  |  |  |  |

| PW3E                                            | activate this PWM (logic 1)                                                      |  |  |  |

| PW3V5 to PW3V0                                  | pulse width modulator high time                                                  |  |  |  |

| Pulse Width Modulator 4 Control                 | Register (PWM4)                                                                  |  |  |  |

| PW4E                                            | activate this PWM (logic 1)                                                      |  |  |  |

| PW4V5 to PW4V0                                  | pulse width modulator high time                                                  |  |  |  |

# Enhanced TV microcontrollers with On-Screen Display (OSD)

SAA55xx

| BIT                                             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pulse Width Modulator 5 Control Register (PWM5) |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| PW5E                                            | activate this PWM (logic 1)                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| PW5V5 to PW5V0                                  | pulse width modulator high time                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Pulse Width Modulator 6 Co                      | ntrol Register (PWM6)                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| PW6E                                            | activate this PWM (logic 1)                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| PW6V5 to PW6V0                                  | pulse width modulator high time                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Pulse Width Modulator 7 Co                      | ntrol Register (PWM7)                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

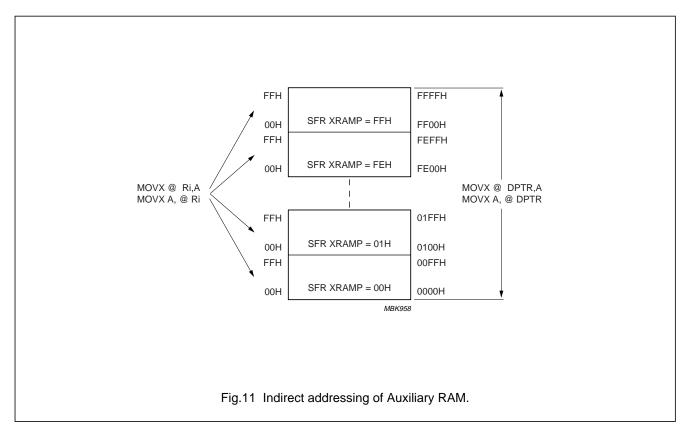

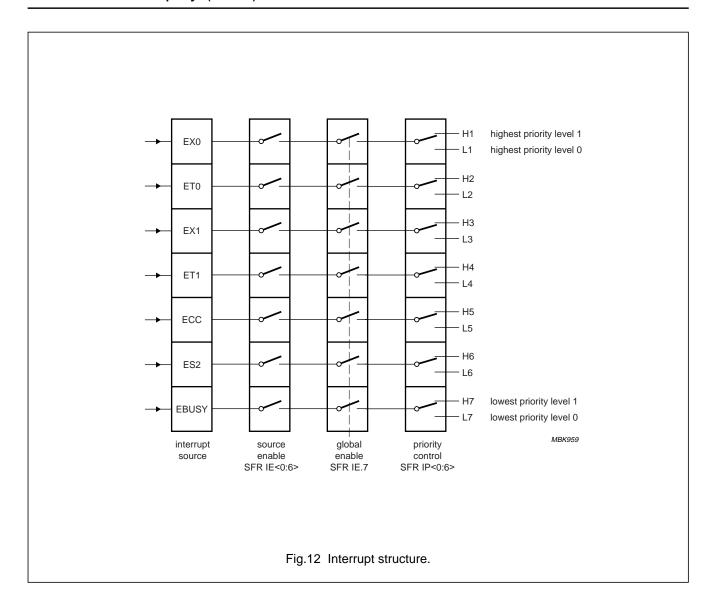

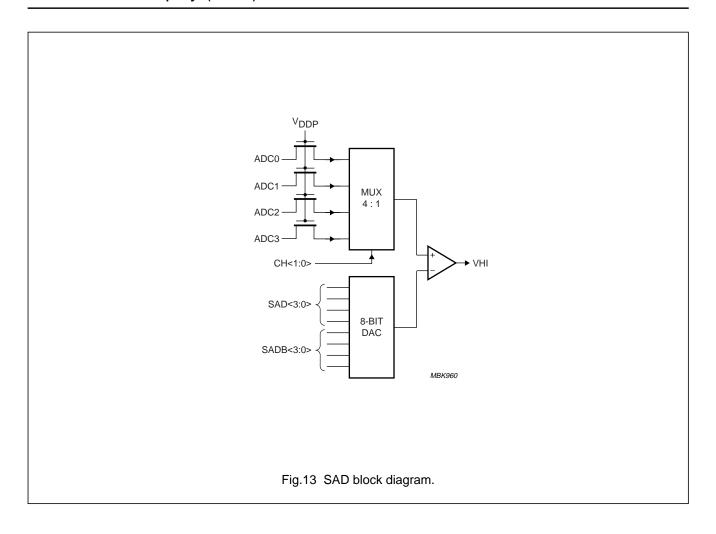

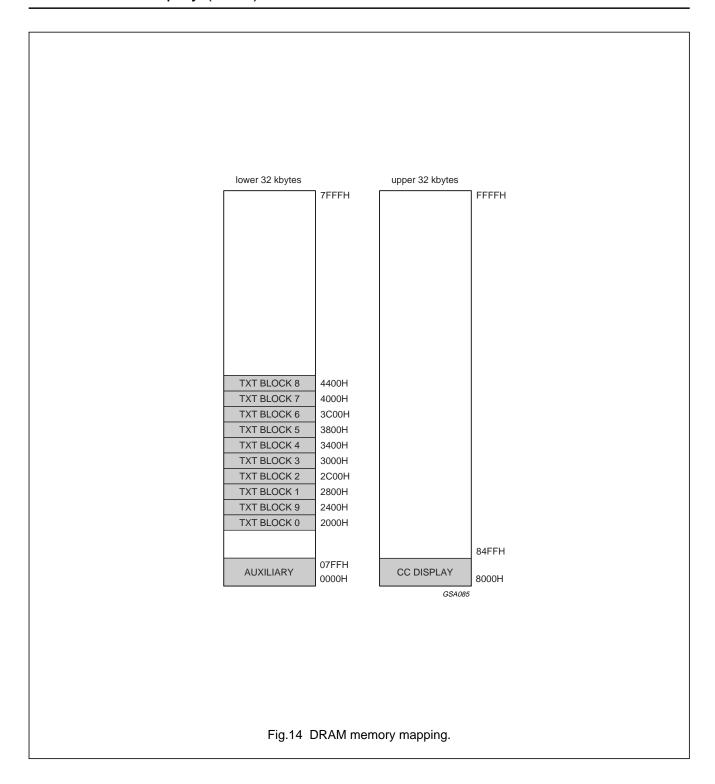

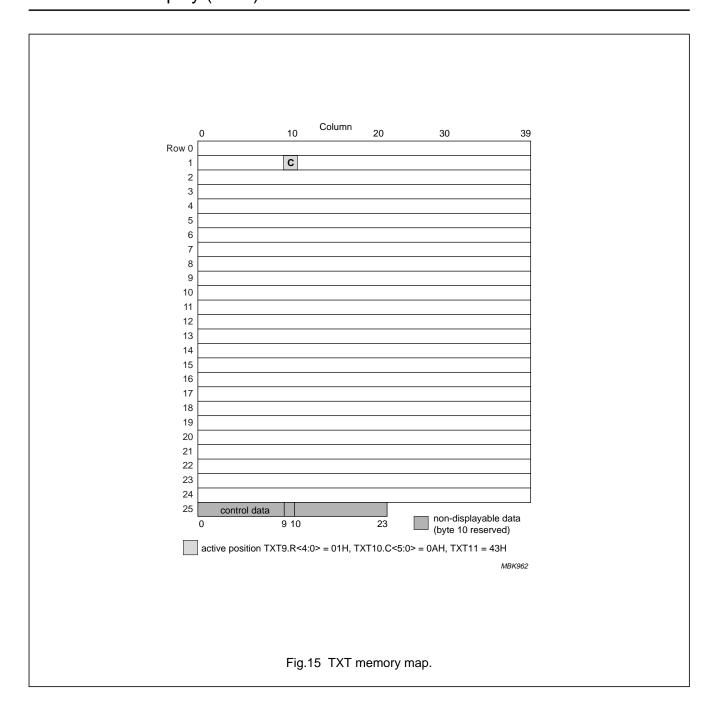

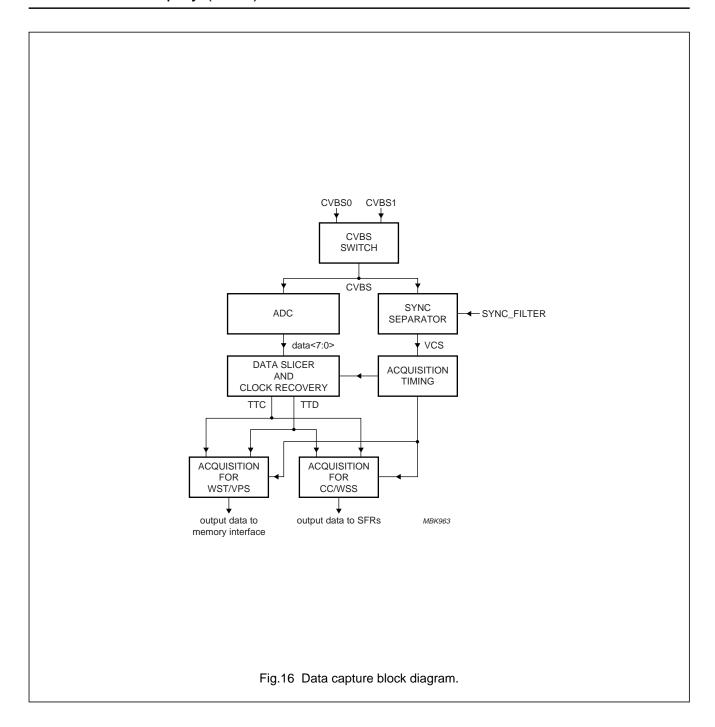

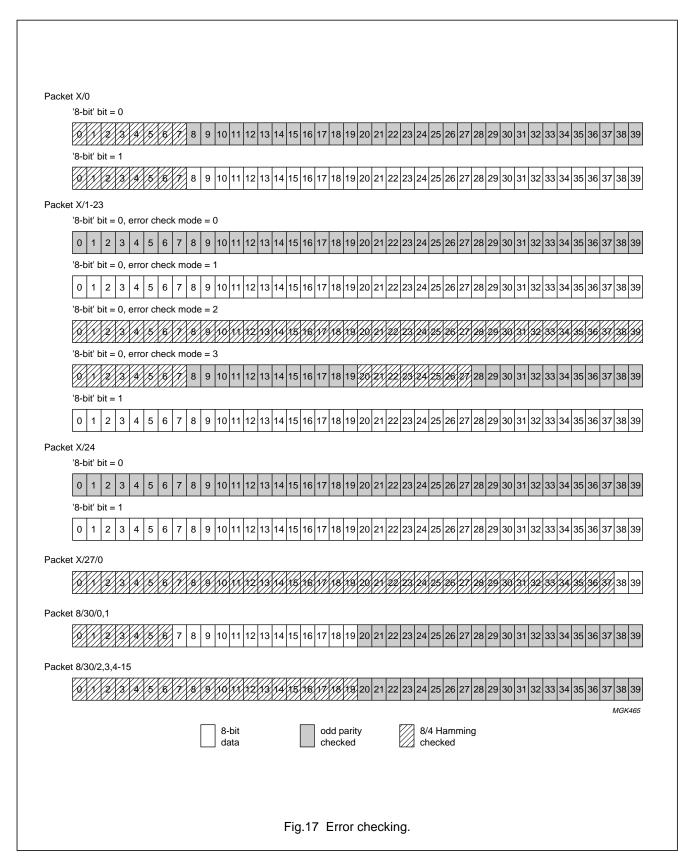

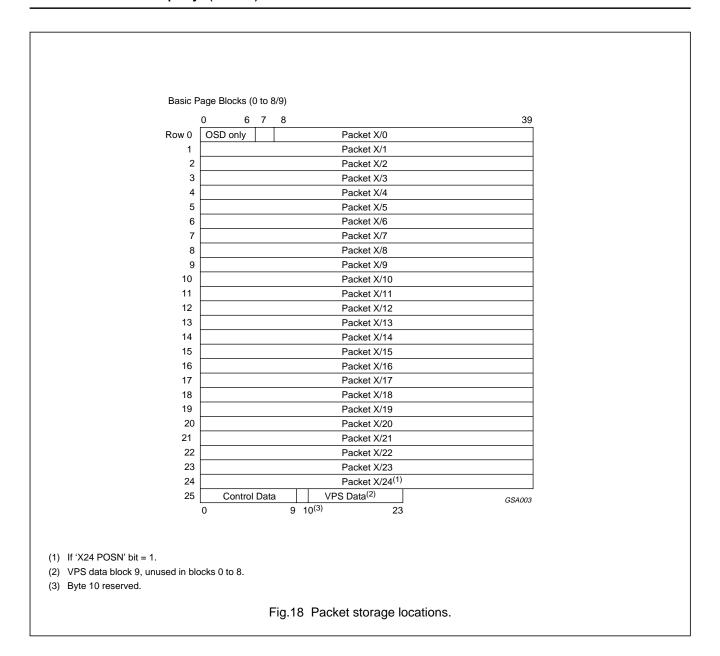

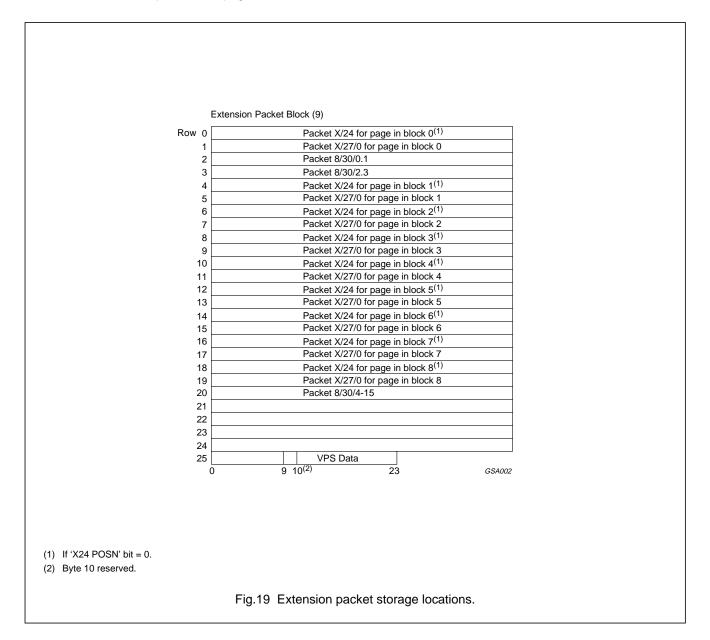

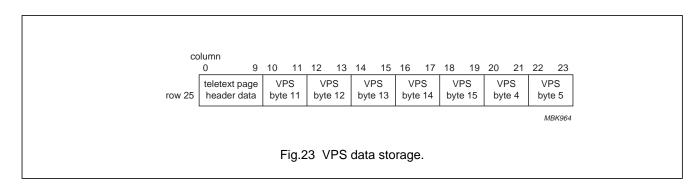

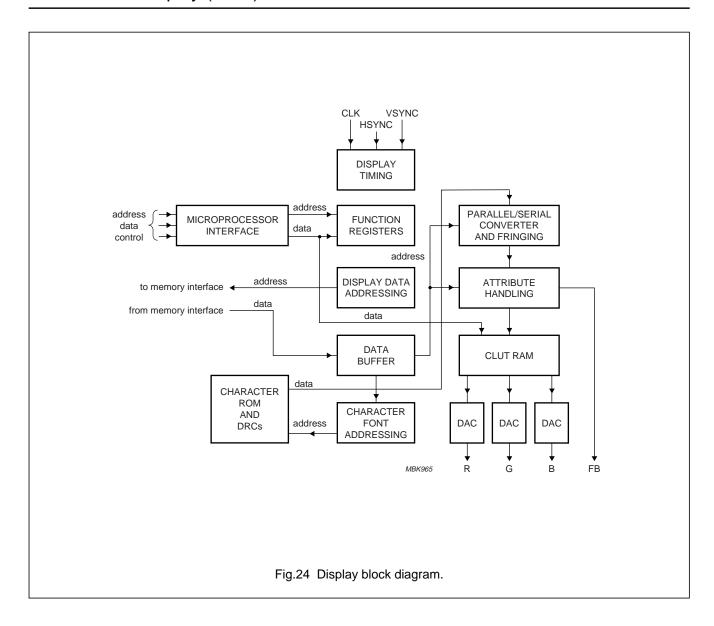

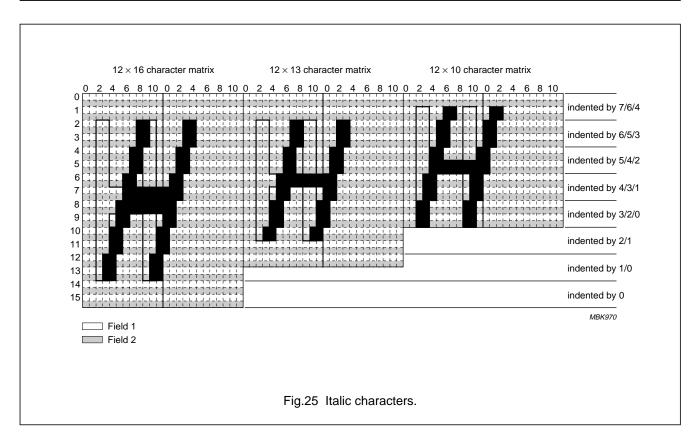

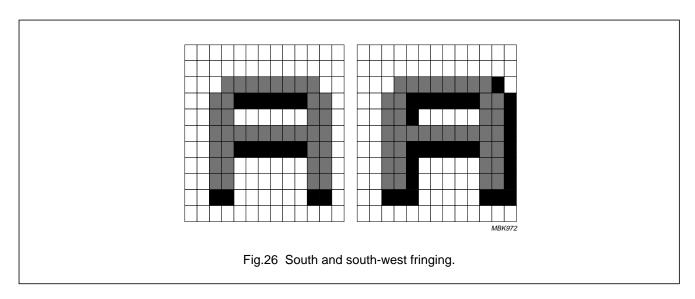

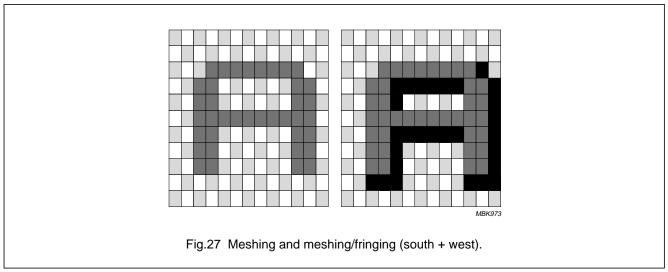

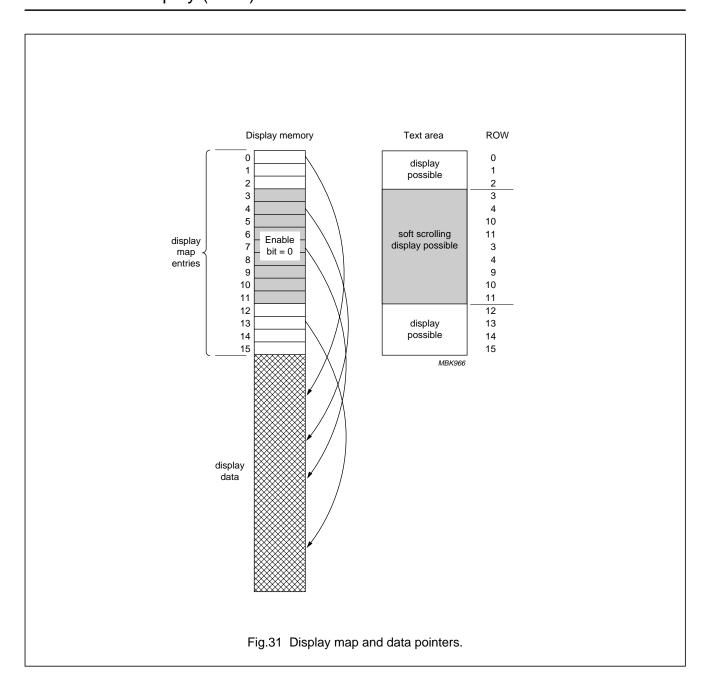

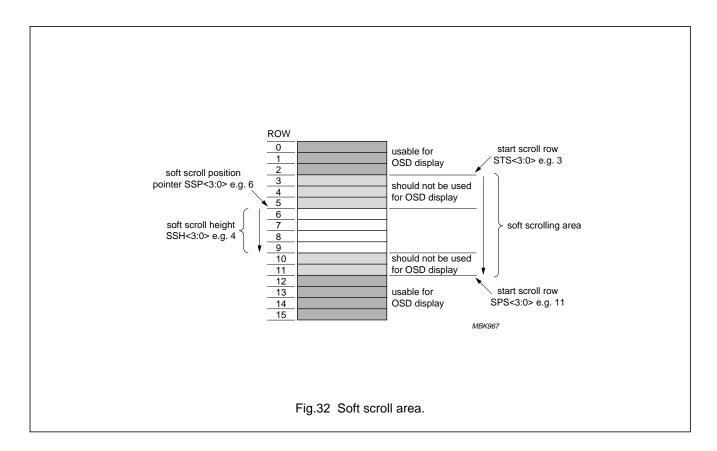

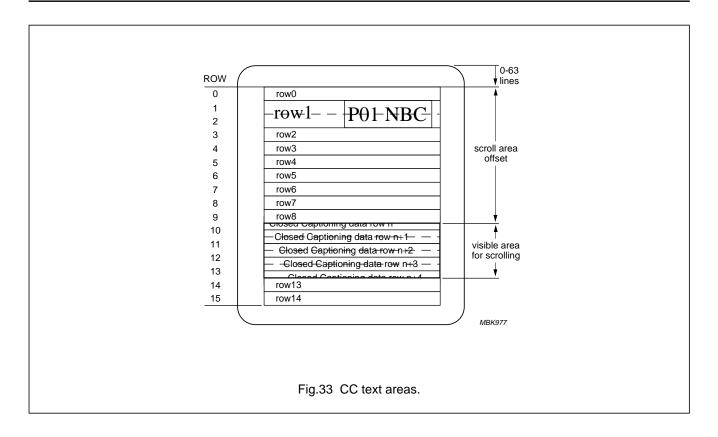

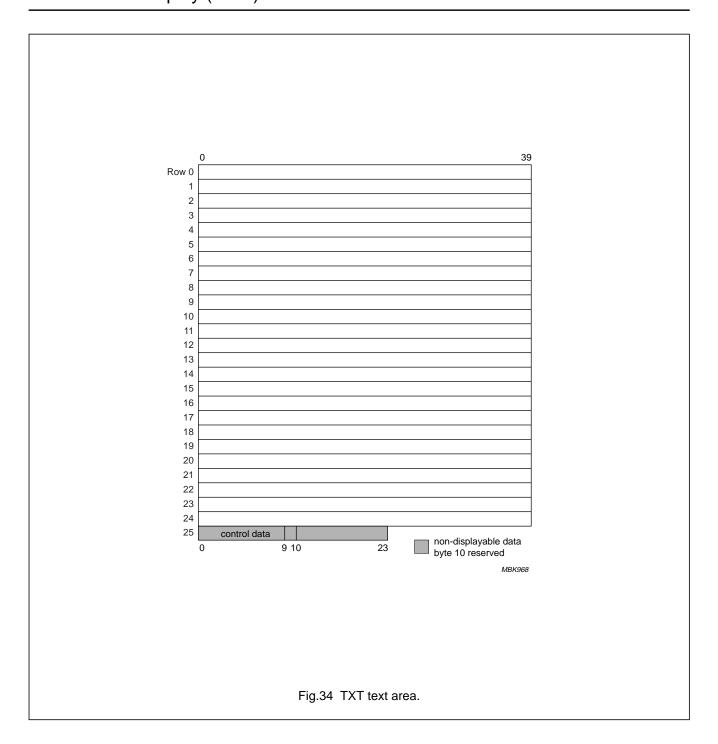

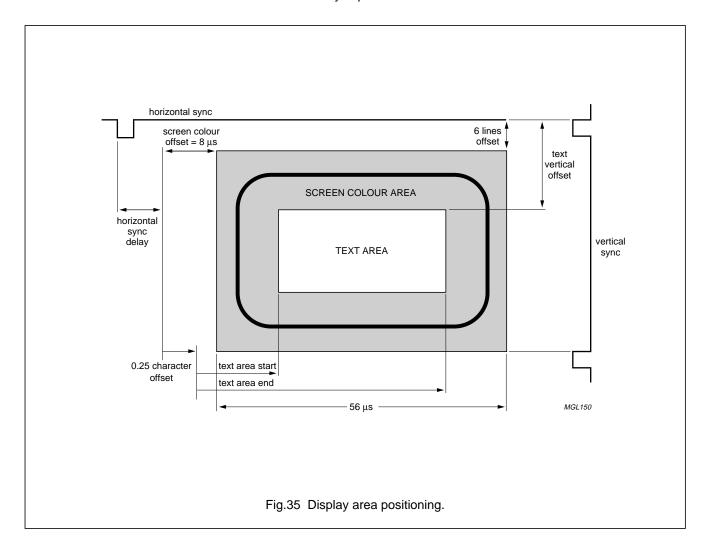

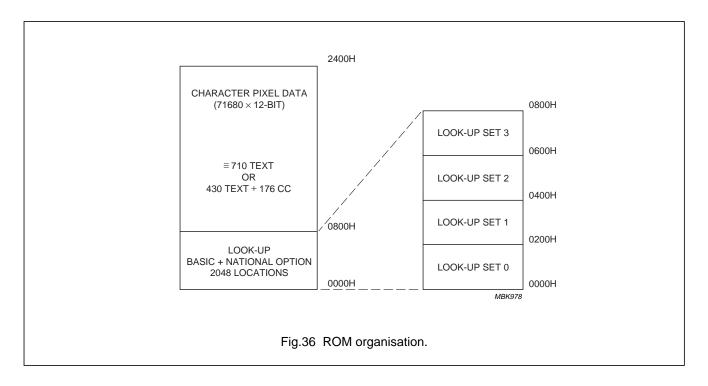

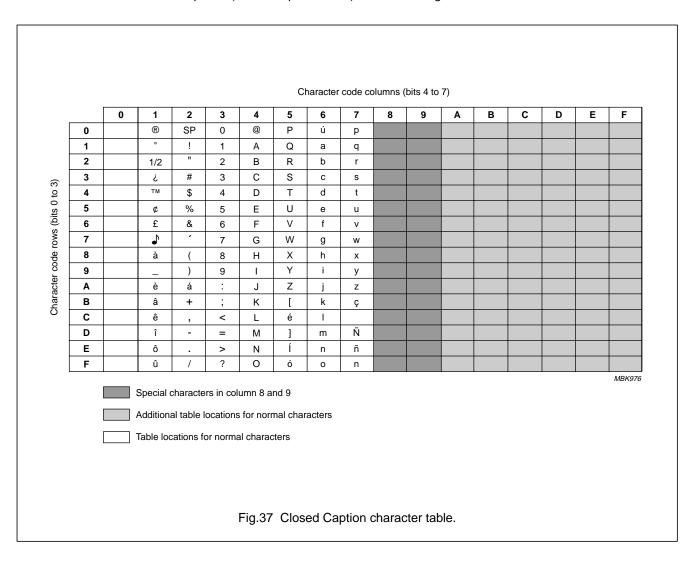

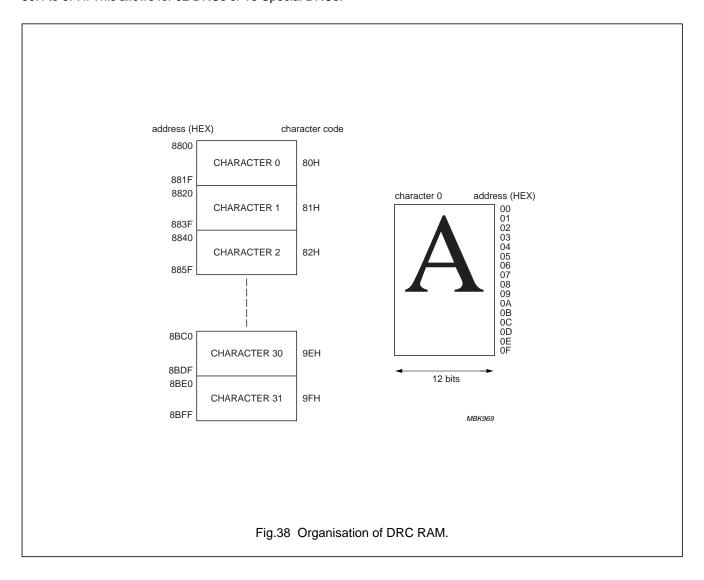

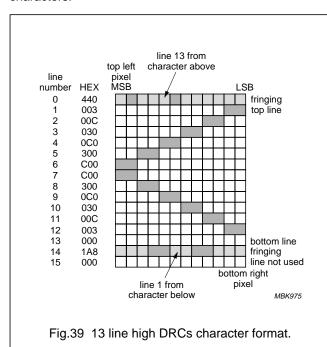

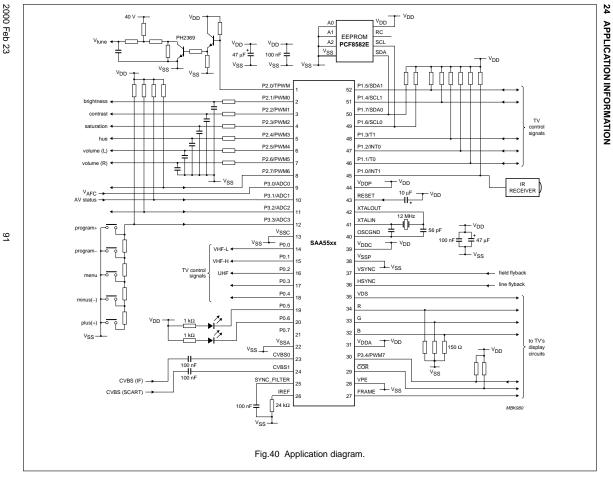

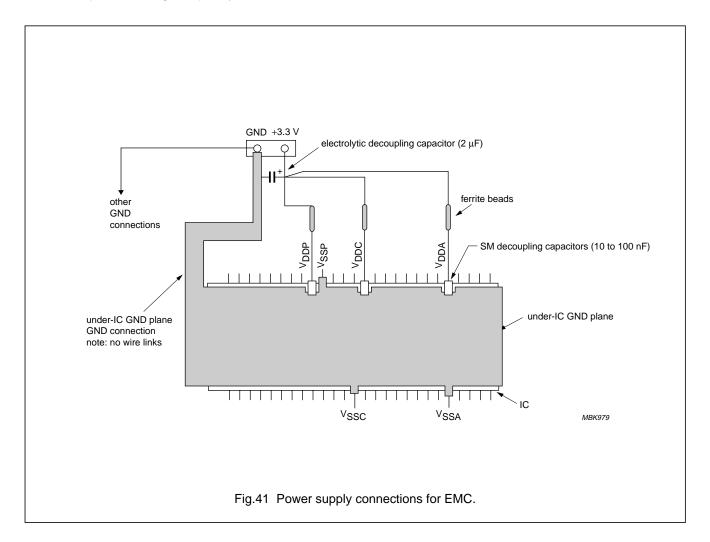

| PW7E                                            | activate this PWM (logic 1)                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |