## INTEGRATED CIRCUITS

# DATA SHEET

# **74LVT74**3.3V Dual D-type flip-flop

Product specification

1996 Aug 28

IC24 Data Handbook

# 3.3V Dual D-type flip-flop

74LVT74

### **QUICK REFERENCE DATA**

| SYMBOL                               | DL PARAMETER CONDITION  Tamb = 25  GND = 0 |                                                  | TYPICAL    | UNIT |

|--------------------------------------|--------------------------------------------|--------------------------------------------------|------------|------|

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation<br>delay<br>CPn to Qn          | C <sub>L</sub> = 50pF;<br>V <sub>CC</sub> = 3.3V | 3.1<br>3.6 | ns   |

| C <sub>IN</sub>                      | Input capacitance                          | V <sub>I</sub> = 0V or 3.0V                      | 3          | pF   |

| Icc                                  | Total supply current                       | V <sub>CC</sub> = 3.6V                           | 0.5        | mA   |

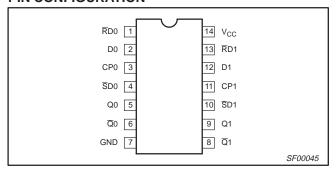

### **PIN CONFIGURATION**

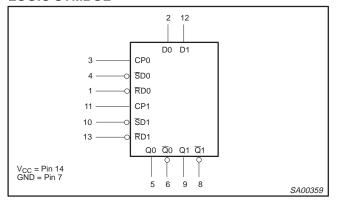

### **LOGIC SYMBOL**

### **DESCRIPTION**

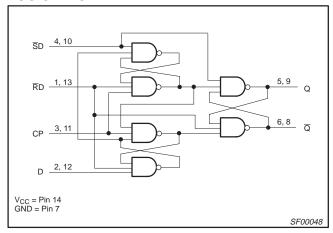

The 74LVT74 is a dual positive edge-triggered D-type flip-flop featuring individual data, clock, set, and reset inputs; also true and complementary outputs. Set (\$\overline{S}D\$) and reset (\$\overline{R}D\$) are asynchronous active low inputs and operate independently of the clock input. When set and reset are inactive (high), data at the D input is transferred to the Q and \$\overline{Q}\$ outputs on the low-to-high transition of the clock. Data must be stable just one setup time prior to the low-to-high transition of the clock for predictable operation. Clock triggering occurs at a voltage level and is not directly related to the transition time of the positive-going pulse. Following the hold time interval, data at the D input may be changed without affecting the levels of the output.

### **PIN DESCRIPTION**

| PIN NUMBER | SYMBOL   | NAME AND FUNCTION                 |

|------------|----------|-----------------------------------|

| 2, 12      | D0, D1   | Data inputs                       |

| 3, 11      | CP0, CP1 | Clock inputs (active rising edge) |

| 4, 10      | SD0, SD1 | Set inputs (active LOW)           |

| 1, 13      | RD0, RD1 | Reset inputs (active LOW)         |

| 5, 6, 8, 9 | Qn, Qn   | Data outputs                      |

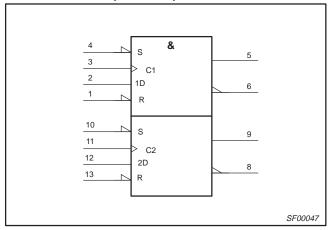

### LOGIC SYMBOL (IEEE/IEC)

### **ORDERING INFORMATION**

| PACKAGES             | TEMPERATURE RANGE | OUTSIDE NORTH AMERICA | NORTH AMERICA | DWG NUMBER |

|----------------------|-------------------|-----------------------|---------------|------------|

| 14-Pin Plastic SO    | -40°C to +85°C    | 74LVT74 D             | 74LVT74 D     | SOT108-1   |

| 14-Pin Plastic SSOP  | -40°C to +85°C    | 74LVT74 DB            | 74LVT74 DB    | SOT337-1   |

| 14-Pin Plastic TSSOP | –40°C to +85°C    | 74LVT74 PW            | 74LVT74PW DH  | SOT402-1   |

# 3.3V Dual D-type flip-flop

74LVT74

### LOGIC DIAGRAM

### **FUNCTION TABLE**

|    | INP | JTS |   | OUTF | PUTS | OPERATING          |

|----|-----|-----|---|------|------|--------------------|

| SD | RD  | СР  | D | Q    | Q    | MODE               |

| L  | Н   | Х   | Х | Н    | L    | Asynchronous set   |

| Н  | L   | Х   | Х | L    | Н    | Asynchronous reset |

| L  | L   | Х   | Х | Н    | Н    | Undetermined*      |

| Н  | Н   | 1   | h | Н    | L    | Load "1"           |

| Н  | Н   | 1   | I | L    | Н    | Load "0"           |

| Н  | Н   | 1   | Х | NC   | NC   | Hold               |

### NOTES:

H = High voltage level

High voltage level one setup time prior to low-to-high clock transition

Low voltage level

Low voltage level one setup time prior to low-to-high clock transition

No change from the previous setup

Don't care

Low-to-high clock transition

Not low-to-high clock transition

This setup is unstable and will change when either set or reset return to the high level.

### **ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>**

| SYMBOL           | PARAMETER                      | CONDITIONS                  | RATING       | UNIT  |  |

|------------------|--------------------------------|-----------------------------|--------------|-------|--|

| V <sub>CC</sub>  | DC supply voltage              |                             | -0.5 to +4.6 | V     |  |

| I <sub>IK</sub>  | DC input diode current         | V <sub>I</sub> < 0          | -50          | mA    |  |

| VI               | DC input voltage <sup>3</sup>  |                             | -0.5 to +7.0 | V     |  |

| I <sub>OK</sub>  | DC output diode current        | V <sub>O</sub> < 0          | -50          | mA    |  |

| V <sub>OUT</sub> | DC output voltage <sup>3</sup> | Output in Off or High state | -0.5 to +7.0 | V     |  |

| lau-             | DC output current              | Output in High state        | -32          | mA    |  |

| OUT              | Do output current              | Output in Low state         | 64           | 111/4 |  |

| T <sub>stg</sub> | Storage temperature range      |                             | -65 to 150   | °C    |  |

- 1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

- 3. The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed.

### RECOMMENDED OPERATING CONDITIONS

| SYMBOL           | PARAMETER                                           | LIM | UNIT |      |  |

|------------------|-----------------------------------------------------|-----|------|------|--|

| STWIBOL          | FARAMETER                                           | MIN | MAX  |      |  |

| V <sub>CC</sub>  | DC supply voltage                                   | 2.7 | 3.6  | V    |  |

| V <sub>I</sub>   | Input voltage                                       |     | 5.5  | V    |  |

| V <sub>IH</sub>  | High-level input voltage                            |     |      | V    |  |

| V <sub>IL</sub>  | Low-level Input voltage                             |     | 0.8  | V    |  |

| I <sub>OH</sub>  | High-level output current                           |     | -20  | mA   |  |

| I <sub>OL</sub>  | Low-level output current                            |     | 32   | mA   |  |

| Δt/Δν            | Input transition rise or fall rate; Outputs enabled |     | 10   | ns/V |  |

| T <sub>amb</sub> | Operating free-air temperature range                | -40 | +85  | °C   |  |

1996 Aug 28

# 3.3V Dual D-type flip-flop

74LVT74

### DC ELECTRICAL CHARACTERISTICS

Over recommended operating conditions Voltages are referenced to GND (ground = 0V)

|                  |                                                      |                                                                                     | ı                    |                  |      |    |  |

|------------------|------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------|------------------|------|----|--|

| SYMBOL           | PARAMETER                                            | TEST CONDITIONS                                                                     | Temp = -             | UNIT             |      |    |  |

|                  |                                                      |                                                                                     | MIN                  | TYP <sup>1</sup> | MAX  |    |  |

| V <sub>IK</sub>  | Input clamp voltage                                  | $V_{CC} = 2.7V; I_{IK} = -18mA$                                                     |                      |                  | -1.2 | V  |  |

|                  |                                                      | $V_{CC} = 2.7 \text{ to } 3.6V; I_{OH} = -100 \mu\text{A}$                          | V <sub>CC</sub> -0.2 |                  |      |    |  |

| $V_{OH}$         | High-level output voltage                            | $V_{CC} = 2.7V; I_{OH} = -6mA$                                                      | 2.4                  |                  |      | V  |  |

|                  |                                                      | $V_{CC} = 3.0V; I_{OH} = -20mA$                                                     | 2.0                  |                  |      |    |  |

|                  |                                                      | $V_{CC} = 2.7V; I_{OL} = 100\mu A$                                                  |                      |                  | 0.2  | V  |  |

| V <sub>OL</sub>  | Low-level output voltage                             | V <sub>CC</sub> = 2.7V; I <sub>OL</sub> = 24mA                                      |                      |                  | 0.5  |    |  |

|                  |                                                      | $V_{CC} = 3.0V; I_{OL} = 32mA$                                                      |                      |                  | 0.5  |    |  |

| l.               | Input leakage current                                | $V_{CC} = 0 \text{ or } 3.6V; V_{I} = 5.5V$                                         |                      |                  | 10   | μА |  |

| '1               | input leakage current                                | $V_{CC} = 3.6V$ ; $V_I = V_{CC}$ or GND                                             |                      |                  | ±1   | μΑ |  |

| I <sub>OFF</sub> | Output off current                                   | $V_{CC} = 0V$ ; $V_I$ or $V_O = 0$ to 4.5V                                          |                      |                  | ±100 | μΑ |  |

| I <sub>CC</sub>  | Quiescent supply current                             | $V_{CC}$ = 3.6V; Outputs High, $V_{I}$ = GND or $V_{CC}$ , $I_{O}$ = 0              |                      | 0.5              | 1    | mA |  |

| Δl <sub>CC</sub> | Additional supply current per input pin <sup>2</sup> | $V_{CC}$ = 3V to 3.6V; One input at $V_{CC}$ –0.6V, Other inputs at $V_{CC}$ or GND |                      |                  | 0.2  | μА |  |

| C <sub>I</sub>   | Input capacitance                                    | $V_I = 3V \text{ or } 0$                                                            |                      | 3                |      | pF |  |

### NOTES:

- All typical values are at V<sub>CC</sub> = 3.3V and T<sub>amb</sub> = 25°C.

This is the increase in supply current for each input at the specificed voltage level other than V<sub>CC</sub> or GND.

### **AC CHARACTERISTICS**

GND = 0V;  $t_R = t_F = 2.5 \text{ns}$ ;  $C_L = 50 \text{pF}$ ,  $R_L = 500 \Omega$ ;  $T_{amb} = -40 ^{\circ} \text{C}$  to  $+85 ^{\circ} \text{C}$ .

| SYMBOL                               | PARAMETER                                 | WAVEFORM | $V_{CC}$ = 3.3V $\pm$ 0.3V |                  | V <sub>CC</sub> = 2.7V | UNIT       |     |

|--------------------------------------|-------------------------------------------|----------|----------------------------|------------------|------------------------|------------|-----|

|                                      |                                           |          | MIN                        | TYP <sup>1</sup> | MAX                    | MAX        |     |

| f <sub>MAX</sub>                     | Maximum clock frequency                   | 1        | 150                        | 345              |                        |            | MHz |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>CPn to Qn or Qn      | 1        | 1.0<br>1.0                 | 3.1<br>3.6       | 4.8<br>5.0             | 5.8<br>5.0 | ns  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>SDn, RDn to Qn or Qn | 2        | 1.0<br>1.0                 | 3.1<br>3.0       | 5.0<br>4.4             | 6.2<br>4.8 | ns  |

### **AC SETUP REQUIREMENTS**

|                                          |                                  |          |                | LIMITS       |                        |      |  |  |  |

|------------------------------------------|----------------------------------|----------|----------------|--------------|------------------------|------|--|--|--|

| SYMBOL                                   | PARAMETER                        | WAVEFORM | $V_{CC} = 3.3$ | 3V ± 0.3V    | V <sub>CC</sub> = 2.7V | UNIT |  |  |  |

|                                          |                                  |          | MIN            | TYP          | MIN                    |      |  |  |  |

| t <sub>S</sub> (H)<br>t <sub>S</sub> (L) | Setup time<br>Dn to CPn          | 1        | 1.7<br>1.4     | 0.6<br>0.4   | 1.8<br>1.6             | ns   |  |  |  |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Holdtime<br>Dn to CPn            | 1        | 0.3<br>0       | -0.3<br>-0.6 | 0.3<br>0               | ne   |  |  |  |

| t <sub>W</sub> (H)<br>t <sub>W</sub> (L) | CPn Pulse Width                  | 1        | 2.0<br>2.0     | 1.0<br>1.2   | 3.0<br>3.0             | ns   |  |  |  |

| t <sub>W</sub> (L)                       | SDn, RDn Pulse Width             | 2        | 2.0            | 1.0          | 3.0                    |      |  |  |  |

| t <sub>rec</sub>                         | Recovery time<br>SDn, RDn tp CPn | 3        | 0.5            | -0.3         | 0.5                    | ns   |  |  |  |

1996 Aug 28

<sup>1.</sup> All typical values are at  $V_{CC}$  = 3.3V and  $T_{amb}$  = 25°C.

# 3.3V Dual D-type flip-flop

74LVT74

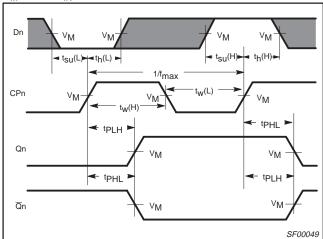

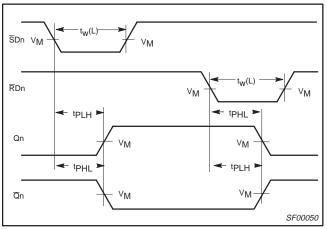

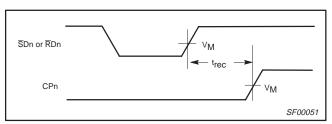

### **AC WAVEFORMS**

$V_{M} = 1.5V, V_{IN} = GND \text{ to } 2.7V$

Waveform 1. Propagation delay for data to output, data setup time and hold times, and clock width, and maximum clock frequency

Waveform 2. Propagation delay for set and reset to output, set and reset pulse width

Waveform 3. Recovery time for set or reset to clock

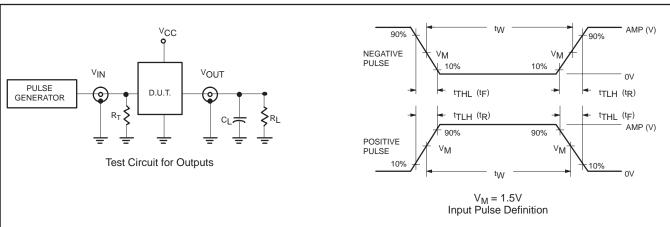

### **TEST CIRCUIT AND WAVEFORMS**

### **DEFINITIONS**

R<sub>L</sub> = Load resistor; see AC CHARACTERISTICS for value.

$C_L = Load$  capacitance includes jig and probe capacitance; see AC CHARACTERISTICS for value.

$\label{eq:RT} \begin{aligned} R_T = & & \text{Termination resistance should be equal to } Z_{OUT} \text{ of } \\ & & \text{pulse generators.} \end{aligned}$

| FAMILY | INPUT PULSE REQUIREMENTS |           |                |                |                |  |  |  |  |

|--------|--------------------------|-----------|----------------|----------------|----------------|--|--|--|--|

|        | Amplitude                | Rep. Rate | t <sub>W</sub> | t <sub>R</sub> | t <sub>F</sub> |  |  |  |  |

| 74LVT  | 2.7V                     | ≤10MHz    | 500ns          | ≤2.5ns         | ≤2.5ns         |  |  |  |  |

SV00022

1996 Aug 28 5

# 3.3V Dual D-type flip-flop

**74LVT74**

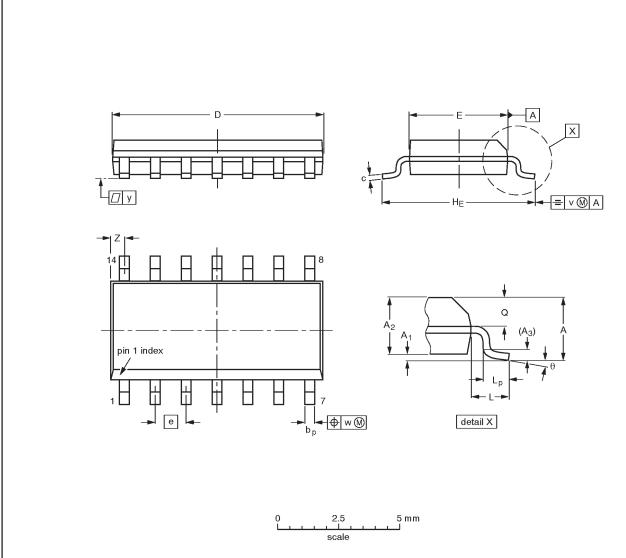

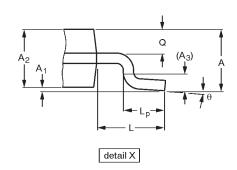

### SO14: plastic small outline package; 14 leads; body width 3.9 mm

SOT108-1

### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | Α1               | A <sub>2</sub> | <b>A</b> <sub>3</sub> | bp           | С                | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE           | L     | Lp             | Ø          | v    | w    | у     | Z <sup>(1)</sup> | θ  |

|--------|-----------|------------------|----------------|-----------------------|--------------|------------------|------------------|------------------|-------|--------------|-------|----------------|------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10     | 1.45<br>1.25   | 0.25                  | 0.49<br>0.36 | 0.25<br>0.19     | 8.75<br>8.55     | 4.0<br>3.8       | 1.27  | 6.2<br>5.8   | 1.05  | 1.0<br>0.4     | 0.7<br>0.6 | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.0098<br>0.0039 | 0.057<br>0.049 | 0.01                  |              | 0.0098<br>0.0075 | 0.35<br>0.34     | 0.16<br>0.15     | 0.050 | 0.24<br>0.23 | 0.041 | 0.039<br>0.016 |            | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

### Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  |          | REFER    | EUROPEAN | ISSUE DATE |                                 |   |

|----------|----------|----------|----------|------------|---------------------------------|---|

| VERSION  | IEC      | JEDEC    | EIAJ     | PROJECTION | ISSUE DATE                      | l |

| SOT108-1 | 076E06\$ | MS-012AB |          |            | <del>91-08-13</del><br>95-01-23 |   |

1996 Aug 28 6

# 3.3V Dual D-type flip-flop

74LVT74

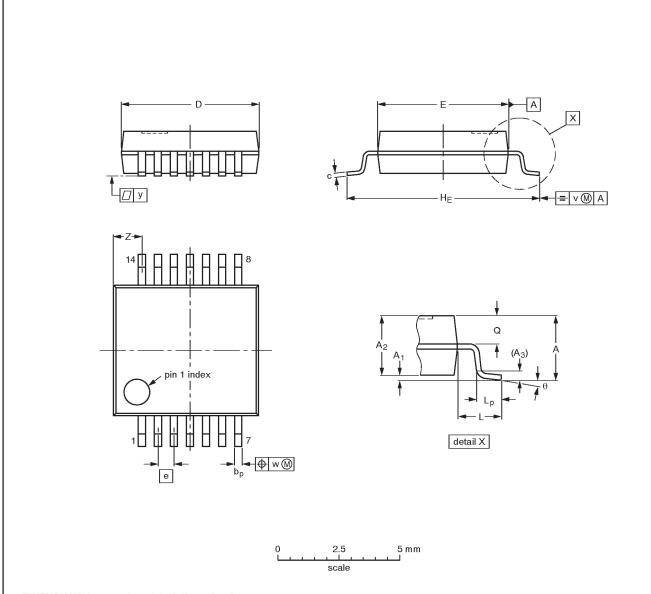

SSOP14: plastic shrink small outline package; 14 leads; body width 5.3 mm

SOT337-1

### DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | <b>A</b> <sub>3</sub> | bp           | C            | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | HE         | L    | Lp           | ø          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|-----------------------|--------------|--------------|------------------|------------------|------|------------|------|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 2.0       | 0.21<br>0.05   | 1.80<br>1.65   | 0.25                  | 0.38<br>0.25 | 0.20<br>0.09 | 6.4<br>6.0       | 5.4<br>5.2       | 0.65 | 7.9<br>7.6 | 1.25 | 1.03<br>0.63 | 0.9<br>0.7 | 0.2 | 0.13 | 0.1 | 1.4<br>0.9       | 8°<br>0° |

### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER    | EUROPEAN | ISSUE DATE |            |                                  |  |

|----------|-----|----------|----------|------------|------------|----------------------------------|--|

| VERSION  | IEC | JEDEC    | EIAJ     |            | PROJECTION | 1550E DATE                       |  |

| SOT337-1 |     | MO-150AB |          |            |            | <del>-95-02-04</del><br>96-01-18 |  |

1996 Aug 28 7

# 3.3V Dual D-type flip-flop

74LVT74

TSSOP14: plastic thin shrink small outline package; 14 leads; body width 4.4 mm

SOT402-1

### DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | Α1           | A <sub>2</sub> | A <sub>3</sub> | bр           | c          | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE         | L   | Lp           | Q          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|--------------|----------------|----------------|--------------|------------|------------------|------------------|------|------------|-----|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 1.10      | 0.15<br>0.05 | 0.95<br>0.80   | 0.25           | 0.30<br>0.19 | 0.2<br>0.1 | 5.1<br>4.9       | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1.0 | 0.75<br>0.50 | 0.4<br>0.3 | 0.2 | 0.13 | 0.1 | 0.72<br>0.38     | 8°<br>0° |

### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

|         | OUTLINE  |     | REFER  | EUROPEAN | ISSUE DATE |            |                                 |  |

|---------|----------|-----|--------|----------|------------|------------|---------------------------------|--|

| VERSION |          | IEC | JEDEC  | EIAJ     |            | PROJECTION | ISSUE DATE                      |  |

|         | SOT402-1 |     | MO-153 |          |            |            | <del>94-07-12</del><br>95-04-04 |  |

1996 Aug 28

# 3.3V Dual D-type flip-flop

74LVT74

**NOTES**

1996 Aug 28

9

## 3.3V Dual D-type flip-flop

74LVT74

|                           | DEFINITIONS            |                                                                                                                                                                                                                                                            |  |  |  |  |  |

|---------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Data Sheet Identification | Product Status         | Definition                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Objective Specification   | Formative or in Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                                         |  |  |  |  |  |

| Preliminary Specification | Preproduction Product  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |  |  |  |  |  |

| Product Specification     | Full Production        | This data sheet contains Final Specifications. Philips Semiconductors reserves the right to make changes at any time without notice, in order to improve design and supply the best possible product.                                                      |  |  |  |  |  |

Philips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

### LIFE SUPPORT APPLICATIONS

Philips Semiconductors and Philips Electronics North America Corporation Products are not designed for use in life support appliances, devices, or systems where malfunction of a Philips Semiconductors and Philips Electronics North America Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North America Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from such improper use or sale.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 Philips Semiconductors and Philips Electronics North America Corporation register eligible circuits under the Semiconductor Chip Protection Act.

© Copyright Philips Electronics North America Corporation 1996

All rights reserved. Printed in U.S.A.