### INTEGRATED CIRCUITS

# DATA SHEET

### 74ABT16374B 74ABTH16374B

16-bit D-type flip-flop; positive-edge trigger (3-State)

Product specification Supersedes data of 1995 Sep 28 IC23 Data Handbook

## 16-bit D-type flip-flop; positive-edge trigger (3-State)

### 74ABT16374B 74ABTH16374B

#### **FEATURES**

- Two 8-bit positive edge triggered registers

- Live insertion/extraction permitted

- Power-up 3-State

- Power-up reset

- Multiple V<sub>CC</sub> and GND pins minimize switching noise

- 3-State output buffers

- 74ABTH16373B incorporates bus-hold data inputs which eliminate the need for external pull-up resistors to hold unused inputs

- Bus-hold data inputs eliminate the need for external pull-up resistors to hold unused inputs

- Output capability: +64mA/-32mA

- Latch-up protection exceeds 500mA per JEDEC Std 17

- ESD protection exceeds 2000V per MIL STD 883 Method 3015 and 200V per Machine Model

#### **DESCRIPTION**

The 74ABT16374B high-performance BiCMOS device combines low static and dynamic power dissipation with high speed and high output drive.

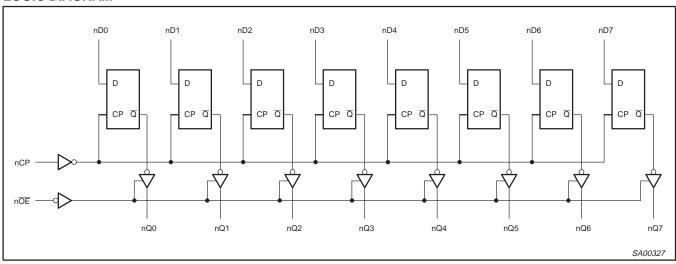

The 74ABT16374B has two 8-bit, edge triggered registers, with each register coupled to eight 3-State output buffers. The two sections of each register are controlled independently by the clock (nCP) and Output Enable ( $\overline{\text{NOE}}$ ) control gates.

Each register is fully edge triggered. The state of each D input, one set-up time before the Low-to-High clock transition, is transferred to the corresponding flip-flop's Q output.

The 3-State output buffers are designed to drive heavily loaded 3-State buses, MOS memories, or MOS microprocessors. Each active-Low Output Enable (nOE) controls all eight 3-State buffers for its register independent of the clock operation.

When nOE is Low, the stored data appears at the outputs for that register. When nOE is High, the outputs for that register are in the High-impedance "OFF" state, which means they will neither drive nor load the bus.

Two options are available, 74ABT16374B which does not have the bus-hold feature and 74ABTH16374B which incorporates the bus-hold feature.

#### **QUICK REFERENCE DATA**

| SYMBOL                               | PARAMETER                    | CONDITIONS<br>T <sub>amb</sub> = 25°C; GND = 0V | TYPICAL    | UNIT |

|--------------------------------------|------------------------------|-------------------------------------------------|------------|------|

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay nCP to nQx | $C_L = 50pF; V_{CC} = 5V$                       | 2.6<br>2.2 | ns   |

| C <sub>IN</sub>                      | Input capacitance            | $V_I = 0V \text{ or } V_{CC}$                   | 4          | pF   |

| C <sub>OUT</sub>                     | Output capacitance           | $V_O = 0V$ or $V_{CC}$ ; 3-State                | 7          | pF   |

| I <sub>CCZ</sub>                     | Quiescent supply current     | Outputs disabled; V <sub>CC</sub> = 5.5V        | 500        | μΑ   |

| Iccl                                 | Quicocont supply current     | Outputs Low; V <sub>CC</sub> = 5.5V             | 8          | mA   |

#### ORDERING INFORMATION

| ONDERNING INI ORMATION       |                   |                       |               |            |

|------------------------------|-------------------|-----------------------|---------------|------------|

| PACKAGES                     | TEMPERATURE RANGE | OUTSIDE NORTH AMERICA | NORTH AMERICA | DWG NUMBER |

| 48-Pin Plastic SSOP Type III | -40°C to +85°C    | 74ABT16374B DL        | BT16374B DL   | SOT370-1   |

| 48-Pin Plastic TSSOP Type II | -40°C to +85°C    | 74ABT16374B DGG       | BT16374B DGG  | SOT362-1   |

| 48-Pin Plastic SSOP Type III | -40°C to +85°C    | 74ABTH16374B DL       | BH16374B DL   | SOT370-1   |

| 48-Pin Plastic TSSOP Type II | -40°C to +85°C    | 74ABTH16374B DGG      | BH16374B DGG  | SOT362-1   |

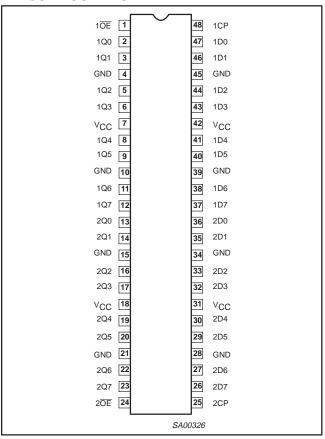

#### PIN DESCRIPTION

| PIN NUMBER                                                       | SYMBOL                            | FUNCTION                                |  |  |

|------------------------------------------------------------------|-----------------------------------|-----------------------------------------|--|--|

| 47, 46, 44, 43, 41, 40, 38, 37<br>36, 35, 33, 32, 30, 29, 27, 26 | 1D0 – 1D7<br>2D0 – 2D7            | Data inputs                             |  |  |

| 2, 3, 5, 6, 8, 9, 11, 12<br>13, 14, 16, 17, 19, 20, 22, 23       | 1Q0 – 1Q7<br>2Q0 – 2Q7            | Data outputs                            |  |  |

| 1, 24                                                            | 1 <del>0E</del> , 2 <del>0E</del> | Output enable inputs (active-Low)       |  |  |

| 48, 25                                                           | 1CP, 2CP                          | Clock pulse inputs (active rising edge) |  |  |

| 4, 10, 15, 21, 28, 34, 39, 45                                    | GND                               | Ground (0V)                             |  |  |

| 7, 18, 31, 42                                                    | V <sub>CC</sub>                   | Positive supply voltage                 |  |  |

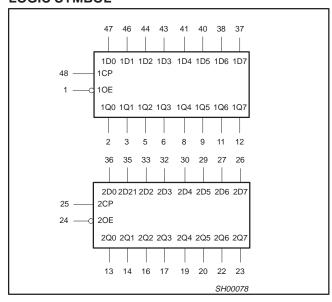

#### LOGIC SYMBOL

## 16-bit D-type flip-flop; positive-edge trigger (3-State)

74ABT16374B 74ABTH16374B

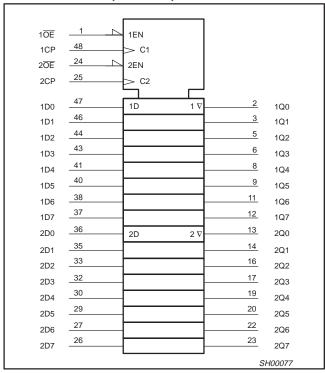

#### LOGIC SYMBOL (IEEE/IEC)

#### **PIN CONFIGURATION**

#### **LOGIC DIAGRAM**

## 16-bit D-type flip-flop; positive-edge trigger (3-State)

74ABT16374B 74ABTH16374B

#### **FUNCTION TABLE**

|        | INPUTS   |          | INTERNAL  | OUTPUTS   | OPERATING MODE         |  |  |

|--------|----------|----------|-----------|-----------|------------------------|--|--|

| nOE    | nCP      | nDx      | REGISTER  | nQ0 – nQ7 | OFERATING MODE         |  |  |

| L<br>L | <b>↑</b> | l<br>h   | L<br>H    | L<br>H    | Load and read register |  |  |

| L      | 1        | Х        | NC        | NC        | Hold                   |  |  |

| H<br>H | <u></u>  | X<br>nDx | NC<br>nDx | Z<br>Z    | Disable outputs        |  |  |

H = High voltage level

h = High voltage level one set-up time prior to the High-to-Low E transition

Low voltage level

= Low voltage level one set-up time prior to the High-to-Low E transition

NC= No change

X = Don't care

Z = High impedance "off" state

↑ = Low-to-High clock transition ↑ = Not a Low-to-High clock transition

### **ABSOLUTE MAXIMUM RATINGS<sup>1, 2</sup>**

| SYMBOL           | PARAMETER                      | CONDITIONS                  | RATING       | UNIT |  |

|------------------|--------------------------------|-----------------------------|--------------|------|--|

| V <sub>CC</sub>  | DC supply voltage              |                             | -0.5 to +7.0 | V    |  |

| I <sub>IK</sub>  | DC input diode current         | V <sub>I</sub> < 0          | -18          | mA   |  |

| V <sub>I</sub>   | DC input voltage <sup>3</sup>  |                             | -1.2 to +7.0 | V    |  |

| l <sub>ok</sub>  | DC output diode current        | V <sub>O</sub> < 0          | -50          | mA   |  |

| V <sub>OUT</sub> | DC output voltage <sup>3</sup> | output in Off or High state | −0.5 to +5.5 | V    |  |

|                  | DC output ourrent              | output in Low state         | 128          | A    |  |

| IOUT             | DC output current              | output in High state        | -64          | mA   |  |

| T <sub>stg</sub> | Storage temperature range      |                             | -65 to 150   | °C   |  |

#### NOTES:

- 1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150°C.

3. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL           | PARAMETER                            | LIM | UNIT            |      |

|------------------|--------------------------------------|-----|-----------------|------|

| STIMBUL          | PARAMETER                            | MIN | MAX             | UNII |

| V <sub>CC</sub>  | DC supply voltage                    | 4.5 | 5.5             | V    |

| V <sub>I</sub>   | Input voltage                        | 0   | V <sub>CC</sub> | V    |

| V <sub>IH</sub>  | High-level input voltage             | 2.0 |                 | V    |

| $V_{IL}$         | Low-level Input voltage              |     | 0.8             | V    |

| I <sub>OH</sub>  | High-level output current            |     | -32             | mA   |

| I <sub>OL</sub>  | Low-level output current             |     | 64              | mA   |

| Δt/Δν            | Input transition rise or fall rate   | 0   | 10              | ns/V |

| T <sub>amb</sub> | Operating free-air temperature range | -40 | +85             | °C   |

### 16-bit D-type flip-flop; positive-edge trigger (3-State)

74ABT16374B 74ABTH16374B

#### DC ELECTRICAL CHARACTERISTICS

|                                                 |                                                                   |                                                                            |                                         | LIMITS |                     |      |                    |                 |          |  |

|-------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------|--------|---------------------|------|--------------------|-----------------|----------|--|

| SYMBOL                                          | PARAMETER                                                         | TEST CONDITIO                                                              | NS                                      | Ta     | <sub>mb</sub> = +25 | 5°C  | T <sub>amb</sub> = | : –40°C<br>85°C | UNIT     |  |

|                                                 |                                                                   |                                                                            |                                         | MIN    | TYP                 | MAX  | MIN                | MAX             | 1        |  |

| V <sub>IK</sub>                                 | Input clamp voltage                                               | $V_{CC} = 4.5V; I_{IK} = -18mA$                                            |                                         |        | -0.9                | -1.2 |                    | -1.2            | V        |  |

|                                                 |                                                                   | $V_{CC} = 4.5V; I_{OH} = -3mA; V_{I} =$                                    | = V <sub>IL</sub> or V <sub>IH</sub>    | 2.5    | 2.9                 |      | 2.5                |                 |          |  |

| $V_{OH}$                                        | High-level output voltage                                         | $V_{CC} = 5.0V; I_{OH} = -3mA; V_{I} =$                                    | = V <sub>IL</sub> or V <sub>IH</sub>    | 3.0    | 3.4                 |      | 3.0                |                 | V        |  |

|                                                 |                                                                   | $V_{CC} = 4.5V; I_{OH} = -32mA; V_{I}$                                     | 2.0                                     | 2.4    |                     | 2.0  |                    |                 |          |  |

| V <sub>OL</sub>                                 | Low-level output voltage                                          | $V_{CC} = 4.5V; I_{OL} = 64mA; V_{I} =$                                    |                                         | 0.42   | 0.55                |      | 0.55               | V               |          |  |

| V <sub>RST</sub>                                | Power-up output voltage <sup>3</sup>                              | $V_{CC} = 5.5V; I_{O} = 1mA; V_{I} = 0$                                    | SND or V <sub>CC</sub>                  |        | 0.13                | 0.55 |                    | 0.55            | V        |  |

| I <sub>I</sub>                                  | Input leakage current<br>74ABT16374B                              | $V_{CC} = 5.5V$ ; $V_I = V_{CC}$ or GNE                                    | $V_{CC} = 5.5V$ ; $V_I = V_{CC}$ or GND |        | 0.01                | ±1   |                    | ±1              | μΑ       |  |

|                                                 | Input leakage current                                             | $V_{CC}$ = 5.5V; $V_I$ = $V_{CC}$ or GND                                   | Control pins                            |        | ±0.01               | ±1   |                    | ±1              |          |  |

| II                                              | 74ABTH16374B                                                      | $V_{CC} = 5.5V$ ; $V_I = V_{CC}$                                           | D-1                                     |        | 0.01                | 1    |                    | 1               | μΑ       |  |

|                                                 |                                                                   | $V_{CC} = 5.5V; V_I = 0$                                                   | Data pins <sup>5</sup>                  |        | -1                  | -3   |                    | -5              |          |  |

|                                                 |                                                                   | $V_{CC} = 4.5V; V_I = 0.8V$                                                |                                         | 50     |                     |      | 50                 |                 |          |  |

| I <sub>HOLD</sub> Bus Hold current 74ABTH16374B | Bus Hold current inputs <sup>6</sup><br>74ABTH16374B              | V <sub>CC</sub> = 4.5V; V <sub>I</sub> = 2.0V                              | -75                                     |        |                     | -75  |                    | μΑ              |          |  |

|                                                 |                                                                   | $V_{CC} = 5.5V$ ; $V_I = 0$ to 5.5V                                        |                                         | ±800   |                     |      |                    |                 | <u> </u> |  |

| $I_{OFF}$                                       | Power-off leakage current                                         | $V_{CC} = 0.0V; V_{O} \text{ or } V_{I} \le 4.5V$                          |                                         |        | ±5.0                | ±100 |                    | ±100            | μΑ       |  |

| I <sub>PU/PD</sub>                              | Power-up/down 3-State output current <sup>4</sup>                 | $V_{CC} = 2.1V; V_{O} = 0.5V; V_{I} = GND \text{ or } V_{CC}; V_{OE} = GN$ | D                                       |        | ±5.0                | ±50  |                    | ±50             | μΑ       |  |

| I <sub>OZH</sub>                                | 3-State output High current                                       | $V_{CC} = 5.5V; V_{O} = 2.7V; V_{I} = V_{CC}$                              | V <sub>IL</sub> or V <sub>IH</sub>      |        | 0.5                 | 10   |                    | 10              | μА       |  |

| $I_{OZL}$                                       | 3-State output Low current                                        | $V_{CC} = 5.5V; V_O = 0.5V; V_I = V_I$                                     | V <sub>IL</sub> or V <sub>IH</sub>      |        | -0.5                | -10  |                    | -10             | μΑ       |  |

| I <sub>CEX</sub>                                | Output High leakage current                                       | $V_{CC} = 5.5V; V_{O} = 5.5V; V_{I} = 0$                                   | GND or V <sub>CC</sub>                  |        | 5.0                 | 50   |                    | 50              | μΑ       |  |

| I <sub>O</sub>                                  | Output current <sup>1</sup>                                       | $V_{CC} = 5.5V; V_{O} = 2.5V$                                              |                                         | -50    | -70                 | -180 | -50                | -180            | mA       |  |

| I <sub>CCH</sub>                                |                                                                   | $V_{CC}$ = 5.5V; Outputs High, $V_{I}$                                     | = GND or V <sub>CC</sub>                |        | 0.5                 | 2    |                    | 2               | mA       |  |

| I <sub>CCL</sub>                                | Quiescent supply current                                          | $V_{CC}$ = 5.5V; Outputs Low, $V_{I}$                                      | = GND or V <sub>CC</sub>                |        | 8                   | 19   |                    | 19              | mA       |  |

| I <sub>CCZ</sub>                                |                                                                   | $V_{CC}$ = 5.5V; Outputs 3-State; $V_I$ = GND or $V_{CC}$                  |                                         | 0.5    | 2                   |      | 2                  | mA              |          |  |

| Δl <sub>CC</sub>                                | Additional supply current per input pin <sup>2</sup> 74ABT16374B  | V <sub>CC</sub> = 5.5V; one input at 3.4V,<br>V <sub>CC</sub> or GND       |                                         | 5      | 100                 |      | 100                | μА              |          |  |

| Δl <sub>CC</sub>                                | Additional supply current per input pin <sup>2</sup> 74ABTH16374B | $V_{CC}$ = 5.5V; one input at 3.4V, $V_{CC}$ or GND                        | other inputs at                         |        | 0.5                 | 1.5  |                    | 1.5             | mA       |  |

- 1. Not more than one output should be tested at a time, and the duration of the test should not exceed one second.

- This is the increase in supply current for each input at 3.4V.

For valid test results, data must not be loaded into the flip-flops (or latches) after applying the power.

This parameter is valid for any V<sub>CC</sub> between 0V and 2.1V with a transition time of up to 10msec. From V<sub>CC</sub> = 2.1V to V<sub>CC</sub> = 5V ± 10% a transition time of up to 100μsec is permitted.

5. Unused pins at V<sub>CC</sub> or GND.

- 6. This is the bus hold overdrive current required to force the input to the opposite logic state.

#### **AC CHARACTERISTICS**

GND = 0V,  $t_R$  =  $t_F$  = 2.5ns,  $C_L$  = 50pF,  $R_L$  = 500 $\Omega$

| SYMBOL                               | PARAMETER                                   | WAVEFORM | T <sub>2</sub> | <sub>amb</sub> = +25°<br>CC = +5.0 | ℃<br>V     | $T_{amb} = -40$ $V_{CC} = +5$ | UNIT       |     |

|--------------------------------------|---------------------------------------------|----------|----------------|------------------------------------|------------|-------------------------------|------------|-----|

|                                      |                                             |          | MIN            | TYP                                | MAX        | MIN                           | MAX        |     |

| f <sub>MAX</sub>                     | Maximum clock frequency                     | 1        | 180            | 260                                |            |                               |            | MHz |

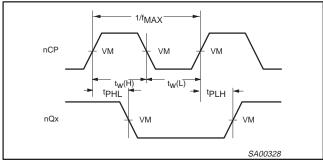

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay<br>nCP to nQx             | 1        | 1.7<br>1.4     | 2.6<br>2.2                         | 4.0<br>3.4 | 1.7<br>1.4                    | 4.7<br>3.9 | ns  |

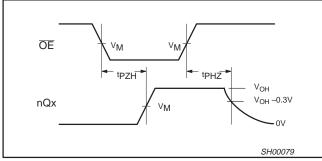

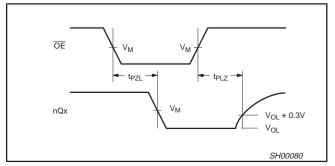

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output enable time to High and Low level    | 3<br>4   | 1.3<br>1.3     | 2.4<br>2.3                         | 3.7<br>3.4 | 1.3<br>1.3                    | 4.7<br>4.6 | ns  |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output disable time from High and Low level | 3<br>4   | 1.9<br>1.7     | 3.1<br>2.6                         | 4.6<br>4.0 | 1.9<br>1.7                    | 5.5<br>4.4 | ns  |

#### **AC SETUP REQUIREMENTS**

GND = 0V,  $t_R$  =  $t_F$  = 2.5ns,  $C_L$  = 50pF,  $R_L$  = 500 $\Omega$

| SYMBOL                                   | PARAMETER                             | WAVEFORM | T <sub>amb</sub> = V <sub>CC</sub> = | +25°C<br>+5.0V | $T_{amb}$ = -40 to +85°C $V_{CC}$ = +5.0V $\pm$ 0.5V | UNIT |

|------------------------------------------|---------------------------------------|----------|--------------------------------------|----------------|------------------------------------------------------|------|

|                                          |                                       |          | MIN                                  | TYP            | MIN                                                  | 1    |

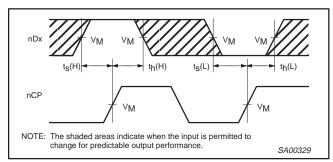

| t <sub>S</sub> (H)<br>t <sub>S</sub> (L) | Setup time, High or Low<br>nDx to nCP | 2        | 1.0<br>1.0                           | 0.3<br>0.1     | 1.0<br>1.0                                           | ns   |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold time, High or Low<br>nDx to nCP  | 2        | 1.0<br>1.0                           | -0.1<br>-0.3   | 1.0<br>1.0                                           | ns   |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | nCP pulse width<br>High or Low        | 1        | 2.8<br>2.8                           | 1.2<br>1.5     | 2.8<br>2.8                                           | ns   |

#### **AC WAVEFORMS**

$V_{M} = 1.5V, V_{IN} = GND \text{ to } 3.0V$

Waveform 1. Propagation Delay, Clock Input to Output, Clock Pulse Width, and Maximum Clock Frequency

Waveform 2. Data Setup and Hold Times

1998 Feb 27 6

## 16-bit D-type flip-flop; positive-edge trigger (3-State)

74ABT16374B 74ABTH16374B

Waveform 3. 3-State Output Enable Time to High Level and Output Disable Time from High Level

Waveform 4. 3-State Output Enable Time to Low Level and Output Disable Time from Low Level

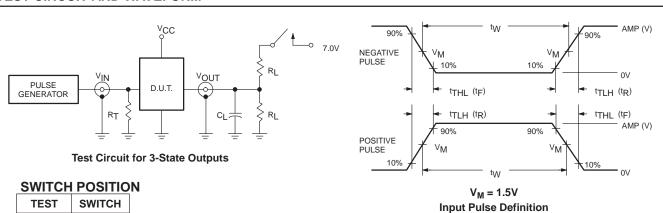

#### **TEST CIRCUIT AND WAVEFORM**

| TEST             | SWITCH |

|------------------|--------|

| t <sub>PLZ</sub> | closed |

| t <sub>PZL</sub> | closed |

| All other        | open   |

#### **DEFINITIONS**

$R_L$  = Load resistor; see AC CHARACTERISTICS for value.

$C_L = Load$  capacitance includes jig and probe capacitance; see AC CHARACTERISTICS for value.

| FAMILY    | IN        | INPUT PULSE REQUIREMENTS |                |                |                |  |  |  |  |  |  |

|-----------|-----------|--------------------------|----------------|----------------|----------------|--|--|--|--|--|--|

| FAMILI    | Amplitude | Rep. Rate                | t <sub>W</sub> | t <sub>R</sub> | t <sub>F</sub> |  |  |  |  |  |  |

| 74ABT/H16 | 3.0V      | 1MHz                     | 500ns          | 2.5ns          | 2.5ns          |  |  |  |  |  |  |

SA00018

Dual octal D-type flip-flop; positive-edge trigger (3-State)

74ABT16374B 74ABTH16374B

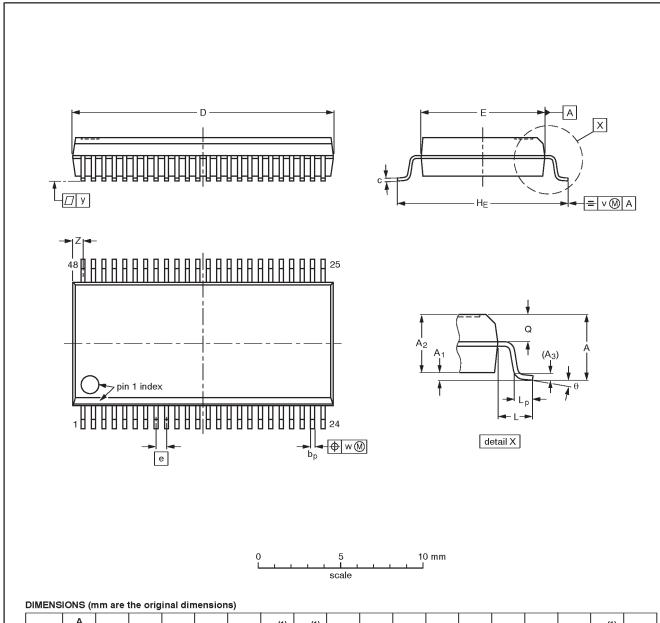

#### SSOP48: plastic shrink small outline package; 48 leads; body width 7.5 mm

SOT370-1

| UNIT | A<br>max. | Α1         | A <sub>2</sub> | <b>A</b> <sub>3</sub> | bp         | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE           | L   | Lp         | Q          | v    | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|------------|----------------|-----------------------|------------|--------------|------------------|------------------|-------|--------------|-----|------------|------------|------|------|-----|------------------|----------|

| mm   | 2.8       | 0.4<br>0.2 | 2.35<br>2.20   | 0.25                  | 0.3<br>0.2 | 0.22<br>0.13 | 16.00<br>15.75   | 7.6<br>7.4       | 0.635 | 10.4<br>10.1 | 1.4 | 1.0<br>0.6 | 1.2<br>1.0 | 0.25 | 0.18 | 0.1 | 0.85<br>0.40     | 8°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER    | EUROPEAN | ISSUE DATE |            |                                 |

|----------|-----|----------|----------|------------|------------|---------------------------------|

| VERSION  | IEC | JEDEC    | EIAJ     |            | PROJECTION | ISSUE DATE                      |

| SOT370-1 |     | MO-118AA |          |            |            | <del>93-11-02</del><br>95-02-04 |

Dual octal D-type flip-flop; positive-edge trigger (3-State)

74ABT16374B 74ABTH16374B

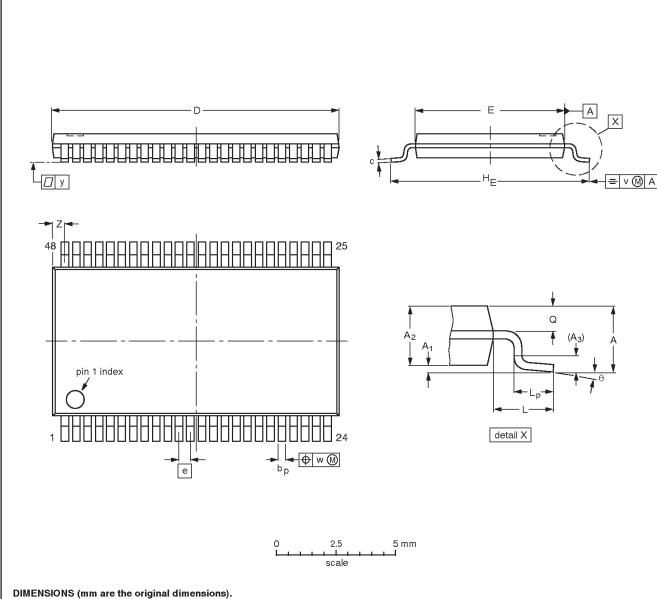

TSSOP48: plastic thin shrink small outline package; 48 leads; body width 6.1mm

SOT362-1

| UNIT | A<br>max. | Α1           | A <sub>2</sub> | А3   | bp           | С          | D <sup>(1)</sup> | E <sup>(2)</sup> | е   | HE         | L | Lp         | Q            | v    | w    | у   | z          | θ        |

|------|-----------|--------------|----------------|------|--------------|------------|------------------|------------------|-----|------------|---|------------|--------------|------|------|-----|------------|----------|

| mm   | 1.2       | 0.15<br>0.05 | 1.05<br>0.85   | 0.25 | 0.28<br>0.17 | 0.2<br>0.1 | 12.6<br>12.4     | 6.2<br>6.0       | 0.5 | 8.3<br>7.9 | 1 | 0.8<br>0.4 | 0.50<br>0.35 | 0.25 | 0.08 | 0.1 | 0.8<br>0.4 | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER    | EUROPEAN | ISSUE DATE |            |                                  |

|----------|-----|----------|----------|------------|------------|----------------------------------|

| VERSION  | IEC | JEDEC    | EIAJ     |            | PROJECTION | ISSUE DATE                       |

| SOT362-1 |     | MO-153ED |          |            |            | <del>-93-02-03</del><br>95-02-10 |

16-bit D-type flip-flop; positive-edge trigger (3-State)

74ABT16374B 74ABTH16374B

#### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                            |

|---------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                         |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make chages at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                      |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1998 All rights reserved. Printed in U.S.A.

print code Date of release: 05-96

Document order number: 9397-750-03492

Let's make things better.

Philips Semiconductors