# INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC04 January 1995

### HEF4750V LSI

#### DESCRIPTION

The HEF4750V frequency synthesizer is one of a pair of LOCMOS devices, primarily intended for use in high-performance frequency synthesizers, e.g. in all communication, instrumentation, television and broadcast applications. A combination of analogue and digital techniques results in an integrated circuit that enables high performance. The complementary device is the universal divider type HEF4751V.

Together with a standard prescaler, the two LOCMOS integrated circuits offer low-cost single loop synthesizers with full professional performance. Salient features offered (in combination with HEF4751V) are:

- Wide choice of reference frequency using a single crystal.

- High-performance phase comparator low phase noise low spurii.

- System operation to > 1 GHz.

- Typical 15 MHz input at 10 V.

- Flexible programming:

- frequency offsets

- **ROM** compatible

- fractional channel capability.

- Programme range 6<sup>1</sup>/<sub>2</sub> decades, including up to 3 decades of prescaler control.

- Division range extension by cascading.

- Built-in phase modulator.

- Fast lock feature.

- Out-of-lock indication.

- Low power dissipation and high noise immunity.

#### **APPLICATION INFORMATION**

Some examples of applications for the HEF4750V in combination with the HEF4751V are:

- VHF/UHF mobile radios.

- HF s.s.b. transceivers.

- Airborne and marine communications and navaids.

- Broadcast transmitters.

- High quality radio and television receivers.

- High performance citizens band equipment.

- Signal generators.

#### SUPPLY VOLTAGE

| RATING      | RECOMMENDED OPERATING |

|-------------|-----------------------|

| -0,5 to +15 | 9,5 to 10,5 V         |

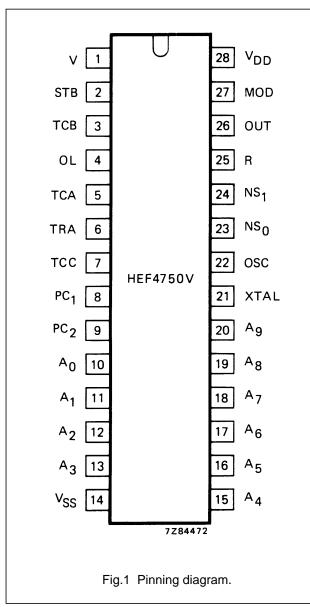

# **HEF4750V** LSI

HEF4750VD(F): 28-lead DIL; ceramic (cerdip) (SOT135)

(): Package Designator North America

| PINNING                           |                                         |

|-----------------------------------|-----------------------------------------|

| R                                 | phase comparator input, reference       |

| V                                 | phase comparator input                  |

| STB                               | strobe input                            |

| TCA                               | timing capacitor C <sub>A</sub> pin     |

| тсв                               | timing capacitor C <sub>B</sub> pin     |

| TCC                               | timing capacitor C <sub>C</sub> pin     |

| TRA                               | biasing pin (resistor R <sub>A</sub> )  |

| PC <sub>1</sub>                   | analogue phase comparator output        |

| PC <sub>2</sub>                   | digital phase comparator output         |

| MOD                               | phase modulation input                  |

| OL                                | out-of-lock indication                  |

| OSC                               | reference oscillator/buffer input       |

| XTAL                              | reference oscillator/buffer output      |

| $A_0$ to $A_9$                    | programming inputs/programmable divider |

| NS <sub>0</sub> , NS <sub>1</sub> | programming inputs, prescaler           |

| OUT                               | reference divider output                |

### HEF4750V LSI

## Frequency synthesizer

#### FUNCTIONAL DESCRIPTION

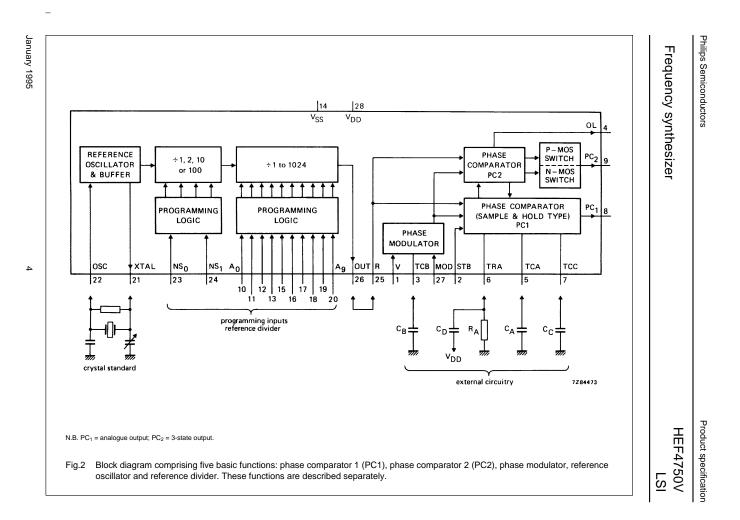

#### Phase comparator 1

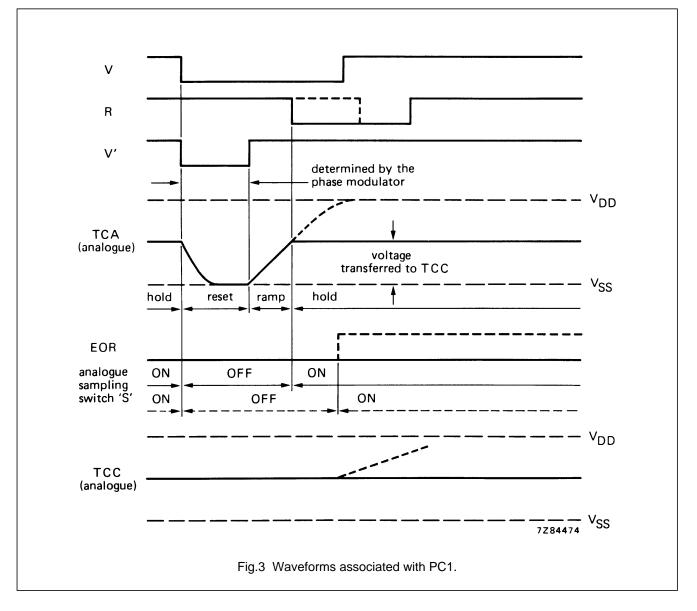

Phase comparator 1 (PC1) is built around a SAMPLE and HOLD circuit. A negative-going transition at the V-input causes the hold capacitor ( $C_A$ ) to be discharged and after a specified delay, caused by the Phase Modulator by means of an internal V' pulse, it produces a positive-going ramp. A negative-going transition at the R-input terminates

the ramp. Capacitor  $C_A$  holds the voltage that the ramp has attained. Via an internal sampling switch this voltage is transferred to  $C_C$  and in turn buffered and made available at output PC<sub>1</sub>.

If the ramp terminates before an R-input is present, an internal end of ramp (EOR) signal is produced.

These actions are illustrated in Fig.3.

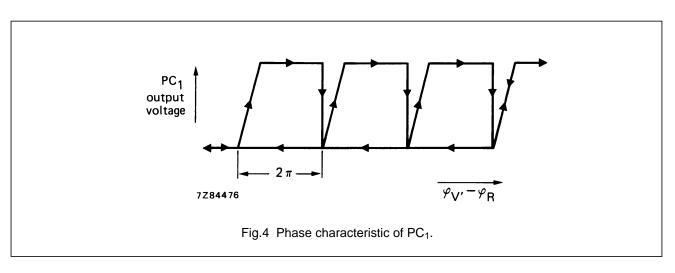

The resultant phase characteristic is shown in Fig.4.

### HEF4750V LSI

PC1 is designed to have a high gain, typically 3200 V/cycle (at 12,5 kHz). This enables a low noise performance.

#### Phase comparator 2

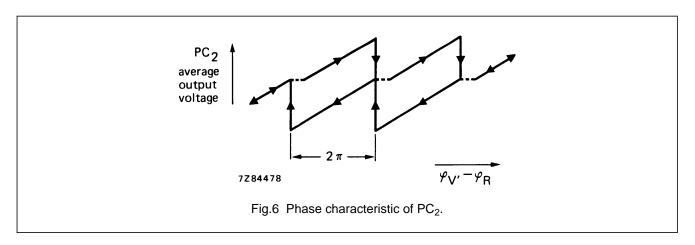

Phase comparator 2 (PC2) has a wide range, which enables faster lock times to be achieved than otherwise would be possible. It has a linear  $\pm$  360° phase range, which corresponds to a gain of typically 5 V/cycle.

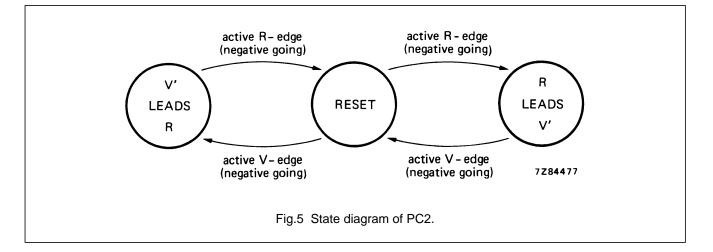

This digital phase comparator has three stable states:

- reset state,

- V' leads R state,

- R leads V' state.

Conversion from one state to another takes place according to the state diagram of Fig.5.

Output PC<sub>2</sub> produces positive or negative-going pulses with variable width; they depend on the phase relationship of R and V'. The average output voltage is a linear function of the phase difference. Output PC<sub>2</sub> remains in the high impedance OFF-state in the region in which PC1 operates. The resultant phase characteristic is shown in Fig.6.

# HEF4750V LSI

#### Strobe function

The strobe function is intended for applications requiring extremely fast lock times. In normal operation the additional strobe input (STB) can be connected to the V-input and the circuit will function as described in the previous sections.

In single, phase-locked-loop type frequency synthesizers, the comparison frequency generally used is either the nominal channel spacing or a sub-multiple. PC2 runs at the higher frequency (a higher reference frequency must also be used), whilst strobing takes place on the lower frequency, thereby obtaining a decrease in lock time. In a system using the Universal Divider HEF4751V, the output OFS cycles on the lower frequency, the output OFF cycles on the higher frequency.

#### **Out-of-lock function**

There are a number of situations in which the system goes from the locked to the out-of-lock state (OL goes HIGH):

- 1. When V' leads R, however out of the range of PC1.

- 2. When R leads V'.

- 3. When an R-pulse is missing.

- 4. When a V-pulse is missing.

- 5. When two successive STB-commands occur, the first without corresponding V-signal.

#### Phase modulator

The phase modulator only uses one external capacitor,  $C_B$  at pin TCB. A negative-going transition at the V-input causes  $C_B$  to produce a positive-going linear ramp. When the ramp has reached a value almost equal to the modulation input voltage (at MOD), the ramp terminates,  $C_B$  discharges and a start signal to the  $C_A$ -ramp at TCA is produced. A linear phase modulation is reached in this

way. If no modulation is required, the MOD-input must be connected to a fixed voltage of a certain positive value up to  $V_{DD}$ . Care must be taken that the V' pulse is never smaller than the minimum value to ensure that the external capacitor of PC1 (C<sub>A</sub>) can be discharged during that time. Since the V' pulse width is directly related to the TCB ramp duration, there is a requirement for the minimum value of this ramp duration.

#### **Reference oscillator**

The reference oscillator normally operates with an external crystal as shown in Fig.2. The internal circuitry can be used as a buffer amplifier in case an external reference should be required.

#### **Reference divider**

The reference divider consists of a binary divider with a programmable division ratio of 1 to 1024 and a prescaler with selectable division ratios of 1, 2, 10 and 100, according to the following tables:

#### **Binary divider**

| N (A <sub>0</sub> TO A <sub>9</sub> ) | DIVISION RATIO |

|---------------------------------------|----------------|

| 0                                     | 1024           |

| $0 \le N \le 1023$                    | Ν              |

#### Prescaler

| PROGRAMMING WORD<br>(NS <sub>0</sub> , NS <sub>1</sub> ) | DIVISION RATIO |

|----------------------------------------------------------|----------------|

| 0                                                        | 1              |

| 1                                                        | 2              |

| 2                                                        | 10             |

| 3                                                        | 100            |

**HEF4750V**

LSI

## Frequency synthesizer

In this way suitable comparison frequencies can be obtained from a range of crystal frequencies. The divider can also be used as a 'stand alone' programmable divider by connecting input TRA to  $V_{DD}$ , which causes all internal analogue currents to be switched off.

#### **Biasing circuitry**

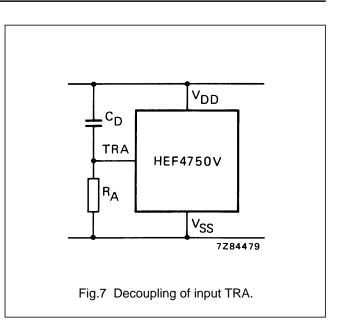

The biasing circuitry uses an external current source or resistor, which has to be connected between the TRA and  $V_{SS}$  pins. This circuitry supplies all analogue parts of the circuit. Consequently the analogue properties of the device, such as gain, charge currents, speed, power dissipation, impedance levels etc., are mainly determined by the value of the input current at TRA. The TRA input must be decoupled to  $V_{DD}$ , as shown in Fig.7. The value of  $C_D$  has to be chosen such that the TRA input is 'clean', e.g. 10 nF at  $R_A = 68 \text{ k}\Omega$ .

#### RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| Supply voltage                        | V <sub>DD</sub>  | -0,5                   | to + 15 V             |

|---------------------------------------|------------------|------------------------|-----------------------|

| Voltage on any input                  | VI               | –0,5 to $V_{\text{D}}$ | <sub>DD</sub> + 0,5 V |

| D.C. current into any input or output | ±Ι               | max.                   | 10 mA                 |

| Power dissipation per package         |                  |                        |                       |

| for $T_{amb} = 0$ to + 85 °C          | P <sub>tot</sub> | max.                   | 500 mW                |

| Power dissipation per output          |                  |                        |                       |

| for $T_{amb} = 0$ to 85 °C            | Р                | max.                   | 100 mW                |

| Storage temperature                   | T <sub>stg</sub> | –65 te                 | o + 150 °C            |

| Operating ambient temperature         | $T_{amb}$        | -40 te                 | o +85 °C              |

# HEF4750V LSI

### **DC CHARACTERISTICS**

at  $V_{DD}$  = 10 V ± 5%; voltages are referenced to  $V_{SS}$  = 0 V, unless otherwise specified; for definitions see note 1.

|                                            |                   | T <sub>amb</sub> (°C |      |      |              |            |         |      |      |      |    |       |

|--------------------------------------------|-------------------|----------------------|------|------|--------------|------------|---------|------|------|------|----|-------|

| PARAMETER                                  | SYMBOL            | -40                  |      |      | + 25         |            |         | + 85 |      |      |    | NOTES |

|                                            |                   | MIN.                 | TYP. | MAX. | MIN.         | TYP.       | MAX.    | MIN. | TYP. | MAX. |    |       |

| Quiescent device                           |                   |                      |      |      |              |            |         |      |      |      |    |       |

| current                                    | I <sub>DD</sub>   | _                    | _    | 100  | _            | _          | 100     | _    | _    | 750  | μA | 2     |

| Input current; logic                       |                   |                      |      |      |              |            |         |      |      |      |    |       |

| inputs, MOD                                | ± I <sub>IN</sub> | _                    | _    | 300  | _            | _          | 300     | _    | _    | 1000 | nA | 3     |

| Output leakage current                     |                   |                      |      |      |              |            |         |      |      |      |    |       |

| at $\frac{1}{2}$ V <sub>DD</sub>           |                   |                      |      |      |              |            |         |      |      |      |    | 3,4   |

| TCA, hold-state                            | $\pm I_Z$         | _                    | _    | 20   | _            | 0,05       | 20      | _    | _    | 60   | nA |       |

| TCC, analogue                              |                   |                      |      |      |              |            |         |      |      |      |    |       |

| switch OFF                                 | $\pm I_Z$         | _                    | _    | 20   | _            | 0,05       | 20      | _    | _    | 60   | nA |       |

| PC <sub>2</sub> , high impedance           |                   |                      |      |      |              | -,         |         |      |      |      |    |       |

| OFF-state                                  | $\pm I_Z$         | _                    | _    | 50   | _            | _          | 50      | _    | _    | 500  | nA |       |

| Logic input voltage                        |                   |                      |      |      |              |            |         |      |      |      |    |       |

| LOW                                        | VIL               |                      |      |      | <br>ma       | ax. 0,3    | Vpp     |      |      |      | v  |       |

| HIGH                                       |                   |                      |      |      |              | ax. 0,7    |         |      |      |      | v  |       |

| Logic output voltage                       | VIH               |                      |      |      |              | IX. 0,7    | • DD    |      |      |      | V  |       |

| LOW; at $ I_0  < 1 \mu A$                  | V <sub>OL</sub>   |                      | _    | 50   |              | _          | 50      |      | _    | 50   | mV | 3     |

| HIGH                                       | Vol<br>Voн        |                      |      | 50   | 1            | V          | 50 mV - | I    |      | 50   | mV | 3     |

| Logic output current                       | ⊻ОН               |                      |      |      | - 11111.<br> | v DD — .   | 50 m -  |      |      |      |    | 5     |

| LOW; at $V_{OL} = 0.5 V$                   |                   |                      |      |      |              |            |         |      |      |      |    | 3     |

|                                            |                   |                      |      |      |              |            |         |      |      |      |    | 3     |

| outputs OL, PC <sub>2</sub> ,<br>OUT       |                   | FF                   |      |      | 10           |            |         | 2.0  |      |      |    |       |

|                                            | I <sub>OL</sub>   | 5,5                  | _    | -    | 4,6          | _          | -       | 3,6  | _    | _    | mA |       |

| output XTAL                                | I <sub>OL</sub>   | 2,8                  | _    | _    | 2,4          | -          | _       | 1,9  | _    | _    | mA |       |

| Logic output current                       |                   |                      |      |      |              |            |         |      |      |      |    |       |

| HIGH;                                      |                   |                      |      |      |              |            |         |      |      |      |    |       |

| at $V_{OH} = V_{DD} - 0.5 V$               | .                 | 4.5                  |      |      |              |            |         |      |      |      |    | 3     |

| outputs OL, PC <sub>2</sub> ,OUT           | –I <sub>OH</sub>  | 1,5                  | -    | -    | 1,3          | _          | -       | 1,0  | -    | -    | mA |       |

| output XTAL                                | –I <sub>OH</sub>  | 1,4                  | _    | _    | 1,2          | _          | _       | 0,9  | _    | _    | mA |       |

| Output TCC sink                            |                   |                      |      |      |              | <b>.</b> . |         |      |      |      |    |       |

| current                                    | lo                | -                    | -    | -    | -            | 2,1        | -       | -    | -    | -    | mA | 3,4,5 |

| Output TCC source                          |                   |                      |      |      |              |            |         |      |      |      |    |       |

| current                                    | -lo               | -                    | -    | -    | -            | 1,9        | -       | -    | -    | -    | mA | 3,4,6 |

| Internal resistance                        |                   |                      |      |      |              |            |         |      |      |      |    |       |

| of TCC                                     |                   |                      |      |      |              |            |         |      |      |      |    |       |

| output swing  <br>≤ 200 mV                 |                   |                      |      |      |              |            |         |      |      |      |    |       |

| specified output range:                    |                   |                      |      |      |              |            |         |      |      |      |    |       |

| 0,3 V <sub>DD</sub> to 0,7 V <sub>DD</sub> | R <sub>i</sub>    | -                    | _    | _    | _            | 0,7        | _       | _    | _    | _    | kΩ | 3,4   |

# HEF4750V LSI

|                                            |                  |      |      |      | 7    | ר <sub>amb</sub> (° | С    |      |      |      |    |        |

|--------------------------------------------|------------------|------|------|------|------|---------------------|------|------|------|------|----|--------|

| PARAMETER                                  | SYMBOL           | -40  |      |      | + 25 |                     |      | + 85 |      |      |    | NOTES  |

|                                            |                  | MIN. | TYP. | MAX. | MIN. | TYP.                | MAX. | MIN. | TYP. | MAX. |    |        |

| Output TCC voltage                         |                  |      |      |      |      |                     |      |      |      |      |    |        |

| with respect to                            |                  |      |      |      |      |                     |      |      |      |      |    |        |

| TCA input voltage                          | ΔV               | -    | 0    | _    | -    | 0                   | _    | -    | 0    | _    | V  | 3,4,7  |

| Output PC <sub>1</sub> sink                |                  |      |      |      |      |                     |      |      |      |      |    |        |

| current                                    | lo               | -    | _    | _    | -    | 1,1                 | _    | -    | _    | _    | mA | 3,4,8  |

| Output PC <sub>1</sub> source              |                  |      |      |      |      |                     |      |      |      |      |    |        |

| current                                    | -lo              | -    | _    | _    | -    | 1,0                 | _    | -    | _    | _    | mA | 3,4,9  |

| Internal resistance                        |                  |      |      |      |      |                     |      |      |      |      |    |        |

| of PC <sub>1</sub>                         |                  |      |      |      |      |                     |      |      |      |      |    |        |

| output swing                               |                  |      |      |      |      |                     |      |      |      |      |    |        |

| ≤ 200 mV                                   |                  |      |      |      |      |                     |      |      |      |      |    |        |

| specified output range:                    |                  |      |      |      |      |                     |      |      |      |      |    |        |

| 0,3 V <sub>DD</sub> to 0,7 V <sub>DD</sub> | R <sub>i</sub>   | -    | -    | -    | -    | 1,4                 | -    | -    | -    | _    | kΩ | 3,4    |

| Output PC <sub>1</sub> voltage             |                  |      |      |      |      |                     |      |      |      |      |    |        |

| with respect to                            |                  |      |      |      |      |                     |      |      |      |      |    |        |

| TCC input voltage                          | ΔV               | -    | 0    | -    | -    | 0                   | -    | -    | 0    | -    | V  | 3,4,10 |

| EOR generation                             |                  |      |      |      |      |                     |      |      |      |      |    |        |

| $V_{EOR} = V_{DD} - V_{TCA}$               | V <sub>EOR</sub> | -    | 0,9  | _    | -    | 0,7                 | _    | -    | 0,6  | _    | V  | 3,4,11 |

| Source current; HIGH                       |                  |      |      |      |      |                     |      |      |      |      |    |        |

| at V <sub>OUT</sub> = ½ V <sub>DD</sub> ;  |                  |      |      |      |      |                     |      |      |      |      |    |        |

| output in ramp mode                        |                  |      |      |      |      |                     |      |      |      |      |    | 3,4    |

| TCA                                        | Io               | -    | _    | _    | _    | 13                  | _    | -    | _    | _    | mA |        |

| тсв                                        | lo               | _    | _    | _    | _    | 2,5                 | _    | _    | _    | _    | mA |        |

# HEF4750V LSI

### AC CHARACTERISTICS

#### **General note**

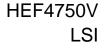

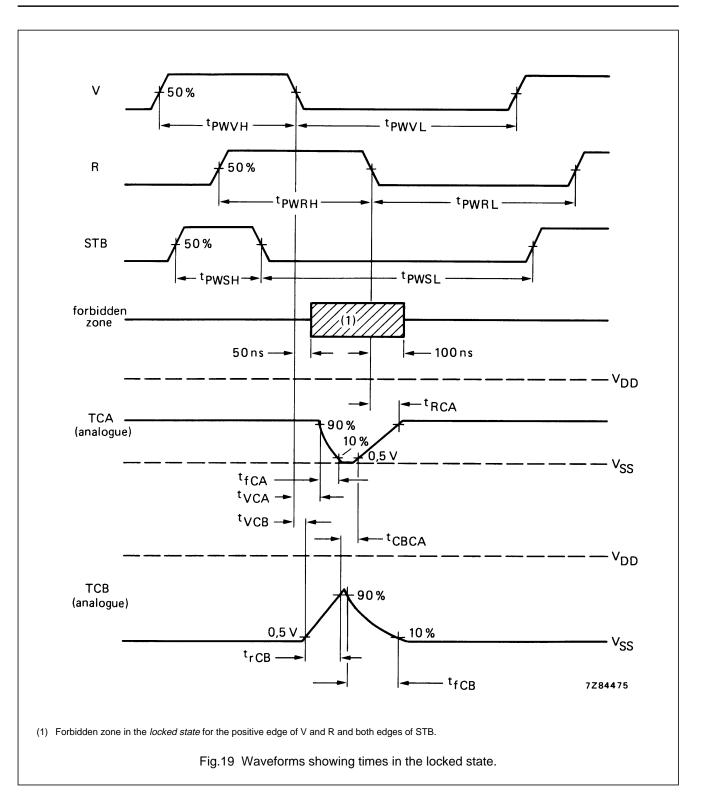

The dynamic specifications are given for the circuit built-up with external components as given in Fig.8, under the following conditions; for definitions see note 1; for definitions of times see Fig.19;  $V_{DD} = 10 \text{ V} \pm 5\%$ ;  $T_{amb} = 25 \text{ °C}$ ; input transition times  $\leq 20 \text{ ns}$ ;  $R_A = 68 \text{ k}\Omega \pm 30\%$  (see also note 4);  $C_A = 270 \text{ pF}$ ;  $C_B = 150 \text{ pF}$ ;  $C_C = 1 \text{ nF}$ ;  $C_D = 10 \text{ nF}$ ; unless otherwise specified.

|                              | SYMBOL            | MIN. | TYP. | MAX. | UNIT | CONDITIONS               | NOTES |

|------------------------------|-------------------|------|------|------|------|--------------------------|-------|

| Slew rate                    |                   |      |      |      |      |                          |       |

| ТСА                          | S <sub>TCA</sub>  | _    | 52   | _    | V/µs | R <sub>A</sub> = minimum | 12    |

| ТСА                          | S <sub>TCA</sub>  | _    | 28   | _    | V/µs | R <sub>A</sub> = maximum | 12    |

| ТСВ                          | S <sub>TCB</sub>  | _    | 20   | _    | V/µs | R <sub>A</sub> = minimum | 12    |

| ТСВ                          | S <sub>TCB</sub>  | _    | 10   | _    | V/µs | R <sub>A</sub> = maximum | 12    |

| Ramp linearity               |                   |      |      |      |      |                          |       |

| ТСА                          | I <sub>TCA</sub>  | _    | 2    | _    | %    |                          | 13    |

| ТСВ                          | I <sub>TCB</sub>  | _    | 2    | _    | %    |                          | 13    |

| Start of TCA-ramp delay      | t <sub>CBCA</sub> | -    | 200  | _    | ns   |                          |       |

| Delay of TCA-hold            | t <sub>RCA</sub>  | _    | 40   | _    | ns   |                          |       |

| Delay of TCA-discharge       | t <sub>VCA</sub>  | _    | 60   | _    | ns   |                          |       |

| Start of TCB-ramp delay      | t <sub>VCB</sub>  | _    | 60   | _    | ns   |                          |       |

| TCB-ramp duration            | t <sub>rCB</sub>  | -    | 250  | _    | ns   | $V_{MOD} = 4 V$          |       |

|                              | t <sub>rCB</sub>  | _    | 350  | _    | ns   | $V_{MOD} = 6 V$          |       |

|                              | t <sub>rCB</sub>  | _    | 450  | _    | ns   | V <sub>MOD</sub> = 8 V   |       |

| Required TCB min.            |                   |      |      |      |      |                          |       |

| ramp duration                | t <sub>rCB</sub>  | _    | 150  | _    | ns   |                          | 14    |

| Pulse width                  |                   |      |      |      |      |                          |       |

| V : LOW                      | t <sub>PWVL</sub> | _    | 20   | _    | ns   |                          |       |

| V : HIGH                     | t <sub>PWVH</sub> | _    | 20   | _    | ns   |                          |       |

| R : LOW                      | t <sub>PWRL</sub> | _    | 20   | _    | ns   |                          |       |

| R : HIGH                     | t <sub>PWRH</sub> | _    | 20   | _    | ns   |                          |       |

| STB : LOW                    | t <sub>PWSL</sub> | _    | 20   | _    | ns   |                          |       |

| STB : HIGH                   | t <sub>PWSH</sub> | _    | 20   | _    | ns   |                          |       |

| Fall time                    |                   |      |      |      |      |                          |       |

| ТСА                          | t <sub>fCA</sub>  | _    | 50   | _    | ns   |                          |       |

| ТСВ                          | t <sub>fCB</sub>  | _    | 50   | _    | ns   |                          |       |

| Prescaler input frequency    | f <sub>PR</sub>   | -    | 30   | _    | MHz  | all division ratios      |       |

| Binary divider frequency     | f <sub>DIV</sub>  | _    | 30   | _    | MHz  | all division ratios      |       |

| Crystal oscillator frequency | f <sub>OSC</sub>  | _    | 10   | _    | MHz  |                          |       |

| Average power supply current |                   |      |      |      |      | locked state             |       |

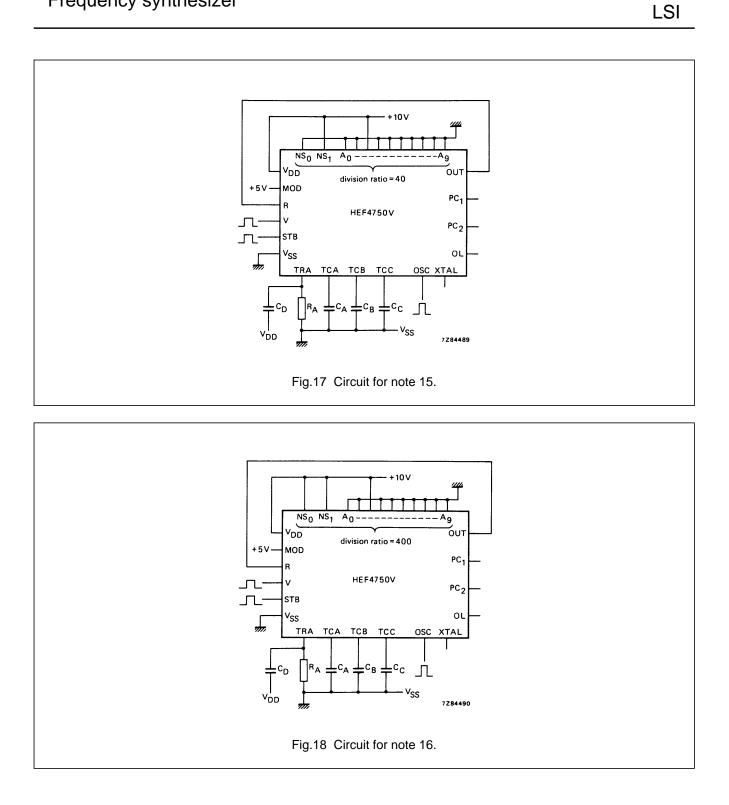

| with speed-up 1 : 10         | I <sub>P</sub>    | _    | 3,6  | _    | mA   |                          | 15    |

| without speed-up             | I <sub>P</sub>    | _    | 3,2  | _    | mA   |                          | 16    |

HEF4750V LSI

#### Notes

- 1. Definitions:

- $R_{A}$  = external biasing resistor between pins TRA and V\_{SS}; 68 k\Omega  $\pm$  30%.

- $C_A$  = external timing capacitor for time/voltage converter, between pins TCA and  $V_{SS}$ .

- $C_B$  = external timing capacitor for phase modulator, between pins TCB and V<sub>SS</sub>.

- $C_C$  = external hold capacitor between pins TCC and V<sub>SS</sub>.

- $C_D$  = decoupling capacitor between pins TRA and  $V_{DD}$ .

- Logic inputs: V, R, STB, A<sub>0</sub> to A<sub>9</sub>, NS<sub>0</sub>, NS<sub>1</sub>, OSC.

- Logic outputs: OL, PC<sub>2</sub>, XTAL, OUT.

- Analogue signals: TCA, TCB, TCC, TRA, PC<sub>1</sub>, MOD.

- 2. TRA at  $V_{DD}$ ; TCA, TCB, TCC and MOD at  $V_{SS}$ ; logic inputs at  $V_{SS}$  or  $V_{DD}$ .

- 3. All logic inputs at  $V_{SS}$  or  $V_{DD}$ .

- 4. R<sub>A</sub> connected; its value chosen such that  $I_{TRA} = 100 \ \mu A$ .

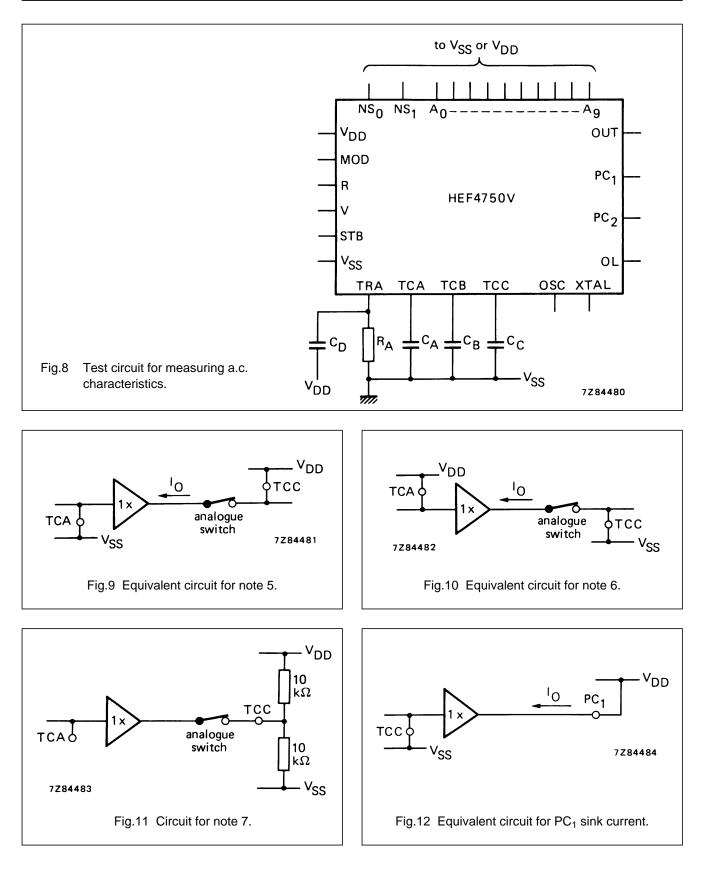

- 5. The analogue switch is in the ON position (see Fig.9).

- 6. The analogue switch is in the ON position (see Fig.10).

```

7. See Fig.11.

```

This guarantees the d.c. voltage gain, combined with d.c.-offset. Input condition: 0,3  $V_{DD}$   $\leq$   $V_{TCA}$   $\leq$  0,7  $V_{DD}.$

$$\Delta \mathsf{V} = \mathsf{V}_{\mathsf{TCC}} - \mathsf{V}_{\mathsf{TCA}}$$

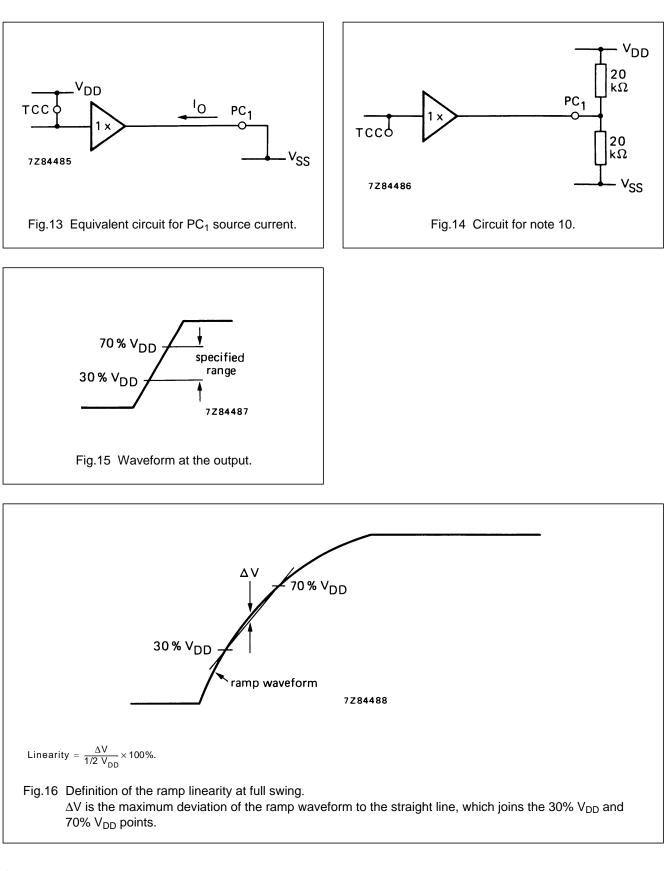

- 8. See Fig.12.

- 9. See Fig.13.

- 10. See Fig.14.

This guarantees the d.c. voltage gain, combined with d.c.-offset. Input condition: 0,3  $V_{DD} \leq V_{TCC} \leq 0,7 \ V_{DD}$ .  $\Delta V = V_{PC1} - V_{TCC}$ .

- 11. Switching level at TCA, generating an EOR-signal, during increasing input voltage.

- 12. See Fig.15.

```

13. See Fig.16.

```

Definition of the ramp linearity at full swing.

- 14. The external components and modulation input voltage must be chosen such that this requirement will be fulfilled, to ensure that C<sub>A</sub> is sufficiently discharged during that time.

- 15. See Fig.17.

Circuit connections for power supply current specification, with speed-up 1 : 10. V and R are in the range of PC1, such that the output voltage at  $PC_1$  is equal to 5 V.

$f_{OSC} = 5 \text{ MHz}$  (external clock)  $f_{STB} = 12,5 \text{ kHz}$  $f_V = 125 \text{ kHz}$

16. See Fig.18.

Circuit connections for power supply current specification, without speed-up. V and R are in the range of PC1, such that the output voltage at  $PC_1$  is equal to 5 V.

$f_{OSC} = 5$  MHz (external clock)  $f_{STB} = 12,5$  kHz  $f_V = 12,5$  kHz

HEF4750V LSI

HEF4750V

# Frequency synthesizer

# HEF4750V LSI

## HEF4750V LSI

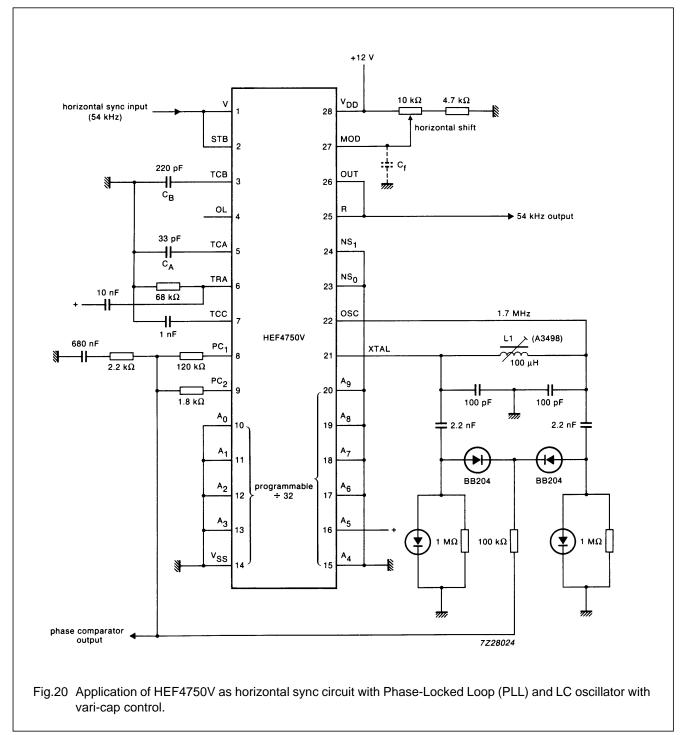

#### APPLICATION INFORMATION