## INTEGRATED CIRCUITS

Product specification Supersedes data of 1999 Mar 22 File under Integrated Circuits, IC12 1999 Aug 16

HILIPS

#### **Product specification**

## $65 \times 102$ pixels matrix LCD driver

#### CONTENTS

| FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Packages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PINNING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PIN FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| R0 to R64: row driver outputs<br>C0 to C101: column driver outputs<br>$V_{SS1}$ and $V_{SS2}$ : negative power supply rails<br>$V_{DD1}$ to $V_{DD3}$ : positive power supply rails<br>$V_{LCDIN}$ : LCD power supply<br>$V_{LCDOUT}$ : LCD power supply<br>$V_{LCDSENSE}$ : voltage multiplier regulation input<br>( $V_{LCD}$ )<br>T1 to T12: test pads<br>SDAIN and SDAOUT: I <sup>2</sup> C-bus data lines<br>SCL: I <sup>2</sup> C-bus clock signal<br>SA0: slave address<br>OSC: oscillator<br>RES: reset |

| BLOCK DIAGRAM FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Oscillator<br>I <sup>2</sup> C-bus interface<br>Display control logic<br>Display Data RAM (DDRAM)<br>Timing generator<br>LCD row and column drivers                                                                                                                                                                                                                                                                                                                                                             |

| INITIALIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ADDRESSING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Display data RAM structure<br>RAM access                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I <sup>2</sup> C-BUS INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Characteristics of the I <sup>2</sup> C-bus<br>Bit transfer<br>START and STOP conditions<br>System configuration                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

- Acknowledge 11.1.4

- 11.2 I<sup>2</sup>C-bus protocol

| 12     | INSTRUCTIONS         |

|--------|----------------------|

| 12.1   | External reset (RES) |

| 12.2   | Function set         |

| 12.2.1 | Power-Down (PD)      |

| 12.2.2 | V                    |

| 12.2.3 | Н                    |

| 12.2.4 | MX                   |

| 12.2.5 | MY                   |

|        |                      |

- 12.3 **Display control**

- 12.3.1 D and E 12.4

- **Display configuration** TRS

- 12.4.1 BRS 12.4.2

- 12.5 Set Y address of RAM

- Set X address of RAM 12.6

- 12.7 Set HV generator stages

- 12.7.1 S[1:0]

- 12.8 Temperature control

- 12.9 Bias system

- 12.10 Set V<sub>OP</sub> value

- LIMITING VALUES 13

- 14 HANDLING

- DC CHARACTERISTICS 15

- 16 AC CHARACTERISTICS

- RESET 17

- 18 APPLICATION INFORMATION

- 19 CHIP INFORMATION

- 20 PAD INFORMATION

- 21 DEVICE PROTECTION DIAGRAM

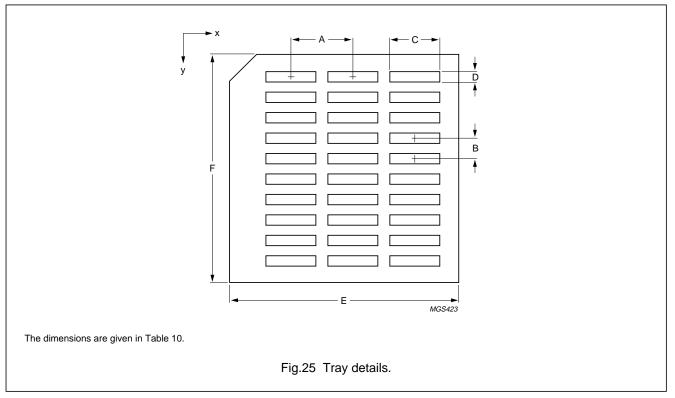

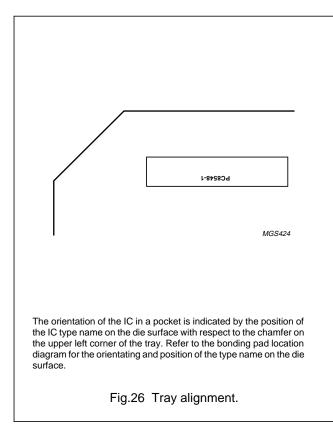

- 22 TRAY INFORMATION

- 23 DEFINITIONS

- LIFE SUPPORT APPLICATIONS 24

- 25 PURCHASE OF PHILIPS I<sup>2</sup>C COMPONENTS

- 26 BARE DIE DISCLAIMER

#### 1 FEATURES

- Single-chip LCD controller/driver

- 65 row and 102 column outputs

- Display data RAM  $65 \times 102$  bits

- On-chip:

- Configurable 5 (4, 3 and 2)  $\times$  voltage multiplier generating V\_{LCD} (external V\_{LCD} also possible)

- Generation of intermediate LCD bias voltages

- Oscillator requires no external components (external clock also possible).

- 400 kbits/s fast I<sup>2</sup>C-bus interface

- CMOS compatible inputs

- Mux rate: 1 : 65

- Logic supply voltage range V<sub>DD1</sub> to V<sub>SS</sub>:

- 1.9 to 5.5 V.

- High voltage generator supply voltage range  $V_{DD2}$  to  $V_{SS}$  and  $V_{DD3}$  to  $V_{SS}$ :

- 2.4 to 4.5 V with LCD voltage internally generated (voltage generator enabled).

- Display supply voltage range  $V_{\text{LCD}}$  to  $V_{\text{SS}}$ :

- 4.5 to 9.0 V

- Low power consumption, suitable for battery operated systems

- Temperature compensation of V<sub>LCD</sub>

- Slim chip layout, suitable for Chip-On-Glass (COG) applications

- Programmable bottom row pads mirroring and top row pads mirroring, for compatibility with both Tape Carrier Package (TCP) and COG applications.

#### 4 ORDERING INFORMATION

| TYPE NUMBER |              | PACKAGE                 |         |

|-------------|--------------|-------------------------|---------|

| ITFE NUMBER | NAME         | DESCRIPTION             | VERSION |

| PCF8548U/2  | Tray         | chip with bumps in tray | _       |

| PCF8548U/9  | Bumped wafer | quarter wafer           | -       |

|             |              |                         |         |

#### Product specification

PCF8548

3

3 GENERAL DESCRIPTION

2

The PCF8548 is a low power CMOS LCD controller driver, designed to drive a graphic display of 65 rows and 102 columns. All necessary functions for the display are provided in a single chip, including on-chip generation of LCD supply and bias voltages, resulting in a minimum of external components and low power consumption. The PCF8548 interfaces to most microcontrollers via an I<sup>2</sup>C-bus interface.

#### 3.1 Packages

DACKACE

**APPLICATIONS**

Telecom equipment

Portable instruments

Point of sale terminals.

The PCF8548 is available as chip with bumps in tray; tape carrier package is available on request.

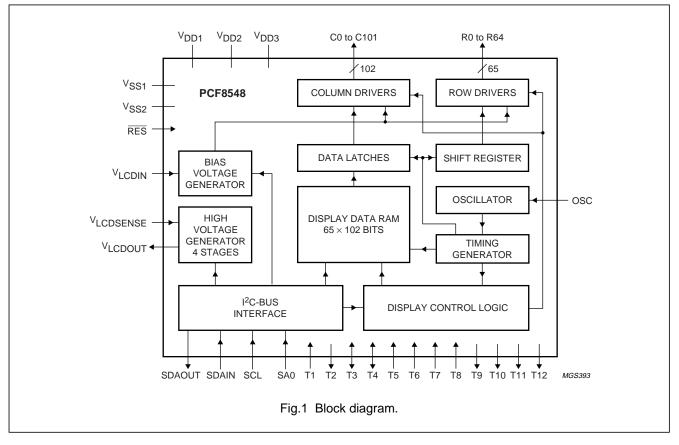

#### 5 BLOCK DIAGRAM

#### 6 PINNING

| SYMBOL                | PAD       | DESCRIPTION                                                |

|-----------------------|-----------|------------------------------------------------------------|

| RES                   | 1         | external reset input (active LOW)                          |

| SDAOUT                | 2         | I <sup>2</sup> C-bus data output                           |

| SDAIN                 | 3 and 4   | I <sup>2</sup> C-bus data input                            |

| SCL                   | 5 and 6   | I <sup>2</sup> C-bus clock input                           |

| T2                    | 7         | test 2 output                                              |

| SA0                   | 8         | least significant bit of slave address                     |

| T7 to T5              | 9 to 11   | test inputs                                                |

| T4 and T3             | 12 and 13 | test input/output                                          |

| T1                    | 14        | test input                                                 |

| V <sub>SS1</sub>      | 15 to 20  | negative power supply 1                                    |

| V <sub>SS2</sub>      | 21 to 26  | negative power supply 2                                    |

| V <sub>LCDOUT</sub>   | 28 to 33  | voltage multiplier output                                  |

| V <sub>LCDSENSE</sub> | 34        | voltage multiplier<br>regulation input (V <sub>LCD</sub> ) |

| SYMBOL             | PAD                        | DESCRIPTION               |

|--------------------|----------------------------|---------------------------|

| V <sub>LCDIN</sub> | 35 to 40                   | LCD supply voltage        |

| R32 to R19         | 41 to 54                   | LCD row driver outputs    |

| R0 to R18          | 57 to 75                   | LCD row driver outputs    |

| C0 to C101         | 76 to 177                  | LCD column driver outputs |

| R50 to R33         | 178 to 195                 | LCD row driver outputs    |

| R51 to R64         | 198 to 211                 | LCD row driver outputs    |

| T12 to T9          | 212 to 215                 | test outputs              |

| OSC                | 216                        | oscillator                |

| T8                 | 217                        | test input                |

| V <sub>DD1</sub>   | 218 to 223                 | supply voltage 1          |

| V <sub>DD3</sub>   | 224 to 226                 | supply voltage 3          |

| V <sub>DD2</sub>   | 227 to 233                 | supply voltage 2          |

|                    | 27, 55, 56,<br>196 and 197 | dummy pads                |

#### 7 PIN FUNCTIONS

#### 7.1 R0 to R64: row driver outputs

These pads output the row signals.

#### 7.2 C0 to C101: column driver outputs

These pads output the column signals.

#### 7.3 V<sub>SS1</sub> and V<sub>SS2</sub>: negative power supply rails

$V_{SS2}$  is related to  $V_{DD2}$  and  $V_{DD3}$  and  $V_{SS1}$  is related to  $V_{DD1}.$

#### 7.4 V<sub>DD1</sub> to V<sub>DD3</sub>: positive power supply rails

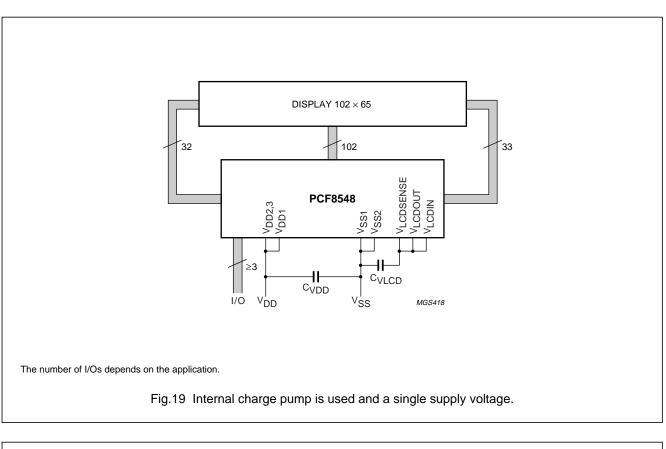

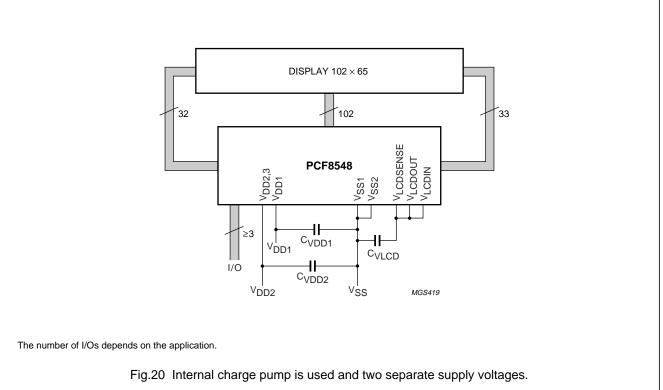

$V_{DD2}$  and  $V_{DD3}$  are the supply voltages for the internal voltage generator. Both have to be at the same voltage and must be connected together outside of the chip. If the internal voltage generator is not used, they should both be connected to power or to the  $V_{DD1}$  pad.

$V_{DD1}$  is used as the power supply for the rest of the chip. This voltage can be a different voltage than  $V_{DD2}$  and  $V_{DD3}.$

#### 7.5 V<sub>LCDIN</sub>: LCD power supply

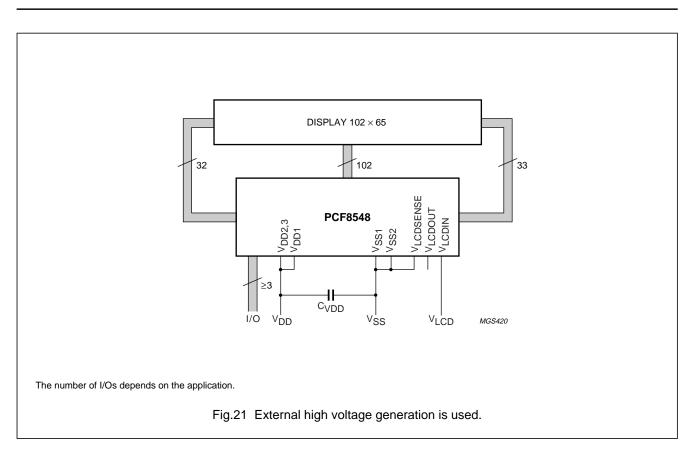

Internally generated positive power supply for the liquid crystal display. An external LCD supply voltage can be supplied using the  $V_{LCDIN}$  pad. In this case,  $V_{LCDOUT}$  has to be connected to ground, and the internal voltage generator has to be programmed to zero. If the PCF8548 is in power-down mode, the external LCD supply voltage must be switched off.

#### 7.6 V<sub>LCDOUT</sub>: LCD power supply

Positive power supply for the liquid crystal display. If the internal voltage generator is used, the two supply rails  $V_{LCDIN}$  and  $V_{LCDOUT}$  must be connected together and an external capacitor must be connected (see Fig.19).

## 7.7 V<sub>LCDSENSE</sub>: voltage multiplier regulation input (V<sub>LCD</sub>)

V<sub>LCDSENSE</sub> is the input voltage for the internal voltage multiplier regulation.

If the internal voltage generator is used then V<sub>LCDSENSE</sub> must be connected to V<sub>LCDOUT</sub>. If an external supply voltage is used then V<sub>LCDSENSE</sub> must be connected to ground.

#### 7.8 T1 to T12: test pads

T1 and T3 to T7 must be connected to  $V_{SS1}$ . T8 must be connected to  $V_{DD1}$ . T2 and T9 to T12 must be left open-circuit; not accessible to user.

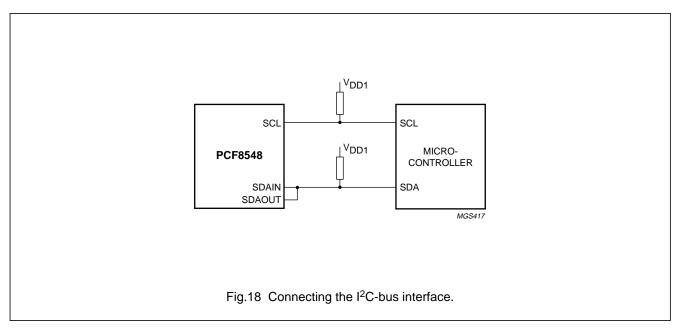

#### 7.9 SDAIN and SDAOUT: I<sup>2</sup>C-bus data lines

Serial data and acknowledge lines for the I<sup>2</sup>C-bus. By connecting SDAIN to SDAOUT, the SDA line becomes fully I<sup>2</sup>C-bus compatible. Having the acknowledge output (SDAOUT) separated from the serial data line is advantageous in Chip-On-Glass (COG) applications. In COG applications where the track resistance from the SDAOUT pad to the system SDA line can be significant, a potential divider is generated by the bus pull-up resistor and the Indium Tin Oxide (ITO) track resistance. It is possible that during the acknowledge cycle the PCF8548 will not be able to create a valid logic 0 level. By splitting the SDA input from the output the device could be used in a mode that ignores the acknowledge bit. In COG applications where the acknowledge cycle is required, it is necessary to minimize the track resistance from the SDACK pad to the system SDA line to guarantee a valid LOW level.

#### 7.10 SCL: I<sup>2</sup>C-bus clock signal

I<sup>2</sup>C-bus serial clock signal input.

#### 7.11 SA0: slave address

Two different slave addresses can be selected using the SA0 pad. This allows two PCF8548 LCD drivers to be connected to the same  $I^2$ C-bus.

#### 7.12 OSC: oscillator

When the on-chip oscillator is used this input must be connected to  $V_{DD1}$ . An external clock signal, if used, is connected to this input.

#### 7.13 RES: reset

This signal is used to reset the device. The signal is active LOW.

#### 8 BLOCK DIAGRAM FUNCTIONS

#### 8.1 Oscillator

The on-chip oscillator provides the clock signal for the display system. No external components are required and the OSC input must be connected to  $V_{DD1}$ . An external clock signal (if used), is connected to this input.

#### 8.2 I<sup>2</sup>C-bus interface

The I<sup>2</sup>C-bus interface receives and executes the commands sent via the I<sup>2</sup>C-bus. It also receives RAM data and sends it to the RAM.

#### 8.3 Display control logic

The display control logic generates the control signals to read from the RAM via the 102 bits parallel port. It also generates the control signals for the row and column drivers.

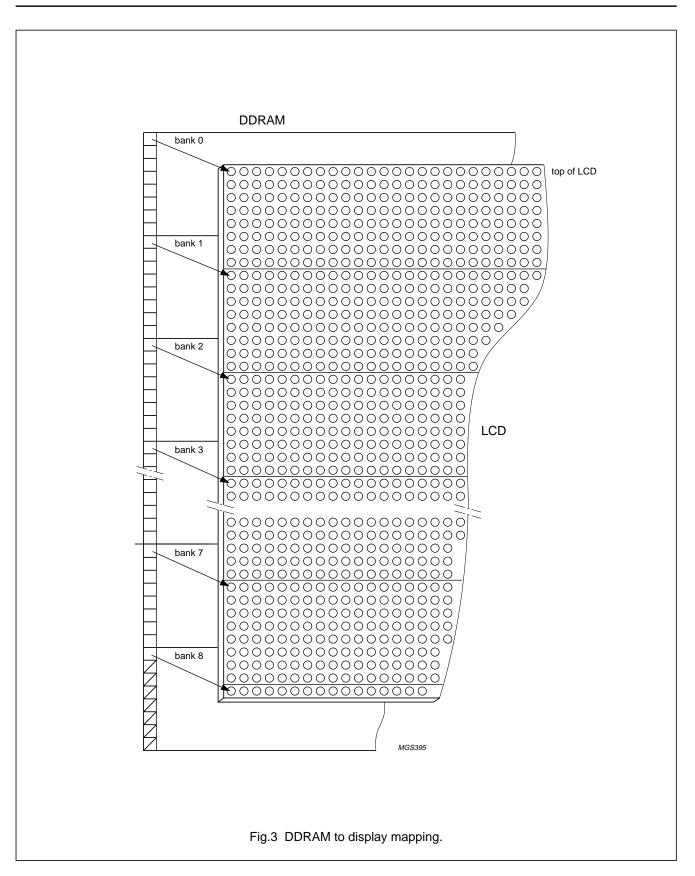

#### 8.4 Display Data RAM (DDRAM)

The PCF8548 contains a  $65 \times 102$  bit static RAM which stores the display data. The RAM is divided into 8 banks of 102 bytes and 1 bank of 102 bits [ $(8 \times 8 + 1) \times 102$  bits]. During RAM access, data is transferred to the RAM via the I<sup>2</sup>C-bus interface. There is a direct correspondence between the X address and column output number.

#### 8.5 Timing generator

The timing generator produces the various signals required to drive the internal circuitry. Internal chip operation is not disturbed by operations on the  $l^2C$ -bus.

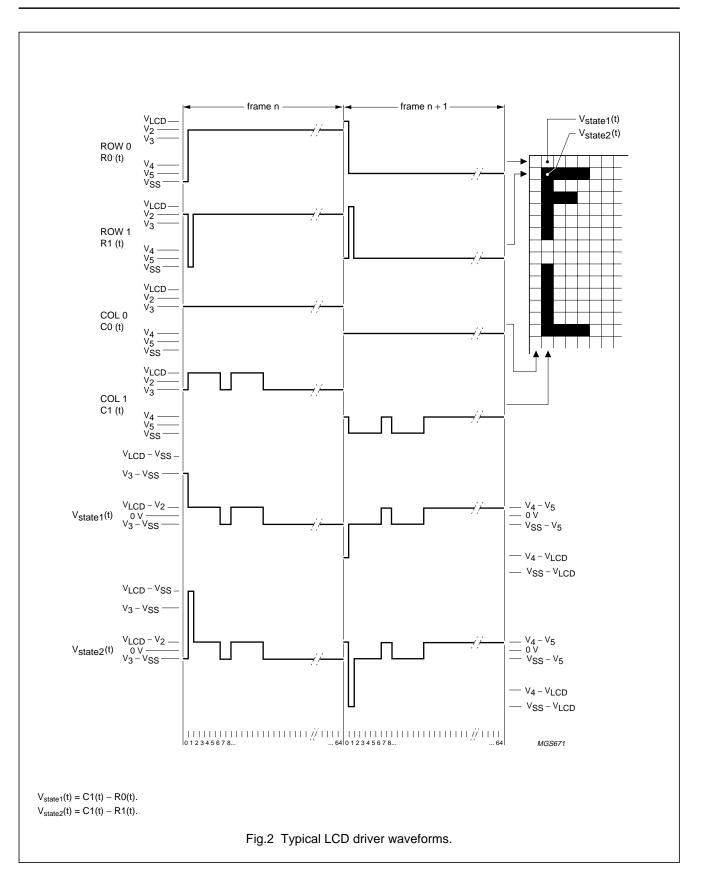

#### 8.6 LCD row and column drivers

The PCF8548 contains 65 row and 102 column drivers, which connect the appropriate LCD bias voltages to the display in accordance with the data to be displayed. Figure 2 shows typical waveforms. Unused outputs should be left unconnected.

#### 9 INITIALIZATION

Immediately following Power-on, all internal registers and the RAM content are undefined. A reset pulse must first be applied.

Reset is accomplished by applying an external RES pulse (active LOW). When reset occurs within the specified time all internal registers are initialized, however the RAM is still undefined. The state after reset is described in Section 12.1.

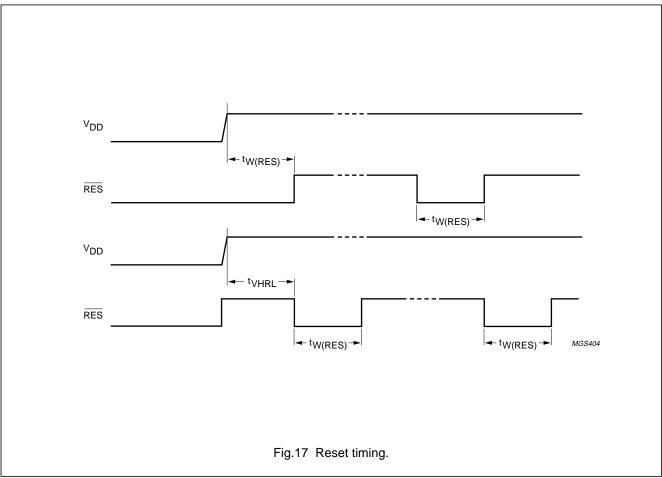

The  $\overline{RES}$  input must be  ${\leq}0.3~V_{DD}$  when  $V_{DD}$  reaches  $V_{DD(min)}$  (or higher) within a maximum time  $t_{VHRL}$  after  $V_{DD}$  goes HIGH (see Fig.17).

PCF8548

## $65 \times 102$ pixels matrix LCD driver

PCF8548

#### 10 ADDRESSING

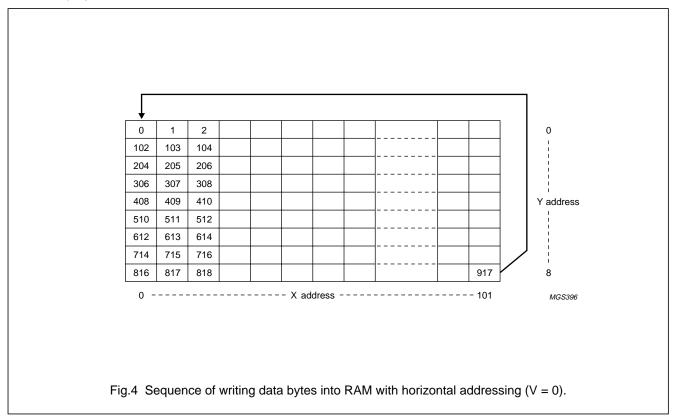

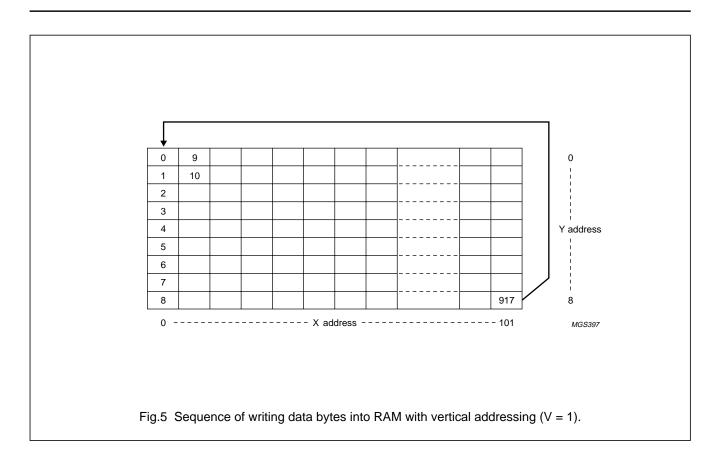

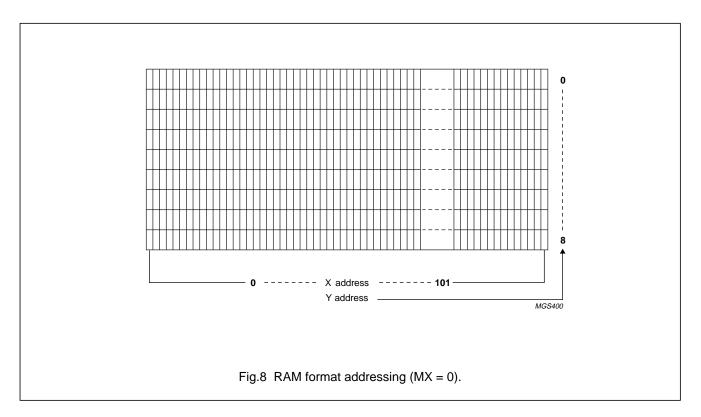

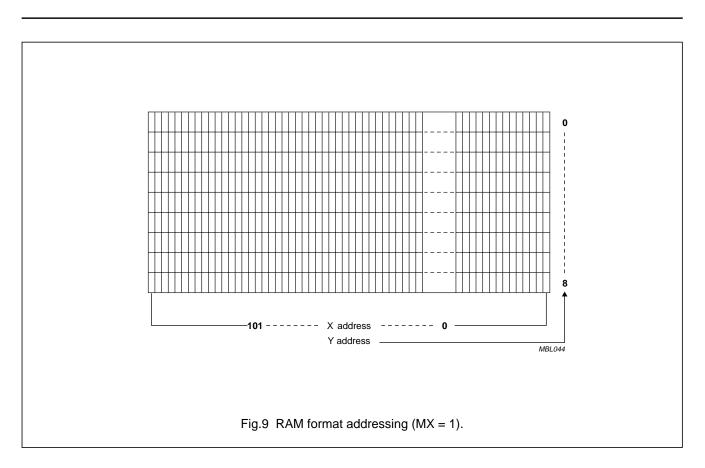

The Display Data RAM (DDRAM) of the PCF8548 is accessed as indicated in Figs 3, 6, 7, 8 and 9. The DDRAM has a matrix of  $65 \times 102$  bits. The RAM cells are addressed by the X and Y address pointers. The address ranges are X0 to X101 (1100101b) and Y0 to Y8 (1000b). Addresses outside of these ranges are not allowed. In vertical addressing mode (V = 1) the Y address increments after each byte (see Fig.5). After the last Y address (Y = 8), Y wraps around to 0 and X increments to address the next column. In the horizontal addressing mode (V = 0) the X address increments after each byte (see Fig.4). After the last X address (X = 101), X wraps around to 0 and Y increments to address the next row. After the very last address (X = 101 and Y = 8) the address pointers wrap around to address X = 0 and Y = 0.

#### 10.1 Display data RAM structure

## PCF8548

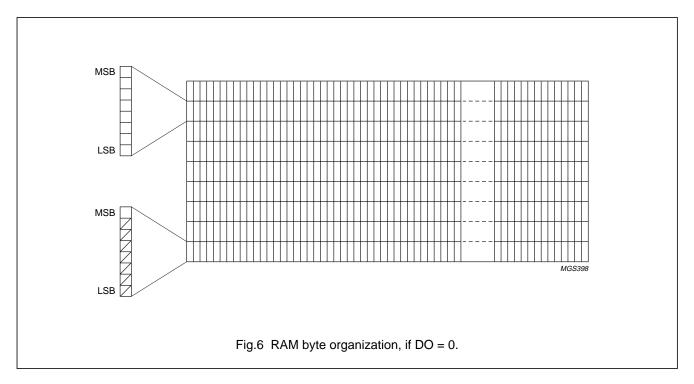

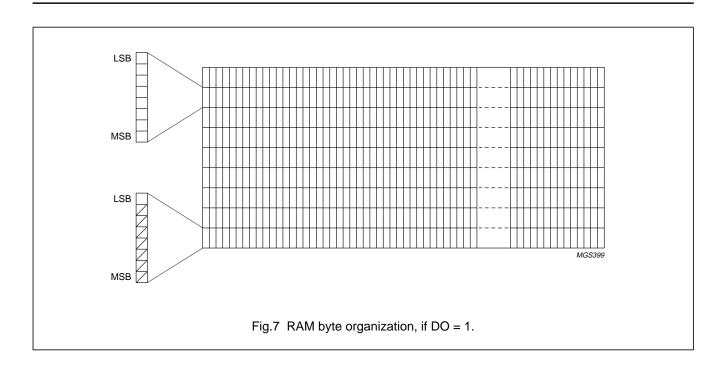

The DO bit defines the bit order (MSB on top or MSB on bottom) for writing to the RAM (see Figs 6 and 7).

The MX bit allows a horizontal mirroring; when MX = 1, the X address space is mirrored. The address X = 0 is then located at the right side (column 101) of the display (see Fig.9). When MX = 0 the mirroring is disabled and the address X = 0 is located at the left side (column 0) of the display (see Fig.8).

## PCF8548

#### 10.2 RAM access

If the  $D/\overline{C}$  bit is logic 1 the RAM can be written to. The data is written to the RAM during the acknowledge cycle.

#### 11 I<sup>2</sup>C-BUS INTERFACE

#### 11.1 Characteristics of the I<sup>2</sup>C-bus

The I<sup>2</sup>C-bus is for bidirectional, two-line communication between different ICs or modules. The two lines are a Serial Data line (SDA) and a Serial Clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor. Data transfer may be initiated only when the bus is not busy.

#### 11.1.1 BIT TRANSFER

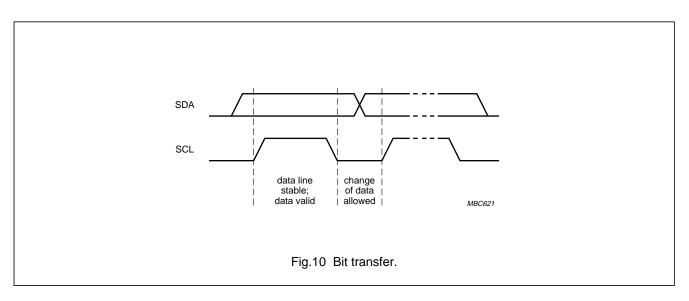

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse because changes in the data line at this time will be interpreted as a control signal. Bit transfer is illustrated in Fig.10.

#### 11.1.2 START AND STOP CONDITIONS

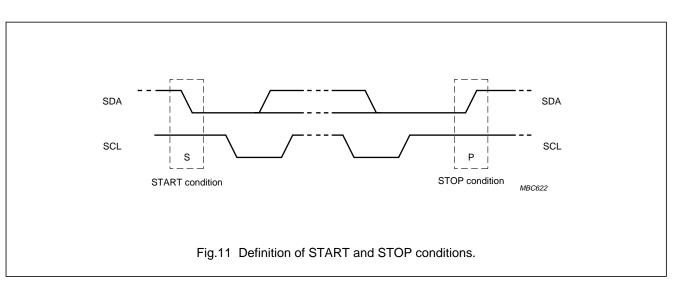

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P). The START and STOP conditions are illustrated in Fig.11.

#### 11.1.3 SYSTEM CONFIGURATION

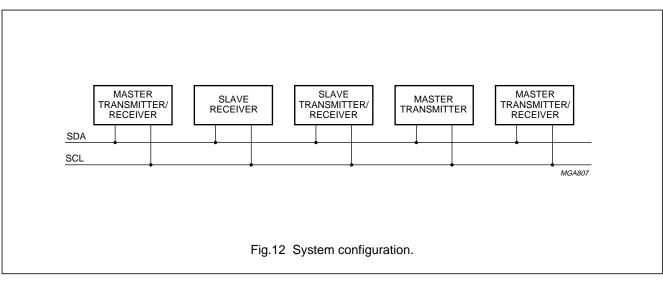

The system configuration is illustrated in Fig.12.

- Transmitter: the device which sends the data to the bus

- Receiver: the device which receives the data from the bus

- Master: the device which initiates a transfer, generates clock signals and terminates a transfer

- · Slave: the device addressed by a master

- Multi-Master: more than one master can attempt to control the bus at the same time without corrupting the message

- Arbitration: procedure to ensure that, if more than one master simultaneously tries to control the bus, only one is allowed to do so and the message is not corrupted

- Synchronization: procedure to synchronize the clock signals of two or more devices.

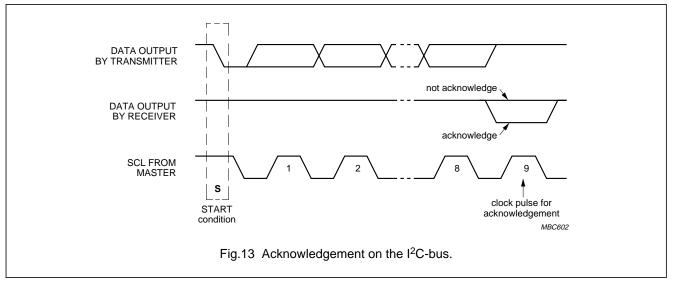

#### 11.1.4 ACKNOWLEDGE

Each byte of eight bits is followed by an acknowledge bit. The acknowledge bit is a HIGH signal put on the bus by the transmitter during which time the master generates an extra acknowledge related clock pulse. A slave receiver which is addressed must generate an acknowledge after the reception of each byte. A master receiver must also generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges must pull-down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse (set-up and hold times must be taken into consideration). A master receiver must signal an end-of-data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a STOP condition. Acknowledgement on the I<sup>2</sup>C-bus is illustrated in Fig.13.

## PCF8548

#### 11.2 I<sup>2</sup>C-bus protocol

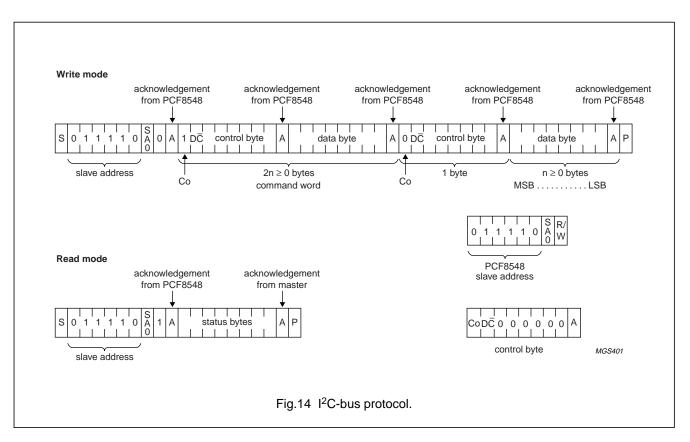

The PCF8548 supports command, data write and status read access.

Before any data is transmitted on the  $I^2$ C-bus, the device which should respond is addressed first. Two 7-bit slave addresses (0111100 and 0111101) are reserved for the PCF8548. The least significant bit of the slave address is set by connecting the input SA0 to either logic 0 (V<sub>SS1</sub>) or logic 1 (V<sub>DD1</sub>).

The I<sup>2</sup>C-bus protocol is illustrated in Fig.14.

The sequence is initiated with a START condition (S) from the l<sup>2</sup>C-bus master which is followed by the slave address. All slaves with the corresponding address acknowledge in parallel, all the others will ignore the l<sup>2</sup>C-bus transfer. After acknowledgement, one or more command words follow which define the status of the addressed slaves. A command word consists of a control byte, which defines Co and D/ $\overline{C}$ , plus a data byte (see Fig.14 and Table 1).

The last control byte is tagged with a cleared most significant bit (i.e. the continuation bit Co). After a control byte with a cleared Co bit, only data bytes will follow. The state of the  $D/\overline{C}$  bit defines whether the data byte is interpreted as a command or as RAM data.

The control and data bytes are also acknowledged by all addressed slaves on the bus.

After the last control byte, depending on the  $D/\overline{C}$  bit setting, either a series of display data bytes or command data bytes may follow. If the  $D/\overline{C}$  bit is set to logic 1, these display bytes are stored in the display RAM at the address specified by the data pointer. The data pointer is automatically updated and the data is directed to the intended PCF8548 device. If the  $D/\overline{C}$  bit of the last control byte is set to logic 0, these command bytes will be decoded and the setting of the device will be changed according to the received commands. The acknowledgement after each byte is made only by the addressed slave. At the end of the transmission the  $I^2C$ -bus master issues a STOP condition (P).

If the R/W bit is set to logic 1 the chip will output data immediately after the slave address if the  $D/\overline{C}$  bit, which was sent during the last write access, is set to logic 0. If no acknowledge is generated by the master after a byte, the driver stops transferring data to the master.

## PCF8548

#### 12 INSTRUCTIONS

The instruction format is divided into two modes:

- 1. If  $D/\overline{C}$  is set LOW, commands can be sent to the chip.

- 2. If  $D/\overline{C}$  is set HIGH, the DDRAM will be accessed.

Every instruction can be sent in any order to the PCF8548.

| Table 1Instruction set |

|------------------------|

|------------------------|

|                            | D/0 | DAT |                |                  | CC               |                  | ND BY            | TE               |                  |                  | DECODUCTION                                                                |

|----------------------------|-----|-----|----------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|----------------------------------------------------------------------------|

| INSTRUCTION                | D/C | R/W | B7             | B6               | B5               | B4               | B3               | B2               | B1               | B0               | DESCRIPTION                                                                |

| H = 0 or 1                 |     | 1   |                | 1                | 1                |                  | 1                |                  | 1                |                  |                                                                            |

| NOP                        | 0   | 0   | 0              | 0                | 0                | 0                | 0                | 0                | 0                | 0                | no operation                                                               |

| Reserved                   | 0   | 0   | 0              | 0                | 0                | 0                | 0                | 0                | 0                | 1                | do not use                                                                 |

| Function set               | 0   | 0   | 0              | 0                | 1                | MX               | MY               | PD               | V                | Н                | Power-down control; entry<br>mode; extended instruction<br>set control (H) |

| Read status byte           | 0   | 1   | PD             | TRS              | BRS              | D                | E                | MX               | MY               | DO               | read status byte                                                           |

| Write data                 | 1   | 0   | D <sub>7</sub> | D <sub>6</sub>   | D <sub>5</sub>   | D <sub>4</sub>   | D <sub>3</sub>   | D <sub>2</sub>   | D <sub>1</sub>   | D <sub>0</sub>   | writes data to RAM                                                         |

| H = 0                      |     |     | -              |                  |                  |                  |                  |                  |                  |                  |                                                                            |

| Reserved                   | 0   | 0   | 0              | 0                | 0                | 0                | 0                | 0                | 1                | Х                | do not use                                                                 |

| Set V <sub>LCD</sub> range | 0   | 0   | 0              | 0                | 0                | 0                | 0                | 1                | 0                | PRS              | V <sub>LCD</sub> programming range select                                  |

| Display control            | 0   | 0   | 0              | 0                | 0                | 0                | 1                | D                | 0                | Е                | sets display configuration                                                 |

| Set HV-gen<br>stages       | 0   | 0   | 0              | 0                | 0                | 1                | 0                | 0                | S1               | S0               | # of HV-gen voltage multiplication                                         |

| Set Y address of<br>RAM    | 0   | 0   | 0              | 1                | 0                | 0                | Y <sub>3</sub>   | Y <sub>2</sub>   | Y <sub>1</sub>   | Y <sub>0</sub>   | sets Y address of RAM: $0 \le Y \le 8$                                     |

| Set X address of<br>RAM    | 0   | 0   | 1              | X <sub>6</sub>   | X <sub>5</sub>   | X <sub>4</sub>   | X <sub>3</sub>   | X <sub>2</sub>   | X <sub>1</sub>   | X <sub>0</sub>   | sets X address of RAM: $0 \le X \le 101$                                   |

| H = 1                      |     | •   |                |                  |                  |                  |                  |                  | •                |                  |                                                                            |

| Reserved                   | 0   | 0   | 0              | 0                | 0                | 0                | 0                | 0                | 1                | Х                | do not use                                                                 |

| Temperature control        | 0   | 0   | 0              | 0                | 0                | 0                | 0                | 1                | TC <sub>1</sub>  | TC <sub>0</sub>  | set temperature coefficient<br>(TCx)                                       |

| Display configuration      | 0   | 0   | 0              | 0                | 0                | 0                | 1                | DO               | TRS              | BRS              | top/bottom row mode set data order                                         |

| Bias system                | 0   | 0   | 0              | 0                | 0                | 1                | 0                | BS <sub>2</sub>  | BS <sub>1</sub>  | BS <sub>0</sub>  | set bias system (BSx)                                                      |

| Reserved                   | 0   | 0   | 0              | 1                | Х                | Х                | Х                | Х                | Х                | Х                | do not use (reserved for test)                                             |

| Set V <sub>OP</sub>        | 0   | 0   | 1              | V <sub>OP6</sub> | V <sub>OP5</sub> | V <sub>OP4</sub> | V <sub>OP3</sub> | V <sub>OP2</sub> | V <sub>OP1</sub> | V <sub>OP0</sub> | write V <sub>OP</sub> to register                                          |

| BI                    | т  | 0                                          | 1                                       | RESET STATE                     |

|-----------------------|----|--------------------------------------------|-----------------------------------------|---------------------------------|

| PD                    |    | chip is active                             | chip is in Power-down mode              | 1                               |

| V                     |    | horizontal addressing                      | vertical addressing                     | 0                               |

| Н                     |    | use basic instruction set                  | use extended instruction set            | 0                               |

| MX                    |    | normal X addressing                        | X address is mirrored                   | 0                               |

| MY                    |    | display is not vertically mirrored         | display is vertically mirrored          | 0                               |

| TRS                   |    | top rows are not mirrored                  | top rows are mirrored                   | 0                               |

| BRS                   |    | bottom rows are not mirrored               | bottom rows are mirrored                | 0                               |

| DO                    |    | MSB is on top                              | LSB is on top                           | 0                               |

| PRS                   |    | V <sub>LCD</sub> programming range LOW     | V <sub>LCD</sub> programming range HIGH | 0                               |

| D and E               | 00 | display blank                              |                                         | D = 0                           |

|                       | 10 | normal mode                                |                                         | E = 0                           |

|                       | 01 | all display segments on                    |                                         |                                 |

|                       | 11 | inverse video mode                         |                                         |                                 |

| TC[1:0]               | 00 | V <sub>LCD</sub> temperature coefficient 0 |                                         | TC[1:0] = 00                    |

|                       | 01 | V <sub>LCD</sub> temperature coefficient 1 |                                         |                                 |

|                       | 10 | V <sub>LCD</sub> temperature coefficient 2 |                                         |                                 |

|                       | 11 | V <sub>LCD</sub> temperature coefficient 3 |                                         |                                 |

| S[1:0]                | 00 | $2 \times voltage multiplier$              |                                         | S[1:0] = 00                     |

|                       | 01 | $3 \times voltage multiplier$              |                                         |                                 |

|                       | 10 | $4 \times$ voltage multiplier              |                                         |                                 |

|                       | 11 | $5 \times voltage multiplier$              |                                         |                                 |

| BS[2:0]               |    | bias system                                |                                         | BS[2:0] = 000                   |

| V <sub>op</sub> [6:0] |    | V <sub>LCD</sub> programming               |                                         | V <sub>op</sub> [6:0] = 0000000 |

#### Table 2 Explanations of symbols in Table 1

#### 12.1 External reset (RES)

After power-on a reset pulse must be applied immediately to the chip, as it is in an undefined state. A reset of the chip can be achieved using the external reset pad. After the reset the LCD driver is set to the following states:

- Power-down mode (PD = 1)

- All LCD outputs at V<sub>SS</sub> (display off)

- Horizontal addressing (V = 0)

- Normal instruction set (H = 0)

- Normal display (MX = MY = TRS = BRS = 0)

- Display blank (E = D = 0)

- Address counter X[6:0] = 0 and Y[3:0] = 0

- Temperature coefficient (TC[1:0] = 0)

- Bias system (BS[2:0] = 0)

- V<sub>LCD</sub> is equal to 0, the HV generator is switched off (V<sub>op</sub>[6:0] = 0 and PRS = 0)

- After power-on (RAM data is undefined), the reset signal does not change the content of the RAM.

#### 12.2 Function set

12.2.1 POWER-DOWN (PD)

- All LCD outputs at V<sub>SS</sub> (display off)

- Bias generator and V<sub>LCD</sub> generator off

- Oscillator off (external clock possible)

- V<sub>LCD</sub> can be disconnected

- RAM contents not cleared (RAM data can be written)

- V<sub>LCD</sub> output is discharged to V<sub>SS</sub>.

#### 12.2.2 V

When V = 0, the horizontal addressing is selected. The data is written to the RAM as shown in Fig.4. When V = 1, the vertical addressing is selected. The data is written to the RAM as shown in Fig.5.

#### 12.2.3 H

When H = 0 the commands 'display control', 'set HV-gen stages', 'set Y address' and 'set X address' can be performed. When H = 1 the other commands can be executed. The commands 'write data' and 'function set' can be executed in both cases.

#### 12.2.4 MX

When MX = 0, the display RAM is written from left to right (X = 0 is on the left side of the display, X = 100 is on the right side of the display). When MX = 1 the display RAM is written from right to left (X = 0 is on the right side of the display, X = 100 is on the left side of the display).

Thus, if a horizontally mirroring of the display is desired the RAM must first be rewritten.

#### 12.2.5 MY

When MY = 1, the display is mirrored vertically.

A change of this bit has an immediate effect on the display.

#### 12.3 Display control

12.3.1 D AND E

The bits D and E select the display mode (see Table 2).

#### 12.4 Display configuration

#### 12.4.1 TRS

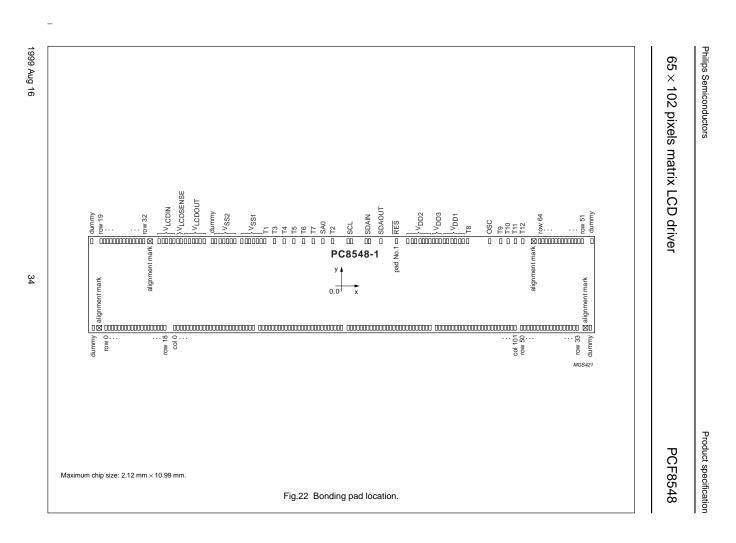

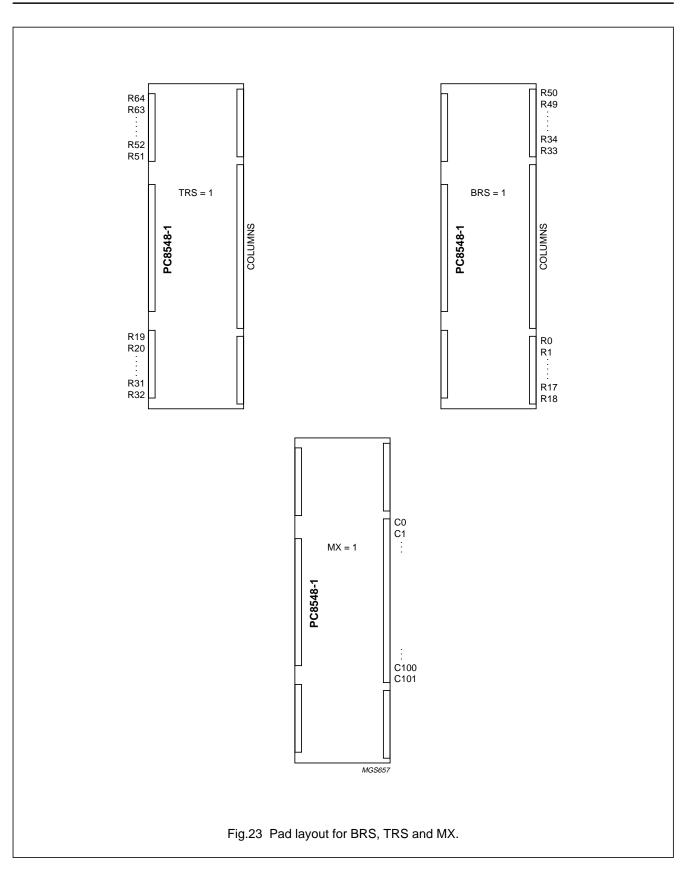

Bit TRS enables the top row pad blocks to be mirrored. This is used to enable flexibility in the wiring of the row lines from the PCF8548 to the LCD cell (e.g. COG or TCP wiring). When TRS = 0 rows 19 to 32 and rows 51 to 64 are organized as illustrated in Fig.22. When TRS = 1 rows 19 to 32 and rows 51 to 64 are mirrored and organized as illustrated in Fig.23.

#### 12.4.2 BRS

Bit BRS enables the bottom row pad blocks to be mirrored. This is used to enable flexibility in the wiring of the row lines from the PCF8548 to the LCD cell (e.g. COG or TCP wiring). When BRS = 0 rows 0 to 18 and rows 33 to 50 are organized as illustrated in Fig.22. When BRS = 1 rows 0 to 18 and rows 33 to 50 are mirrored and organized as illustrated in Fig.23.

#### 12.5 Set Y address of RAM

Y[3:0] defines the Y address vector address of the RAM.

|                |                | angee          |                |                              |                 |

|----------------|----------------|----------------|----------------|------------------------------|-----------------|

| Y <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> | CONTENT                      | ALLOWED X RANGE |

| 0              | 0              | 0              | 0              | bank 0 (display RAM)         | 0 to 101        |

| 0              | 0              | 0              | 1              | bank 1 (display RAM)         | 0 to 101        |

| 0              | 0              | 1              | 0              | bank 2 (display RAM)         | 0 to 101        |

| 0              | 0              | 1              | 1              | bank 3 (display RAM)         | 0 to 101        |

| 0              | 1              | 0              | 0              | bank 4 (display RAM)         | 0 to 101        |

| 0              | 1              | 0              | 1              | bank 5 (display RAM)         | 0 to 101        |

| 0              | 1              | 1              | 0              | bank 6 (display RAM)         | 0 to 101        |

| 0              | 1              | 1              | 1              | bank 7 (display RAM)         | 0 to 101        |

| 1              | 0              | 0              | 0              | bank 8 (display RAM); note 1 | 0 to 101        |

#### Table 3 X and Y address ranges

#### Note

1. In bank 8 only the MSB is accessed.

PCF8548

## $65 \times 102$ pixels matrix LCD driver

#### 12.6 Set X address of RAM

The X address points to the columns. The range of X is 0 to 101 (65H).

#### 12.7 Set HV generator stages

#### 12.7.1 S[1:0]

The PCF8548 incorporates a software configurable voltage multiplier. After reset the voltage multiplier is set to  $2 \times V_{DD2}$ . Other voltage multiplier factors are set via the command 'set HV-gen stages' (see Tables 1 and 2).

#### 12.8 Temperature control

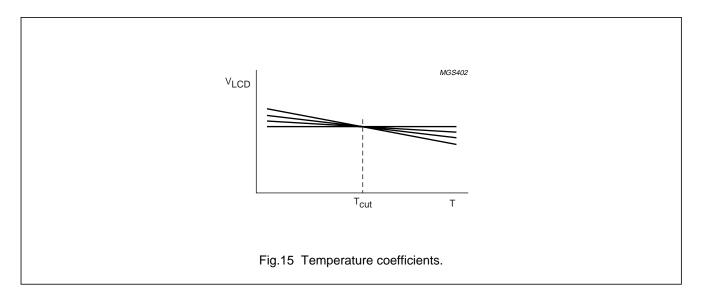

Due to the temperature dependency of the liquid crystals viscosity, the LCD controlling voltage  $V_{LCD}$  must be increased with lower temperature to maintain optimum contrast.

# There are 4 different temperature coefficients available in the PCF8548 (see Fig.15). The coefficients are selected by the two bits TC[1:0]. Table 6 shows the typical values of the different temperature coefficients. The coefficients are proportional to the programmed $V_{LCD}$ .

#### 12.9 Bias system

The Bias voltage levels are set in the ratio

of R - R - nR - R - R giving a  $\frac{1}{n+4}$  bias system.

The resulting bias levels are shown in Table 5.

Different multiplex rates require different factors n (see Table 4); this is programmed by BS[2 : 0]. For Mux 1 : 65 the optimum bias value n is given by:

$n = \sqrt{m} - 3 = \sqrt{65} - 3 = 5.06 = 5$  resulting in <sup>1</sup>/<sub>9</sub>bias.

| BS[2] | BS[1] | BS[0] | n | RECOMMENDED MUX RATE |

|-------|-------|-------|---|----------------------|

| 0     | 0     | 0     | 7 | 1 : 100              |

| 0     | 0     | 1     | 6 | 1 : 81               |

| 0     | 1     | 0     | 5 | 1 : 64               |

| 0     | 1     | 1     | 4 | 1 : 49               |

| 1     | 0     | 0     | 3 | 1 : 36               |

| 1     | 0     | 1     | 2 | 1 : 24               |

| 1     | 1     | 0     | 1 | 1 : 16               |

| 1     | 1     | 1     | 0 | 1:9                  |

#### Table 4 Programming the required bias system

Table 5 LCD bias voltage

| SYMBOL | BIAS VOLTAGES    | BIAS VOLTAGES<br>FOR <sup>1</sup> / <sub>9</sub> BIAS |

|--------|------------------|-------------------------------------------------------|

| V1     | V <sub>LCD</sub> | V <sub>LCD</sub>                                      |

| V2     | (n + 3)/(n + 4)  | $^{8}$ / <sub>9</sub> × V <sub>LCD</sub>              |

| V3     | (n + 2)/(n + 4)  | $7_{9} \times V_{LCD}$                                |

| V4     | 2/(n + 4)        | $^{2}$ / <sub>9</sub> × V <sub>LCD</sub>              |

| V5     | 1/(n + 4)        | $1_{9} \times V_{LCD}$                                |

| V6     | V <sub>SS</sub>  | V <sub>SS</sub>                                       |

#### 12.10 Set V<sub>OP</sub> value

The voltage at reference temperature can be calculated as:  $[V_{LCD} (T = T_{cut})]$

$$V_{LCD_{(Tcut)}} = (a + V_{OP} \times b)$$

(1)

The operating voltage  $V_{LCD}$  can be set by software. The generated voltage is dependent on the temperature, programmed Temperature Coefficient (TC) and the programmed voltage at reference temperature ( $T_{cut}$ ).  $V_{LCD} = (a + V_{OP} \times b) \times [1 + (T - T_{cut}) \times TC]$  (2) The parameters are explained in Fig.16 and Table 6. The maximum voltage that can be generated is dependent on the V<sub>DD2</sub> voltage and the display load current. Two overlapping V<sub>LCD</sub> ranges are selectable via the command 'HV-gen control'. For the LOW (PRS = 0) range  $a = a_1$  and for the HIGH (PRS = 1) range  $a = a_2$  with steps equal to b in both ranges. It should be noted that the charge pump is turned off if V<sub>OP</sub>[6;0] and bit PRS are all set to zero. For Mux 1 : 65 the optimum operation voltage of the liquid can be calculated as follows:

$$V_{LCD} = \frac{1 + \sqrt{65}}{\sqrt{2 \times \left(1 - \frac{1}{\sqrt{65}}\right)}} \times V_{th} = 6.85 \times V_{th}$$

where  $V_{\text{th}}$  is the threshold voltage of the liquid crystal material used.

| Table 6         Typical values for parameters for the HV-generator programmi |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

| SYMBOL           | BITS | VALUE          | UNIT |

|------------------|------|----------------|------|

| a <sub>1</sub>   |      | 2.94 (PRS = 0) | V    |

| a <sub>2</sub>   |      | 6.75 (PRS = 1) | V    |

| b                |      | 0.03           | V    |

| T <sub>cut</sub> |      | 27             | ٥C   |

## VLCD no off a<sub>2</sub> charge pui a'ı 0H '01H '02H '03H '04H '05H '06H '... '5FH '6FH '7FH '00H '01H '02H '03H '04H '05H '06H '... '5FH '6FH '7FH LOW (PRS = 0) -- HIGH (PRS = 1) MGS658 $V_{\mbox{OP}}\mbox{[6:0]}$ (programmed); 00H to 7FH, programme range LOW and HIGH. Fig.16 V<sub>OP</sub> programming of PCF8548.

As the programming range for the internally generated V<sub>LCD</sub> allows values above the maximum allowed V<sub>LCD</sub> (9.0 V) the customer must ensure while setting the V<sub>OP</sub> register and selecting the temperature coefficient, under all conditions and including all tolerances V<sub>LCD</sub> remains below 9.0 V.

#### 13 LIMITING VALUES

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134); parameters are valid over operating temperature range unless otherwise specified; all voltages referenced to  $V_{SS} = 0$  V. Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

| SYMBOL             | PARAMETER                                     | MIN. | MAX.                  | UNIT |

|--------------------|-----------------------------------------------|------|-----------------------|------|

| V <sub>DD1</sub>   | supply voltage                                | -0.5 | +6.5                  | V    |

| $V_{DD2}, V_{DD3}$ | supply voltage for internal voltage generator | -0.5 | +4.5                  | V    |

| V <sub>LCD</sub>   | supply voltage for the LCD                    | -0.5 | +9.0                  | V    |

| I <sub>SS</sub>    | supply current                                | -50  | +50                   | mA   |

| V <sub>i(n)</sub>  | all input voltages                            | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| l <sub>l</sub>     | DC input current                              | -10  | +10                   | mA   |

| I <sub>O</sub>     | DC output current                             | -10  | +10                   | mA   |

| P <sub>pack</sub>  | power dissipation per package                 | -    | 300                   | mW   |

| P/out              | power dissipation per output                  | -    | 30                    | mW   |

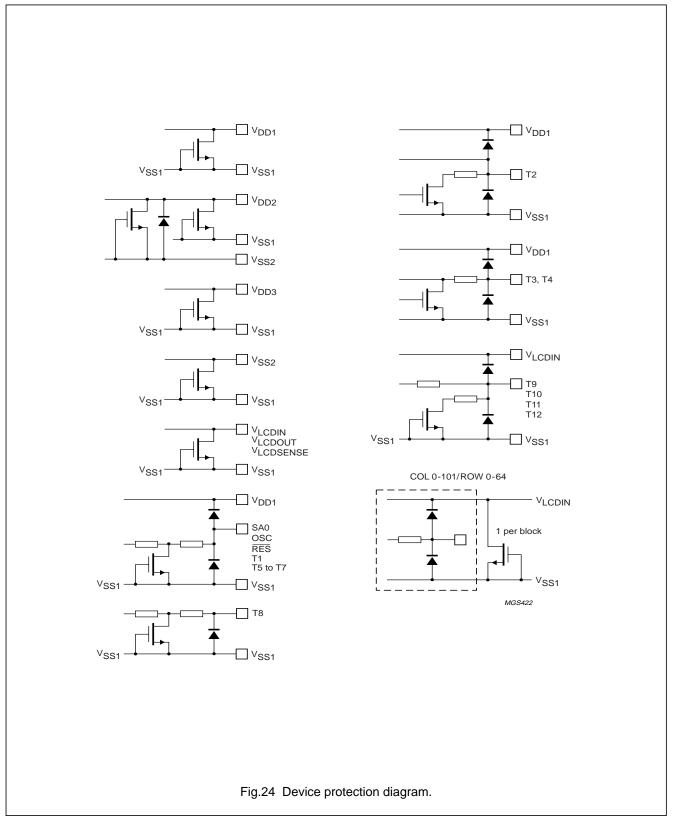

#### 14 HANDLING

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices (see "Handling MOS Devices").

#### 15 DC CHARACTERISTICS

$V_{DD1}$  = 1.9 to 5.5 V;  $V_{DD2}$  and  $V_{DD3}$  = 2.4 to 4.5 V;  $V_{SS1}$  and  $V_{SS2}$  = 0 V;  $V_{LCD}$  = 4.5 to 9.0 V;  $T_{amb}$  = -40 to +85 °C; unless otherwise specified.

| SYMBOL                             | PARAMETER                                           | CONDITIONS                                                                                                                                                                                              | MIN. | TYP. | MAX. | UNIT |

|------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>DD1</sub>                   | supply voltage                                      |                                                                                                                                                                                                         | 1.9  | -    | 5.5  | V    |

|                                    |                                                     | $T_{amb} = -25 \text{ to } +85 ^{\circ}\text{C}$                                                                                                                                                        | 1.8  | -    | 5.5  | V    |

| V <sub>DD2</sub> ,V <sub>DD3</sub> | supply voltage for<br>internal voltage<br>generator | LCD voltage internally<br>generated (voltage generator<br>enabled)                                                                                                                                      | 2.4  | -    | 4.5  | V    |

| V <sub>LCDIN</sub>                 | LCD input supply voltage                            | LCD voltage externally<br>supplied (voltage generator<br>disabled)                                                                                                                                      | 4.5  | _    | 9.0  | V    |

| V <sub>LCDOUT</sub>                | LCD output supply voltage                           | LCD voltage internally<br>generated (voltage generator<br>enabled); note 1                                                                                                                              | 4.5  | -    | 9.0  | V    |

| I <sub>DD1</sub>                   | supply current                                      | $V_{DD1} = 2.8 \text{ V}; V_{LCD} = 7.6 \text{ V};$<br>$f_{sclk} = 0; T_{amb} = 25 \text{ °C};$<br>notes 2 and 3                                                                                        | _    | 20   | _    | μΑ   |

| I <sub>DD2</sub> ,I <sub>DD3</sub> | supply current for                                  | with external V <sub>LCD</sub>                                                                                                                                                                          | -    | 0.5  | -    | μA   |

|                                    | internal voltage<br>generator                       | with internal V <sub>LCD</sub> generation;<br>V <sub>DD1</sub> = 2.8 V; V <sub>LCD</sub> = 7.6 V;<br>$f_{sclk} = 0$ ; $T_{amb} = 25 \text{ °C}$ ; no<br>display load; 4 × charge pump;<br>notes 2 and 3 | _    | 180  | _    | μΑ   |

## PCF8548

| SYMBOL                 | PARAMETER                                          | CONDITIONS                                                                                                                                                                                           | MIN.                | TYP.                     | MAX.                | UNIT |

|------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|---------------------|------|

| I <sub>DD(tot)</sub>   | total supply current                               | with internal V <sub>LCD</sub> generation;<br>V <sub>DD1</sub> = 2.8 V; V <sub>LCD</sub> = 7.6 V;<br>$f_{sclk}$ = 0; T <sub>amb</sub> = 25 °C; no<br>display load; 4 × charge pump;<br>notes 2 and 3 | -                   | 200                      | 350                 | μA   |

|                        |                                                    | (Power-down mode) with internal or external $V_{LCD}$ generation; note 4                                                                                                                             | _                   | 1.5                      | 10                  | μA   |

| I <sub>LCDIN</sub>     | supply current from external V <sub>LCD</sub>      | $V_{DD1} = 2.8 V; V_{LCD} = 7.6 V;$<br>$f_{sclk} = 0; T_{amb} = 25 °C; no$<br>display load; notes 2, 3 and 5                                                                                         | _                   | 30                       | _                   | μA   |

| Logic                  |                                                    |                                                                                                                                                                                                      |                     |                          |                     |      |

| V <sub>IL</sub>        | LOW-level input voltage                            |                                                                                                                                                                                                      | V <sub>SS1</sub>    | -                        | 0.3V <sub>DD1</sub> | V    |

| V <sub>IH</sub>        | HIGH-level input voltage                           |                                                                                                                                                                                                      | 0.7V <sub>DD1</sub> | -                        | V <sub>DD1</sub>    | V    |

| IL                     | leakage current                                    | $V_i = V_{DD1}$ or $V_{SS1}$                                                                                                                                                                         | -1                  | -                        | +1                  | μA   |

| Column an              | d row outputs                                      |                                                                                                                                                                                                      | •                   | •                        |                     |      |

| R <sub>row</sub>       | row output resistance<br>R0 to R64                 | $V_{DD1}$ to $V_{DD3}$ = 5.0 V;<br>$V_{LCD}$ = 7.6 V; $I_{L}$ = 10 $\mu$ A;<br>outputs tested one at a time                                                                                          | _                   | 12                       | 20                  | kΩ   |

| R <sub>col</sub>       | column output<br>resistance C0 to C101             | V <sub>LCD</sub> = 7.6 V                                                                                                                                                                             | -                   | 12                       | 20                  | kΩ   |

| V <sub>bias(col)</sub> | column bias tolerance<br>C0 to C101                |                                                                                                                                                                                                      | -100                | 0                        | +100                | mV   |

| V <sub>bias(row)</sub> | row bias tolerance<br>R0 to R64                    |                                                                                                                                                                                                      | -100                | 0                        | +100                | mV   |

| LCD suppl              | y voltage generator                                |                                                                                                                                                                                                      |                     |                          |                     |      |

| V <sub>LCD</sub>       | V <sub>LCD</sub> tolerance<br>internally generated | $V_{DD1} = 2.8 \text{ V}; V_{LCD} = 7.6 \text{ V};$<br>$f_{sclk} = 0; T_{amb} = 25 \text{ °C};$<br>no display load;<br>notes 2, 3 6 and 7                                                            | -300                | 0                        | +300                | mV   |

| тс                     | temperature coefficient                            | 00                                                                                                                                                                                                   | -                   | -0.0 × 10 <sup>-3</sup>  | -                   | 1/°C |

|                        |                                                    | 01                                                                                                                                                                                                   | -                   | $-0.76 \times 10^{-3}$   | -                   | 1/°C |

|                        |                                                    | 10                                                                                                                                                                                                   | _                   | -1.05 × 10 <sup>-3</sup> | -                   | 1/°C |

|                        |                                                    | 11                                                                                                                                                                                                   | _                   | -2.10 × 10 <sup>-3</sup> | _                   | 1/°C |

#### Notes

- 1. The maximum possible V<sub>LCD</sub> voltage that can be generated is dependent on voltage, temperature and (display) load.

- 2. Internal clock.

- 3. When  $f_{sclk} = 0$  there is no l<sup>2</sup>C-bus clock.

- 4. Power-down mode. During power-down all static currents are switched off.

- 5. If external V<sub>LCD</sub>, the display load current is not transmitted to I<sub>DD</sub>.

- 6. Tolerance depends on the temperature; (typically zero at T<sub>amb</sub> = 27 °C), maximum tolerance values are measured at the temperature range limit.

- 7. For TC0 to TC3.

## PCF8548

#### **16 AC CHARACTERISTICS**

$V_{DD1}$  = 1.9 to 5.5 V;  $V_{DD2}$  and  $V_{DD3}$  = 2.4 to 4.5 V;  $V_{SS1}$  and  $V_{SS2}$  = 0 V;  $V_{LCD}$  = 4.5 to 9 V;  $T_{amb}$  = -40 to +85 °C; unless otherwise specified.

| SYMBOL                   | PARAMETER                                        | CONDITIONS                                                    | MIN.                   | TYP. | MAX. | UNIT |

|--------------------------|--------------------------------------------------|---------------------------------------------------------------|------------------------|------|------|------|

| f <sub>OSC</sub>         | oscillator frequency                             | V <sub>DD1</sub> = 2.8 V;<br>T <sub>amb</sub> = -20 to +70 °C | 20                     | 38   | 70   | kHz  |

| f <sub>clk(ext)</sub>    | external clock frequency                         |                                                               | 20                     | 38   | 100  | kHz  |

| f <sub>frame</sub>       | frame frequency                                  | $f_{OSC}$ or $f_{clk(ext)} = 38$ kHz;<br>note 1               | -                      | 73   | -    | Hz   |

| t <sub>VHRL</sub>        | V <sub>DD1</sub> to RES LOW                      | see Fig.17 and note 2                                         | 0                      | _    | 1    | μs   |

| t <sub>W(RES)</sub>      | RES LOW pulse width                              | see Fig.17 and note 3                                         | 100                    | -    | -    | ns   |

| I <sup>2</sup> C-bus tin | ning characteristics; see note 4                 |                                                               |                        |      | •    | •    |

| f <sub>SCLK</sub>        | SCL clock frequency                              |                                                               | 0                      | -    | 400  | kHz  |

| t <sub>SCLL</sub>        | SCL clock LOW period                             |                                                               | 1.3                    | -    | -    | μs   |

| t <sub>SCLH</sub>        | SCL clock HIGH period                            |                                                               | 0.6                    | -    | -    | μs   |

| t <sub>SU;DAT</sub>      | data set-up time                                 |                                                               | 100                    | -    | -    | ns   |

| t <sub>HD;DAT</sub>      | data hold time                                   |                                                               | 0                      | —    | 0.9  | μs   |

| t <sub>r</sub>           | SCL and SDA rise time                            | note 5                                                        | 20 + 0.1C <sub>b</sub> | -    | 300  | ns   |

| t <sub>f</sub>           | SCL and SDA fall time                            | note 5                                                        | 20 + 0.1C <sub>b</sub> | -    | 300  | ns   |

| t <sub>f(SDA)(ro)</sub>  | SDA fall time for read out                       | V <sub>DD1</sub> = <3.6 V                                     | 20 + 0.1C <sub>b</sub> | -    | 1000 | ns   |

| C <sub>b</sub>           | capacitive load represented by each bus line     |                                                               | -                      | -    | 400  | pF   |

| t <sub>SU;STA</sub>      | set-up time for a repeated START condition       |                                                               | 0.6                    | -    | -    | μs   |

| t <sub>HD;STA</sub>      | START condition hold time                        |                                                               | 0.6                    | -    | -    | μs   |

| t <sub>SU;STO</sub>      | set-up time for STOP condition                   |                                                               | 0.6                    | -    | -    | μs   |

| t <sub>SW</sub>          | tolerable spike width on bus                     | note 6                                                        | -                      | -    | 50   | ns   |

| t <sub>BUF</sub>         | bus free time between a STOP and START condition |                                                               | 1.3                    | -    | -    | μs   |

#### Notes

1.

$$f_{frame} = \frac{f_{clk(ext)}}{520}$$

- 2. RES may be LOW before  $V_{DD1}$  goes HIGH.

- 3. If  $t_{W(RES)}$  is longer than 3 ns (typical) a reset may be generated.

- All timing values are valid within the operating supply voltage and ambient temperature ranges and are referenced to V<sub>IL</sub> and V<sub>IH</sub> with an input voltage swing of V<sub>SS</sub> to V<sub>DD</sub>.

- 5. The rise and fall times specified here refer to the driver device (i.e. not PCF8548) and are part of the general fast I<sup>2</sup>C-bus specification. When PCF8548 asserts an acknowledge on SDA, the minimum fall time is 10 ns.  $C_b$  = capacitive load per bus line.

- 6. The device inputs SDA and SCL are filtered and will reject spikes on the bus lines of width <t<sub>SW(max)</sub>.

PCF8548

## $65\times102$ pixels matrix LCD driver

#### **18 APPLICATION INFORMATION**

#### Table 7 Programming example for PCF8548

| 0755 |    |    |    | Bľ                  | тѕ      |    |    |    |         |                                                                                                                                       |

|------|----|----|----|---------------------|---------|----|----|----|---------|---------------------------------------------------------------------------------------------------------------------------------------|

| STEP | B7 | B6 | B5 | B4                  | B3      | B2 | B1 | B0 | DISPLAY | OPERATION                                                                                                                             |

| 1    |    |    |    | l <sup>2</sup> C-bu | s start |    |    |    |         |                                                                                                                                       |

| 2    | 0  | 1  | 1  | 1                   | 1       | 0  | 0  | 0  |         | slave address for write                                                                                                               |

| 3    | 0  | 0  | 0  | 0                   | 0       | 0  | 0  | 0  |         | control byte with cleared Co bit and $D/\overline{C}$ set to logic 0                                                                  |

| 4    | 0  | 0  | 1  | 0                   | 0       | 0  | 0  | 1  |         | function set; $PD = 0$ ; $V = 0$ ;<br>select extended instruction<br>set (H = 1 mode)                                                 |

| 5    | 0  | 0  | 0  | 1                   | 0       | 0  | 1  | 0  |         | set bias system 2; this is the<br>recommended bias system<br>for a multiplex rate 1 : 65                                              |

| 6    | 1  | 1  | 1  | 0                   | 1       | 0  | 1  | 0  |         | set $V_{OP}$ ; $V_{OP}$ is set to a<br>+106 × b [V]; it should be<br>noted that the required<br>voltage is dependent on the<br>liquid |

| 7    | 0  | 0  | 1  | 0                   | 0       | 0  | 0  | 0  |         | function set; $PD = 0$ ; $V = 0$ ;<br>select normal instruction set<br>(H = 0 mode)                                                   |

| 8    | 0  | 0  | 0  | 0                   | 1       | 1  | 0  | 0  |         | display control; set normal<br>mode (D = 1; E = 0)                                                                                    |

| 9    |    |    |    | l <sup>2</sup> C-bu | s start |    |    |    |         | restart; to write into the display RAM the $D/\overline{C}$ must be set to logic 1; therefore a control byte is needed                |

| 10   | 0  | 1  | 1  | 1                   | 1       | 0  | 0  | 0  |         | slave address for write                                                                                                               |

| 11   | 0  | 1  | 0  | 0                   | 0       | 0  | 0  | 0  |         | control byte with cleared Co bit and $D/\overline{C}$ set to logic 1                                                                  |

| 12   | 1  | 1  | 1  | 1                   | 1       | 0  | 0  | 0  | MGS405  | data write; Y and X are<br>initialized to 0 by default, so<br>they are not set here                                                   |

| 13   | 1  | 0  | 1  | 0                   | 0       | 0  | 0  | 0  | MGS406  | data write                                                                                                                            |

| 0755 |    |    |    | Bľ                  | TS       |    |    |    |         |                                                                     |

|------|----|----|----|---------------------|----------|----|----|----|---------|---------------------------------------------------------------------|

| STEP | B7 | B6 | B5 | B4                  | B3       | B2 | B1 | B0 | DISPLAY | OPERATION                                                           |

| 14   | 1  | 1  | 1  | 0                   | 0        | 0  | 0  | 0  | MGS407  | data write                                                          |

| 15   | 0  | 0  | 0  | 0                   | 0        | 0  | 0  | 0  | MGS408  | data write                                                          |

| 16   | 1  | 1  | 1  | 1                   | 1        | 0  | 0  | 0  | MGS409  | data write                                                          |

| 17   | 0  | 0  | 1  | 0                   | 0        | 0  | 0  | 0  | MGS410  | data write                                                          |

| 18   | 1  | 1  | 1  | 1                   | 1        | 0  | 0  | 0  | MGS411  | data write                                                          |

| 19   |    |    |    | I <sup>2</sup> C-bu | ls start |    |    |    |         | restart                                                             |

| 20   | 0  | 1  | 1  | 1                   | 1        | 0  | 0  | 0  |         | slave address for write                                             |

| 21   | 1  | 0  | 0  | 0                   | 0        | 0  | 0  | 0  |         | control byte with set Co bit and $D/\overline{C}$ set to logic 0    |

| 22   | 0  | 0  | 0  | 0                   | 1        | 1  | 0  | 1  | MGS412  | display control; set inverse<br>video mode (D = 1; E = 1)           |

| 23   | 1  | 0  | 0  | 0                   | 0        | 0  | 0  | 0  |         | control byte with set Co bit<br>and $D/\overline{C}$ set to logic 0 |

| 24   | 1  | 0  | 0  | 0                   | 0        | 0  | 0  | 0  | MGS413  | set X address of RAM; set<br>address to '0000000'                   |

| 0755 |    |    |    | Bľ                  | тѕ       |    |    |    |         |                                                                      |

|------|----|----|----|---------------------|----------|----|----|----|---------|----------------------------------------------------------------------|

| STEP | B7 | B6 | B5 | B4                  | B3       | B2 | B1 | B0 | DISPLAY | OPERATION                                                            |

| 25   | 1  | 1  | 0  | 0                   | 0        | 0  | 0  | 0  |         | control byte with set Co bit and $D/\overline{C}$ set to logic 1     |

| 26   | 0  | 0  | 0  | 0                   | 0        | 0  | 0  | 0  | MGS414  | data write                                                           |

| 27   | 0  | 0  | 0  | 0                   | 0        | 0  | 0  | 0  |         | control byte with cleared Co bit and $D/\overline{C}$ set to logic 0 |

| 28   | 1  | 0  | 0  | 0                   | 0        | 0  | 0  | 0  | MGS415  | set X address of RAM; set<br>address to '0000000'                    |

| 29   |    |    |    | l <sup>2</sup> C-bu | is start |    |    |    |         | restart                                                              |

| 30   | 0  | 1  | 1  | 1                   | 1        | 0  | 0  | 0  |         | slave address for write                                              |

| 31   | 1  | 1  | 0  | 0                   | 0        | 0  | 0  | 0  |         | control byte with set Co bit and $D/\overline{C}$ set to logic 1     |

| 32   | 1  | 1  | 1  | 1                   | 1        | 0  | 0  | 0  | MGS416  | write data                                                           |

| 33   | 1  | 0  | 0  | 0                   | 0        | 0  | 0  | 0  |         | control byte with set Co bit and $D/\overline{C}$ set to logic 0     |

## PCF8548

The pinning of the PCF8548 is optimized for single plane wiring e.g. for chip-on-glass display modules, or for TCP. Display size:  $65 \times 102$  pixels. The required minimum value for the external capacitors in an application with the PCF8548 are:  $C_{VDD}$ ,  $C_{VDD1}$ ,  $C_{VDD2}$  and  $C_{VLCD} = 1.0 \ \mu\text{F}$  (min.). Higher capacitor values are recommended for ripple reduction.

To reduce the sensitivity of the reset to ESD/EMC disturbances for a COG application, it is strongly recommended to implement on the glass (ITO) a series input resistance in the reset line (The recommended minimum value is  $8 \text{ k}\Omega$ ).

#### **19 CHIP INFORMATION**

The PCF8548 is manufactured in n-well CMOS technology. The substrate is at  $V_{SS}$  potential.

#### 20 PAD INFORMATION

| PAD                           | VALUE                         | UNIT |

|-------------------------------|-------------------------------|------|

| Minimum bump pitch            | 70                            | μm   |

| Pad size, alumin              | 62×100                        | μm   |

| Bumps                         | 50 (±6) × 90 (±6) × 17.5 (±5) | μm   |

| Wafer thickness without bumps | U/2 = 381; U/9 = 525          | μm   |

## PCF8548

#### Table 8 Bonding pad location All x and y coordinates are referenced to the centre of the chip (dimension in $\mu\text{m};$ see Fig.22).

| SYMBOL                | PAD | x     | У      | SYMBOL    | P/ |

|-----------------------|-----|-------|--------|-----------|----|

| RES                   | 1   | +1160 | +899.4 | R32       | 4  |

| SDAOUT                | 2   | +840  | +899.4 | R31       | 4  |

| SDAIN                 | 3   | +600  | +899.4 | R30       | 4  |

| SDAIN                 | 4   | +520  | +899.4 | R29       | 4  |

| SCL                   | 5   | +200  | +899.4 | R28       | 4  |

| SCL                   | 6   | +120  | +899.4 | R27       | 4  |

| T2                    | 7   | -200  | +899.4 | R26       | 4  |

| SA0                   | 8   | -410  | +899.4 | R25       | 4  |

| T7                    | 9   | -620  | +899.4 | R24       | 4  |

| Т6                    | 10  | -830  | +899.4 | R23       | 5  |

| T5                    | 11  | -1040 | +899.4 | R22       | 5  |

| T4                    | 12  | -1250 | +899.4 | R21       | 5  |

| Т3                    | 13  | -1460 | +899.4 | R20       | 5  |

| T1                    | 14  | -1670 | +899.4 | R19       | 5  |

| V <sub>SS1</sub>      | 15  | -1750 | +899.4 | dummy pad | 5  |

| V <sub>SS1</sub>      | 16  | -1830 | +899.4 | dummy pad | 5  |

| V <sub>SS1</sub>      | 17  | -1910 | +899.4 | R0        | 5  |

| V <sub>SS1</sub>      | 18  | -1990 | +899.4 | R1        | 5  |

| V <sub>SS1</sub>      | 19  | -2070 | +899.4 | R2        | 5  |

| V <sub>SS1</sub>      | 20  | -2150 | +899.4 | R3        | 6  |

| V <sub>SS2</sub>      | 21  | -2310 | +899.4 | R4        | 6  |