### INTEGRATED CIRCUITS

# DATA SHEET

# SA1638 Low voltage IF I/Q transceiver

**Product specification**

1997 Sept 03

IC17 Data Handbook

### Low voltage IF I/Q transceiver

**SA1638**

#### **DESCRIPTION**

The SA1638 is a combined Rx and Tx IF I/Q circuit. The receive path contains an IF amplifier, a pair of quadrature down-mixers, and a pair of baseband filters and amplifiers. A second pair of mixers in the transmit path transposes a quadrature baseband input up to the IF frequency. An external VCO signal is divided down internally and buffered to provide quadrature local oscillator signals for the mixers. A further divider chain, reference divider and phase detector are provided to avoid the need for an external IF synthesizer. Rx or Tx path or the entire circuit may be powered down by logic inputs. On-board voltage regulators are provided to allow direct connection to a battery supply.

#### **FEATURES**

- Direct supply: 3.3V to 7.5V

- Two DC regulators giving 3.0V output

- Low current consumption: 18mA for Rx or 22mA for Tx

- Input/output IF frequency from 70-400 MHz

- Internal IF PLL for synthesizing the local oscillator signal

- High performance on-board integrated receive filters with bandwidth tunable between 50-850 kHz

- Switchable alternative bandwidth setting available to allow channel bandwidth flexibility in operation

- Designed for a widely used I and Q baseband GSM interface

- Control registers power up in a default state

- Optional DC offset trim capability to <200mV</li>

- Only a standard reference input frequency required, choice of 13, 26, 39 or 52MHz

- Fully compatible with SA1620 GSM RF front-end (see Figure 9)

#### **APPLICATIONS**

- IF circuitry for GSM 900MHz hand-held units

- IF circuitry for PCN (DCS1800) hand-held units

- Quadrature up and down mixer stage

#### **PIN CONFIGURATION**

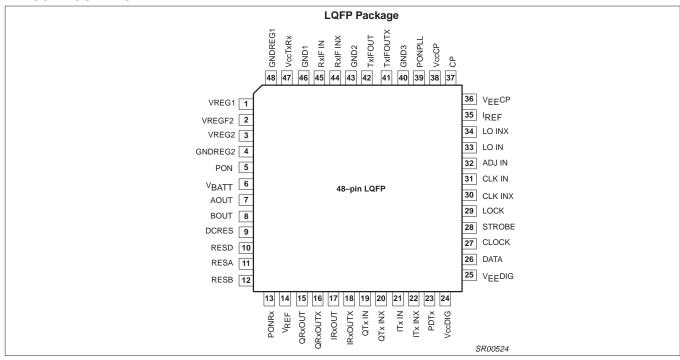

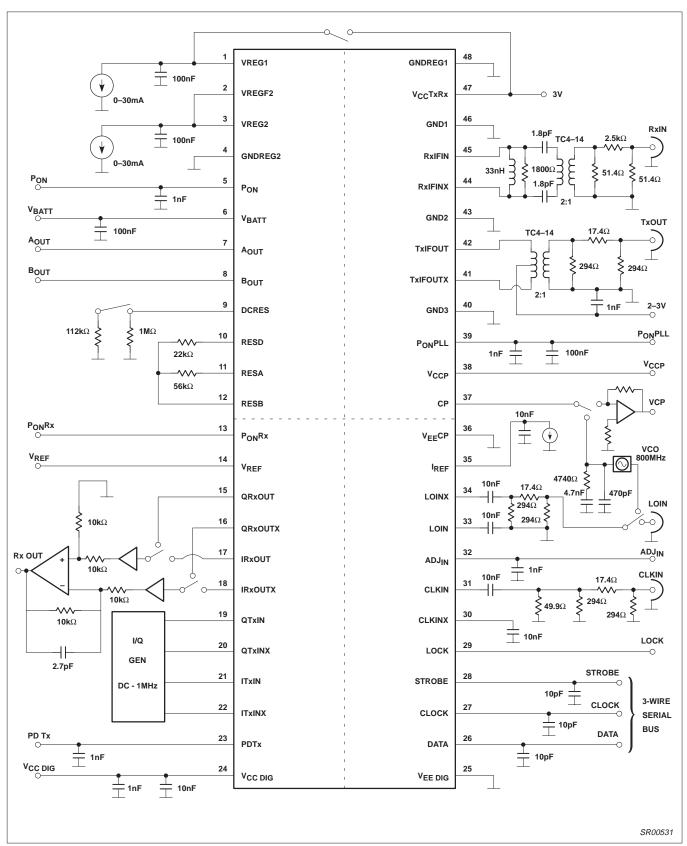

Figure 1. SA1638 Pin Configuration

#### ORDERING INFORMATION

| DESCRIPTION                       | TEMPERATURE RANGE | ORDER CODE | DWG #    |

|-----------------------------------|-------------------|------------|----------|

| 48-Pin Thin Quad Flat Pack (LQFP) | -40 to +85°C      | SA1638BE   | SOT313-2 |

SA1638

#### **BLOCK DIAGRAM**

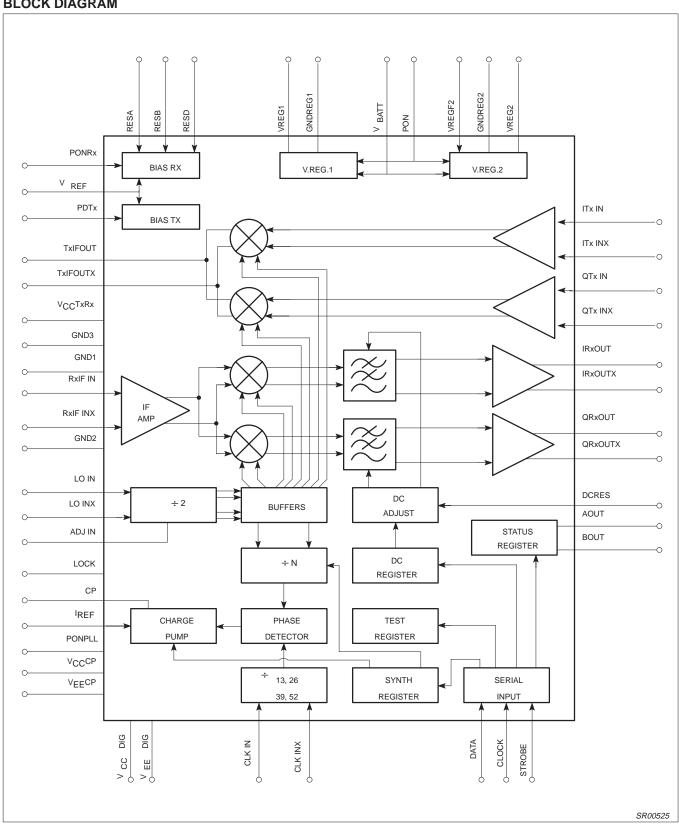

Figure 2. SA1638 Block Diagram

# Low voltage IF I/Q transceiver

SA1638

### **PIN DESCRIPTIONS**

| Pin No. | Pin Name             | Description                                                                 |

|---------|----------------------|-----------------------------------------------------------------------------|

| 1       | VREG1                | Output voltage of regulator 1                                               |

| 2       | VREGF2               | Feedback of regulator 2                                                     |

| 3       | VREG2                | Output voltage of regulator 2                                               |

| 4       | GNDREG2              | Ground of regulator 2                                                       |

| 5       | PON                  | Power-on input for voltage regulators 1 and 2 (active high)                 |

| 6       | $V_{BATT}$           | Input voltage for regulators 1 and 2                                        |

| 7       | AOUT                 | Programmable logic output (see Figure 9)                                    |

| 8       | BOUT                 | Programmable logic output (see Figure 9)                                    |

| 9       | DCRES                | Reference current setting resistor for DC offset circuit                    |

| 10      | RESD                 | Additional external current defining resistor for filters                   |

| 11      | RESA                 | Principal external current defining resistor for filters                    |

| 12      | RESB                 | Principal external current defining resistor for filters                    |

| 13      | PONRx                | Power-on input for Rx (active high)                                         |

| 14      | V <sub>REF</sub>     | Reference voltage                                                           |

| 15      | QRxOUT               | Differential receive baseband output                                        |

| 16      | QRxOUTX              | Differential receive baseband output                                        |

| 17      | IRxOUT               | Differential receive baseband output                                        |

| 18      | IRXOUTX              | Differential receive baseband output                                        |

| 19      | QTx IN               | Differential transmit baseband input                                        |

| 20      | QTx INX              | Differential transmit baseband input                                        |

| 21      | ITx IN               | Differential transmit baseband input  Differential transmit baseband input  |

| 22      | ITx INX              | Differential transmit baseband input                                        |

| 23      | PDTx                 | Power-on for transmitter (active low)                                       |

|         |                      | · · · · · · · · · · · · · · · · · · ·                                       |

| 24      | V <sub>CC</sub> DIG  | Digital circuit supply                                                      |

| 25      | V <sub>EE</sub> DIG  | Digital ground                                                              |

| 26      | DATA                 | Serial bus data input                                                       |

| 27      | CLOCK                | Serial bus clock input                                                      |

| 28      | STROBE               | Serial bus strobe input                                                     |

| 29      | LOCK                 | Test control/synthesizer lock indicator                                     |

| 30      | CLK INX              | Differential reference divider input                                        |

| 31      | CLK IN               | Differential reference divider input                                        |

| 32      | ADJ IN               | Used for test only. Do not connect                                          |

| 33      | LO IN                | Differential LO input                                                       |

| 34      | LO INX               | Differential LO input                                                       |

| 35      | I <sub>REF</sub>     | Reference current setting for charge pump                                   |

| 36      | V <sub>EE</sub> CP   | Charge pump ground                                                          |

| 37      | СР                   | Charge pump output                                                          |

| 38      | V <sub>CC</sub> CP   | Charge pump circuit supply                                                  |

| 39      | POnPLL               | Power-on input for synthesizer circuits (active high)                       |

| 40      | GND3                 | Ground (internal connection to GND1 and GND2)                               |

| 41      | TxIFOUTX             | Differential transmit IFoutput (open collector)                             |

| 42      | TxIFOUT              | Differential transmit IFoutput (open collector)                             |

| 43      | GND2                 | Ground (internal connection to GND1 and GND3)                               |

| 44      | RxIF INX             | Differential receive IF input                                               |

| 45      | RxIF IN              | Differential receive IF input                                               |

| 46      | GND1                 | Ground (internal connection to GND2 and GND3)                               |

| 47      | V <sub>CC</sub> TxRx | Transmit and receive circuits supply voltage (also feedback of Regulator 1) |

| 48      | GNDREG1              | Ground of regulator 1                                                       |

NOTE: There are no ESD protection diodes at Pins 41 and 42. Thus, open collector outputs may have increased DC voltage or higher AC peak voltage.

# Low voltage IF I/Q transceiver

SA1638

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL              | PARAMETER                                                                      | RATING                            | UNITS |

|---------------------|--------------------------------------------------------------------------------|-----------------------------------|-------|

| V <sub>CC</sub> XXX | Supply voltages: V <sub>CC</sub> TxRx, V <sub>CC</sub> DIG, V <sub>CC</sub> CP | -0.3 to +6.0                      | V     |

| V <sub>BATT</sub>   | Battery voltage                                                                | -0.3 to +8.0                      | V     |

| V <sub>IN</sub>     | Voltage applied to any other pin                                               | -0.3 to (V <sub>CCXXX</sub> +0.3) | V     |

| ΔVG                 | Any GND pin to any other GND pin                                               | 0                                 | V     |

| P <sub>D</sub>      | Power dissipation, T <sub>A</sub> = 25°C (still air)                           | 300                               | mW    |

| T <sub>JMAX</sub>   | Maximum operating junction temperature                                         | 150                               | °C    |

| P <sub>MAX</sub>    | Maximum power input/output                                                     | +20                               | dBm   |

| T <sub>STG</sub>    | Storage temperature range                                                      | -65 to +150                       | °C    |

#### NOTE:

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL              | PARAMETER                                                  | RATING     | UNITS |

|---------------------|------------------------------------------------------------|------------|-------|

| V <sub>CC</sub> XXX | Supply voltages: V <sub>CC</sub> TxRx, V <sub>CC</sub> DIG | 2.7 to 5.5 | V     |

| V <sub>CC</sub> CP  | Charge pump supply voltage                                 | 2.9 to 5.5 | V     |

| V <sub>BATT</sub>   | Battery voltage                                            | 3.3 to 7.5 | V     |

| T <sub>A</sub>      | Operating ambient temperature range                        | -40 to +85 | °C    |

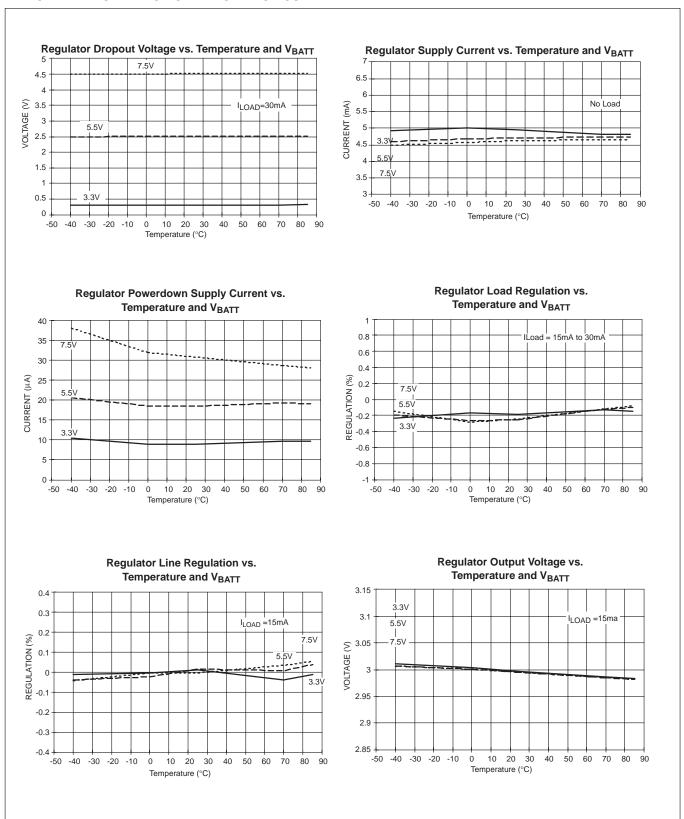

#### **Voltage Regulators**

$T_A = 25^{\circ}\text{C}, \ P_{ON} = 3\text{V}, \ P_{ON}\text{RX} = 0\text{V}, \ PDTX = 3\text{V}, \ P_{ON}\text{PLL} = 0\text{V}, \ V_{BATT} = 3.3\text{V}, \ I_{OUT}1 = I_{OUT}2 = 15\text{mA}, \ V_{REG}1 \ \text{connected to } V_{CC}\text{TxRx}, \ V_{REG}2 \ \text{connected to } V_{REG}\text{F2}; \ V_{CC}\text{DIG} = V_{CC}\text{CP} = 3\text{V}; \ \text{unless otherwise stated}.$

| CVMDOL                                    | DADAMETED                                                        | TEST COMPLIANC                                                                                                         |            |             | LIMITS                           |             |      | UNITS |

|-------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------|-------------|----------------------------------|-------------|------|-------|

| SYMBOL                                    | PARAMETER                                                        | TEST CONDITIONS                                                                                                        | Min        | <b>−3</b> σ | Тур                              | <b>+3</b> σ | Max  | UNITS |

| V <sub>REG</sub> 1,<br>V <sub>REG</sub> 2 | Nominal V <sub>OUT</sub>                                         |                                                                                                                        | 2.85       | 2.93        | 3.00                             | 3.07        | 3.15 | V     |

| V <sub>BATT</sub>                         |                                                                  |                                                                                                                        | 3.3        |             |                                  |             | 7.5  | V     |

| I <sub>OUT</sub> 1, I <sub>OUT</sub> 2    | Maximum output current for each regulator <sup>1</sup>           |                                                                                                                        |            |             |                                  |             | 30   | mA    |

| I <sub>BATT</sub>                         | Supply current for both regulators                               | $I_{LOAD} = 0mA$                                                                                                       |            | 4.3         | 5                                | 5.7         | 7    | mA    |

| I <sub>BATT PD</sub>                      | Power-down supply current                                        | $P_{ON} = 0V$ , $I_{LOAD} = 0mA$                                                                                       |            | 7.7         | 9                                | 10.3        | 15   | μΑ    |

| C <sub>REG</sub> 1 <sup>2</sup>           | V <sub>REG</sub> 1 cap load                                      |                                                                                                                        | 0.1        |             |                                  |             | 1000 | μF    |

| C <sub>REG</sub> 2 <sup>2</sup>           | V <sub>REG</sub> 2 cap load                                      |                                                                                                                        | 0.1        |             |                                  |             | 500  | μF    |

| LINEREG                                   | Line regulation                                                  | DC, $V_{BATT} = 3.3V$ to 7.5V                                                                                          | -0.4       | -0.2        | 0.001                            | 0.2         | 0.4  | %     |

| LOADREG                                   | Load regulation                                                  | I <sub>LOAD</sub> = 15mA to 30mA                                                                                       | <b>-</b> 5 | -0.37       | -0.17                            | 0.03        | 5    | %     |

| BW                                        | Bandwidth                                                        |                                                                                                                        | 100        |             |                                  |             |      | kHz   |

| F <sub>PON</sub>                          | Feedthrough attenuation from P <sub>ON</sub> to each regulator   |                                                                                                                        |            |             | ≤ -40                            |             |      | dB    |

| F <sub>REG</sub>                          | Feedthrough attenuation from V <sub>BATT</sub> to each regulator | $\begin{split} &f \leq 100 \text{kHz} \\ &f = 10 \text{MHz} \\ &f = 100 \text{MHz} \\ &f = 400 \text{MHz} \end{split}$ |            |             | ≤ -61<br>≤ -32<br>≤ -37<br>≤ -48 |             |      | dB    |

| t <sub>ON</sub>                           | Turn ON time                                                     |                                                                                                                        |            |             | 10                               |             |      | μs    |

#### NOTES

- 1. At  $T_i \ge 150$ °C a thermal switch reduces the output current to avoid damage.

- 2. Recommended load capacitors: In every case  $C_{REG}1 = C_{REG}2 = 100$ nF to ground with series resistance  $\le 0.1\Omega$ . Additional capacitor optional  $\le 1000\mu$ F with series resistance  $\le 5\Omega$ . The low series resistance is very important to ensure regulator stability.

5

3. Standard deviations are based on the characterization results of 90 ICs.

<sup>1.</sup> Maximum dissipation is determined by the operating ambient temperature and the thermal resistance,  $\theta_{JA}$ . 48-pin LQFP:  $\theta_{JA} = 67^{\circ}$ C/W.

# Low voltage IF I/Q transceiver

SA1638

#### DC ELECTRICAL CHARACTERISTICS

$V_{CC} \\ \\ TxRx = V_{CC} \\ \\ DIG = V_{CC} \\ \\ CP = PONRx = PONPLL \\ \\ +3V; \\ V_{EE} \\ DIG = V_{EE} \\ \\ CP = GND1 \\ \\ = GND2 \\ \\ = GND3 \\ \\ = DTx \\ \\ = 0V; \\ T_A = 25 \\ \\ \\ C, \\ \\ unless \\ \\ otherwise \\ \\ stated. \\ \\ DTx = 0V \\ \\ T_A = 25 \\ \\ \\ C, \\ \\ unless \\ \\ otherwise \\ \\ stated. \\ \\ unless \\ \\ otherwise \\ \\ stated. \\ \\ unless \\ \\ otherwise \\ \\ \\ otherwise \\ \\ otherwise \\ \\ \\ otherwise \\ \\ otherwise \\ \\ \\ otherwis$

| SYMBOL            | DADAMETED                                                             | TEST CONDITIONS                    |                         |             | LIMITS |             |                     | UNITS |

|-------------------|-----------------------------------------------------------------------|------------------------------------|-------------------------|-------------|--------|-------------|---------------------|-------|

| STWBOL            | PARAMETER                                                             | TEST CONDITIONS                    | MIN                     | <b>−3</b> σ | TYP    | <b>+3</b> σ | MAX                 | UNIIS |

|                   | Supply current                                                        |                                    |                         |             |        |             |                     |       |

|                   | Rx and IF synthesizer active                                          | PONRx = PONPLL = PDTx = Hi         |                         | 14.4        | 16     | 17.6        | 20                  |       |

| Icc               | Tx and IF synthesizer active                                          | PONRx = PDTx = Low;<br>PONPLL = Hi |                         | 17.4        | 19.5   | 21.6        | 24                  | mA    |

|                   | Power-down mode                                                       | PONRx = PONPLL = Low;<br>PDTx = Hi |                         |             | 0.068  |             |                     |       |

| $V_{REF}$         | Reference voltage                                                     | Generated internally               |                         | 1.39        | 1.57   | 1.75        |                     | V     |

| IV <sub>REF</sub> | V <sub>REF</sub> I <sub>SINK</sub><br>I <sub>SOURCE</sub>             |                                    |                         |             | 5<br>5 |             |                     | μΑ    |

| I <sub>OUT</sub>  | DC output current                                                     | At pins TxIFOUT and TxIFOUTX       | 1.5                     | 1.86        | 2.0    | 2.14        | 2.7                 | mA    |

| Digital inp       | uts (P <sub>ON</sub> )                                                |                                    | -                       |             |        |             |                     |       |

| V <sub>IH</sub>   | High level input voltage range                                        |                                    | 2.0                     |             |        |             | $V_{BATT}$          | V     |

| $V_{IL}$          | Low level input voltage range                                         |                                    | 0                       |             |        |             | 0.8                 | V     |

| Digital inp       | uts (PDTx, P <sub>ON</sub> Rx, P <sub>ON</sub> PLL, P <sub>ON</sub> ) |                                    |                         |             |        |             |                     |       |

| V <sub>IH</sub>   | High level input voltage range                                        |                                    | 2.0                     |             |        |             | $V_{CC}TxRx$        | V     |

| V <sub>IL</sub>   | Low level input voltage range                                         |                                    | 0                       |             |        |             | 0.8                 | V     |

| Digital inp       | uts (Clock, Data, Strobe)                                             |                                    |                         |             |        |             |                     |       |

| V <sub>IH</sub>   | High level input voltage range                                        |                                    | 2.0                     |             |        |             | V <sub>CC</sub> Dig | V     |

| $V_{IL}$          | Low level input voltage range                                         |                                    | 0                       |             |        |             | 0.8                 | V     |

| Digital out       | puts (LOCK, AOUT, BOUT)                                               |                                    |                         |             |        |             |                     |       |

| V <sub>OH</sub>   | Output voltage HIGH                                                   | I <sub>O</sub> = -2mA              | V <sub>CC</sub> DIG-0.4 |             |        |             |                     | V     |

| $V_{OL}$          | Output voltage LOW                                                    | $I_O = 2mA$                        |                         |             |        |             | 0.4                 | V     |

#### **AC ELECTRICAL CHARACTERISTICS**

$V_{CC}TxRx = V_{CC}DIG = V_{CC}CP = PONRx = PONPLL = +3V; \ V_{EE}DIG = V_{EE}CP = GND1 = GND2 = GND3 = PDTx = 0V; \ LO_{IN} = 100mV_{PEAK}, 800MHz; \ CLK_{IN} = 100mV_{PEAK}, 52MHz; \ serial registers programmed with default values; \ T_A = 25^{\circ}C \ unless otherwise stated. \ Test Circuit Figure 8.$

| CVMDOL            | DADAMETED                              | TEST COMPITIONS                                               |     |             | LIMI | TS          |                          | LINUTO |

|-------------------|----------------------------------------|---------------------------------------------------------------|-----|-------------|------|-------------|--------------------------|--------|

| SYMBOL            | PARAMETER                              | TEST CONDITIONS                                               | MIN | <b>−3</b> σ | TYP  | <b>+3</b> σ | MAX                      | UNITS  |

| IF Transm         | it Modulator                           |                                                               |     |             |      |             |                          |        |

| BW                | Input modulation bandwidth             | 200Ω source impedance                                         |     | 0.82        | 0.94 | 1.06        |                          | MHz    |

| V <sub>COM</sub>  | Common mode range for baseband inputs  | DC at pins ITxIN, ITxINx, QTxIN, QTxINx                       | 1   |             | 1.5  |             | 2                        | V      |

| V <sub>IN</sub>   | Peak input signal amplitude            | Centered on V <sub>COM</sub>                                  |     |             | 0.75 |             |                          | V      |

|                   | Third harmonic distortion <sup>1</sup> |                                                               |     | -61         | -57  | -53         | -40                      | dB     |

| R <sub>INTx</sub> | Input resistance                       | resistance Between pins: ITxIn and ITxInX or QTxIn and QTxInX |     |             | kΩ   |             |                          |        |

| C <sub>INTx</sub> | Input capacitance                      | At ITxIn, ITxInX,<br>QTxIn, QTxInX                            |     |             |      |             | 10                       | pF     |

|                   | Output saturation limit                |                                                               |     |             |      |             | V <sub>CC</sub> TxRx-0.3 | V      |

| I <sub>OUT</sub>  | RMS output current                     |                                                               | 0.6 |             |      | 1.08        | mA                       |        |

| S <sub>LO</sub>   | LO suppression <sup>1</sup>            |                                                               |     | dB          |      |             |                          |        |

| SSB               | Sideband suppression <sup>1</sup>      |                                                               | +35 |             | +50  |             |                          | dB     |

SA1638

### AC ELECTRICAL CHARACTERISTICS (Continued)

| SYMBOL             | PARAMETER                                                            | TEST CONDITIONS                                                                |                        | _                       | LIMITS                         | _                      | _                      | UNITS         |

|--------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------|-------------------------|--------------------------------|------------------------|------------------------|---------------|

|                    | Transmit Modulator (continued)   Noise density at 600kHz             | TEST CONDITIONS                                                                | MIN                    | <b>−3</b> σ             | TYP                            | <b>+3</b> σ            | MAX                    | OMITS         |

| IF Transm          | it Modulator (continued)                                             |                                                                                | _                      |                         |                                |                        |                        |               |

|                    | ·                                                                    | ITxIn  =  ITxInX  =  QTxIn  =                                                  |                        | -130                    | -129                           | -128                   |                        | dBc/Hz        |

|                    | Noise density at 10MHz                                               | $ QTxInX  = 0.75V_{PEAK}$                                                      |                        | -133                    | -131                           | -129                   |                        | GDC/TIZ       |

| t <sub>ON</sub>    |                                                                      | PdTx = LO, transmit signal to 90%                                              |                        |                         | 5                              |                        |                        | μs            |

| t <sub>OFF</sub>   | Turn OFF time                                                        | PdTx = HI, transmit signal to 10%                                              |                        |                         | 5                              |                        |                        | μs            |

| IF Receive         | er (R = 36k $\Omega$ between pins RESA ar                            | -                                                                              |                        |                         |                                |                        |                        |               |

| RInRx              | Differential input impedance                                         | f <sub>IN</sub> = 400MHz                                                       |                        |                         | 5    0.6                       |                        |                        | kΩ    pF      |

| ROutRx             | Output impedance                                                     |                                                                                |                        |                         | 1                              |                        |                        | kΩ            |

|                    | Output common mode voltage                                           |                                                                                |                        |                         | $V_{REF}$                      |                        |                        | V             |

| f3dB               |                                                                      |                                                                                | 70                     |                         | 83                             |                        | 90                     | kHz           |

|                    | 200kHz<br>400kHz<br>600kHz<br>6.5MHz                                 |                                                                                | 6.5<br>30              | 8.9<br>38.1             | 10.7<br>45<br>70<br>>80<br>>80 | 12.5<br>51.9           |                        | dB            |

| VG                 | Voltage gain                                                         | Differential output PD into GSM baseband relative to 1200Ω source EMF          | 43                     | 49.4                    | 51                             | 52.7                   | 58                     | dB            |

| NF                 | Noise figure <sup>8</sup>                                            | 1200Ω source and external matching resistor and inductor                       |                        | 5.7                     | 7.0                            | 8.3                    |                        | dB            |

|                    | Gain                                                                 | f <sub>IN</sub> = 400.005MHz                                                   | -1.5                   |                         | -0.26<br>0.0                   |                        | 1.5                    | dB<br>degrees |

|                    | Output DC offset <sup>2</sup>                                        | Differential, DCRES=562kΩ                                                      | -60                    |                         | -25                            |                        | 60                     | mV            |

| I <sub>OUT</sub>   | Output drive current at each pin                                     | Source (Sink)                                                                  |                        |                         | 10 (700)                       |                        |                        | μΑ            |

| V <sub>OUT</sub>   | Minimum differential output swing                                    |                                                                                |                        |                         | 2.0                            |                        |                        | V             |

| P <sub>-1dB</sub>  | In band<br>200kHz<br>400kHz                                          | 1200Ω source EMF                                                               | -59<br>-54             | -55.3<br>-49.3          | -53<br>-47<br>-47<br>-47       | -50.7<br>-44.8         | -47<br>-40             | dBV           |

| t <sub>ON</sub>    | Turn ON time <sup>3</sup>                                            | POnRx = HI, to baseband signal out                                             |                        |                         | 2                              |                        |                        | μs            |

| t <sub>OFF</sub>   | Turn OFF time                                                        | POnRx = LO, to no baseband signal out                                          |                        |                         | 2                              |                        |                        | μs            |

| IF Synthes         | sizer                                                                |                                                                                | _                      |                         |                                |                        | _                      |               |

| f <sub>LO</sub>    |                                                                      |                                                                                | 140                    |                         |                                |                        | 800                    | MHz           |

| Z <sub>LOIN</sub>  | Differential input impedance                                         | Between pins LO <sub>IN</sub> and LO <sub>IN</sub> X, f <sub>IN</sub> = 800MHz |                        |                         | 276    0.6                     |                        |                        | Ω    pF       |

| $V_{LOIN}$         | LO peak input voltage range                                          | Single-ended Referred to $50\Omega$                                            | 50                     |                         |                                |                        | 100                    | mV            |

|                    | Programmable divider:<br>Division range<br>Step size                 |                                                                                | 64                     |                         | 1                              |                        | 511                    |               |

| f <sub>CLKIN</sub> | Reference clock input frequency                                      | $V_{CLKIN} = 100 \text{mV}_{PEAK}$                                             |                        |                         |                                |                        | 52                     | MHz           |

| Z <sub>CLKIN</sub> | Differential input impedance                                         | Between pins Clkln and ClklnX                                                  |                        |                         | 10    1.0                      |                        |                        | kΩ    pF      |

| $V_{CLKIN}$        | CLK <sub>IN</sub> peak input voltage range                           | Single-ended, referred to $50\Omega$                                           | 50                     |                         |                                |                        | 400                    | mV            |

| I <sub>REF</sub>   | Charge pump input reference current                                  |                                                                                |                        |                         | 31.2                           |                        |                        | μА            |

| I <sub>CP</sub>    | Charge pump output current:<br>c0c2 = 000<br>c0c2 = 111<br>Step size | $I_{REF} = 31.2\mu A,$ $V_{CP} = V_{CC}CP/2$                                   | 0.425<br>0.85<br>0.045 | 0.487<br>0.979<br>0.062 | 0.5<br>1.0<br>0.071            | 0.513<br>1.021<br>0.08 | 0.575<br>1.15<br>0.105 | mA            |

#### AC ELECTRICAL CHARACTERISTICS (Continued)

| SYMBOL                         | DADAMETED                                      | TEST CONDITIONS                                                                                 |     |             | LIMITS |             |     | UNITS |

|--------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-------------|--------|-------------|-----|-------|

| STIMBUL                        | PARAMETER                                      | TEST CONDITIONS                                                                                 | MIN | <b>−3</b> σ | TYP    | <b>+3</b> σ | MAX | UNITS |

| IF Synthes                     | sizer (cont.)                                  |                                                                                                 |     |             |        |             |     |       |

| $\frac{\Delta I_{CP}}{I_{CP}}$ | Relative output current variation <sup>4</sup> | I <sub>REF</sub> =31.2μA                                                                        |     | 0.1         | 1.3    | 2.5         | ±10 | %     |

| Δl <sub>CP_M</sub>             | Output current matching <sup>5</sup>           | $I_{REF}$ =31.2 $\mu$ A,<br>$V_{CP}$ = $V_{CC}$ CP/2                                            |     |             |        |             | ±12 | %     |

| I <sub>CP_L</sub>              | Output leakage current                         | $V_{CP} = 0.3V$ to $V_{CC}CP-0.3V$                                                              |     | -0.02       | 0.1    | 0.22        | ±15 | nA    |

| t <sub>ON</sub>                | Turn ON time                                   | POnPLL = HI, to full charge pump current                                                        |     |             | 15     |             |     | μs    |

| t <sub>OFF</sub>               | Turn OFF time <sup>6</sup>                     | POnPLL = LO, to I <sub>CC</sub> CP,<br>I <sub>CC</sub> DIG <5% of operational<br>supply current |     |             | 15     |             |     | μs    |

| Serial Inte                    | rface <sup>7</sup>                             |                                                                                                 |     |             |        |             |     |       |

| fclock                         | Clock frequency                                |                                                                                                 |     |             |        |             | 10  | MHz   |

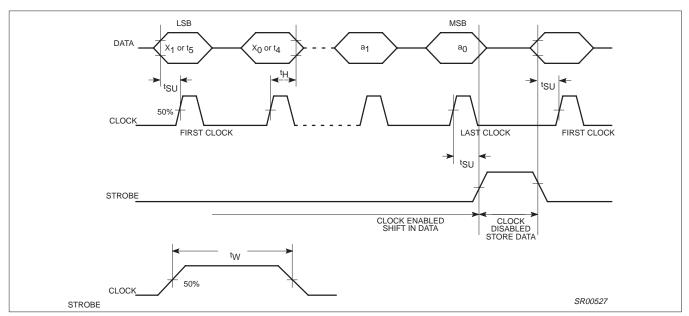

| t <sub>SU</sub>                | Set-up time: DATA to CLOCK,<br>CLOCK to STROBE |                                                                                                 | 30  |             |        |             |     | ns    |

| t <sub>H</sub>                 | Hold time: CLOCK to DATA                       |                                                                                                 | 30  |             |        |             |     | ns    |

| t <sub>W</sub>                 | Pulse width: CLOCK                             |                                                                                                 | 30  |             |        |             |     | ns    |

| ۲۷۷                            | Pulse width: STROBE                            |                                                                                                 | 30  |             |        |             |     | 113   |

- 1. Parameter measured relative to modulation sideband amplitude.

- After programming the DC offset register for minimum offset. DCRES =  $562k\Omega$ .

- The turn on time relates only to the power up time of the circuit. The settling time of the integrated baseband filters has to be added (for GSM-mode =  $8\mu s$  with filter bandwidth setting resistor =  $36k\Omega$ ).

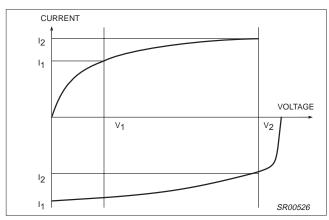

- $\frac{\Delta I_{OUT}}{I_{OUT}} = 2 \cdot \frac{(I_2 I_1)}{|(I_2 + I_1)|}; \text{ with } V_1 = 0.3V, V_2 = V_{CC}CP 0.3V \text{ (see Figure 3)}.$ 4. The relative output current variation is defined thus:

- 5. The output current matching is measured when both (positive current and negative current) sections of the output charge pumps are on.

- As soon as P<sub>ON</sub>PLL is set to LO, the phase detector is reset and no charge pumps pulses are generated.

- 7. Guaranteed by design.

- where,  $E_{no}$  is the output noise voltage measured in a 1Hz bandwidth,  $R = 1200\Omega$ , VG = gain in dB. 8. NF =

- 9. Minimium frequency is guaranteed by design.

Figure 3. Relative Output Current Variation

#### **FUNCTIONAL DESCRIPTION Serial Programming Input**

The serial input is a 3-wire input (CLOCK, STROBE, DATA) to program the counter ratios, charge pump current, status- and DC-offset register, mode select and test register. The programming data is structured into two 21-bit words; each word includes 4 chip

address bits and 1 subaddress bit. Figure 2 shows the timing diagram of the serial input. When the STROBE = L, the clock driver is enabled and on the positive edges of the CLOCK the signal on DATA input is clocked into a shift register. When the STROBE = H, the clock is disabled and the data in the shift register remains stable. Depending on the value of the subaddress bit the data is latched into different working registers. Table 3 shows the contents of each word.

#### **Default States**

Upon power up (V<sub>CC</sub>DIG is applied) a reset signal is generated, which sets all registers to a default state. The logic level at the STROBE pin should be low during power up to guarantee a proper reset. These default states are shown in Table 3.

#### Reference Divider

The reference divider can be programmed to four different division ratios (:13, :26, :39, :52), see registers r0, r1; default setting: divide by 13.

#### **Main Divider**

The external VCO signal, applied to the LO<sub>IN</sub> and LO<sub>IN</sub>X inputs, is divided by two and then fed to the main divider (:N). The main divider is a programmable 9 bit divider, the minimum division ratio is

SA1638

divide by 64. The division ratio is binary coded and set in the registers n0 to n8. The default setting is a divide by 400.

At the completion of a main divider cycle, a main divider output is generated which will drive the phase detector.

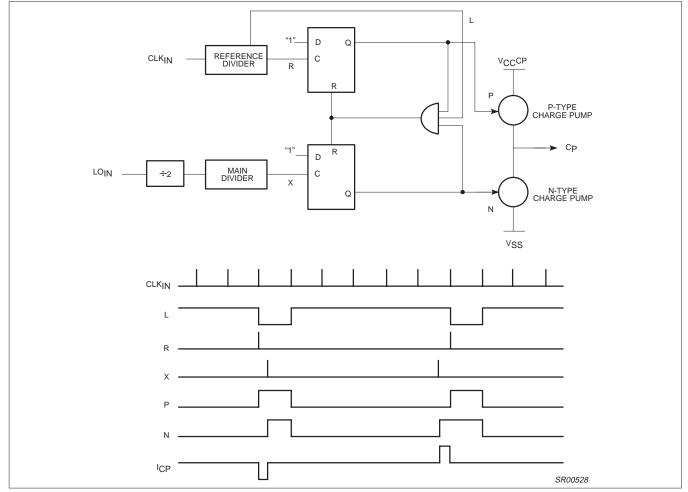

#### **Phase Detector**

The phase detector is a D-type flip-flop phase and frequency detector shown in Figure 5. The flip-flops are set by the negative edges of the output signals of the dividers. The rising edge of the signal L will reset the flip-flops after both flip-flops have been set. Around zero phase error this has the effect of delaying the reset for 1 reference input cycle. This avoids non-linearity or deadband around zero phase error. The flip-flops drive on-chip charge pumps. A source current from the charge pump acts to increase the VCO frequency; a sink current acts to decrease the VCO frequency.

#### **Current Setting**

The charge pump current is defined by the current set between the pin  $I_{REF}$  and  $V_{EE}CP$ . The current value to be set there is 31.2 $\mu A$ . This current can be set by an external resistor to be connected between the pin  $I_{REF}$  and  $V_{EE}CP$ . The typical value  $R_{EXT}$  (current setting resistor) can be calculated with the formula

$$R_{EXT}~=~\frac{V_{CC}CP-1.4V}{31.2\mu A}$$

The current can be set to zero by connecting the pin I<sub>REF</sub> to V<sub>CC</sub>CP.

#### **Charge Pumps**

The charge pumps at pin CP are driven by the phase dectector and the current value is determined by the binary value of the charge pumps register CN = c2, c1, c0, default 1mA. The active charge pump current is typically:

$$|I_{CP}| = (c0 + 2c1 + 4c2) \cdot 71\mu A + 500\mu A$$

#### **Lock Detect**

The output LOCK is H when the phase detector indicates a lock condition. This condition is defined as a phase difference of less than  $\pm 1$  cycle on the reference input CLK<sub>IN</sub>, CLK<sub>IN</sub>X.

#### **Test Modes (Synthesizer, Transmit Mixer)**

The LOCK output is selectable as a test output. Bits x0, x1 control the selection, the default setting is normal lock output as described in the Lock detect section. The selection of a Bit x0, x1 combination has a twofold effect: First it routes a divider output signal to the LOCK pin, second it disables mixer stages in the transmit path. Setting x0,1 = 11 disables both transmit path mixers. This mode can be used to prevent the transmitter from producing an IF output signal even if the transmit part is powered on (PDTx = 0V). This can be used to simplify the control timing while commanding the transmit and receive simultaneously without the transmit part causing interference.

Table 1. Test Modes

| x0 | x1 | Synthesizer Signal                                      | Transmit Mixer |         |  |  |  |

|----|----|---------------------------------------------------------|----------------|---------|--|--|--|

| ΧU | XI | at LOCK Pin                                             | Q-mixer        | I-mixer |  |  |  |

| 0  | 0  | normal lock detect                                      | on             | on      |  |  |  |

| 1  | 0  | CLK <sub>IN</sub> divided by reference<br>divider ratio | off            | on      |  |  |  |

| 0  | 1  | LO <sub>IN</sub> ÷ 2 * (main divider ratio)             | on             | off     |  |  |  |

| 1  | 1  | main divider output, that goes to the phase detector    | off            | off     |  |  |  |

#### **Status Register**

The s0 and s1 status bits determine the values of the logic output pins  $A_{OUT}$  and  $B_{OUT}$ . These outputs can be connected to the AGC control inputs A and B of the SA1620. (See Figure 9)

#### **DC Offset Register**

Registers i0 to i3 and q0 to q3 control a correction to the output DC offset of the I and Q channels of the receiver. The polarity of the DC offset correction in the I and Q channels are determined by i0 and q0, respectively. The other bits set the magnitude of the offset correction. The step size of the two offset correction DACs is fixed by an external resistor between the DCRES pin and ground. A value of  $120 \text{k}\Omega$  will give a step size of 200 mV.

#### **Mode Select Register**

t0: switches the RX IF gain.

t0 = 0 no attenuation t0 = 1 10dB attenuation

The attenuation switch is included between the IF amplifier and the I and Q mixers, thereby influencing the noise figure negligibly. The purpose of this switch is to provide another AGC step which does not influence the receiver noise figure. Please note that this gain change will influence the DC offset of the I and Q mixers.

t1 = 0 test mode only, always to be set to 0.

t2, t3 sets the mode of the level locked loop (LLL)

The LLL is a circuit which processes the LO input signal in order to provide an LO signal with a perfect 50% duty cycle, which determines the precision of the  $90^\circ$  shift of the I and Q mixing signals generated by the  $\div 2$  divider. For an external tuning of the  $90^\circ$  phase shift of the I and Q mixing signals, a trimming resistor may be connected (but is not required) between the ADJ\_IN pin and ground, and the LLL has to be put in one of the following modes:

Table 2. Mode Select Register

| t2 | t3 | LLL Status                                              |

|----|----|---------------------------------------------------------|

| 0  | 0  | LLL on (no external tune, monitor performance, default) |

| 0  | 1  | LLL on (with medium external tune)                      |

| 1  | 0  | LLL off (tune externally)                               |

| 1  | 1  | LLL on (with fine external tune)                        |

selects the bandwidth of the RC low pass filters at the I, Q Rx mixer outputs

t4 = 0 cutt-off frequency (-3dB) 110kHz

t4 = 1 cutt-off frequency (-3dB) 792kHz selects the bandwidth of the integrated 5th-order gyrator filters. The filters are tuneable over a range of 50kHz to 1MHz with external resistors. The -3dB bandwidth is inversely proportional to the value of the external resistor.

With

t5, two external resistor values are selectable.

t5 = 0 the resistance between the pins RESA and RESB determines the cutoff frequency. For GSM a nominal bandwidth of 80kHz is chosen when the external resistor is  $36k\Omega$ .

t5 = 1 a second resistor between the pins RESB and RESD is connected in parallel to the first external resistor, thus increasing the filter bandwidth. The relative amplification is decreased in this mode.

### Low voltage IF I/Q transceiver

SA1638

The overall filter response in the receive section is the sum of the filter responses of the passive RC low-pass filter and the active gyrator filter.

#### **Power Down Modes**

There are 4 power-on pins in the SA1638:  $P_{ON}$ ,  $P_{ON}Rx$ , PDTx,  $P_{ON}PLL$ .

$P_{ON}$  = H powers up both voltage regulators  $V_{REG}1$  and  $V_{REG}2.\ P_{ON}$  should be set to L, if these internal voltage regulators are not to be used.

$P_{ON}Rx = H$  powers up the receiver part.

PDTx = L powers up the transmitter part.

$P_{ON}PLL = H$  powers up the synthesizer part. As it also powers up the first divide by 2 stage for generating the 0/90 degree phase shifted signals for the transmit and receive mixers, it also has to be set H if either the transmit part or the receive part is used.  $P_{ON}PLL = L$  powers down the dividers, resets the phase detector and disconnects the current setting pin  $I_{REF}.\ In\ P_{ON}PLL = L$  mode, the values in the serial input registers are still kept and the part still can be reprogrammed as long as  $V_{CC}DIG$  is present.

Table 3. Definition of SA1638 Serial Registers

| First                      | data w               | ord: (s | hown    | with d     | efault v                                                          | alues)                                                                                                                                                   |                     |                     |          |                     |                    |                                |         |                 |                     |         |         |       |     |      |

|----------------------------|----------------------|---------|---------|------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|----------|---------------------|--------------------|--------------------------------|---------|-----------------|---------------------|---------|---------|-------|-----|------|

| Ad                         | ddress               | SA163   | 38      | Sub<br>Adr |                                                                   |                                                                                                                                                          |                     | N                   | -Divide  | er                  |                    |                                |         | Ref -           | - Reg               | Cha     | arge-Pı | ımp   | Reg | Test |

| MSB                        |                      |         |         | •          |                                                                   |                                                                                                                                                          |                     |                     |          |                     |                    |                                |         | •               |                     | •       |         |       |     | LSB  |

| a0                         | a1                   | a2      | а3      | sa         | n0                                                                | n1                                                                                                                                                       | n2                  | n3                  | n4       | n5                  | n6                 | n7                             | n8      | r0              | r1                  | c0      | c1      | c2    | х0  | х1   |

| 1                          | 1                    | 1       | 0       | 0          | 1                                                                 | 1                                                                                                                                                        | 0                   | 0                   | 1        | 0                   | 0                  | 0                              | 0       | 0               | 0                   | 1       | 1       | 1     | 0   | 0    |

|                            |                      |         | Add     | dress:     | 4 bits,                                                           | a0a                                                                                                                                                      | 3, fixed            | to 111              | 0        |                     |                    |                                |         |                 |                     |         |         |       |     |      |

|                            |                      | S       | Sub:Add | dress:     | 1 bit,                                                            | 1 bit, sa, fixed to 0 for first data word                                                                                                                |                     |                     |          |                     |                    |                                |         |                 |                     |         |         |       |     |      |

|                            | N-Divide             |         |         |            |                                                                   | 9 bits, n0n8, values 64 (00100 0000) to 511 (111111111) allowed for IF-choice, default 400                                                               |                     |                     |          |                     |                    |                                |         |                 |                     |         |         |       |     |      |

| Reference Divider Register |                      |         |         |            | 2 bits, r0r1, 00 = ÷13, 01 = ÷26, 10 = ÷39, 11 = ÷52. Default: 00 |                                                                                                                                                          |                     |                     |          |                     |                    |                                |         |                 |                     |         |         |       |     |      |

|                            | Charge-Pump Register |         |         |            |                                                                   | 3 bits, c0c2, Binary current setting factor for charge pumps, values 000 = minimum current to 111 = maximum current, default maximum charge pump current |                     |                     |          |                     |                    |                                |         |                 |                     |         |         |       |     |      |

|                            |                      | T       | est Re  | gister:    | 2 bits, x0x1, default 00, see Functional Description              |                                                                                                                                                          |                     |                     |          |                     |                    |                                |         |                 |                     |         |         |       |     |      |

| Seco                       | nd data              | a word  | : (sho  | vn witl    | n defau                                                           | ılt valu                                                                                                                                                 | es)                 |                     |          |                     |                    |                                |         |                 |                     |         |         |       |     |      |

| Δ,                         | ddrocc               | SA163   | 32      | Sub        |                                                                   | Status DC Offset Register                                                                                                                                |                     |                     |          |                     |                    |                                |         |                 | Mode Select Registe |         |         |       |     |      |

| Α.                         |                      | OA 10.  |         | Adr        | Re                                                                | ₽g                                                                                                                                                       | Q-Channel I-Channel |                     |          |                     |                    |                                |         | mode delect reg |                     |         |         | 13101 | _   |      |

| MSB                        |                      |         |         |            |                                                                   |                                                                                                                                                          |                     |                     |          |                     |                    |                                |         |                 |                     |         |         |       |     | LSB  |

| a0                         | a1                   | a2      | а3      | sa         | s0                                                                | s1                                                                                                                                                       | q0                  | q1                  | q2       | q3                  | i0                 | i1                             | i2      | i3              | t0                  | t1      | t2      | t3    | t4  | t5   |

| 1                          | 1                    | 1       | 0       | 1          | 1                                                                 | 1                                                                                                                                                        | 0                   | 0                   | 0        | 0                   | 0                  | 0                              | 0       | 0               | 0                   | 0       | 0       | 0     | 0   | 0    |

|                            |                      |         | Add     | dress:     | 4 bits,                                                           | a0a                                                                                                                                                      | 3, fixed            | to 111              | 0        |                     |                    |                                |         |                 |                     |         |         |       |     |      |

|                            |                      | S       | Sub:Ado | dress:     | 1 bit,                                                            | sa, fixe                                                                                                                                                 | d to 1 f            | or seco             | ond dat  | a word              |                    |                                |         |                 |                     |         |         |       |     |      |

|                            |                      | Sta     | tus Re  | gister:    | 2 bits,                                                           | s0 set                                                                                                                                                   | s pin A             | <sub>OUT</sub> ; s′ | l sets p | oin B <sub>OU</sub> | <sub>T</sub> , see | Functio                        | onal De | scription       | on                  |         |         |       |     |      |

|                            |                      | DC Off: | set Re  | gister:    | i0 and                                                            | q0 sw                                                                                                                                                    | itches (            | offset p            | olarity, | 0 to lo             | wer vo             | tion as<br>tage, 1<br>. correc | to hig  | her volt        | tage                |         |         |       |     |      |

|                            | Мо                   | de Sel  | ect Re  | gister:    | 6 bits,                                                           | t0.                                                                                                                                                      | t5,                 | 00000               | 00 = no  | rmal G              | SM-Op              | eration                        | as de   | fault, se       | ee Fund             | ctional | Descri  | otion |     |      |

# Low voltage IF I/Q transceiver

SA1638

Figure 4. Serial Input Timing Sequence

Figure 5. Phase Detector Structure with Timing

SA1638

### **PIN FUNCTIONS**

| 1 114 1    |                      |      |                                       |            |                      |      |                                       |

|------------|----------------------|------|---------------------------------------|------------|----------------------|------|---------------------------------------|

| PIN<br>No. | PIN<br>MNEMONIC      | DC V | EQUIVALENT CIRCUIT                    | PIN<br>No. | PIN<br>MNEMONIC      | DC V | EQUIVALENT CIRCUIT                    |

| 47         | V <sub>CC</sub> TxRx | 3.0  | 1.2 2.5 6                             | 10         | RES <sub>D</sub>     | 0.05 | 10                                    |

| 48         | GND <sub>REG</sub> 1 | 0.0  | 35k 1 1 47 25k 48                     | 11         | RES <sub>A</sub>     | 0.00 | 15 — 40 43 46                         |

| 1          | V <sub>REG</sub> 1   | 3.0  | 40 43 46                              |            |                      |      |                                       |

| 2          | V <sub>REG</sub> F2  | 3.0  | BG5                                   |            |                      |      | <b>—</b>                              |

| 3          | V <sub>REG</sub> 2   | 3.0  | 2.5                                   |            |                      |      |                                       |

| 4          | GND <sub>REG</sub> 2 | 0.0  | 35k 3                                 | 12         | RES <sub>B</sub>     | 0.05 |                                       |

| 5          | P <sub>ON</sub>      | 3.3  | 2<br>25k                              |            |                      |      |                                       |

| 6          | V <sub>BATT</sub>    | 3.3  | 40 43 46                              |            |                      |      |                                       |

| 7          | Аоит                 | 3.0  | 7                                     | 13         | P <sub>ON</sub> Rx   | 3.0  | 13                                    |

| 8          | B <sub>OUT</sub>     | 3.0  | 8                                     | 14         | V <sub>REF</sub>     | 1.5  |                                       |

|            |                      |      | $\overline{\downarrow} \oplus \oplus$ | 15         | QRX <sub>OUT</sub>   | 1.5  | <b>(</b>                              |

|            |                      |      | 9 🛧                                   | 16         | QRX <sub>OUT</sub> X | 1.5  |                                       |

| 9          | DC <sub>RES</sub>    | 1.6  | <u> </u>                              | 17         | IRX <sub>OUT</sub>   | 1.5  | 15, 17                                |

|            |                      |      | = =                                   | 18         | IRX <sub>OUT</sub> X | 1.5  | — — — — — — — — — — — — — — — — — — — |

Figure 6. Pin Functions

SA1638

#### PIN FUNCTIONS (continued)

| PIN<br>No. | PIN<br>MNEMONIC     | DC V | EQUIVALENT CIRCUIT    | PIN<br>No. | PIN<br>MNEMONIC       | DC V              | EQUIVALENT CIRCUIT |

|------------|---------------------|------|-----------------------|------------|-----------------------|-------------------|--------------------|

| 19         | QTX <sub>IN</sub>   | 1.5  | ***                   |            |                       |                   |                    |

| 20         | QTX <sub>IN</sub> x | 1.5  | 19, 20, 21, 22        | 35         | I <sub>REF</sub>      | 1.6               |                    |

| 21         | ITX <sub>IN</sub>   | 1.5  | $\uparrow$ $\uparrow$ |            | IXEI                  |                   | 35 +               |

| 22         | ITX <sub>IN</sub> X | 1.5  | <u> </u>              |            |                       |                   | <u></u>            |

| 23         | PdTx                | 0.0  | 23                    | 36         | V <sub>EE</sub> CP    | 0.0               | 37                 |

| 24         | V <sub>CC</sub> DIG | 3.0  |                       | 38         | V <sub>CC</sub> CP    | 3.0               |                    |

| 25         | V <sub>EE</sub> DIG | 3.0  |                       |            |                       |                   | *                  |

| 26         | DATA                |      | * 1 .                 | 39         | P <sub>ON</sub> PLL   | 3.0               | 39                 |

| 27         | CLOCK               |      | 26, 27, 28            |            |                       |                   | <b>→</b>           |

| 28         | STROBE              |      | <b>A</b>              | 40         | GND3                  | 0.0               |                    |

| 29         | LOCK                |      | = =                   | 41         | TXIF <sub>OUT</sub> X | OPEN              | 41 42              |

| 30         | CLK <sub>IN</sub>   | 2.0  |                       | 42         | TXIF <sub>OUT</sub> X | OPEN<br>COLLECTOR |                    |

|            |                     |      | 30 + 31               | 43         | GND2                  | 0.0               |                    |

| 31         | CLK <sub>IN</sub> X | 2.0  |                       | 44         | RxIF <sub>IN</sub> X  | 1.5               | 44 + 45            |

| 32         | ADJ <sub>IN</sub>   | 2.0  | 32                    | 45         | RxIF <sub>IN</sub>    | 1.5               | V <sub>REF</sub>   |

| 33         | LO <sub>IN</sub>    | 2.0  |                       | 46         | GND1                  | 0.0               |                    |

|            |                     |      | 33 34                 | 47         | V <sub>CC</sub> TxRx  | 3.0               |                    |

| 34         | LO <sub>IN</sub> X  | 2.0  |                       | 48         | GND <sub>REG</sub> 1  | 0.0               | SR00530            |

Figure 7. Pin Functions (cont.)

### Low voltage IF I/Q transceiver

SA1638

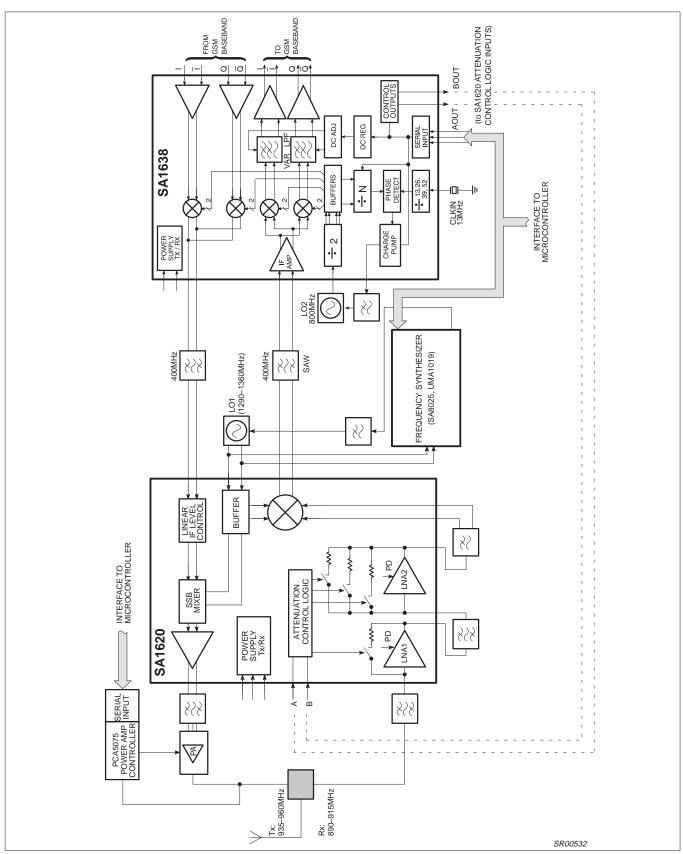

#### Overview of Dual GSM/PCN Architecture

The SA1620 RF front-end and SA1638 IF transceivers form a dual conversion architecture which uses a common IF and standard I/Q baseband interface for both transmit and receive paths. The time division multiplex nature of the GSM system permits integration of the transmit and receive functions together on the one RF and one IF chips. This simplifies the distribution of local oscillator signals, maximizes circuitry commonality, and reduces power consumption.

The SA1620 and SA1638 allow considerable flexibility to optimize the transceiver design for particular price/size/performance requirements, through choice of appropriate RF and IF filters. The IF may be chosen freely in the range 70–400 MHz. The same IF can be used in the transmit and receive directions. Alternately, different IFs can be used if the SA1638 synthesizer frequency is switched between transmit and receive timeslots. The comparison frequency of the SA1638 PLL is high in order to provide fast switching time.

With suitable choice of the IF, an identical SA1638 IF receiver design can be used for both 900MHz GSM and 1800MHz PCN (DCS1800) equipment.

#### **General Benefits/Advantages**

- 2.7V operation. Compatible with 3V digital technology and portable applications. (Higher voltage operation also possible, if desired.)

- Excellent dynamic range. The availability of two LNAs in the SA1620 allows flexibility in receiver dynamic design for portable and mobile GSM spec. applications with appropriate filters. If for a particular application a GaAs or discrete front-end is desired, one of the LNAs can be left unpowered. Placing the AGC gain switches at the front results in some attenuation most of the time, further increasing typical dynamic performance beyond that specified by GSM.

- High power transmit output driver, delivering +7.5dBm output.

This is sufficient to drive a filter and power amplifier input, without a driver amplifier. To avoid unnecessary current consumption, the

- output power can be reduced to an appropriate level by choice of an external resistor.

- DC offsets generated in the receive channel are independent of the LNA AGC setting, and correctable by software to prevent erosion of signal handling dynamic range by DC offsets.

- Minimal high-quality filter requirements. As a result of the integration in the SA1638 of high quality channel selectivity filters, only sufficient filtering is needed in the receive path to provide blocking protection for the second mixers. This reduces receiver cost and size.

- Operation at a high IF allows RF image reject filter requirements to be relaxed. For example, at a 400MHz IF, the natural gain roll-off in the SA1620 LNAs and mixer suppresses the image signal in the 1800MHz band by typically 28dB below the desired 900MHz band signal.

#### **DC Offset Correction**

DC offset correction is provided by two DACs each feeding into one of the two Rx channels. The step size of both DACs is set by the value of the external resistor between DCRES and ground. Thus any original offset less than 1.5V magnitude in either channel can be reduced to the specified level by selecting the appropriate DAC setting via the serial interface.

#### **Integrated Receive Filters**

The low-pass characteristics of the Rx channel are determined by two low-pass responses. The first of these is a passive filter at the output of the quadrature mixers and the second is the low-pass filters which follow the post-mixer amplifiers. These specifications refer only to the response of the default state, but this may be switched by the control register to an alternative setting with a nominal 3dB point of 792kHz.

The corner frequency of the low pass filters can be adjusted over a wide range by varying the value of the external resistor between RESA and RESB. The range of feasible corner frequencies extends at least between 50kHz and 500kHz.

Figure 8. SA1638 Test Circuit

SA1638

Figure 9. SA1620 / SA1638 System Block Diagram

SA1638

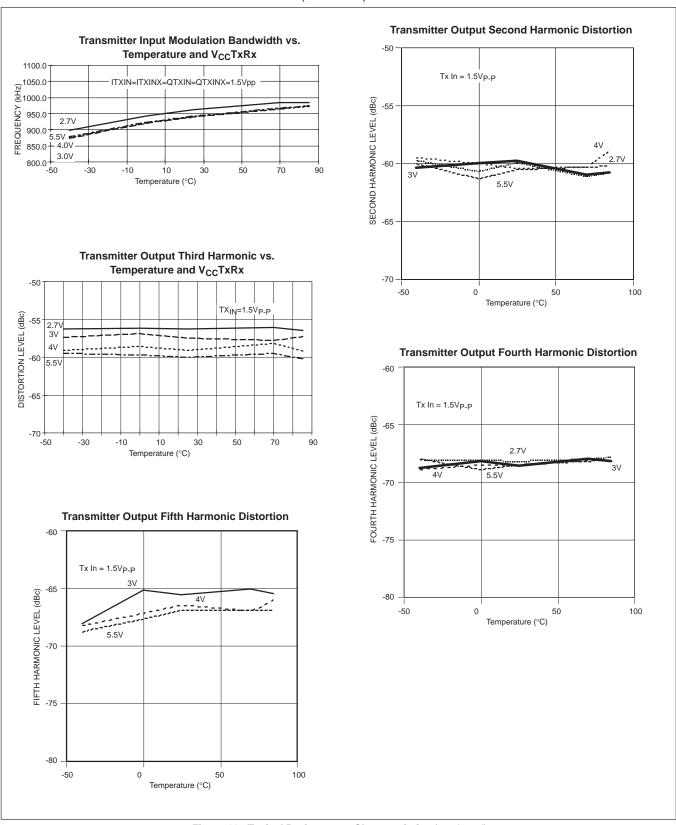

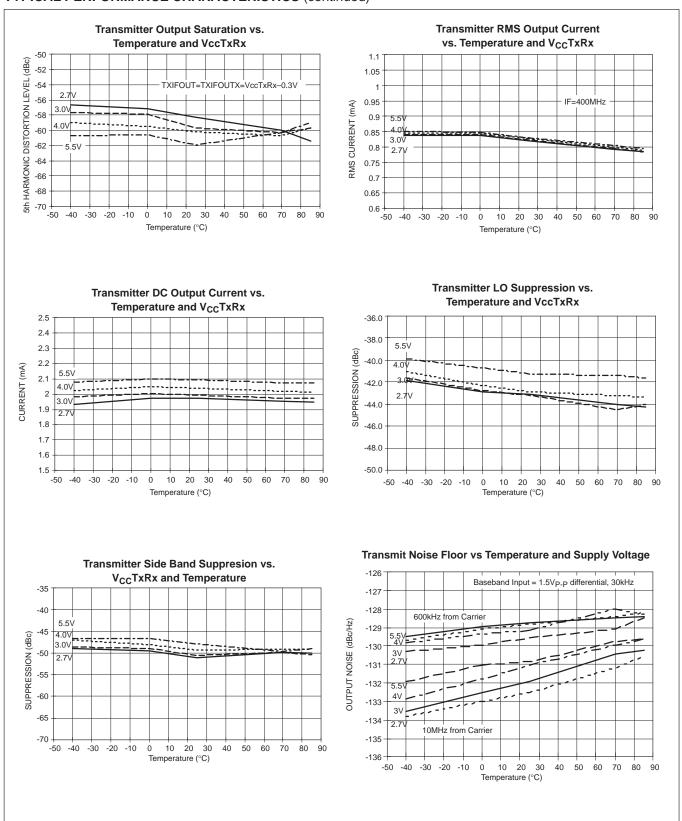

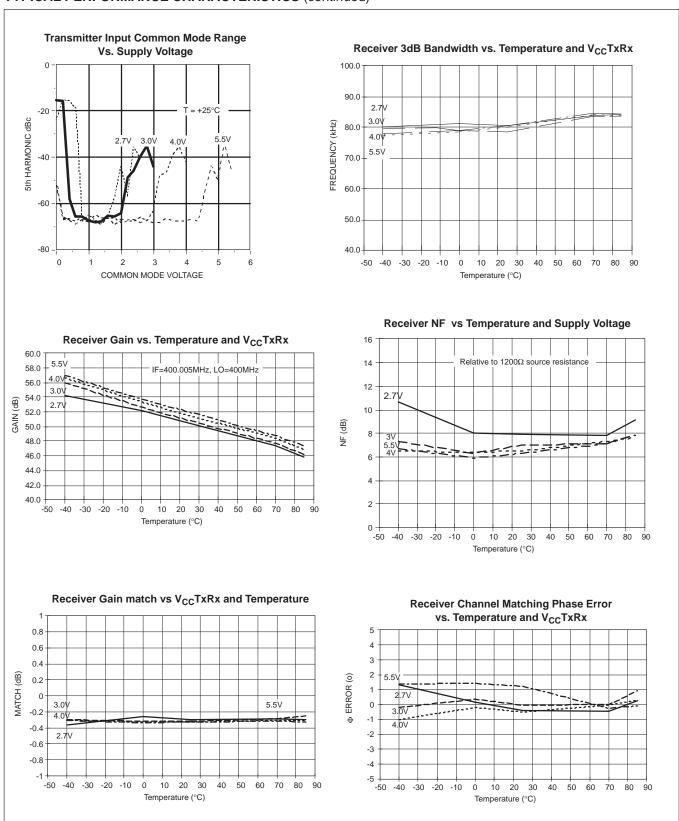

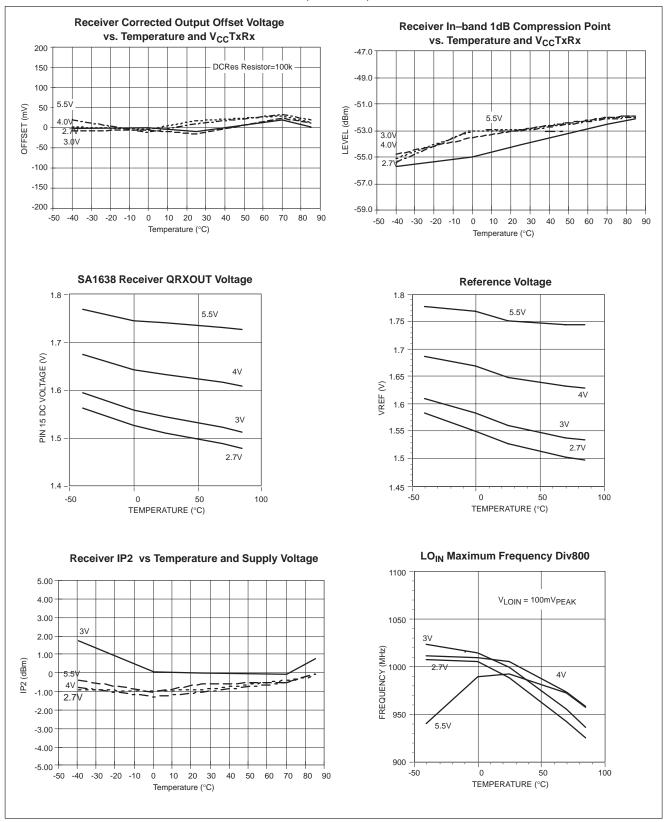

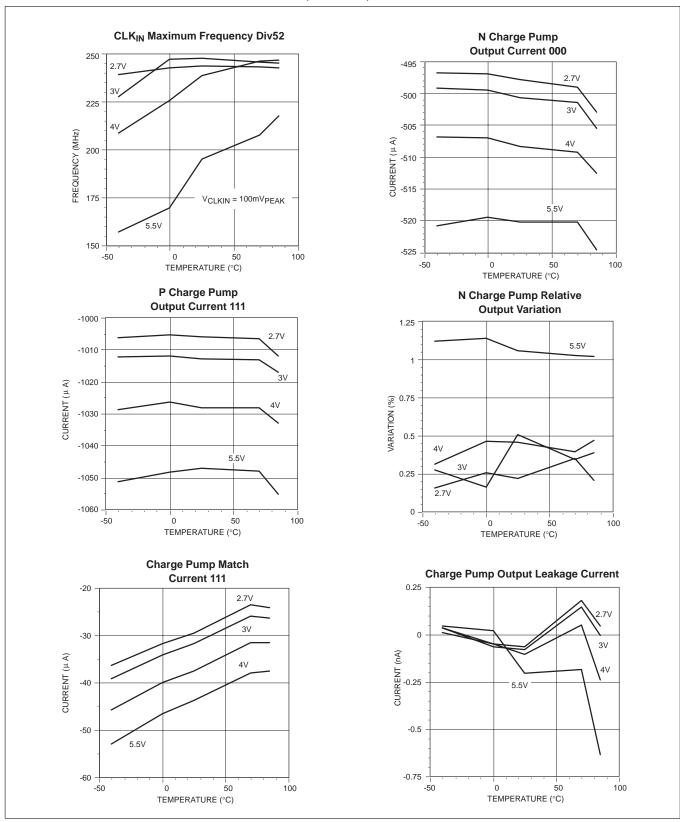

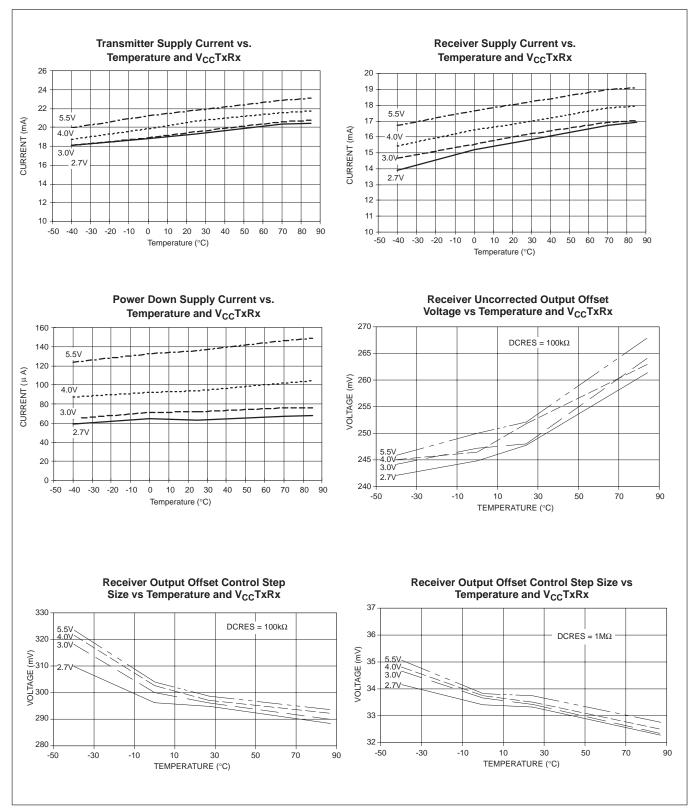

#### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 10. Typical Performance Characteristics

Figure 11. Typical Performance Characteristics (continued)

Figure 12. Typical Performance Characteristics (continued)

Figure 13. Typical Performance Characteristics (continued)

Figure 14. Typical Performance Characteristics (continued)

Figure 15. Typical Performance Characteristics (continued)

Figure 16. Typical Performance Characteristics (continued)

SA1638

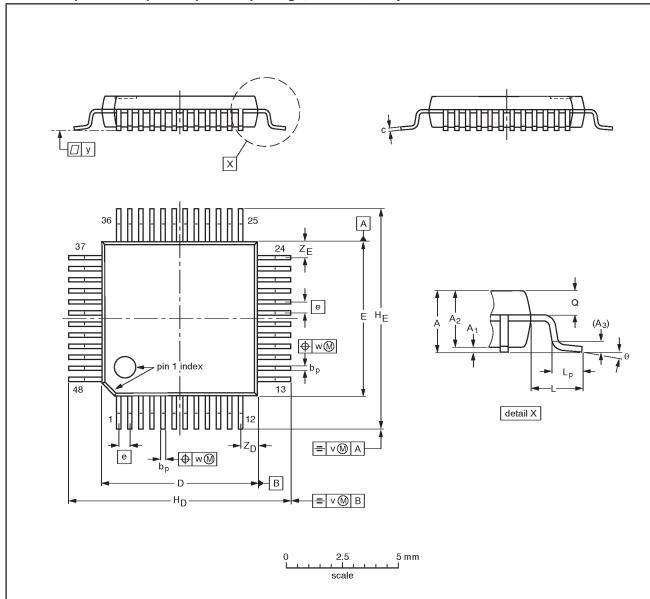

#### LQFP48: plastic low profile quad flat package; 48 leads; body 7 x 7 x 1.4 mm

SOT313-2

#### DIMENSIONS (mm are the original dimensions)

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | рb           | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | е   | H <sub>D</sub> | HE           | L   | Lp           | Q            | v   | w    | у   | Z <sub>D</sub> <sup>(1)</sup> | Z <sub>E</sub> <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|------|--------------|--------------|------------------|------------------|-----|----------------|--------------|-----|--------------|--------------|-----|------|-----|-------------------------------|-------------------------------|----------|

| mm   | 1.60      | 0.20<br>0.05   | 1.45<br>1.35   | 0.25 | 0.27<br>0.17 | 0.18<br>0.12 | 7.1<br>6.9       | 7.1<br>6.9       | 0.5 | 9.15<br>8.85   | 9.15<br>8.85 | 1.0 | 0.75<br>0.45 | 0.69<br>0.59 | 0.2 | 0.12 | 0.1 | 0.95<br>0.55                  | 0.95<br>0.55                  | 7°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER | EUROPEAN | ISSUE DATE |            |                                 |

|----------|-----|-------|----------|------------|------------|---------------------------------|

| VERSION  | IEC | JEDEC | EIAJ     |            | PROJECTION | ISSUE DATE                      |

| SOT313-2 |     |       |          |            |            | <del>93-06-15</del><br>94-12-19 |

# Low voltage IF I/Q transceiver

SA1638

**NOTES**

### Low voltage IF I/Q transceiver

SA1638

#### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                            |

|---------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                         |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make chages at any time without notice in order to improve design and supply the best possible product. |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                      |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.