#### INTEGRATED CIRCUITS

## DATA SHEET

# SA56600-42 System reset for lithium battery backup

Product data

Supersedes data of 2001 Apr 24

File under Integrated Circuits, Standard Analog

#### System reset for lithium battery back-up

#### SA56600-42

#### **GENERAL DESCRIPTION**

The SA56600-42 is designed to protect SRAM data in computer systems during periods of sagging power supply voltages and power outages. When the power supply voltage drops to typically 4.2 V, the CS output goes to a logic LOW state pulling CE to a LOW state, disabling the SRAM device. In addition, a reset logic LOW is asserted for system use. If the supply voltage drops further, to 3.3 V typically or lower, the SA56600-42 switches the system's operation from the main power supply source to the Lithium back-up battery. As the main supply is restored and the voltage rises to 3.3 V or higher, the SRAM support voltage transfers from the Lithium back-up battery to the main supply. When the main supply voltage rises to greater than typically 4.2 V, the CS output goes to a logic HIGH state for SRAM CE control. Reset assertion is released and normal operation is resumed. This sequence ensures reliable preservation of SRAM data during periods of supply deficiency and interruptions.

The SA56600-42 is offered in the SO8 surface mount package.

#### **FEATURES**

- Supply switching at 4.2 V<sub>DC</sub> threshold (falling supply)

- RESET output

- Both CS and CS outputs available for SRAM control

- During battery back-up operation:

- Low supply current (0.3 µA typical)

- Low input/output voltage drop (0.3 V typical at 100  $\mu$ A)

- Low reverse current leakage (0.1 μA max.)

- During normal operation:

- Low input/output voltage drop (0.2 V typical at 50 mA)

- 4.8 V typical output voltage at 50 mA with  $V_{CC} = 5.0 \text{ V}$

- Restoration of main supply operation at 3.3 V

#### **APPLICATIONS**

- Memory cards (SRAM)

- PCs, word processors

- FAX machines, photocopiers, office equipment

- Sequence controllers

- Video games and other equipment with SRAM

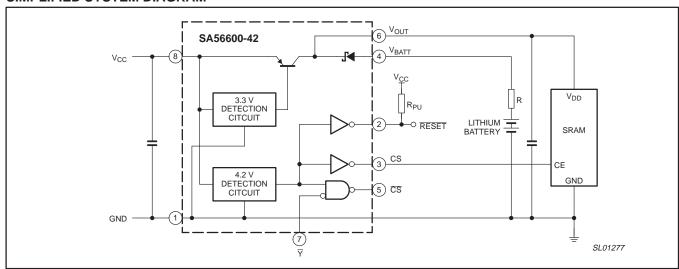

#### SIMPLIFIED SYSTEM DIAGRAM

Figure 1. Simplified system diagram.

#### ORDERING INFORMATION

| TYPE NUMBER  | PACKAGE | TEMPERATURE                                               |               |  |

|--------------|---------|-----------------------------------------------------------|---------------|--|

| TIPE NOWIBER | NAME    | DESCRIPTION                                               | RANGE         |  |

| SA56600-42D  | SO8     | plastic small outline package; 8 leads; body width 3.9 mm | –40 to +85 °C |  |

## System reset for lithium battery back-up

SA56600-42

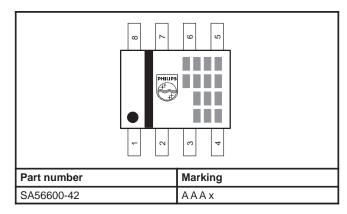

#### Part number marking

The package is marked with a four letter code in the first line to the right of the logo. The first three letters designate the product. The fourth letter, represented by 'x', is a date tracking code. The remaining two or three lines of characters are internal manufacturing codes.

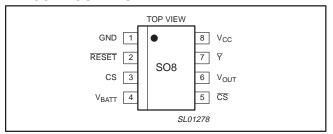

#### **PIN CONFIGURATION**

Figure 2. Pin configuration.

#### **PIN DESCRIPTION**

| PIN | SYMBOL            | DESCRIPTION                                                                                                                                                                                                                   |

|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND               | Circuit ground for the device.                                                                                                                                                                                                |

| 2   | RESET             | Asserted open collector output LOW whenever the $V_{CC}$ input source voltage falls below $V_S$ (4.2 V typical). The open collector topology requires an external pull-up resistor.                                           |

| 3   | CS                | Chip select HIGH output signal, asserted whenever the $V_{CC}$ input source voltage is above $V_S$ (4.2 V typical). Can be used as a chip enable HIGH (CE) signal for system SRAM.                                            |

| 4   | V <sub>BATT</sub> | Positive polarity connection for lithium back-up battery.                                                                                                                                                                     |

| 5   | CS                | Asserted chip select LOW output signal whenever the $V_{CC}$ input source voltage is above $V_S$ (4.2 V typical) and $\overline{Y}$ is grounded. Can be used as a chip enable LOW ( $\overline{CE}$ ) signal for system SRAM. |

| 6   | V <sub>OUT</sub>  | Primary power with lithium battery back-up power for the protected system. Switch over to lithium battery back-up operation occurs when V <sub>CC</sub> falls below V <sub>S</sub> .                                          |

| 7   | Y                 | Open Emitter input to microcontroller used to enable $\overline{\text{CS}}$ output (microcontroller controls $\overline{\text{CS}}$ function).                                                                                |

| 8   | V <sub>CC</sub>   | Primary input power source for device.                                                                                                                                                                                        |

#### **MAXIMUM RATINGS**

| SYMBOL                              | PARAMETER             | RATING       | UNIT |

|-------------------------------------|-----------------------|--------------|------|

| V <sub>CC(max)</sub>                | Power supply voltage  | -0.3 to +7.0 | V    |

| V <sub>CC(op)</sub>                 | Operating voltage     | -0.3 to +7.0 | V    |

| I <sub>O</sub> (V <sub>CC</sub> )   | Output current        | 80           | mA   |

| I <sub>O</sub> (V <sub>BATT</sub> ) | Output current        | 200          | μΑ   |

| T <sub>oper</sub>                   | Operating temperature | -40 to +85   | °C   |

| T <sub>stg</sub>                    | Storage temperature   | -40 to +125  | °C   |

| Р                                   | Power dissipation     | 250          | mW   |

## System reset for lithium battery back-up

SA56600-42

#### **ELECTRICAL CHARACTERISTICS**

Characteristics measured with  $V_{CC}$  = 5.0 V, and  $T_{amb}$  = 25 °C, unless otherwise specified.

| SYMBOL                | PARAMETER                                    | CONDITIONS                                                                         | MIN.                 | TYP.  | MAX.  | UNIT |

|-----------------------|----------------------------------------------|------------------------------------------------------------------------------------|----------------------|-------|-------|------|

| I <sub>CC</sub>       | Supply current                               | V <sub>CC</sub> = 5.0 V; V <sub>BATT</sub> = 3.0 V; I <sub>O</sub> = 0 mA          | -                    | 1.4   | 2.2   | mA   |

| V <sub>SAT1</sub>     | I/O voltage difference 1                     | V <sub>CC</sub> = 5.0 V; V <sub>BATT</sub> = 3.0 V; I <sub>O</sub> = 1.0 mA        | -                    | 0.03  | 0.05  | V    |

| V <sub>O1</sub>       | Output voltage 1                             | V <sub>CC</sub> = 5.0 V; V <sub>BATT</sub> = 3.0 V; I <sub>O</sub> = 1.0 mA        | 4.95                 | 4.97  | _     | V    |

| V <sub>O2</sub>       | Output voltage 2                             | V <sub>CC</sub> = 5.0 V; V <sub>BATT</sub> = 3.0 V; I <sub>O</sub> = 15 mA         | 4.75                 | 4.90  | -     | V    |

| V <sub>S</sub>        | Detection threshold                          | V <sub>CC</sub> falling                                                            | 4.00                 | 4.20  | 4.40  | V    |

| ΔV <sub>S</sub>       | Detection hysteresis                         | $\Delta V_S = V_{SH}$ (rising $V_{CC}$ ) – $V_{SL}$ (falling $V_{CC}$ )            | -                    | 100   | -     | mA   |

| V <sub>RSL</sub>      | Reset output LOW                             | V <sub>CC</sub> = 3.7 V                                                            | -                    | 0.2   | 0.4   | V    |

| I <sub>RSH</sub>      | Reset leakage current HIGH                   | V <sub>CC</sub> = 5.0 V; V <sub>RS</sub> = 7.0 V                                   | -                    | ±0.01 | ±0.1  | μΑ   |

| V <sub>OPL</sub>      | Reset assertion (minimum operating voltage)  | $V_{RSL} \le 0.4 \text{ V}; V_{CC} \text{ falling; } R_{PU} = 10 \text{ k}\Omega$  | -                    | 0.8   | 1.2   | V    |

| V <sub>CSL</sub>      | CS output voltage LOW                        | $V_{CC} = 3.7 \text{ V}; V_{BATT} = 3.0 \text{ V}; I_{CS} = 1.0 \mu\text{A}$       | _                    | -     | 0.1   | V    |

| V <sub>CSH</sub>      | CS output voltage HIGH                       | $V_{CC} = 5.0 \text{ V}; V_{BATT} = 3.0 \text{ V}; I_{CS} = -1.0 \mu\text{A}$      | 4.90                 | -     | -     | V    |

| V <sub>CSL</sub>      | CS output voltage LOW                        | $V_{CC} = 5.0 \text{ V}; V_{BATT} = 3.0 \text{ V}; I_{CS} = 1.0 \mu\text{A}$       | -                    | -     | 0.2   | V    |

| V <sub>CSH</sub>      | CS output voltage HIGH                       | $V_{CC} = 3.7 \text{ V}; V_{BATT} = 3.0 \text{ V}; I_{CS} = -1.0 \mu\text{A}$      | V <sub>O</sub> – 0.1 | -     | -     | V    |

| $\Delta V_S/\Delta T$ | Detection voltage temperature characteristic | -40 ≤ T <sub>amb</sub> ≤ +85                                                       | -                    | -     | ±0.05 | %/°C |

| $V_{BT}$              | Battery back-up threshold                    | V <sub>CC</sub> falling                                                            | 3.15                 | 3.30  | 3.45  | V    |

| V <sub>BT(HYS)</sub>  | Battery back-up hysteresis                   | $V_{BT(HYS)} = V_{BTH} (V_{CC} \text{ rising}) - V_{BTL} (V_{CC} \text{ falling})$ | -                    | 100   | 1.0   | mV   |

| V <sub>BT</sub> /ΔT   | Switching voltage temperature characteristic | -40 ≤ T <sub>amb</sub> ≤ +85                                                       | -                    | ı     | ±0.05 | %/°C |

| IL                    | Loss current                                 | $V_{CC} = 0 \text{ V; } V_{BATT} = 3.0 \text{ V; } I_{O} = 0  \mu\text{A}$         | _                    | 0.3   | 0.5   | μΑ   |

| V <sub>SAT2</sub>     | I/O voltage difference 2                     | $V_{CC} = 0 \text{ V}; V_{BATT} = 3.0 \text{ V}; I_{O} = 1.0 \mu\text{A}$          | _                    | 0.2   | 0.3   | V    |

| $V_{O3}$              | Output voltage 3                             | $V_{CC} = 0 \text{ V}; V_{BATT} = 3.0 \text{ V}; I_{O} = 1.0 \mu\text{A}$          | 2.7                  | 2.8   | _     | V    |

| V <sub>O4</sub>       | Output voltage 4                             | $V_{CC} = 0 \text{ V}; V_{BATT} = 3.0 \text{ V}; I_{CS} = 100 \mu\text{A}$         | 2.6                  | 2.7   | -     | V    |

| $V_{REF}$             | Reference voltage (typical)                  |                                                                                    | _                    | 1.25  | -     | V    |

| I <sub>BL</sub>       | V <sub>BATT</sub> leakage current            | V <sub>CC</sub> = 5.0 V; V <sub>BATT</sub> = 0 V                                   | _                    | _     | 0.1   | μΑ   |

| I <sub>YLO</sub>      | Ÿ current                                    | $V_{CC} = 5.0 \text{ V}; V_{BATT} = 3.0 \text{ V}; V_{Y}^{-} = 0 \text{ V}$        | _                    | 150   | 400   | μΑ   |

| t <sub>PLH</sub>      | ▼ propagation delay time (Note 1)            | $\overline{VY}$ = logic LOW to logic HIGH                                          | -                    | 8.0   | 20    | ns   |

| t <sub>PHL</sub>      | ▼ propagation delay time (Note 1)            | V                                                                                  | -                    | 8.0   | 20    | ns   |

#### NOTE:

<sup>1.</sup>  $\overline{Y}$  input rise and fall time less than 6.0 ns. 15 pF capacitance load on  $\overline{CS}$  (Pin 5 to GND).

## System reset for lithium battery back-up

SA56600-42

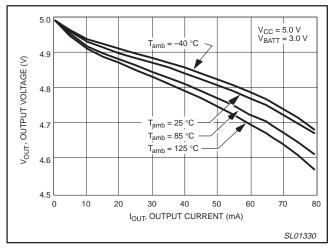

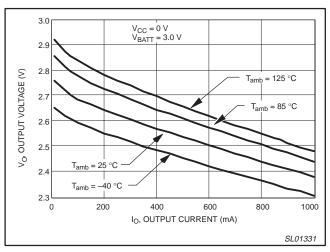

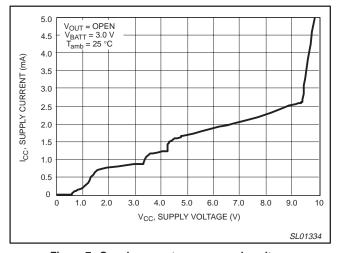

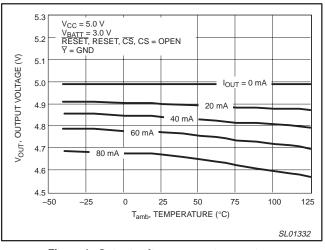

#### **TYPICAL PERFORMANCE CURVES**

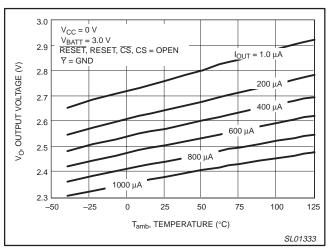

Figure 3. Output voltage versus output current.

Figure 5. Output voltage versus current.

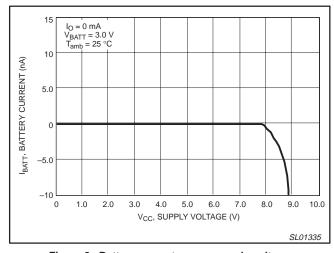

Figure 7. Supply current versus supply voltage.

Figure 4. Output voltage versus temperature.

Figure 6. Output voltage versus temperature.

Figure 8. Battery current versus supply voltage.

## System reset for lithium battery back-up

SA56600-42

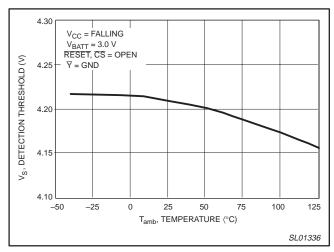

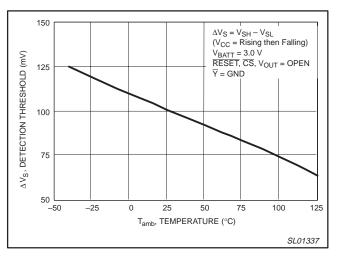

Figure 9. Detection threshold versus temperature.

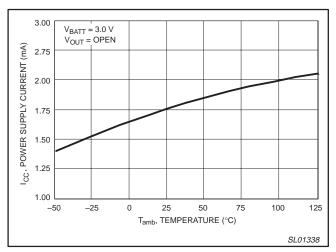

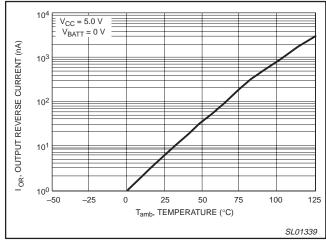

Figure 11. Power supply current versus temperature.

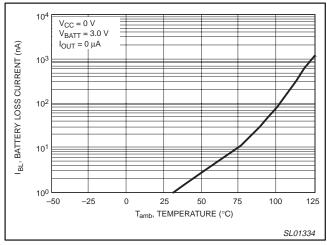

Figure 13. Battery loss current versus temperature.

Figure 10. Detection hysteresis versus temperature.

Figure 12. Output reverse current versus temperature.

#### System reset for lithium battery back-up

SA56600-42

#### **TECHNICAL DESCRIPTION**

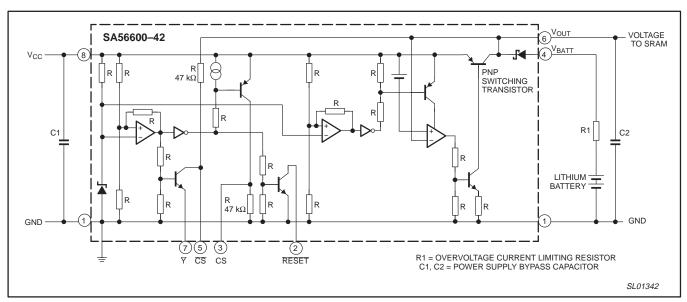

The SA56600-42 provides battery back-up functions to protect SRAM data in computer memory systems. In addition, it provides RESET, Chip Select HIGH (CS), and Chip Select LOW (CS) outputs. The device incorporates a 3.3 V detection circuit, 4.2 V detection circuit, PNP switching transistor, and Schottky diode for low drop lithium battery connection to the output.

During power-up, RESET is actively asserted (LOW logic state) at  $V_{CC}$  voltages as low as 0.8 V and does not output a release (HIGH logic state) until  $V_{CC}$  attains 4.2 V plus hysteresis. CS, in a similar manner, only transitions to a HIGH logic state when  $V_{CC}$  attains 4.2 V plus hysteresis. This ensures adequate voltage being present at the output of the SA56600 for proper operation of the associated computer system.

If the  $V_{CC}$  voltage falls below 4.2 V, CS and RESET both go to a LOW logic state. During this time, with CS in a LOW logic state, no data ca be read from, or written to, the SRAM device. If the primary voltage ( $V_{CC}$ ) continues to fall to 3.3 V and below, the PNP switching transistor disconnects the primary input source power ( $V_{CC}$ ) from the output and the Schottky diode automatically couples the lithium battery power to the output of the SA56600 to supply sustaining power to the SRAM memory.

The SA56600 provides complementary CS and  $\overline{\text{CS}}$  outputs. The outputs differ in ways other than being simple complements of each other. The logic state of CS is strictly a function of V<sub>CC</sub> voltage. When V<sub>CC</sub> is above 4.2 V plus hysteresis, CS is in a HIGH logic state. When V<sub>CC</sub> is below 4.2 V, CS is in a LOW logic state.

$\overline{\text{CS}}$  goes to a LOW logic state only when  $V_{CC}$  is above 4.2 V plus hysteresis, and  $\overline{Y}$  is simultaneously at a LOW logic state. If  $\overline{Y}$  is not a LOW logic state (is open or at a HIGH logic state)  $\overline{\text{CS}}$  will be at a HIGH logic state. Essentially,  $\overline{Y}$  functions as a control switch for  $\overline{\text{CS}}$  and is normally used as an input gating signal from the computer's microprocessor.

Caution should be exercised in the application to keep the voltage on  $\overline{Y}$  to less than 5.0 V when the  $V_{CC}$  voltage is less than 4.2 V to avoid breaking down the Emitter-Base junction of the internal NPN transistor associated with  $\overline{Y}.$  Breakdown of the junction may produce excessive current flow causing damage to the device. When the  $V_{CC}$  voltage is less than 4.2 V, the base of the NPN transistor associated with the  $\overline{Y}$  is at a LOW logic state and most susceptible to an overvoltage on  $\overline{Y}.$

Recovering primary V<sub>CC</sub> power is sensed by the 3.3 V detection circuit. The PNP switching transistor is activated when the applied V<sub>CC</sub> voltage reaches 3.3 V plus hysteresis. When this event occurs, the Schottky diode becomes back-biased, automatically disconnecting the lithium battery from the output and the SRAM is once again supported by the primary V<sub>CC</sub> power source. Full operation is restored when the applied primary V<sub>CC</sub> voltage reaches the required 4.2 V plus hysteresis value. This level is sensed by the 4.2 V detection circuit.  $\overline{\text{RESET}}$  and CS are then caused to go to a HIGH logic state, and the computer memory is back in full operation without any loss of SRAM data.

Figure 14. Functional diagram.

#### System reset for lithium battery back-up

SA56600-42

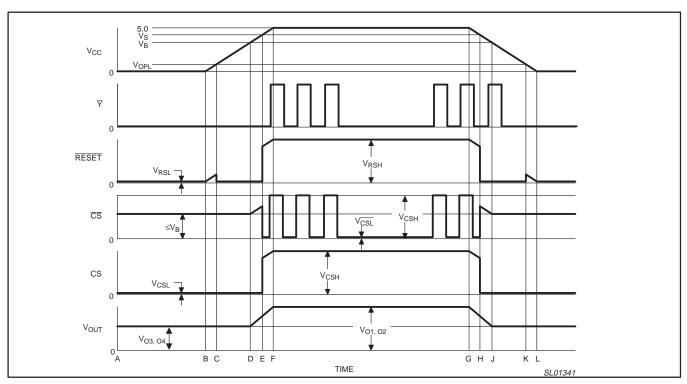

#### Timing diagram

The Timing Diagram shown in Figure 15 depicts the operation of the SA56600-42 in its intended application, with a 3.0 V Lithium battery serving as a backup power source for external SRAM circuitry (see the Simplified system diagram, Figure 1). Letters indicate events along the Time axis.

- **A:** At 'A', the V<sub>CC</sub> primary power source is off. As a result of the backup battery, the  $\overline{\text{CS}}$  and V<sub>OUT</sub> outputs are almost up to the Lithium battery potential (V<sub>B</sub>). All other outputs (Y,  $\overline{\text{RESET}}$ , and CS) are at or very near ground potential.

- B C: At 'B', the V<sub>CC</sub> voltage begins to rise. Also the RESET voltage initially rises but then abruptly returns to a LOW state at 'C'. when the V<sub>CC</sub> voltage reaches the level which activates the internal bias circuitry and asserts  $\overline{\text{RESET}}$  to a logic LOW. This occurs at approximately 0.8 volts.

- **D E:** At 'D' the internal 3.3 V detection circuit is activated when V<sub>CC</sub> voltage rises to 3.3 V. The circuit causes the PNP series pass switching transistor in the output to activate, connecting the main power supply voltage (V<sub>CC</sub>) to the output. This causes the Lithium battery to be automatically disconnected from V<sub>OUT</sub> by back-biasing the Schottky diode. As a result,  $\overline{\text{CS}}$  and V<sub>OUT</sub> begin to rise with V<sub>CC</sub>.

- **E:** At 'E', V<sub>CC</sub> has risen to the upper detection threshold (V<sub>S</sub> plus hysteresis) as sensed by the device's internal 4.2 V detection circuit. This event signals that the output voltage is adequate to support full operation of the associated external computer circuitry. RESET goes HIGH, allowing the microprocessor circuitry to operate. Simultaneously, CS also goes HIGH, signaling the SRAM to start receiving data.  $\overline{\text{CS}}$  goes LOW as a result of  $\overline{\text{Y}}$  simultaneously being at a LOW state.

$\overline{Y}$  controls the  $\overline{CS}$  output. As long as  $\overline{Y}$  is LOW, the  $\overline{CS}$  output is enabled.

- **F:** As  $V_{CC}$  continues to rise,  $\overline{RESET}$ , CS, and  $V_{OUT}$  also continue to rise. Just before 'F',  $\overline{Y}$  is asserted HIGH by the microprocessing circuitry. This causes  $\overline{CS}$  to change from a LOW state to a HIGH state. Following 'F' the microprocessing circuitry is signaling  $\overline{Y}$  through repetitive cycles. This causes  $\overline{CS}$  to also cycle, but has no effect on the battery circuit.

- $\textbf{G:}\ \, \text{At 'G', the V}_{CC}$  voltage begins to fall. As a result  $\ \overline{\text{RESET}},$  CS, and V $_{CC}$  fall.

- **H:** When the V<sub>CC</sub> voltage falls to V<sub>S</sub> (4.2 V) it is detected by the internal 4.2 V detector circuit. The detector circuit forces RESET and CS LOW, deselecting the SRAM and stopping data storage and retrieval. The PNP series pass switching transistor disconnects the primary input source voltage from the output, transferring the SRAM to the backup battery. In addition, because  $\overline{Y}$  is already at a LOW state,  $\overline{CS}$  rises abruptly close to V<sub>S</sub> followed by a continued fall to V<sub>B</sub> (Lithium battery potential), following V<sub>CC</sub>.

- $\begin{tabular}{ll} \bf J: & At `J', V_{OUT} \ has also fallen with V_{CC} \ to a level that is now dictated by the Lithium battery potential. The Lithium battery is now maintaining the V_{OUT} voltage to preserve the SRAM data. \\ \end{tabular}$

- **K** L: As the V<sub>CC</sub> voltage falls to a level which no longer allows the internal bias circuitry to remain active, the assertion of  $\overline{\text{RESET}}$  can no longer be maintained.  $\overline{\text{RESET}}$  rises slightly, then falls to ground as V<sub>CC</sub> falls to ground.

- **M:**  $\overline{Y}$  is asserted HIGH again by the microprocessor, but because  $V_{CC}$  is below  $V_{\overline{S}}$ ,  $\overline{CS}$  remains HIGH and CS remains LOW, preventing the SRAM from being selected.

Figure 15. Timing diagram.

## System reset for lithium battery back-up

SA56600-42

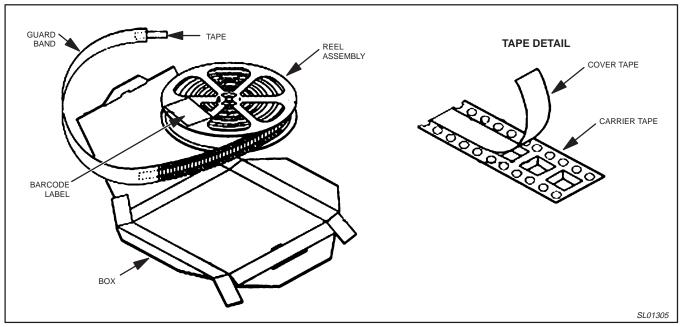

#### **PACKING METHOD**

Figure 16. Tape and reel packing method.

## System reset for lithium battery back-up

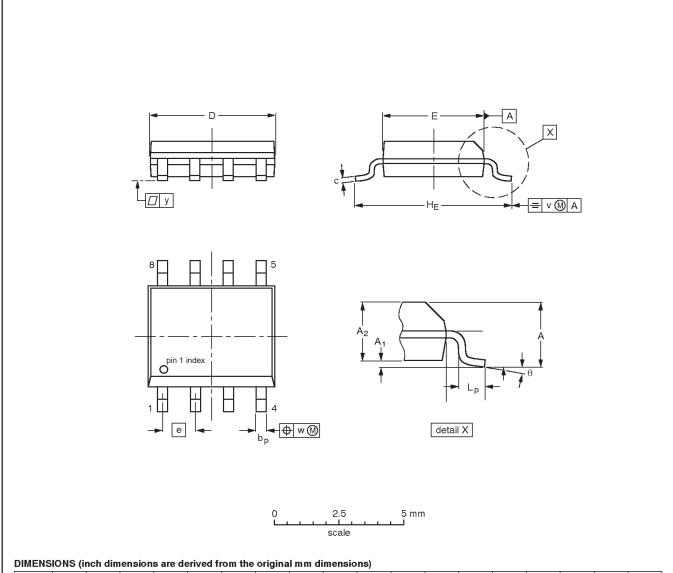

#### SO8: plastic small outline package; 8 leads; body width 3.9 mm

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | B <sub>2</sub> | bp             | С                | D <sup>(1)</sup> | E <sup>(2)</sup> | е     | HE             | Lp             |  | у     | θ  |

|--------|-----------|----------------|----------------|----------------|----------------|------------------|------------------|------------------|-------|----------------|----------------|--|-------|----|

| mm     | 1.73      | 0.25<br>0.10   | 1.45<br>1.25   | 4.95<br>4.80   | 0.51<br>0.33   | 0.25<br>0.19     | 4.95<br>4.80     | 4.0<br>3.8       | 1.27  | 6.2<br>5.8     | 1.27<br>0.38   |  | 0.076 | 8° |

| inches | 0.068     | 0.010<br>0.004 |                | 0.189<br>0.195 | 0.013<br>0.020 | 0.0100<br>0.0075 | 0.20<br>0.19     | 0.16<br>0.15     | 0.050 | 0.244<br>0.228 | 0.050<br>0.015 |  | 0.003 | 0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE |        | REFERENCES |      |  |  |  |  |  |  |

|---------|--------|------------|------|--|--|--|--|--|--|

| VERSION | IEC    | JEDEC      | EIAJ |  |  |  |  |  |  |

| SO8     | 076E03 | MS-012     |      |  |  |  |  |  |  |

## System reset for lithium battery back-up

SA56600-42

**NOTES**

### System reset for lithium battery back-up

SA56600-42

#### Data sheet status

| Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2]</sup> | Definitions                                                                                                                                                                                                                                                                                                            |

|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective data                   | Development                      | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                                           |

| Preliminary data                 | Qualification                    | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.                                     |

| Product data                     | Production                       | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Changes will be communicated according to the Customer Product/Process Change Notification (CPCN) procedure SNW-SQ-650A. |

- [1] Please consult the most recently issued data sheet before initiating or completing a design.

- [2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 2001 All rights reserved. Printed in U.S.A.

Date of release: 06-01

Document order number: 9397 750 08448

Let's make things better.

Philips Semiconductors