# PowerMOS transistor Isolated version of PHP4N50E

PHX4N50E

# **GENERAL DESCRIPTION**

# N-channel enhancement mode field-effect power transistor in a full pack, plastic envelope featuring high avalanche energy capability, stable blocking voltage, fast switching and high thermal cycling performance with low thermal resistance. Intended for use in Switched Mode Power Supplies (SMPS), motor control circuits and general purpose switching applications.

# **QUICK REFERENCE DATA**

| SYMBOL              | PARAMETER                                                                                        | MAX. | UNIT |

|---------------------|--------------------------------------------------------------------------------------------------|------|------|

| V <sub>DS</sub>     | Drain-source voltage Drain current (DC) Total power dissipation Drain-source on-state resistance | 500  | V    |

| I <sub>D</sub>      |                                                                                                  | 2.9  | A    |

| P <sub>tot</sub>    |                                                                                                  | 30   | W    |

| R <sub>DS(ON)</sub> |                                                                                                  | 1.5  | Ω    |

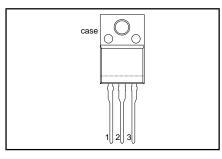

# **PINNING - SOT186A**

| PIN  | DESCRIPTION |

|------|-------------|

| 1    | gate        |

| 2    | drain       |

| 3    | source      |

| case | isolated    |

# PIN CONFIGURATION

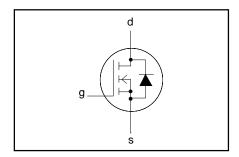

# **SYMBOL**

## LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| SYMBOL                                                 | PARAMETER                                                        | CONDITIONS                                          | MIN.          | MAX.             | UNIT        |

|--------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------|---------------|------------------|-------------|

| $V_{DS}$                                               | Drain-source voltage                                             |                                                     | -             | 500              | V           |

| $V_{DGR}$                                              | Drain-gate voltage                                               | $R_{GS} = 20 \text{ k}\Omega$                       | -             | 500              | V           |

| $\begin{array}{c} V_{DGR} \\ \pm V_{GS} \end{array}$   | Gate-source voltage                                              |                                                     | -             | 30               | V           |

| I <sub>D</sub>                                         | Drain current (DC)                                               | $T_{hs} = 25 ^{\circ}C$<br>$T_{hs} = 100 ^{\circ}C$ | -             | 2.9              | Α           |

| -                                                      | , ,                                                              | $T_{hs}^{r} = 100  ^{\circ}C$                       | -             | 1.8              | Α           |

| I <sub>DM</sub>                                        | Drain current (pulse peak value)                                 | $T_{hs}^{rs} = 25 ^{\circ}C$                        | -             | 11.6             | Α           |

| I <sub>DR</sub>                                        | Source-drain diode current (DC)                                  | $T_{hs} = 25 ^{\circ}C$                             | -             | 2.9              | Α           |

| I <sub>DRM</sub>                                       | Source-drain diode current (pulse peak value)                    | $T_{hs} = 25 ^{\circ}C$                             | -             | 11.6             | Α           |

| P <sub>tot</sub><br>T <sub>stg</sub><br>T <sub>i</sub> | Total power dissipation Storage temperature Junction temperature | $T_{hs} = 25 ^{\circ}C$                             | -<br>-55<br>- | 30<br>150<br>150 | Ç<br>Ç<br>W |

# **AVALANCHE LIMITING VALUE**

| SYMBOL           | PARAMETER                                                                                                                    | CONDITIONS                                                                                                                                                  | MIN. | MAX.             | UNIT     |

|------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------|----------|

| W <sub>DSS</sub> | Drain-source non-repetitive unclamped inductive turn-off energy  Drain-source repetitive unclamped inductive turn-off energy | $T_j = 25^{\circ}\text{C}$ prior to surge $T_j = 100^{\circ}\text{C}$ prior to surge $I_D = 5.3 \text{ A}; V_{DD} \le 50 \text{ V}; V_{GS} = 10 \text{ V};$ |      | 280<br>44<br>7.4 | mJ<br>mJ |

Pulse width and frequency limited by T<sub>i(max)</sub>

Philips Semiconductors Objective specification

# PowerMOS transistor

PHX4N50E

# **ISOLATION LIMITING VALUE & CHARACTERISTIC**

$T_{hs}$  = 25 °C unless otherwise specified

| SYMBOL            | PARAMETER                                                              | CONDITIONS                                                              | MIN. | TYP. | MAX. | UNIT |

|-------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|------|------|

| V <sub>isol</sub> | R.M.S. isolation voltage from all three terminals to external heatsink | f = 50-60 Hz; sinusoidal<br>waveform;<br>R.H. ≤ 65%; clean and dustfree | . 1  |      | 2500 | V    |

| C <sub>isol</sub> | Capacitance from T2 to external heatsink                               | f = 1 MHz                                                               | 1    | 10   | -    | pF   |

# THERMAL RESISTANCES

| SYMBOL               | PARAMETER                               | CONDITIONS             | MIN. | TYP. | MAX. | UNIT |

|----------------------|-----------------------------------------|------------------------|------|------|------|------|

| R <sub>th j-hs</sub> | Thermal resistance junction to heatsink | with heatsink compound | -    | -    | 4.1  | K/W  |

| R <sub>th j-a</sub>  | Thermal resistance junction to ambient  |                        | -    | 55   | -    | K/W  |

# STATIC CHARACTERISTICS

T<sub>i</sub> = 25 °C unless otherwise specified

| SYMBOL        | PARAMETER                                                          | CONDITIONS                                                                                                                                                                              | MIN.          | TYP.             | MAX.              | UNIT          |

|---------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|-------------------|---------------|

| $V_{(BR)DSS}$ | voltage                                                            | $V_{GS} = 0 \text{ V}; I_{D} = 0.25 \text{ mA}$                                                                                                                                         | 500           | -                | -                 | V             |

| $I_{DSS}$     | Gate threshold voltage<br>Drain-source leakage current             | $V_{DS} = V_{GS}; I_D = 0.25 \text{ mA}$<br>$V_{DS} = 500 \text{ V}; V_{GS} = 0 \text{ V}; T_j = 25 \text{ °C}$<br>$V_{DS} = 400 \text{ V}; V_{GS} = 0 \text{ V}; T_j = 125 \text{ °C}$ | 2.0<br>-<br>- | 3.0<br>10<br>0.1 | 4.0<br>100<br>1.0 | V<br>μA<br>mA |

| $R_{DS(ON)}$  | Gate-source leakage current<br>Drain-source on-state<br>resistance | $V_{GS} = \pm 30 \text{ V}; V_{DS} = 0 \text{ V} $ $V_{GS} = 10 \text{ V}; I_{D} = 2.65 \text{ A}$                                                                                      | -             | 10<br>1.3        | 100<br>1.5        | nA<br>Ω       |

| $V_{SD}$      | Source-drain diode forward voltage                                 | $I_F = 5.3 \text{ A ; V}_{GS} = 0 \text{ V}$                                                                                                                                            | -             | 1.1              | 1.4               | V             |

# PowerMOS transistor

PHX4N50E

# **DYNAMIC CHARACTERISTICS**

$T_i = 25$  °C unless otherwise specified

| SYMBOL                                                                                             | PARAMETER                                                                           | CONDITIONS                                                                                                                                          | MIN.        | TYP.                  | MAX.                  | UNIT                 |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------|-----------------------|----------------------|

| g <sub>fs</sub>                                                                                    | Forward transconductance                                                            | $V_{DS} = 15 \text{ V}; I_{D} = 2.65 \text{ A}$                                                                                                     | 1.5         | 2.5                   | -                     | S                    |

| C <sub>iss</sub><br>C <sub>oss</sub><br>C <sub>rss</sub>                                           | Input capacitance<br>Output capacitance<br>Feedback capacitance                     | $V_{GS} = 0 \text{ V}; V_{DS} = 25 \text{ V}; f = 1 \text{ MHz}$                                                                                    |             | 750<br>90<br>40       | 1000<br>140<br>70     | pF<br>pF<br>pF       |

| $\begin{matrix} Q_{g(tot)} \\ Q_{gs} \\ Q_{gd} \end{matrix}$                                       | Total gate charge<br>Gate to source charge<br>Gate to drain (Miller) charge         | $V_{GS} = 10 \text{ V}; I_D = 5.3 \text{ A}; V_{DS} = 400 \text{ V}$                                                                                |             | 35<br>4<br>16         | 1 1 1                 | nC<br>nC<br>nC       |

| $\begin{array}{c} t_{\text{d on}} \\ t_{\text{r}} \\ t_{\text{d off}} \\ t_{\text{f}} \end{array}$ | Turn-on delay time Turn-on rise time Turn-off delay time Turn-off fall time         | $\begin{array}{l} V_{DD} = 30 \text{ V; } I_{D} = 2.6 \text{ A;} \\ V_{GS} = 10 \text{ V; } R_{GS} = 50 \Omega; \\ R_{GEN} = 50 \Omega \end{array}$ | -<br>-<br>- | 10<br>45<br>100<br>40 | 45<br>60<br>140<br>65 | ns<br>ns<br>ns<br>ns |

| t <sub>rr</sub> Q <sub>rr</sub>                                                                    | Source-drain diode reverse recovery time Source-drain diode reverse recovery charge | $I_F = 5.3 \text{ A}; -dI_F/dt = 100 \text{ A/}\mu\text{s};$<br>$V_{GS} = 0 \text{ V}; V_R = 100 \text{ V}$                                         | -           | 1200<br>6             | -                     | ns<br>μC             |

| L <sub>d</sub>                                                                                     | Internal drain inductance Internal source inductance                                | Measured from drain lead 6 mm from package to centre of die Measured from source lead 6 mm from package to source bond pad                          | -           | 4.5<br>7.5            | -                     | nH<br>nH             |

# PowerMOS transistor

PHX4N50E

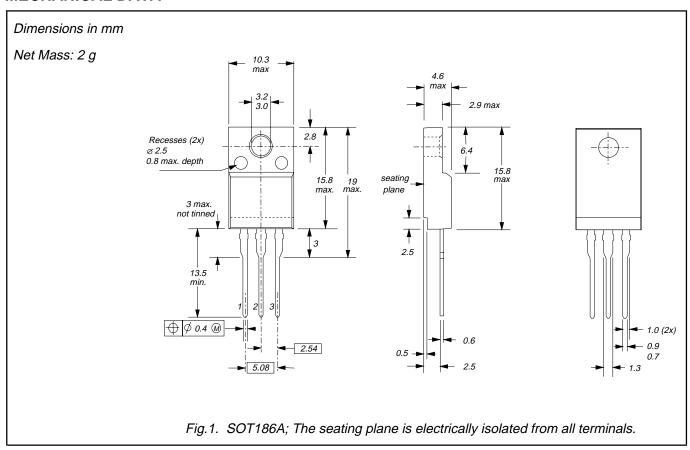

# **MECHANICAL DATA**

## **Notes**

- Observe the general handling precautions for electrostatic-discharge sensitive devices (ESDs) to prevent damage to MOS gate oxide.

Refer to mounting instructions for F-pack envelopes.

Epoxy meets UL94 V0 at 1/8".

# PowerMOS transistor

PHX4N50E

# **DEFINITIONS**

| Data sheet status         |                                                                                       |  |  |  |

|---------------------------|---------------------------------------------------------------------------------------|--|--|--|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |  |  |  |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |  |  |  |

| Product specification     | This data sheet contains final product specifications.                                |  |  |  |

# Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

### © Philips Electronics N.V. 1996

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.