### INTEGRATED CIRCUITS

# DATA SHEET

# TDA8002 IC card interface

Product specification Supersedes data of 1997 Mar 13 File under Integrated Circuits, IC02 1997 Nov 04

IC card interface TDA8002

#### **FEATURES**

- Single supply voltage interface (3.3 or 5 V environment)

- Low-power sleep mode

- Three specific protected half-duplex bidirectional buffered I/O lines

- V<sub>CC</sub> regulation (5 V ±5%, I<sub>CC</sub> <65 mA at V<sub>DD</sub> = 5 V, with controlled rise and fall times

- Thermal and short-circuit protections with current limitations

- Automatic ISO 7816 activation and deactivation sequences

- Enhanced ESD protections on card side (>6 kV)

- Clock generation for the card up to 12 MHz with synchronous frequency changes

- Clock generation up to 20 MHz (auxiliary clock)

- Synchronous and asynchronous cards (memory and smart cards)

- ISO 7816, GSM11.11 compatibility and EMV (Europay, Mastercard, Visa) compliant

- Step-up converter for V<sub>CC</sub> generation

Supply supervisor for spikes elimination and emergency deactivation.

#### **APPLICATIONS**

- IC card readers for:

- GSM applications

- banking

- electronic payment

- identification

- Pay TV

- road tolling.

#### **GENERAL DESCRIPTION**

The TDA8002 is a complete low-power, analog interface for asynchronous and synchronous cards. It can be placed between the card and the microcontroller. It performs all supply, protection and control functions. It is directly compatible with ISO 7816, GSM11.11 and EMV specifications.

#### **QUICK REFERENCE DATA**

| SYMBOL             | PARAMETER                          | CONDITIONS                                                                                      | MIN. | TYP. | MAX. | UNIT |

|--------------------|------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|

| Supply             |                                    |                                                                                                 |      |      |      | •    |

| $V_{DDA}$          | analog supply voltage              |                                                                                                 | 3.0  | 5    | 6.5  | V    |

| I <sub>DD</sub>    | supply current                     | sleep mode                                                                                      | _    | _    | 150  | μΑ   |

|                    |                                    | idle mode; f <sub>CLK</sub> = 2.5 MHz;<br>f <sub>CLKOUT</sub> = 10 MHz; V <sub>DD</sub> = 5 V   | -    | -    | 6    | mA   |

|                    |                                    | active mode; f <sub>CLK</sub> = 2.5 MHz;<br>f <sub>CLKOUT</sub> = 10 MHz; V <sub>DD</sub> = 5 V | -    | -    | 9    | mA   |

|                    |                                    | active mode; f <sub>CLK</sub> = 2.5 MHz;<br>f <sub>CLKOUT</sub> = 10 MHz; V <sub>DD</sub> = 3 V | _    | _    | 12   | mA   |

| Card supp          | ly                                 |                                                                                                 |      |      |      |      |

| V <sub>CC(O)</sub> | output voltage                     | DC load <65 mA                                                                                  | 4.75 | _    | 5.25 | V    |

| I <sub>CC(O)</sub> | output current                     | V <sub>CC</sub> short-circuited to GND                                                          | _    | _    | 100  | mA   |

| General            |                                    |                                                                                                 |      |      |      |      |

| f <sub>CLK</sub>   | card clock frequency               |                                                                                                 | 0    | _    | 12   | MHz  |

| T <sub>de</sub>    | deactivation cycle time            |                                                                                                 | 60   | 80   | 100  | μs   |

| P <sub>tot</sub>   | continuous total power dissipation |                                                                                                 |      |      |      |      |

|                    | TDA8002AT; TDA8002BT               | $T_{amb} = -25 \text{ to } +85 ^{\circ}\text{C}$                                                | _    | _    | 0.56 | W    |

|                    | TDA8002G                           | $T_{amb} = -25 \text{ to } +85 ^{\circ}\text{C}$                                                | _    | _    | 0.46 | W    |

| T <sub>amb</sub>   | operating ambient temperature      |                                                                                                 | -25  | _    | +85  | °C   |

IC card interface TDA8002

#### **ORDERING INFORMATION**

| TYPE NUMBER <sup>(1)</sup>    |             | PACKAGE |                                                  |          |  |  |  |  |  |

|-------------------------------|-------------|---------|--------------------------------------------------|----------|--|--|--|--|--|

| I TPE NUMBER                  | MARKING     | NAME    | DESCRIPTION                                      | VERSION  |  |  |  |  |  |

| TDA8002AT/3/C2 <sup>(2)</sup> | TDA8002AT/3 | SO28    | plastic small outline package; 28 leads;         | SOT136-1 |  |  |  |  |  |

| TDA8002AT/5/C2 <sup>(3)</sup> | TDA8002AT/5 |         | body width 7.5 mm                                |          |  |  |  |  |  |

| TDA8002BT/3/C2 <sup>(2)</sup> | TDA8002BT/3 |         |                                                  |          |  |  |  |  |  |

| TDA8002BT/5/C2 <sup>(3)</sup> | TDA8002BT/5 |         |                                                  |          |  |  |  |  |  |

| TDA8002G/3/C2 <sup>(2)</sup>  | 80023       | LQFP32  | plastic low profile quad flat package; 32 leads; | SOT401-1 |  |  |  |  |  |

| TDA8002G/5/C2 <sup>(3)</sup>  | 80025       |         | body $5 \times 5 \times 1.4 \text{ mm}$          |          |  |  |  |  |  |

#### Notes

- 1. The  $\/\/\ \$  or  $\/\/\ \$  suffix indicates the voltage supervisor option.

- 2. The /3 version can be used with a 3 or 5 V power supply environment (see Chapter "Functional description").

- 3. The /5 version can be used with a 5 V power supply environment.

IC card interface TDA8002

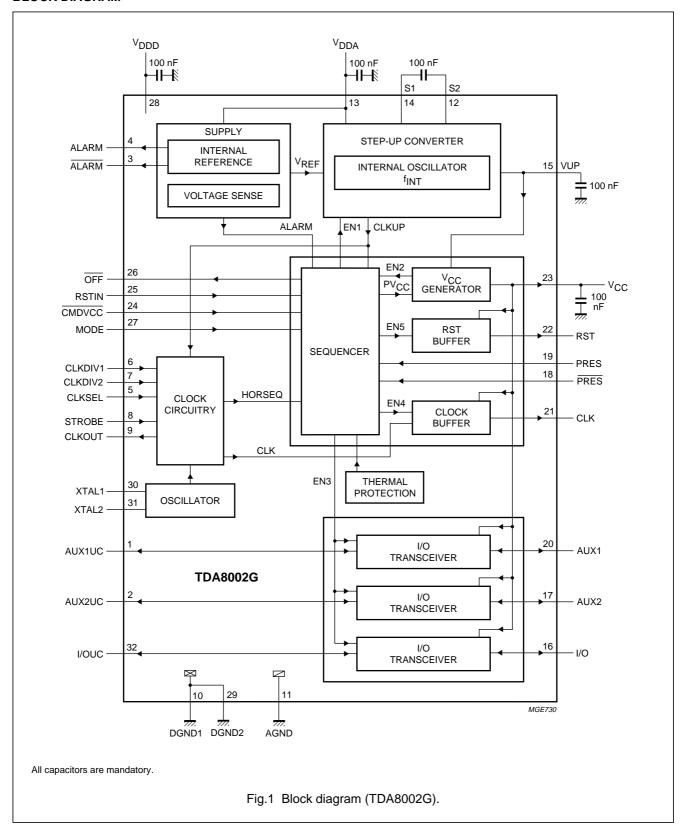

#### **BLOCK DIAGRAM**

## IC card interface TDA8002

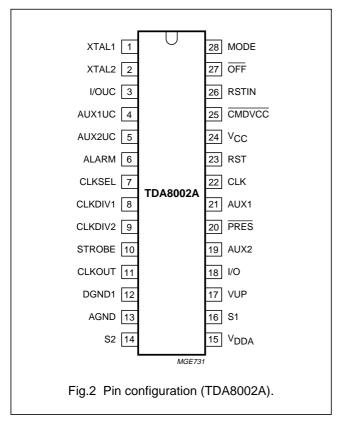

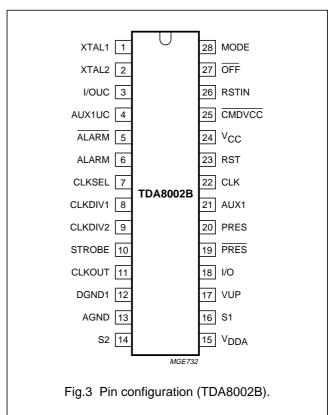

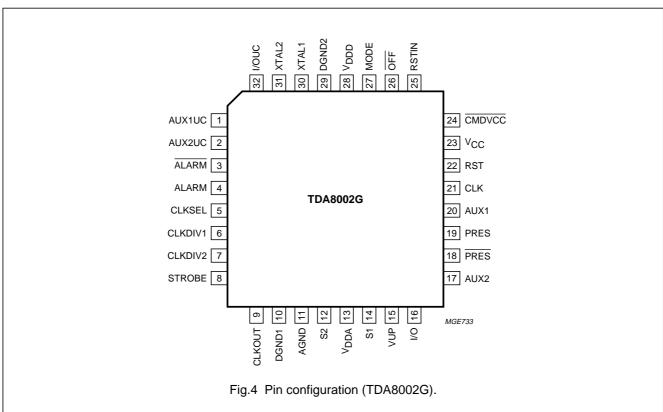

#### **PINNING**

| TYPE A   TYPE B   TYPE G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0)/115.01       |        | PIN    |        |        |                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|--------|--------|--------|------------------------------------------------------------------|

| XTAL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SYMBOL          | TYPE A | TYPE B | TYPE G | I/O    | DESCRIPTION                                                      |

| I/OUC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | XTAL1           | 1      | 1      | 30     | I/O    | crystal connection or input for external clock                   |

| AUX1UC         4         4         1         I/O         auxiliary line to and from microcontroller for synchronous applications           AUX2UC         5         -         2         I/O         auxiliary line to and from microcontroller for synchronous applications           ALARM         -         5         3         O         open drain NMOS reset output for microcontroller (active LC possible plant)           CLKARM         6         6         4         O         open drain PMOS reset output for microcontroller (active HIGH)           CLKSEL         7         7         5         I         control input signal for CLK (LOW = XTAL oscillator; HIGH = STROBE input)           CLKDIV1         8         8         6         I         control input with CLKDIV2 for choosing CLK frequency           CLKDIV2         9         9         7         I         control input with CLKDIV1 for choosing CLK frequency           STROBE         10         10         8         I         external clock input for synchronous applications           CLKOUT         11         11         9         O         clock output (see Table 1)           DGND1         12         12         10         supply digital ground 1           AGND         13         13         11         supply in alog ground </td <td>XTAL2</td> <td>2</td> <td>2</td> <td>31</td> <td>I/O</td> <td>crystal connection</td>                                              | XTAL2           | 2      | 2      | 31     | I/O    | crystal connection                                               |

| AUX2UC 5 — 2 I/O auxiliary line to and from microcontroller for synchronous applications  ALARM — 5 3 O open drain NMOS reset output for microcontroller (active LC ALARM 6 6 6 4 O open drain PMOS reset output for microcontroller (active HIGH)  CLKSEL 7 7 5 I control input signal for CLK (LOW = XTAL oscillator; HIGH = STROBE input)  CLKDIV1 8 8 8 6 I control input with CLKDIV2 for choosing CLK frequency CLKDIV2 9 9 9 7 I control input with CLKDIV1 for choosing CLK frequency STROBE 10 10 8 I external clock input for synchronous applications  CLKOUT 11 11 9 O clock output (see Table 1)  DGND1 12 12 10 supply digital ground 1  AGND 13 13 11 supply analog ground  S2 14 14 12 I/O capacitance connection for voltage doubler VDDA 15 15 13 supply analog supply voltage  S1 16 16 14 I/O capacitance connection for voltage doubler Output of voltage doubler (connect to 100 nF)  I/O 18 18 18 16 I/O data I/O line to and from card  AUX2 19 — 17 I/O auxiliary I/O line to and from card  AUX2 19 1 — 17 I/O auxiliary I/O line to and from card  AUX2 19 1 — 17 I/O auxiliary I/O line to and from card  AUX1 21 21 20 I/O auxiliary I/O line to and from card  AUX1 21 21 20 I/O auxiliary I/O line to and from card  CLK 22 22 21 1 O clock to card output (C2) (see Table 1)  RST 23 23 23 22 O card reset output (C2)  VCC 24 24 24 23 O supply for card (C1) (decouple with 100 nF)  RSTIN 26 26 26 15 I card reset input from microcontroller | I/OUC           | 3      | 3      | 32     | I/O    | data I/O line to and from microcontroller                        |

| ALARM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AUX1UC          | 4      | 4      | 1      | I/O    | 1                                                                |

| ALARM         6         6         4         O         open drain PMoS reset output for microcontroller (active HIGH)           CLKSEL         7         7         5         I         control input signal for CLK (LOW = XTAL oscillator; HIGH = STROBE input)           CLKDIV1         8         8         6         I         control input with CLKDIV2 for choosing CLK frequency           CLKDIV2         9         9         7         I         control input with CLKDIV1 for choosing CLK frequency           STROBE         10         10         8         I         external clock input for synchronous applications           CLKOUT         11         11         9         O         clock output (see Table 1)           DGND1         12         12         10         supply digital ground 1           AGND         13         13         11         supply analog ground           S2         14         14         12         I/O         capacitance connection for voltage doubler           VDDA         15         15         13         supply analog supply voltage           S1         16         16         14         I/O         capacitance connection for voltage doubler           VUP         17         17         15         I/O                                                                                                                                                                                                       | AUX2UC          | 5      | _      | 2      | I/O    | 1                                                                |

| HiGH    CLKSEL   7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ALARM           | _      | 5      | 3      | 0      | open drain NMOS reset output for microcontroller (active LOW)    |

| HIGH = STROBE input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ALARM           | 6      | 6      | 4      | 0      |                                                                  |

| CLKDIV2         9         9         7         I         control input with CLKDIV1 for choosing CLK frequency           STROBE         10         10         8         I         external clock input for synchronous applications           CLKOUT         11         11         9         O         clock output (see Table 1)           DGND1         12         12         10         supply digital ground 1           AGND         13         13         11         supply analog ground           S2         14         14         12         I/O         capacitance connection for voltage doubler           VDDA         15         15         13         supply analog supply voltage           S1         16         16         14         I/O         capacitance connection for voltage doubler           VUP         17         17         15         I/O         output of voltage doubler (connect to 100 nF)           I/O         18         18         16         I/O         data I/O line to and from card           AUX2         19         -         17         I/O         auxiliary I/O line to and from card           PRES         -         20         19         I         active HIGH card input presence contact                                                                                                                                                                                                                                 | CLKSEL          | 7      | 7      | 5      | I      |                                                                  |

| STROBE         10         10         8         I         external clock input for synchronous applications           CLKOUT         11         11         9         O         clock output (see Table 1)           DGND1         12         12         10         supply digital ground 1           AGND         13         13         11         supply analog ground           S2         14         14         12         I/O         capacitance connection for voltage doubler           VDDA         15         15         13         supply analog supply voltage           S1         16         16         14         I/O         capacitance connection for voltage doubler           VUP         17         17         15         I/O         output of voltage doubler (connect to 100 nF)           I/O         18         18         16         I/O         data I/O line to and from card           AUX2         19         -         17         I/O         auxiliary I/O line to and from card           PRES         -         20         19         I         active HIGH card input presence contact           AUX1         21         21         20         I/O         auxiliary I/O line to and from card           CLK                                                                                                                                                                                                                                   | CLKDIV1         | 8      | 8      | 6      | I      | control input with CLKDIV2 for choosing CLK frequency            |

| CLKOUT         11         11         9         O clock output (see Table 1)           DGND1         12         12         10         supply digital ground 1           AGND         13         13         11         supply analog ground           S2         14         14         12         I/O capacitance connection for voltage doubler           VDDA         15         15         13         supply analog supply voltage           S1         16         16         14         I/O capacitance connection for voltage doubler           VUP         17         17         15         I/O output of voltage doubler (connect to 100 nF)           I/O         18         18         16         I/O data I/O line to and from card           AUX2         19         -         17         I/O auxiliary I/O line to and from card           PRES         20         19         18         I active LOW card input presence contact           AUX1         21         21         20         I/O auxiliary I/O line to and from card           CLK         22         22         21         O clock to card output presence contact           AUX1         21         21         20         I/O auxiliary I/O line to and from card           CK                                                                                                                                                                                                                          | CLKDIV2         | 9      | 9      | 7      | I      | control input with CLKDIV1 for choosing CLK frequency            |

| DGND1         12         12         10         supply digital ground 1           AGND         13         13         11         supply analog ground           S2         14         14         12         I/O capacitance connection for voltage doubler           VDDA         15         15         13         supply analog supply voltage           S1         16         16         14         I/O capacitance connection for voltage doubler           VUP         17         17         15         I/O output of voltage doubler (connect to 100 nF)           I/O         18         18         16         I/O output of voltage doubler (connect to 100 nF)           I/O         18         18         16         I/O output of voltage doubler (connect to 100 nF)           I/O         18         18         16         I/O output of voltage doubler (connect to 100 nF)           I/O         18         18         16         I/O output of voltage doubler (connect to 100 nF)           I/O         18         18         16         I/O output of voltage doubler (connect to 100 nF)           I/O         18         18         16         I/O output of voltage doubler (connect to 100 nF)           I/O         18         18         18         18 <t< td=""><td>STROBE</td><td>10</td><td>10</td><td>8</td><td>I</td><td>external clock input for synchronous applications</td></t<>                                                                   | STROBE          | 10     | 10     | 8      | I      | external clock input for synchronous applications                |

| AGND         13         13         11         supply analog ground           S2         14         14         12         I/O capacitance connection for voltage doubler           VDDA         15         15         13         supply analog supply voltage           S1         16         16         14         I/O capacitance connection for voltage doubler           VUP         17         17         15         I/O output of voltage doubler (connect to 100 nF)           I/O         18         18         16         I/O data I/O line to and from card           AUX2         19         -         17         I/O auxiliary I/O line to and from card           PRES         20         19         1         active LOW card input presence contact           AUX1         21         21         20         I/O auxiliary I/O line to and from card           CLK         22         22         21         O clock to card output (C3) (see Table 1)           RST         23         23         22         O supply for card (C1) (decouple with 100 nF)           CMDVCC         25         25         24         I active LOW start activation sequence input from microcontroller                                                                                                                                                                                                                                                                              | CLKOUT          | 11     | 11     | 9      | 0      | clock output (see Table 1)                                       |

| S2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DGND1           | 12     | 12     | 10     | supply | digital ground 1                                                 |

| Voda   15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AGND            | 13     | 13     | 11     | supply | analog ground                                                    |

| S1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | S2              | 14     | 14     | 12     | I/O    | capacitance connection for voltage doubler                       |

| VUP         17         17         15         I/O         output of voltage doubler (connect to 100 nF)           I/O         18         18         16         I/O         data I/O line to and from card           AUX2         19         -         17         I/O         auxiliary I/O line to and from card           PRES         20         19         1         active LOW card input presence contact           PRES         -         20         19         1         active HIGH card input presence contact           AUX1         21         21         20         I/O         auxiliary I/O line to and from card           CLK         22         22         21         O         clock to card output (C3) (see Table 1)           RST         23         23         22         O         card reset output (C2)           V <sub>CC</sub> 24         24         23         O         supply for card (C1) (decouple with 100 nF)           CMDVCC         25         25         24         I         active LOW start activation sequence input from microcontroller           RSTIN         26         26         25         I         card reset input from microcontroller                                                                                                                                                                                                                                                                                    | $V_{DDA}$       | 15     | 15     | 13     | supply | analog supply voltage                                            |

| I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | S1              | 16     | 16     | 14     | I/O    | capacitance connection for voltage doubler                       |

| AUX2         19         -         17         I/O         auxiliary I/O line to and from card           PRES         20         19         18         I active LOW card input presence contact           PRES         -         20         19         I active HIGH card input presence contact           AUX1         21         21         20         I/O auxiliary I/O line to and from card           CLK         22         22         21         O clock to card output (C3) (see Table 1)           RST         23         23         22         O card reset output (C2)           V <sub>CC</sub> 24         24         23         O supply for card (C1) (decouple with 100 nF)           CMDVCC         25         25         24         I active LOW start activation sequence input from microcontroller           RSTIN         26         26         25         I card reset input from microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VUP             | 17     | 17     | 15     | I/O    | output of voltage doubler (connect to 100 nF)                    |

| PRES         20         19         18         I active LOW card input presence contact           PRES         -         20         19         I active HIGH card input presence contact           AUX1         21         21         20         I/O auxiliary I/O line to and from card           CLK         22         22         21         O clock to card output (C3) (see Table 1)           RST         23         23         22         O card reset output (C2)           V <sub>CC</sub> 24         24         23         O supply for card (C1) (decouple with 100 nF)           CMDVCC         25         25         24         I active LOW start activation sequence input from microcontroller           RSTIN         26         26         25         I card reset input from microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I/O             | 18     | 18     | 16     | I/O    | data I/O line to and from card                                   |

| PRES         -         20         19         I         active HIGH card input presence contact           AUX1         21         21         20         I/O         auxiliary I/O line to and from card           CLK         22         22         21         O         clock to card output (C3) (see Table 1)           RST         23         23         22         O         card reset output (C2)           V <sub>CC</sub> 24         24         23         O         supply for card (C1) (decouple with 100 nF)           CMDVCC         25         25         24         I         active LOW start activation sequence input from microcontroller           RSTIN         26         26         25         I         card reset input from microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AUX2            | 19     | _      | 17     | I/O    | auxiliary I/O line to and from card                              |

| AUX1         21         21         20         I/O         auxiliary I/O line to and from card           CLK         22         22         21         O clock to card output (C3) (see Table 1)           RST         23         23         22         O card reset output (C2)           V <sub>CC</sub> 24         24         23         O supply for card (C1) (decouple with 100 nF)           CMDVCC         25         25         24         I active LOW start activation sequence input from microcontroller           RSTIN         26         26         25         I card reset input from microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PRES            | 20     | 19     | 18     | I      | active LOW card input presence contact                           |

| CLK         22         22         21         O clock to card output (C3) (see Table 1)           RST         23         23         22         O card reset output (C2)           V <sub>CC</sub> 24         24         23         O supply for card (C1) (decouple with 100 nF)           CMDVCC         25         25         24         I active LOW start activation sequence input from microcontroller           RSTIN         26         26         25         I card reset input from microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PRES            | _      | 20     | 19     | I      | active HIGH card input presence contact                          |

| RST 23 23 22 O card reset output (C2)  V <sub>CC</sub> 24 24 23 O supply for card (C1) (decouple with 100 nF)  CMDVCC 25 25 24 I active LOW start activation sequence input from microcontroller  RSTIN 26 26 25 I card reset input from microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AUX1            | 21     | 21     | 20     | I/O    | auxiliary I/O line to and from card                              |

| V <sub>CC</sub> 24     24     23     O     supply for card (C1) (decouple with 100 nF)       CMDVCC     25     25     24     I active LOW start activation sequence input from microcontroller       RSTIN     26     26     25     I card reset input from microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLK             | 22     | 22     | 21     | 0      | clock to card output (C3) (see Table 1)                          |

| V <sub>CC</sub> 24     24     23     O     supply for card (C1) (decouple with 100 nF)       CMDVCC     25     25     24     I active LOW start activation sequence input from microcontroller       RSTIN     26     26     25     I card reset input from microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RST             | 23     | 23     | 22     | 0      | card reset output (C2)                                           |

| RSTIN 26 26 25 I card reset input from microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>CC</sub> | 24     | 24     | 23     | 0      |                                                                  |

| - '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CMDVCC          | 25     | 25     | 24     | I      | · · ·                                                            |

| OFF 27 27 26 O open drain NMOS interrupt output to microcontroller (active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RSTIN           | 26     | 26     | 25     | I      | card reset input from microcontroller                            |

| LOW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OFF             | 27     | 27     | 26     | 0      | open drain NMOS interrupt output to microcontroller (active LOW) |

| MODE 28 28 27 I operating mode selection input (HIGH = normal; LOW = sle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MODE            | 28     | 28     | 27     | I      | operating mode selection input (HIGH = normal; LOW = sleep)      |

| V <sub>DDD</sub> – 28 supply digital supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $V_{DDD}$       | _      | -      | 28     | supply | digital supply voltage                                           |

| DGND2 - 29 supply digital ground 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DGND2           | _      | _      | 29     | supply | digital ground 2                                                 |

IC card interface TDA8002

IC card interface TDA8002

#### **FUNCTIONAL DESCRIPTION**

#### Power supply

The supply pins for the chip are  $V_{DDA}$ ,  $V_{DDD}$ , AGND, DGND1 and DGND2.  $V_{DDA}$  and  $V_{DDD}$  (i.e.  $V_{DD}$ ) should be in the range of 3.0 to 6.5 V. All card contacts remain inactive during power-up or power-down.

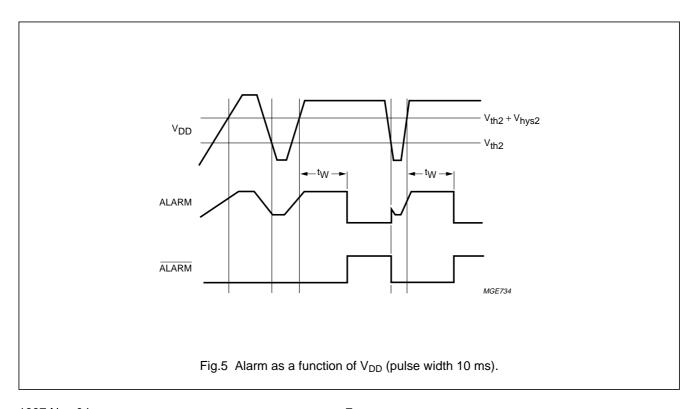

On power-up, the logic is reset by an internal signal. The sequencer is not activated until  $V_{DD}$  reaches  $V_{th2} + V_{hys2}$  (see Fig.5). When  $V_{DD}$  falls below  $V_{th2}$ , an automatic deactivation sequence of the contacts is performed.

#### Supply voltage supervisor (V<sub>DD</sub>)

This block surveys the  $V_{DD}$  supply. A defined reset pulse of 10 ms minimum ( $t_W$ ) can be retriggered and is delivered on the ALARM outputs during power-up or power-down of  $V_{DD}$  (see Fig.5). This signal is also used for eliminating the spikes on card contacts during power-up or power-down.

When  $V_{DD}$  reaches  $V_{th2} + V_{hys2}$ , an internal delay is started. The ALARM outputs are active until this delay has expired. When  $V_{DD}$  falls below  $V_{th2}$ , ALARM is activated and a deactivation sequence of the contacts is performed.

For 3 V supply, the supervisor option must be chosen at 3 V. For 5 V supply, both options (3 or 5 V) may be chosen depending on the application.

#### **Clock circuitry**

The TDA8002 supports both synchronous and asynchronous cards (I<sup>2</sup>C-bus memories requiring an acknowledge signal from the master are not supported). There are three methods to clock the circuitry:

- Apply a clock signal to pin STROBE

- · Use of an internal RC oscillator

- Use of a quartz oscillator which should be connected between pins XTAL1 and XTAL2.

When CLKSEL is HIGH, the clock should be applied on the STROBE pin, and when CLKSEL is LOW, one of the internal oscillators is used.

When an internal clock is used, the clock output is available on pin CLKOUT. The RC oscillator is selected by making CLKDIV1 HIGH and CLKDIV2 LOW. The clock output to the card is available on pin CLK. The frequency of the card clock can be the input frequency divided by 2 or 4, STOP LOW or 1.25 MHz, depending on the states of CLKDIV1 or CLKDIV2 (see Table 1).

Do not change CLKSEL during activation. When in low-power (sleep) mode, the internal oscillator frequency which is available on pin CLKOUT is lowered to approximately 16 kHz for power-economy purposes.

IC card interface TDA8002

Table 1 Clock circuitry definition

| MODE               | CLKSEL           | CLKDIV1          | CLKDIV2          | FREQUENCY<br>OF CLK                           | FREQUENCY<br>OF CLKOUT  |

|--------------------|------------------|------------------|------------------|-----------------------------------------------|-------------------------|

| HIGH               | LOW              | HIGH             | LOW              | <sup>1</sup> / <sub>2</sub> f <sub>int</sub>  | ½f <sub>int</sub>       |

| HIGH               | LOW              | LOW              | LOW              | ½f <sub>xtal</sub>                            | f <sub>xtal</sub>       |

| HIGH               | LOW              | LOW              | HIGH             | <sup>1</sup> / <sub>2</sub> f <sub>xtal</sub> | f <sub>xtal</sub>       |

| HIGH               | LOW              | HIGH             | HIGH             | STOP LOW                                      | f <sub>xtal</sub>       |

| HIGH               | HIGH             | X <sup>(1)</sup> | X <sup>(1)</sup> | STROBE                                        | f <sub>xtal</sub>       |

| LOW <sup>(2)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup> | STOP LOW                                      | 1/2f <sub>int</sub> (3) |

#### **Notes**

- 1. X = don't care.

- 2. In low-power mode.

- 3.  $f_{int} = 32 \text{ kHz in low-power mode.}$

#### I/O circuitry

The three I/O transceivers are identical. The state is HIGH for all I/O pins (i.e. I/O, I/OUC, AUX1, AUX1UC, AUX2 and AUX2UC). Pin I/O is referenced to  $V_{CC}$  and pin I/OUC to  $V_{DD}$ , thus ensuring proper operation in case  $V_{CC} \neq V_{DD}$ .

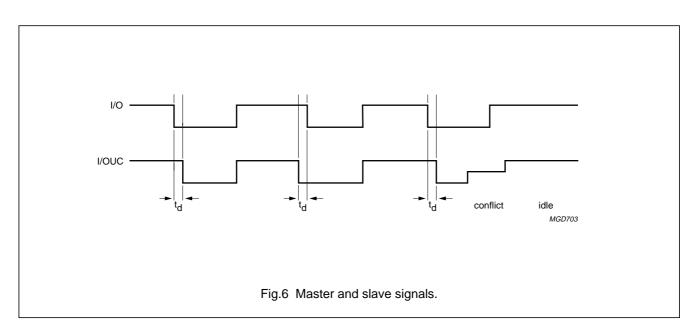

The first side on which a falling edge is detected becomes a master (input). An anti-latch circuitry first disables the detection of the falling edge on the other side, which becomes slave (output).

After a delay time  $t_d$  (about 50 ns), the logic 0 present on the master side is transferred on the slave side.

When the input is back to HIGH level, a current booster is turned on during the delay  $t_{\rm d}$  on the output side and then both sides are back to their idle state, ready to detect the next logic 0 on any side.

In case of a conflict, both lines may remain LOW until the software enables the lines to be HIGH. The anti-latch circuitry ensures that the lines do not remain LOW if both sides return HIGH, regardless of the prior conditions. The maximum frequency on the lines is approximately 1 MHz.

IC card interface TDA8002

#### Logic circuitry

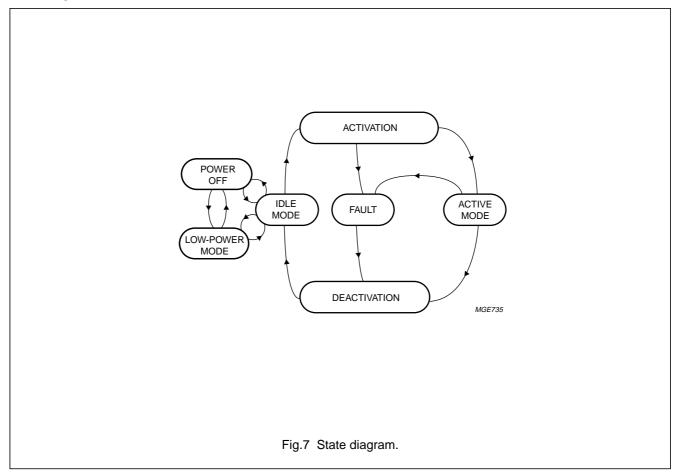

After power-up, the circuit has six possible states of operation. Table 1 shows the sequence of these states.

#### **I**DLE MODE

After reset, the circuit enters the idle mode.

A minimum number of functions in the circuit are active while waiting for the microcontroller to start a session:

- · All card contacts are inactive

- I/OUC, AUX1UC and AUX2UC are high-impedance

- · Oscillator XTAL runs, delivering CLKOUT

- · Voltage supervisor is active.

#### LOW-POWER (SLEEP) MODE

When pin MODE goes LOW, the circuit enters the low-power (sleep) mode. As long as pin MODE is LOW, no activation is possible.

If pin MODE goes LOW in the active mode, a normal deactivation sequence is performed before entering low-power mode. When pin MODE goes HIGH, the circuit enters normal operation after a delay of at least 6 ms (96 cycles of CLKOUT). During this time the CLKOUT remains at 16 kHz.

- · All card contacts are inactive

- · Oscillator XTAL does not run

- The V<sub>DD</sub> supervisor, ALARM output, card presence detection and OFF output remain functional

- Internal oscillator is slowed to 32 kHz, CLKOUT providing 16 kHz.

#### **ACTIVE MODE**

When the activation sequence is completed, the TDA8002 will be in the active mode. Data is exchanged between the card and the microcontroller via the I/O lines.

#### State diagram

IC card interface TDA8002

#### **ACTIVATION SEQUENCE**

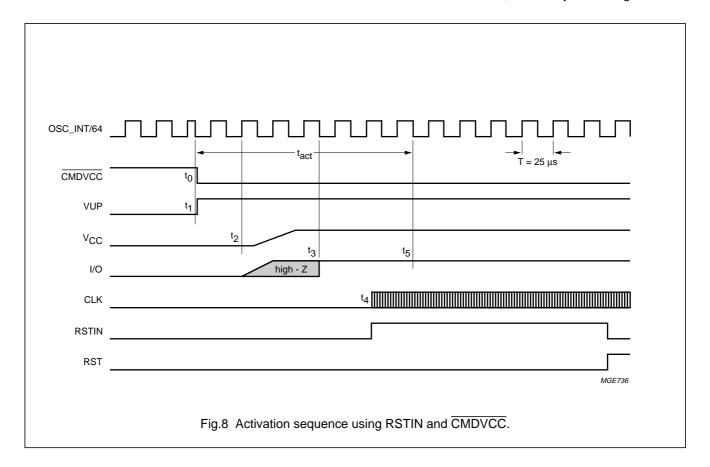

From idle mode, the circuit enters the activation mode when the microcontroller sets the  $\overline{\text{CMDVCC}}$  line LOW or sets the MODE line HIGH when the  $\overline{\text{CMDVCC}}$  line is already LOW. The internal circuitry is then activated, the internal clock is activated and an activation sequence is executed. When RST is enabled, it becomes the inverse of RSTIN.

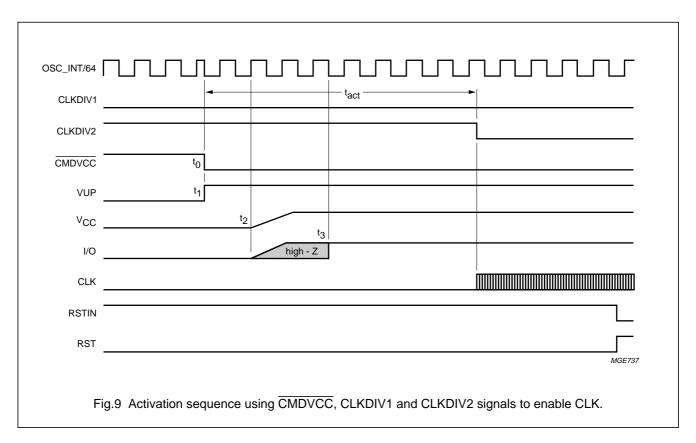

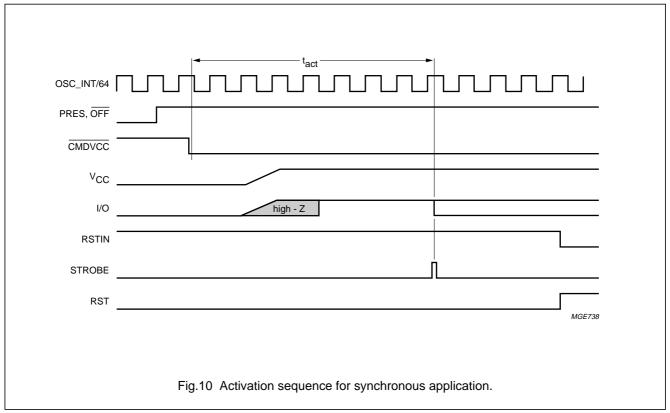

Figures 8 to 10 illustrate the activation sequence as described below:

- 1. Step-up converter is started  $(t_1 \approx t_0)$

- 2.  $V_{CC}$  rises from 0 to 5 V ( $t_2 = t_1 + 1\frac{1}{2}T$ )

- 3. I/O, AUX1, AUX2 are enabled and CLK is enabled  $(t_3 = t_1 + 4T)$ ; a special circuitry ensures that I/O remains below V<sub>CC</sub> during falling slope of V<sub>CC</sub>

- 4. CLK is set by setting RSTIN to HIGH (t<sub>4</sub>)

- 5. RST is enabled ( $t_5 = t_1 + 7T$ ); after  $t_5$ , RSTIN has no further action on CLK, but is only controlling RST.

1997 Nov 04

IC card interface TDA8002

1997 Nov 04

IC card interface TDA8002

#### **DEACTIVATION SEQUENCE**

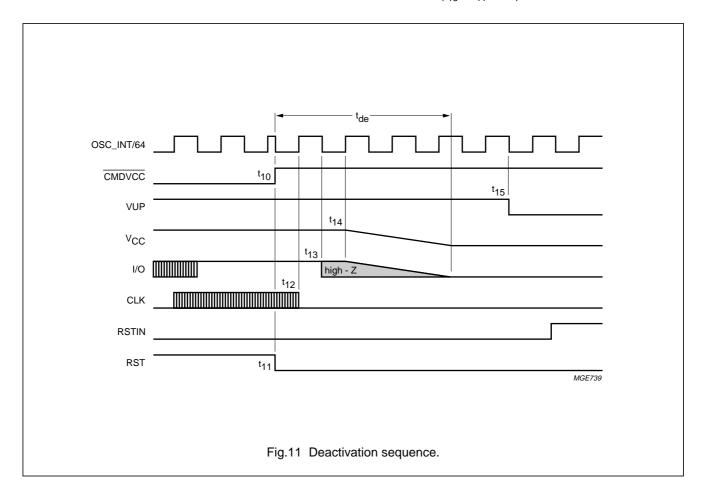

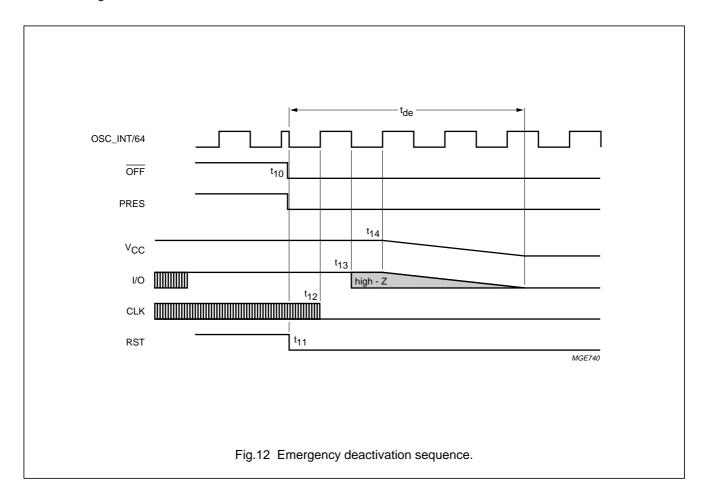

When a session is completed, the microcontroller sets the  $\overline{\text{CMDVCC}}$  line to HIGH state or MODE line to LOW state. The circuit then executes an automatic deactivation sequence by counting the sequencer down and ends in idle mode.

Figures 11 and 12 illustrate the deactivation sequence as described below:

- 1. RST goes LOW  $(t_{11} \approx t_{10})$

- 2. CLK is stopped  $(t_{12} = t_{11} + \frac{1}{2}T)$

- 3. I/O, AUX1, AUX2 are outputs into high-impedance state  $(t_{13} = t_{11} + T)$

- 4.  $V_{CC}$  falls to zero ( $t_{14} = t_{11} + 1\frac{1}{2}T$ ); a special circuitry ensures that I/O remains below  $V_{CC}$  during falling slope of  $V_{CC}$

- 5. VUP falls  $(t_{15} = t_{11} + 5T)$ .

IC card interface TDA8002

#### **Fault detection**

The following fault conditions are monitored by the circuit:

- Short-circuit or high current on V<sub>CC</sub>

- · Removing card during transaction

- V<sub>DD</sub> dropping

- · Overheating.

When one or more of these faults are detected, the circuit pulls the interrupt line  $\overline{\mathsf{OFF}}$  to its active LOW state and a deactivation sequence is initiated. In case the card is present the interrupt line  $\overline{\mathsf{OFF}}$  is set to HIGH when the microcontroller has reset the  $\overline{\mathsf{CMDVCC}}$  line HIGH (after completion of the deactivation sequence). In case the card is not present  $\overline{\mathsf{OFF}}$  remains LOW.

IC card interface TDA8002

#### **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 134); note 1.

| SYMBOL                | PARAMETER                                                                                                                               | CONDITIONS                                       | MIN.       | MAX. | UNIT |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------|------|------|

| V <sub>DD</sub>       | supply voltage                                                                                                                          |                                                  | -0.3       | +6.5 | V    |

| V <sub>i</sub> (CMOS) | voltage on CMOS pins  XTAL1, XTAL2, ALARM, ALARM, MODE, RSTIN, CLKSEL, AUX2UC, AUX1UC, CLKDIV1, CLKDIV2, CLKOUT, STROBE, CMDVCC and OFF |                                                  | -0.3       | +6.5 | V    |

| V <sub>i(card)</sub>  | voltage on card contact pins I/O, AUX2, PRES, PRES, AUX1, CLK, RST and V <sub>CC</sub>                                                  |                                                  | -0.3       | +6.5 | V    |

| V <sub>es</sub>       | electrostatic handling<br>on pins I/O, RST, V <sub>CC</sub> , CLK, AUX1,<br>AUX2, PRES and PRES                                         |                                                  | -6         | +6   | kV   |

|                       | on all other pins                                                                                                                       |                                                  | -2         | +2   | kV   |

| T <sub>stg</sub>      | storage temperature                                                                                                                     |                                                  | <b>–55</b> | +125 | °C   |

| P <sub>tot</sub>      | continuous total power dissipation                                                                                                      |                                                  |            |      |      |

|                       | TDA8002T                                                                                                                                | $T_{amb} = -25 \text{ to } +85 ^{\circ}\text{C}$ | _          | 0.56 | W    |

|                       | TDA8002G                                                                                                                                | $T_{amb} = -25 \text{ to } +85 ^{\circ}\text{C}$ | _          | 0.46 | W    |

| T <sub>amb</sub>      | operating ambient temperature                                                                                                           |                                                  | -25        | +85  | °C   |

| T <sub>j</sub>        | junction temperature                                                                                                                    |                                                  | _          | 150  | °C   |

#### Note

#### **HANDLING**

Every pin withstands the ESD test according to MIL-STD-883C class 3 for card contacts, class 2 for the remaining. Method 3015 (HBM 1500  $\Omega$ , 100 pF) 3 positive pulses and 3 negative pulses on each pin referenced to ground.

#### THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                               | VALUE | UNIT |

|----------------------|---------------------------------------------------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient in free air |       |      |

|                      | SOT136-1                                                | 70    | K/W  |

|                      | SOT401-1                                                | 91    | K/W  |

<sup>1.</sup> Stress beyond these levels may cause permanent damage to the device. This is a stress rating only and functional operation of the device under this condition is not implied.

IC card interface TDA8002

#### **CHARACTERISTICS**

$V_{DD}$  = 5 V;  $T_{amb}$  = 25 °C;  $f_{xtal}$  = 10 MHz; unless otherwise specified.

| SYMBOL                     | PARAMETER                                | CONDITIONS                                                                                            | MIN. | TYP. | MAX. | UNIT |

|----------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|

| Supply                     |                                          |                                                                                                       |      |      |      | •    |

| $V_{DD}$                   | positive supply voltage                  | option 5 V power supply (TDA8002xx/5)                                                                 | 4.5  | 5    | 6.5  | V    |

|                            |                                          | option 3.3 V or 5 V power supply (TDA8002xx/3)                                                        | 3    | 5    | 6.5  | V    |

| I <sub>DD(sl)</sub>        | supply current                           | sleep mode; V <sub>DD</sub> = 5 V                                                                     | _    | _    | 200  | μΑ   |

| I <sub>DD(idle)</sub>      | supply current                           | idle mode; $V_{DD} = 5 \text{ V}$ ;<br>$f_{CLK} = 2.5 \text{ MHz}$ ;<br>$f_{CLKOUT} = 10 \text{ MHz}$ | _    | _    | 6    | mA   |

| I <sub>DD(active)</sub>    | supply current                           | active mode                                                                                           |      |      |      |      |

|                            |                                          | $V_{DD} = 5 \text{ V};$ $f_{CLK} = 2.5 \text{ MHz};$ $f_{CLKOUT} = 10 \text{ MHz}$                    | _    | _    | 9    | mA   |

|                            |                                          | $V_{DD} = 3.3 \text{ V};$<br>$f_{CLK} = 2.5 \text{ MHz};$<br>$f_{CLKOUT} = 10 \text{ MHz}$            | _    | _    | 12   | mA   |

| V <sub>th2</sub>           | threshold voltage on V <sub>DD</sub> for | falling                                                                                               |      |      |      |      |

|                            | voltage supervisor                       | option 5 V power supply (TDA8002xx/5)                                                                 | 3.9  | 4.05 | 4.2  | V    |

|                            |                                          | option 3.3 V or 5 V power supply (TDA8002xx/3)                                                        | 2.6  | 2.7  | 2.8  | V    |

|                            |                                          | rising                                                                                                |      |      |      |      |

|                            |                                          | option 5 V power supply (TDA8002xx/5)                                                                 | 4    | 4.2  | 4.4  | V    |

|                            |                                          | option 3.3 or 5 V power<br>supply (TDA8002xx/3)                                                       | 2.7  | 2.85 | 2.99 | V    |

| V <sub>hys2</sub>          | hysteresis on V <sub>th2</sub>           |                                                                                                       | 100  | 150  | 200  | mV   |

| CARD SUPPLY                | ,                                        | •                                                                                                     | •    | •    | •    | •    |

| V <sub>CC(O)(idle)</sub>   | output voltage                           | idle mode                                                                                             | _    | _    | 0.4  | V    |

| V <sub>CC(O)(active)</sub> | output voltage                           | active mode                                                                                           |      |      |      |      |

|                            |                                          | $I_{CC}$ < 20 mA: DC load with 3 V < $V_{DD}$ < 3.3 V                                                 | 4.75 | _    | 5.25 | V    |

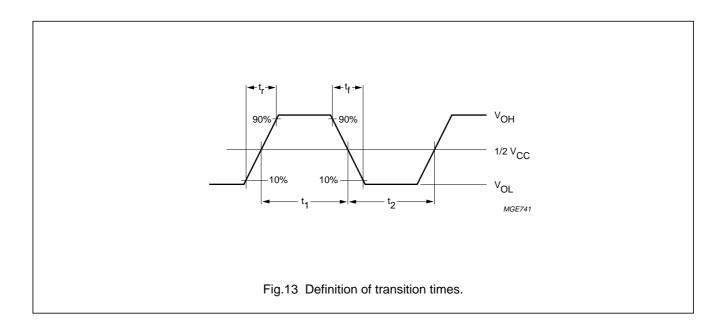

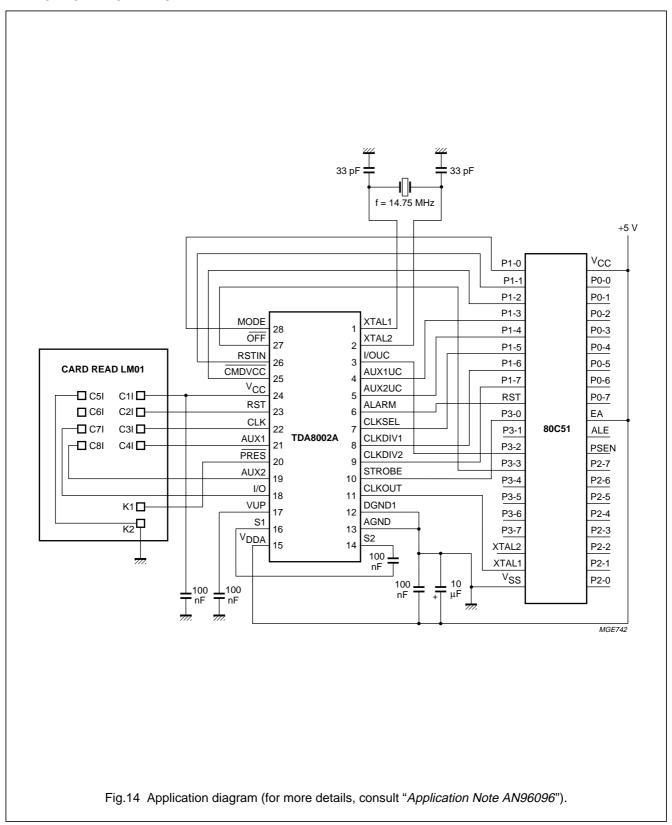

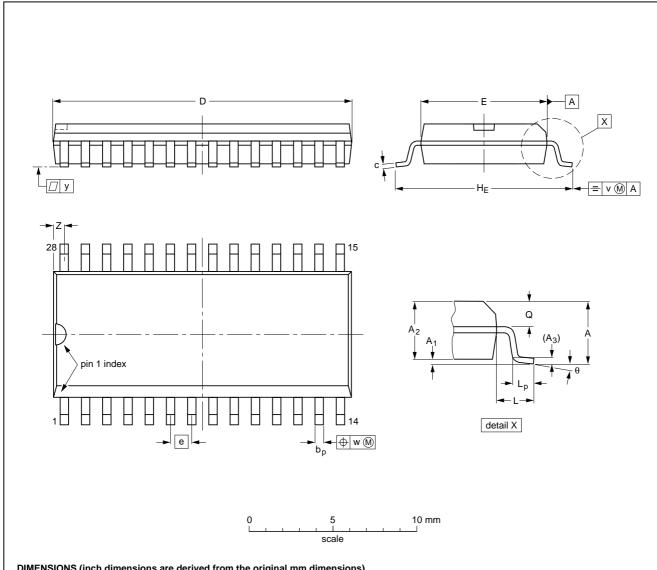

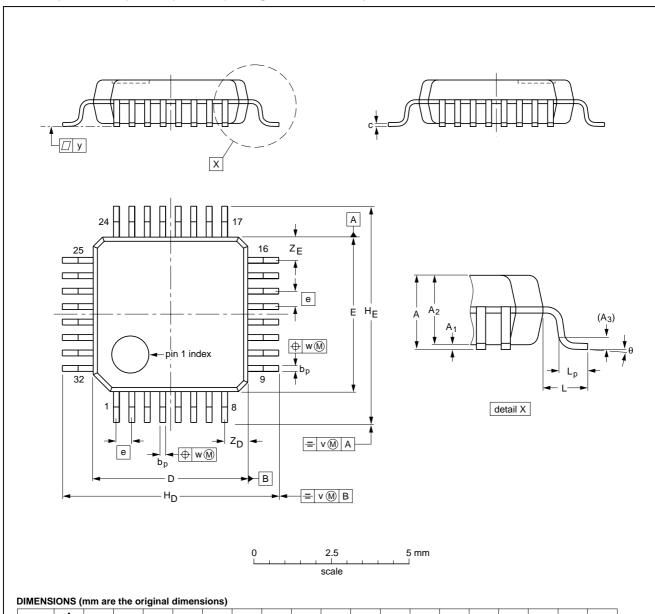

|                            |                                          | I <sub>CC</sub> < 65 mA: DC load<br>with 3.3 V < V <sub>DD</sub> < 6.5 V                              | 4.75 | _    | 5.25 | V    |