### INTEGRATED CIRCUITS

# DATA SHEET

# **UAA1570HL**Global Positioning System (GPS) front-end receiver circuit

Product specification

File under Integrated Circuits, IC18

1999 May 10

# Global Positioning System (GPS) front-end receiver circuit

### **UAA1570HL**

| CONTENT                    | rs                                           | 8            | OPERATING MODE SELECTION TABLES              |

|----------------------------|----------------------------------------------|--------------|----------------------------------------------|

| 1                          | FEATURES                                     | 8.1          | Manual selection operating modes             |

|                            | GENERAL DESCRIPTION                          | 9            | LIMITING VALUES                              |

| 2                          |                                              | 10           | THERMAL CHARACTERISTICS                      |

| 3                          | ORDERING INFORMATION                         | 11           | DC CHARACTERISTICS                           |

| 4                          | QUICK REFERENCE DATA                         | 12           | AC CHARACTERISTICS                           |

| 5                          | BLOCK DIAGRAM                                |              |                                              |

| 6                          | PINNING INFORMATION                          | 13           | CHARACTERIZATION TEST CIRCUIT                |

| 7                          | FUNCTIONAL DESCRIPTION                       | 14           | DEFAULT APPLICATION AND DEMONSTRATION BOARD  |

| 7.1                        | Low noise amplifiers LNA1 and LNA2           | 15           | INTERNAL CIRCUITRY                           |

| 7.1.1                      | LNA1IN                                       | 16           | PACKAGE OUTLINE                              |

| 7.1.2                      | LNA1OUT                                      |              |                                              |

| 7.1.3<br>7.1.4             | LNA2IN<br>LNA2OUT                            | 17           | SOLDERING                                    |

| 7.1. <del>4</del><br>7.1.5 | MX1IN                                        | 17.1         | Introduction to soldering surface mount      |

| 7.1.6                      | General remarks and results                  | 47.0         | packages                                     |

| 7.2                        | Correlation of the UAA1570HL data sheet,     | 17.2         | Reflow soldering                             |

|                            | application and test boards                  | 17.3<br>17.4 | Wave soldering<br>Manual soldering           |

| 7.3                        | RF mixer with preamplifier                   | 17.5         | Suitability of surface mount IC packages for |

| 7.4                        | VCO                                          | 17.0         | wave and reflow soldering methods            |

| 7.5                        | First IF filter                              | 18           | DEFINITIONS                                  |

| 7.6                        | Second IF mixer                              |              |                                              |

| 7.7                        | Second IF filter                             | 19           | LIFE SUPPORT APPLICATIONS                    |

| 7.8<br>7.8.1               | Time and amplitude quantization Clock inputs |              |                                              |

| 7.8.2                      | CMOS to ECL sample clock squaring circuit    |              |                                              |

| 7.8.3                      | Time quantization (sampler)                  |              |                                              |

| 7.8.4                      | TTL output stage                             |              |                                              |

| 7.8.5                      | 1-bit delays                                 |              |                                              |

| 7.9                        | Programmable synthesizer                     |              |                                              |

| 7.9.1                      | VCO prescaler                                |              |                                              |

| 7.9.2                      | Main synthesizer dividers (N-path)           |              |                                              |

| 7.9.3                      | Second local oscillator dividers (L-path)    |              |                                              |

| 7.9.4                      | Reference dividers (R-path)                  |              |                                              |

| 7.10                       | Serial interface                             |              |                                              |

| 7.10.1<br>7.10.2           | p0 and p1                                    |              |                                              |

| 7.10.2                     | r5<br>r0, r1, r2, r3 and r4                  |              |                                              |

| 7.10.4                     | n7                                           |              |                                              |

| 7.10.5                     | n0, n1, n2, n3, n4, n5 and n6                |              |                                              |

| 7.10.6                     | I0, I1, I2 and I3                            |              |                                              |

| 7.11                       | The serial interface word                    |              |                                              |

| 7.12                       | The default frequency plan                   |              |                                              |

| 7 13                       | Phase detector, charge numb and loop filter  |              |                                              |

### Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

#### 1 FEATURES

- Complete single-chip programmable double-superheterodyne C/A-code GPS receiver

- Programmable high IF frequencies supporting wideband/P-code GPS and Global Navigation Satellite System (GLONASS) applications

- Supports frequency plans with a 2nd IF of  $4 \times f_0(1.023 \text{ MHz}) = 4.092 \text{ MHz}$

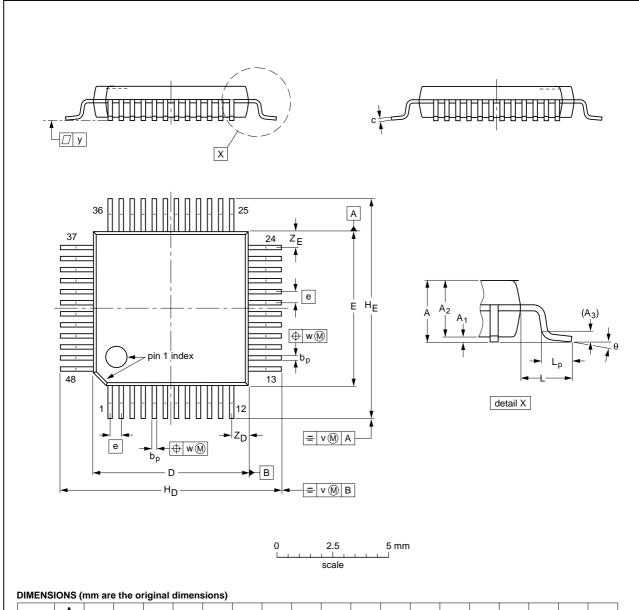

- 48-pin LQFP package

- -40 to +85 °C operating temperature range

- 2.7 V minimum supply voltage

- Low DC power consumption [57 mA typical with both Low-Noise Amplifiers (LNAs) active]

- Power-down mode (<900 μA)</li>

- Typical receiver noise figure at 1.57542 GHz: 4.5 dB

- Typical phase noise -72 dBc/Hz at 10 kHz offset

- Simple microstrip LNA1/2 and first mixer matching

- Single pin VCO with external varactor and resonator

- Digital Phase Locked Loop (DPLL) synthesizer with programmable VCO, 2nd Local Oscillator (LO) and reference dividers

- 3-bit synthesizer and power-down control input

- Reference and independent sample clock input with internal squaring

- 1-bit amplitude quantized and time sampled TTL/CMOS compatible output driver

- High active gain supporting SAW filter applications

- · Configurable for external first LNA applications.

#### 2 GENERAL DESCRIPTION

The UAA1570HL is a complete single-chip double-superheterodyne receiver front-end intended for GPS and GLONASS navigation systems. The IC includes a programmable on-chip DPLL synthesizer, VCO with external varactor and resonator, a 1-bit amplitude quantizer and a time sampled TTL/CMOS compatible SIGN output bit driver. It can be used with either an active or passive antenna system by disabling or enabling the on-chip LNAs and is ideally suited for low power GPS receiver applications because of its 3 V supply and the power management features through control pins.

Programmable prescaler controls provide the flexibility of using different frequency schemes.

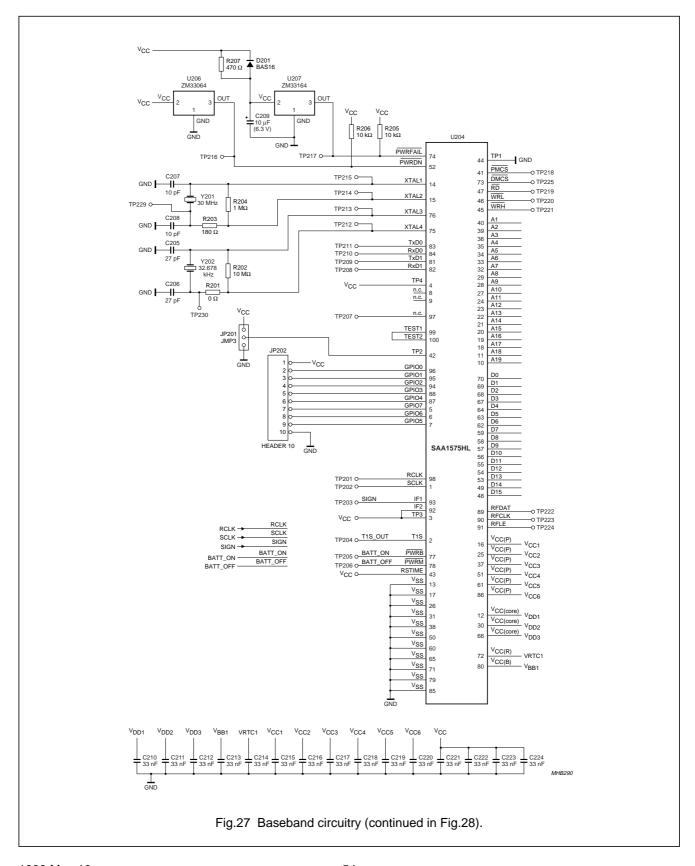

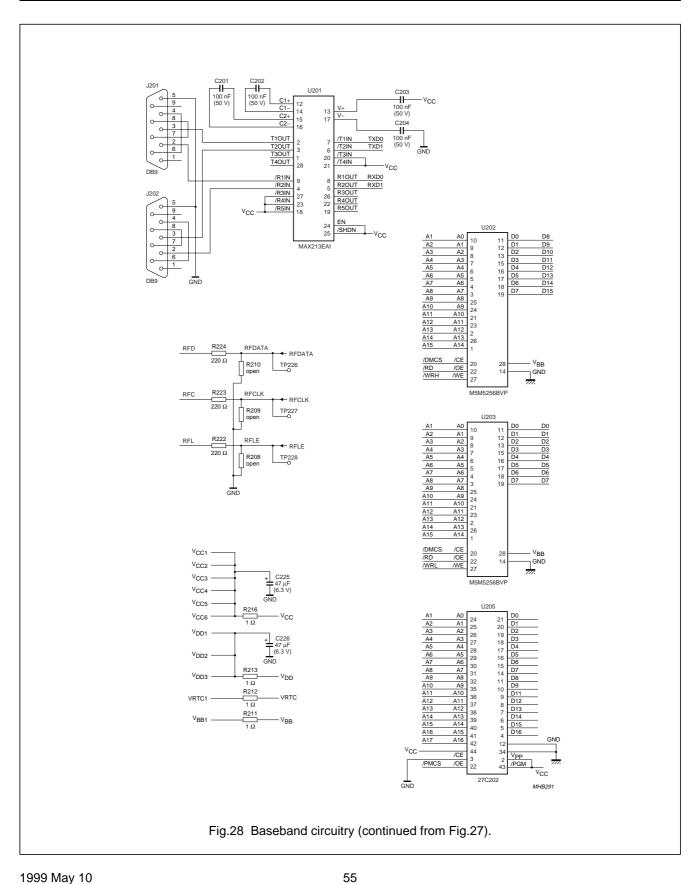

The UAA1570HL is optimized to provide SIGN bit data to the companion Philips part, the SAA1575HL baseband digital signal processor. The SAA1575HL can provide the sample clock input to the UAA1570HL by dividing a TTL/CMOS level reference clock signal down to a programmable sampling clock output frequency. Both ICs can also be used independently.

The UAA1570HL is supplied in a low profile, 48-pin LQFP package for excellent Radio Frequency (RF) performance and small size.

### 3 ORDERING INFORMATION

| TYPE      | PACKAGE                                                                                     |             |          |  |  |

|-----------|---------------------------------------------------------------------------------------------|-------------|----------|--|--|

| NUMBER    | NAME                                                                                        | DESCRIPTION | VERSION  |  |  |

| UAA1570HL | OHL LQFP48 plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm |             | SOT313-2 |  |  |

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

### 4 QUICK REFERENCE DATA

$V_{CCA}$  =  $V_{DDD}$  = 3 V;  $T_{amb}$  = 25  $\pm 2$  °C; unless otherwise specified.

| SYMBOL                                | PARAMETER                                     | CONDITIONS                                         | MIN. | TYP. | MAX. | UNIT |

|---------------------------------------|-----------------------------------------------|----------------------------------------------------|------|------|------|------|

| V <sub>CCA</sub>                      | analog supply voltage                         |                                                    | 2.7  | 3    | 5    | V    |

| $V_{DDD}$                             | digital supply voltage                        |                                                    | 2.7  | 3    | 5    | V    |

| I <sub>VCCA</sub> + I <sub>VDDD</sub> | analog supply current plus digital            | V <sub>CCA</sub> and V <sub>DDD</sub> = 2.7 V      | _    | 55.1 | 62.3 | mA   |

|                                       | supply current                                | V <sub>CCA</sub> and V <sub>DDD</sub> = 5 V        | Ī-   | 61   | 69.3 | mA   |

| G <sub>RF</sub>                       | available RF power gain                       | LNAs at 1.57542 GHz                                | Ī-   | 31   | _    | dB   |

| G <sub>IF1</sub>                      | available 1st mixer power gain                | MX1 at 1.57542 GHz                                 | Ī-   | 17.7 | _    | dB   |

| G <sub>IF2</sub>                      | available 2nd mixer power gain                | MX2 at 41.8 MHz                                    | _    | 21.4 | _    | dB   |

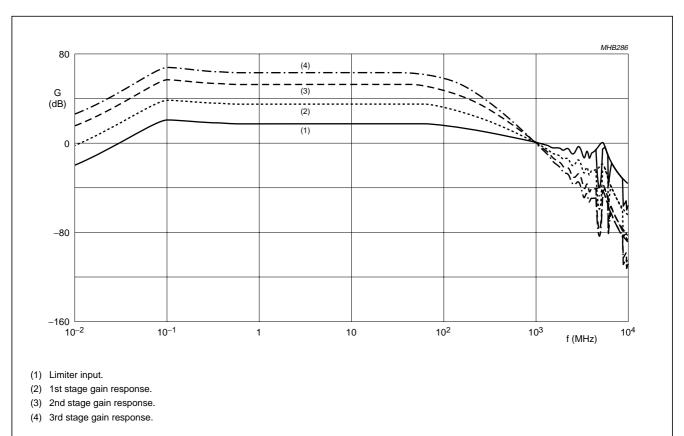

| G <sub>v(lim)</sub>                   | limiter voltage gain to 1st latch             | limiter at 3.48 MHz                                | Ī-   | 78   | _    | dBV  |

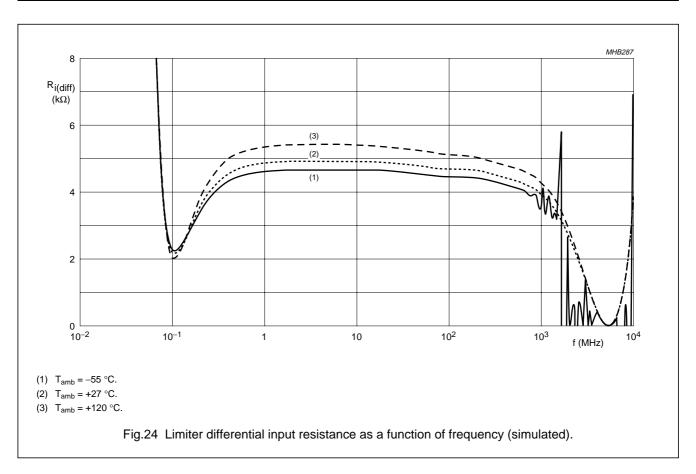

| $\Delta V_{lim(M)}$                   | differential limiter sensitivity (peak value) | f = 3.48 MHz                                       | _    | 100  | _    | μV   |

| F <sub>RX</sub>                       | receiver noise figure                         | f = 1.57542 GHz                                    | -    | 4.5  | 5.2  | dB   |

| T <sub>amb</sub>                      | operating ambient temperature                 | V <sub>CCA</sub> and V <sub>DDD</sub> = 3.3 to 5 V | -40  | +25  | +85  | °C   |

|                                       |                                               | V <sub>CCA</sub> and V <sub>DDD</sub> = 3 to 5 V   | -30  | +25  | +85  | °C   |

|                                       |                                               | $V_{CCA}$ and $V_{DDD} = 2.7$ to 5 V               | 0    | +25  | +85  | °C   |

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

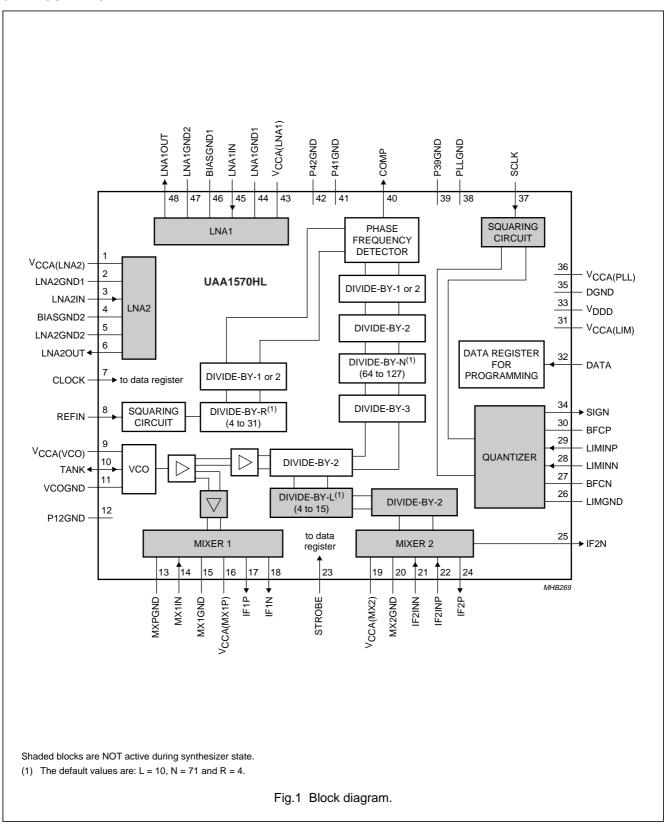

### 5 BLOCK DIAGRAM

5

1999 May 10

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

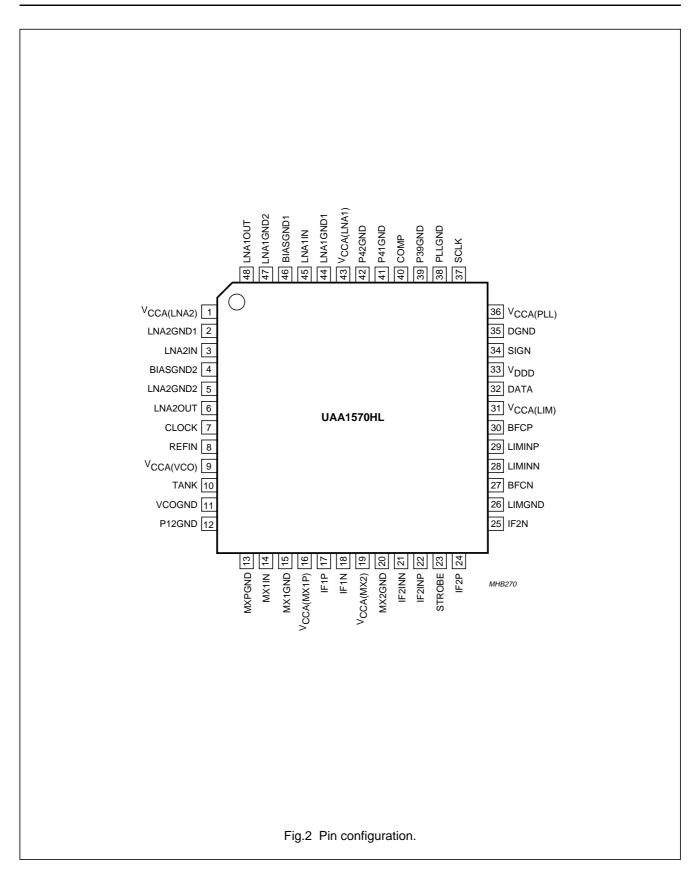

### **6 PINNING INFORMATION**

| SYMBOL                 | PIN | PIN VOLTAGE<br>TYPICAL VALUES (V) |                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |  |

|------------------------|-----|-----------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                        |     | V <sub>CC</sub> = 2.7 V           | V <sub>CC</sub> = 5 V |                                                                                                                                                                                                                                                                                                                                                                |  |

| V <sub>CCA(LNA2)</sub> | 1   | 2.7                               | 5                     | <b>LNA2 power supply:</b> DC operation range 2.7 to 5 V; use close proximity RF decoupling to pins 2, 4 and 5                                                                                                                                                                                                                                                  |  |

| LNA2GND1               | 2   | 0                                 | 0                     | LNA2 ground 1: minimize RF ground inductance                                                                                                                                                                                                                                                                                                                   |  |

| LNA2IN                 | 3   | 0.815                             | 0.807                 | LNA2 input: use external RF AC coupling                                                                                                                                                                                                                                                                                                                        |  |

| BIASGND2               | 4   | 0                                 | 0                     | LNA2 bias circuit ground: minimize RF ground inductance                                                                                                                                                                                                                                                                                                        |  |

| LNA2GND2               | 5   | 0                                 | 0                     | LNA2 ground 2: minimize RF ground inductance                                                                                                                                                                                                                                                                                                                   |  |

| LNA2OUT                | 6   | 1.48                              | 3.629                 | <b>LNA2 output:</b> use external RF AC coupling. The DC voltage is approximately 1.3 V below the V <sub>CCA(LNA2)</sub> supply on pin 1.                                                                                                                                                                                                                       |  |

| CLOCK                  | 7   | CMOS level                        | CMOS level            | Serial interface clock input: this DC coupled CMOS CLOCK input moves 20-bit programming words into the synthesizer DATA input register while the STROBE is LOW. A DC short-circuit to ground is recommended with the default frequency plan.                                                                                                                   |  |

| REFIN                  | 8   | 1.69                              | 3.99                  | <b>Reference input:</b> use external AC coupling. The DC voltage is approximately 1 V below the V <sub>CCA(PLL)</sub> supply on pin 36.                                                                                                                                                                                                                        |  |

| V <sub>CCA(VCO)</sub>  | 9   | 2.7                               | 5                     | VCO power supply: DC operation range 2.7 to 5 V; use critical close proximity RF decoupling to pin 11                                                                                                                                                                                                                                                          |  |

| TANK                   | 10  | 1.92                              | 1.92                  | VCO negative impedance resonator port: use the absolute minimum trace lengths and widths and keep the loop to the VCO ground pin 11 as short as possible, while centring the COMP output voltage at pin 40 within the charge pump output voltage range given in Chapter 11 by adjusting the resonator inductance and/or required AC coupling component.        |  |

| VCOGND                 | 11  | 0                                 | 0                     | VCO ground: minimize RF ground inductance; use critical close proximity RF decoupling to VCO supply pin 9                                                                                                                                                                                                                                                      |  |

| P12GND                 | 12  | 0                                 | 0                     | this pin provides additional RF shielding and has to be connected to ground                                                                                                                                                                                                                                                                                    |  |

| MXPGND                 | 13  | 0                                 | 0                     | RF mixer preamplifier ground: minimize RF ground inductance                                                                                                                                                                                                                                                                                                    |  |

| MX1IN                  | 14  | 0.82                              | 0.81                  | RF mixer preamplifier input: use external AC coupling and RF matching                                                                                                                                                                                                                                                                                          |  |

| MX1GND                 | 15  | 0                                 | 0                     | RF mixer ground: minimize RF ground inductance; use critical close proximity RF decoupling to V <sub>CCA(MX1P)</sub> supply pin 16                                                                                                                                                                                                                             |  |

| V <sub>CCA(MX1P)</sub> | 16  | 2.7                               | 5                     | RF preamplifier/mixer power supply: DC operation range 2.7 to 5 V; use critical close proximity RF decoupling to pin 15                                                                                                                                                                                                                                        |  |

| IF1P                   | 17  | 2.7                               | 5                     | RF mixer IF positive output: DC couple this output pin to the V <sub>CCA(MX1P)</sub> supply through first IF filter inductors or RF chokes. Capacitively decouple the supply near the output inductors. Balanced first mixer IF1 outputs are recommended. Prevent externally squared reference harmonics from entering the first IF signal path or components. |  |

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

| SYMBOL                | PIN | PIN VOLTAGE<br>TYPICAL VALUES (V) |                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |  |

|-----------------------|-----|-----------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                       |     | V <sub>CC</sub> = 2.7 V           | V <sub>CC</sub> = 5 V |                                                                                                                                                                                                                                                                                                                                                                                |  |

| IF1N                  | 18  | 2.7                               | 5                     | RF mixer IF negative output: DC couple this output pin to the V <sub>CCA(MX1P)</sub> supply through first IF filter inductors or RF chokes. Capacitively decouple the supply near the output inductors. Balanced first mixer IF1 outputs are recommended. Prevent externally squared reference harmonics from entering the first IF signal path or components.                 |  |

| V <sub>CCA(MX2)</sub> | 19  | 2.7                               | 5                     | <b>IF mixer power supply:</b> if present, decouple the common V <sub>CC</sub> line sourcing the first and second mixer by placing a large decoupling capacitor between the two                                                                                                                                                                                                 |  |

| MX2GND                | 20  | 0                                 | 0                     | <b>IF mixer ground:</b> minimize IF ground inductance; use close proximity IF decoupling to the V <sub>CCA(MX2)</sub> supply pin 19                                                                                                                                                                                                                                            |  |

| IF2INN                | 21  | 0.983                             | 0.98                  | IF mixer negative input: use external AC coupling. Balanced IF1 second mixer inputs are recommended. Prevent externally squared reference harmonics from entering the first IF signal path or components.                                                                                                                                                                      |  |

| IF2INP                | 22  | 0.983                             | 0.98                  | IF mixer positive input: use external AC coupling. Balanced IF1 second mixer inputs are recommended. Prevent externally squared reference harmonics from entering the first IF signal path or components.                                                                                                                                                                      |  |

| STROBE                | 23  | CMOS level                        | CMOS level            | Serial interface strobe input: a LOW level on this DC-coupled CMOS STROBE input enables the CLOCK input to load the 20-bit programming word into the synthesizer input DATA register. A mandatory DC short-circuit to ground is required to ensure that the default frequency plan is invoked on power-up.                                                                     |  |

| IF2P                  | 24  | 2.7                               | 5                     | IF mixer second IF positive output: DC couple this output pin to the V <sub>CCA(MX2)</sub> supply through second IF filter inductors or RF chokes. Capacitively decouple the supply near the output inductors. Balanced second mixer IF2 outputs are optional for many applications. Short the unused IF2P or IF2N output directly to the supply in single-ended applications. |  |

| IF2N                  | 25  | 2.7                               | 5                     | IF mixer second IF negative output: DC couple this output pin to the V <sub>CCA(MX2)</sub> supply through second IF filter inductors or RF chokes. Capacitively decouple the supply near the output inductors. Balanced second mixer IF2 outputs are optional for many applications. Short the unused IF2P or IF2N output directly to the supply in single-ended applications. |  |

| LIMGND                | 26  | 0                                 | 0                     | Limiter ground: minimize ground inductance                                                                                                                                                                                                                                                                                                                                     |  |

| BFCN                  | 27  | 1.696                             | 3.999                 | Negative limiter input DC feedback loop decoupling: AC couple this pin to ground in close proximity to the pin. The DC voltage is approximately 1 V below the V <sub>CCA(LIM)</sub> supply on pin 31. No DC coupling.                                                                                                                                                          |  |

| LIMINN                | 28  | 1.696                             | 3.999                 | <b>Negative limiter input:</b> AC couple this pin to the second IF filter output or to ground if unused with single-ended filter applications. The DC voltage is approximately 1 V below the V <sub>CCA(LIM)</sub> supply on pin 31. <b>No DC coupling.</b>                                                                                                                    |  |

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

| SYMBOL                | PIN | PIN VOLTAGE<br>TYPICAL VALUES (V)                |                                                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----------------------|-----|--------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                       |     | V <sub>CC</sub> = 2.7 V                          | V <sub>CC</sub> = 5 V                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| LIMINP                | 29  | 1.696                                            | 3.999                                          | Positive limiter input: AC couple this pin to the second IF filter output or to ground if unused with single-ended filter applications. The DC voltage is approximately 1 V below the V <sub>CCA(LIM)</sub> supply on pin 31. <b>No DC coupling.</b>                                                                                                                                                                                                     |  |

| BFCP                  | 30  | 1.696                                            | 3.999                                          | Positive limiter input DC feedback loop decoupling: AC couple this pin to ground in close proximity to the pin. The DC voltage is approximately 1 V below the V <sub>CCA(LIM)</sub> supply on pin 31. <b>No DC coupling.</b>                                                                                                                                                                                                                             |  |

| V <sub>CCA(LIM)</sub> | 31  | 2.7                                              | 5                                              | Limiter, sample clock squaring and sampler Emitter Coupled Logic (ECL) circuits power supply: decouple in close proximity to pins 26 and 31. If present, isolate from the common V <sub>CC</sub> line sourcing the first and second mixer by placing a large decoupling capacitor between this block and the mixers.                                                                                                                                     |  |

| DATA                  | 32  | CMOS level                                       | CMOS level                                     | Serial interface data input: this DC-coupled CMOS DATA input accepts 20-bit programming words into the synthesizer data input register, while the STROBE is LOW, on the rising edge of the CLOCK input. A DC short-circuit to ground is recommended with the default frequency plan.                                                                                                                                                                     |  |

| $V_{DDD}$             | 33  | 2.7<br>(independent<br>of V <sub>CC</sub> level) | 5<br>(independent<br>of V <sub>CC</sub> level) | SIGN bit TTL output driver power supply: critically isolate and separately decouple this digital $V_{DDD}$ supply from all other analog ( $V_{CCA}$ ) supplies. Maintain minimum trace lengths to decoupling components. Particular attention should be applied to prevent coupling into $V_{CCA(LIM)}$ pin 31. If SAA1575HL is used, use the digital supply from the back-end.                                                                          |  |

| SIGN                  | 34  | TTL output                                       | TTL output                                     | Amplitude and time quantized second IF output signal: extreme care should be taken to isolate this sampled TTL output signal from all analog traces and components, particularly the second IF filter components at the limiter input. Avoid coupling into the reference oscillator signal trace.                                                                                                                                                        |  |

| DGND                  | 35  | 0                                                | 0                                              | SIGN bit TTL output driver sink ground: critically isolate this digital supply ground from all other analog supplies and grounds Maintain minimum trace lengths to decoupling components.                                                                                                                                                                                                                                                                |  |

| V <sub>CCA(PLL)</sub> | 36  | 2.7                                              | 5                                              | Synthesizer power supply: decouple in close proximity to pin 38                                                                                                                                                                                                                                                                                                                                                                                          |  |

| SCLK                  | 37  | 1.34                                             | 2.5                                            | Sample clock squaring input: accepts LOW-level AC coupled sample clock inputs directly from the PLL reference oscillator or DC-coupled externally squared digital clocks derived from the PLL reference oscillator after external frequency division. The maximum DC-coupled input level at pin 37 should not exceed 75% of the V <sub>CCA(LIM)</sub> supply value. The threshold level is set at half the supply value on V <sub>CCA(LIM)</sub> pin 31. |  |

| PLLGND                | 38  | 0                                                | 0                                              | <b>PLL ground:</b> minimize ground inductance; use close proximity decoupling to the V <sub>CCA(PLL)</sub> supply pin 36                                                                                                                                                                                                                                                                                                                                 |  |

| P39GND                | 39  | 0                                                | 0                                              | this pin provides additional RF/IF shielding and has to be connected to ground                                                                                                                                                                                                                                                                                                                                                                           |  |

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

| SYMBOL                 | PIN | PIN VOLTAGE<br>TYPICAL VALUES (V) |                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                     |  |

|------------------------|-----|-----------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                        |     | V <sub>CC</sub> = 2.7 V           | V <sub>CC</sub> = 5 V            |                                                                                                                                                                                                                                                                                                                 |  |

| COMP                   | 40  | depends on<br>VCO<br>application  | depends on<br>VCO<br>application | Charge pump phase frequency detector output: the PLL loop filter is connected in shunt and close proximity to this pin. The PLL loop filter tuning control voltage should be routed to the external VCO varactor circuit using minimal trace lengths in complete isolation from all potential coupling sources. |  |

| P41GND                 | 41  | 0                                 | 0                                | this pin provides additional RF/IF shielding and has to be connected to ground                                                                                                                                                                                                                                  |  |

| P42GND                 | 42  | 0                                 | 0                                | this pin provides additional RF/IF shielding and has to be connected to ground                                                                                                                                                                                                                                  |  |

| V <sub>CCA(LNA1)</sub> | 43  | 2.7                               | 5                                | <b>LNA1 power supply:</b> DC operation range 2.7 to 5 V; use close proximity RF decoupling to pins 44, 46 and 47.                                                                                                                                                                                               |  |

| LNA1GND1               | 44  | 0                                 | 0                                | LNA1 ground 1: minimize RF ground inductance                                                                                                                                                                                                                                                                    |  |

| LNA1IN                 | 45  | 0.815                             | 0.807                            | LNA1 input: use external RF AC coupling                                                                                                                                                                                                                                                                         |  |

| BIASGND1               | 46  | 0                                 | 0                                | LNA1 bias circuit ground: minimize RF ground inductance                                                                                                                                                                                                                                                         |  |

| LNA1GND2               | 47  | 0                                 | 0                                | LNA1 ground 2: minimize RF ground inductance                                                                                                                                                                                                                                                                    |  |

| LNA1OUT                | 48  | 1.48                              | 3.629                            | <b>LNA1 output:</b> use external RF AC coupling. The DC voltage is approximately 1.3 V below the V <sub>CCA(LNA1)</sub> supply on pin 43.                                                                                                                                                                       |  |

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

### Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

#### 7 FUNCTIONAL DESCRIPTION

The programmability of the UAA1570HL and flexible interface definitions allow the device to be configured for a wide range of applications. To restrict the content of this document the functional description of the device will generally concentrate on the C/A-code application circuit based on the default frequency plan.

The application circuit does not allow easy measurement, calibration and documentation of the many sub-block characteristics which ensure good system performance. Therefore, test boards have been developed which allow direct measurement of the sub-block characteristics.

The tables and graphs reflect the UAA1570HL specification as derived from simulation and measured results in these characterization board environments. The tables and graphs do not directly specify application board expectations. The functional description however, focuses on the default application.

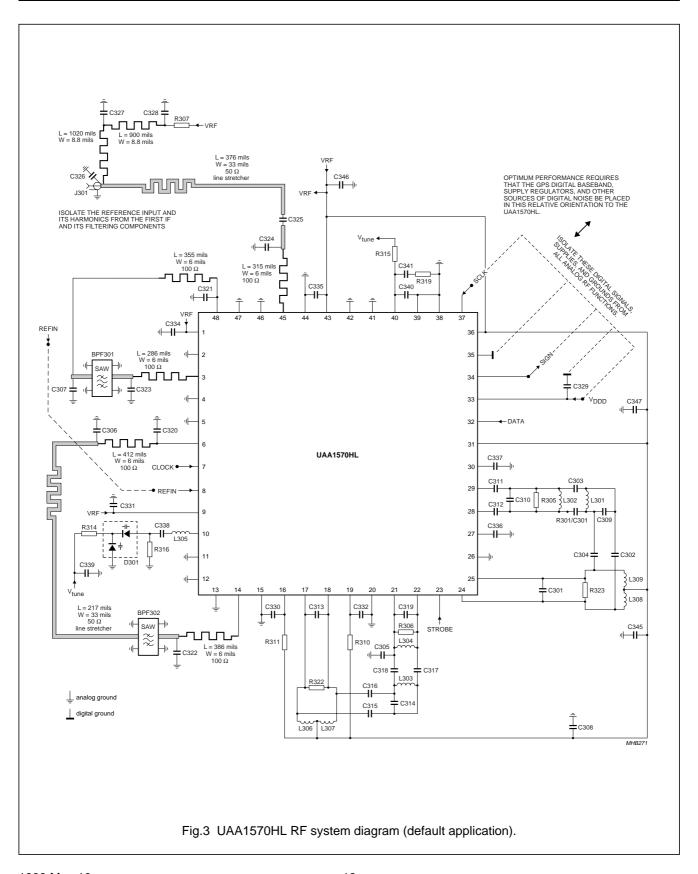

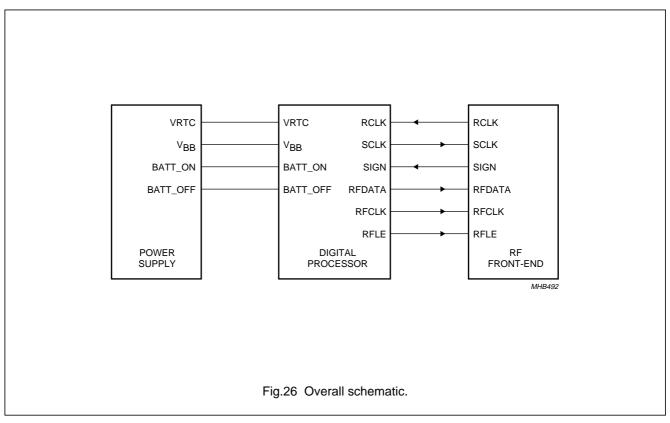

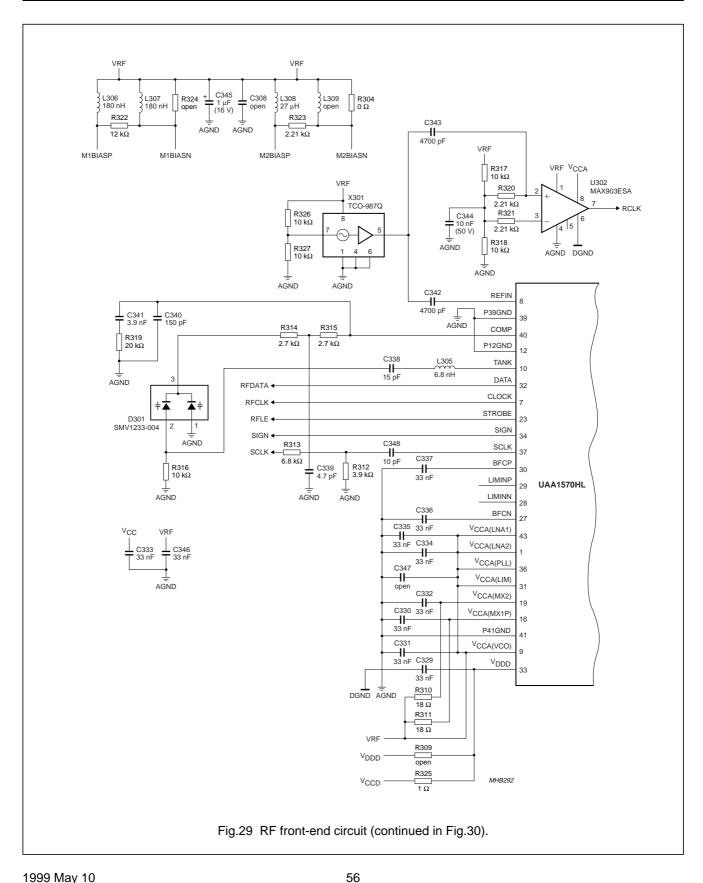

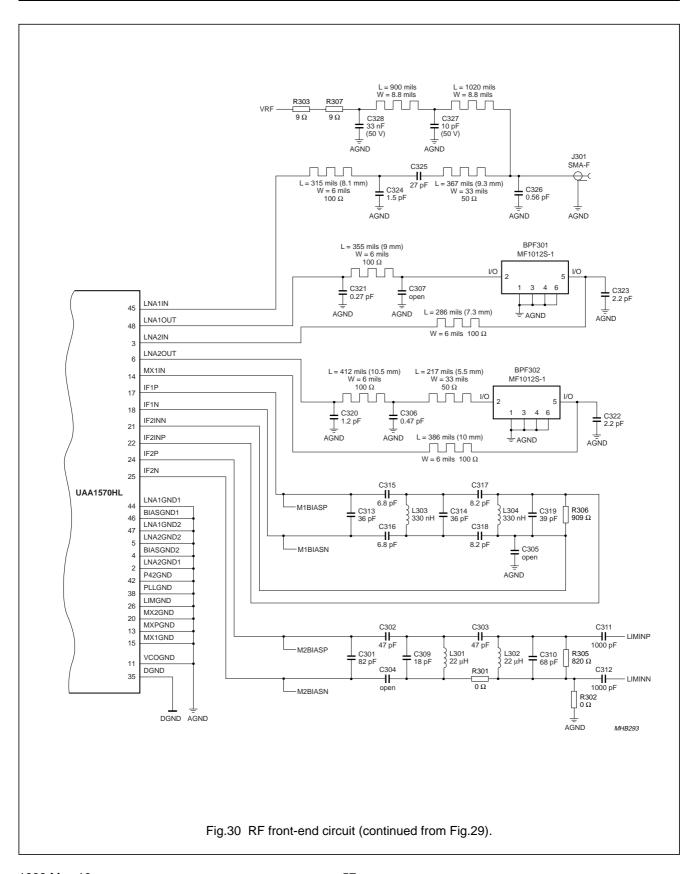

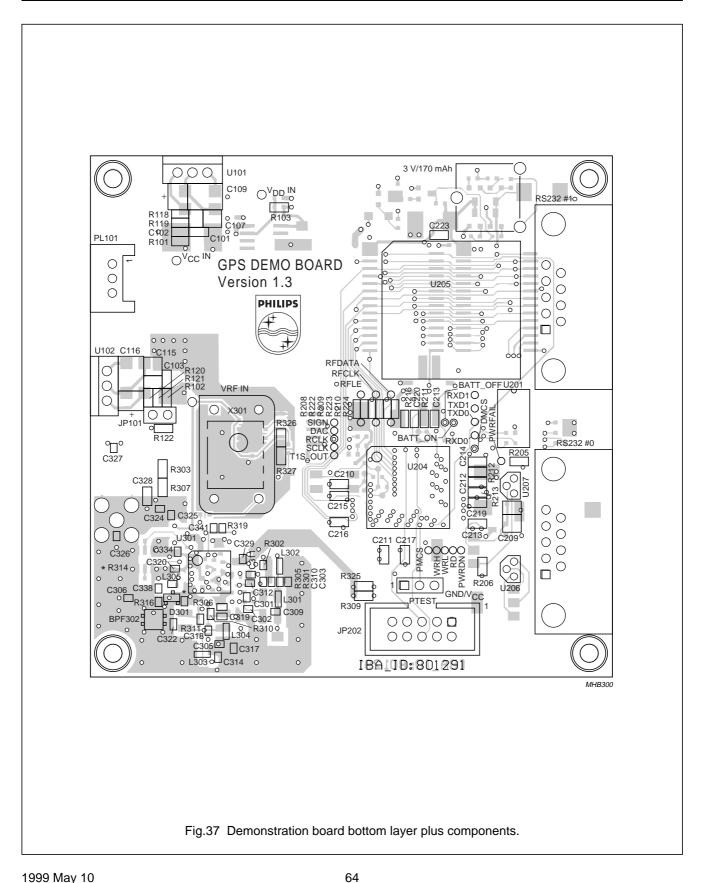

The RF system diagram (see Fig.3) illustrates the default application of the UAA1570HL in the Philips GPS demonstration board. In this application the UAA1570HL is intended to be operated directly from a passive GPS antenna through a very short antenna cable. Any cable loss in this demonstrator adds directly to the system noise figure and should therefore be minimized.

LNA1 can be powered down in the UAA1570HL to accommodate applications built around external LNAs, typically where long antenna cable runs are required.

The first LNA is assumed to be matched with a 2nd-order band-pass structure to provide some input selectivity, since no dielectric or SAW filter has been used in the demonstration board. It should be noted that low loss RF SAW filters now make it possible to significantly improve the jam immunity of this amplifier, by placing a SAW filter at the output of the antenna.

On the demonstration board the first LNA is followed by a low loss RF SAW filter (<2.4 dB).

On the demonstration board the second LNA has been matched to 50  $\Omega$  using a simple transmission line structure.

Finally, another identical RF SAW filter follows the second LNA into the first mixer.

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

### Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

### 7.1 Low noise amplifiers LNA1 and LNA2

Two identical LNAs are provided on the IC although LNA1 need not be biased, if sufficient external gain is provided by an external LNA. The input stage of each amplifier consists of an unbalanced common emitter and a cascode stage. The AC-coupled output stage is a compound feedback bootstrap amplifier. Each stage is independently biased and regulated. LNA1 can be disabled by connecting the respective supply (pin 43) to ground. LNA2 has to be powered-up even if not used.

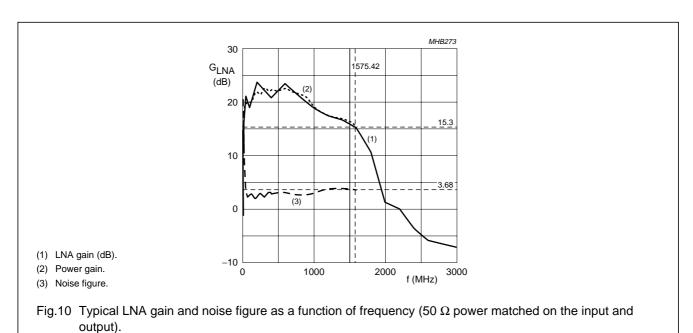

Each LNA can supply a power matched gain of approximately 15.5 dB with an associated noise figure of 3.7 dB.

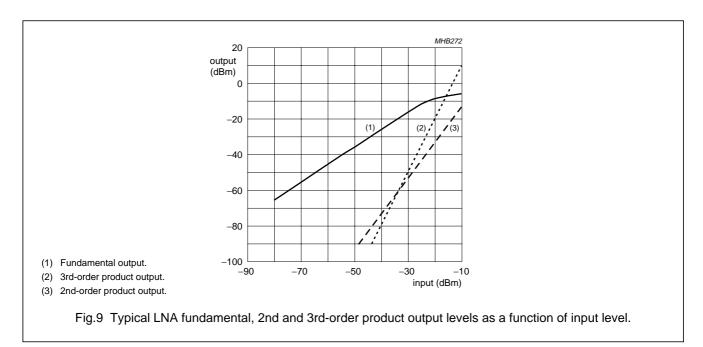

Both LNAs have –1 dB input compression points of approximately –22 dBm from a 3 V supply. The 2nd and 3rd-order input intercepts are approximately –7.9 and –13 dBm, respectively, in a power matched environment.

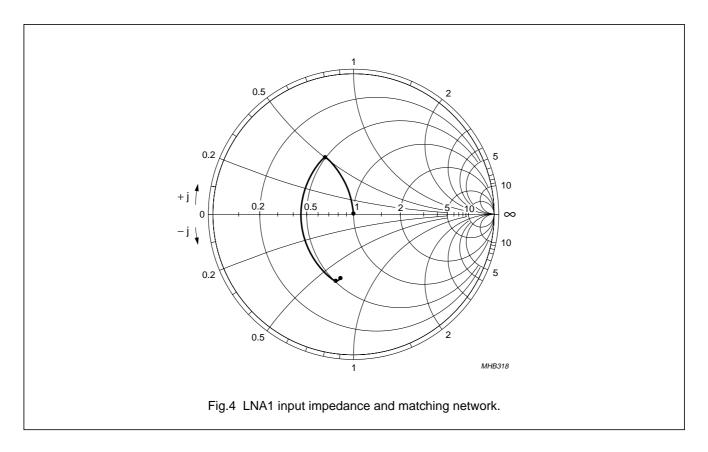

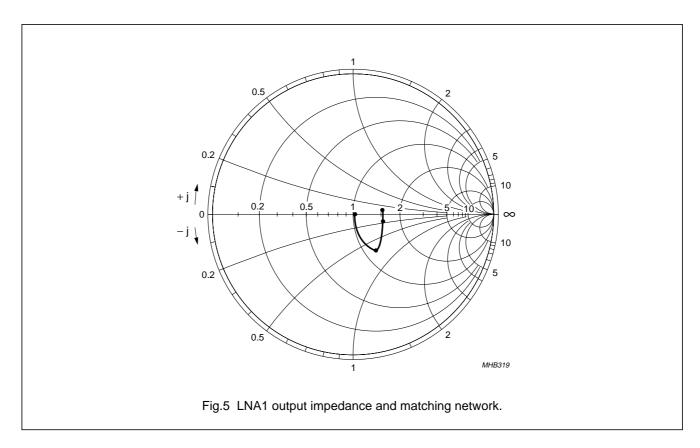

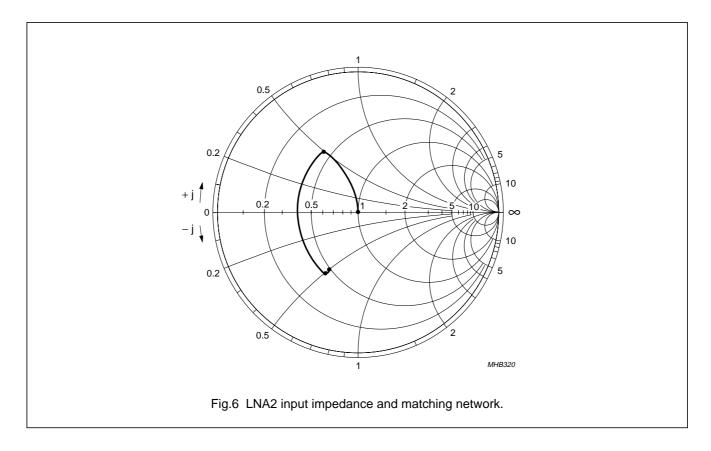

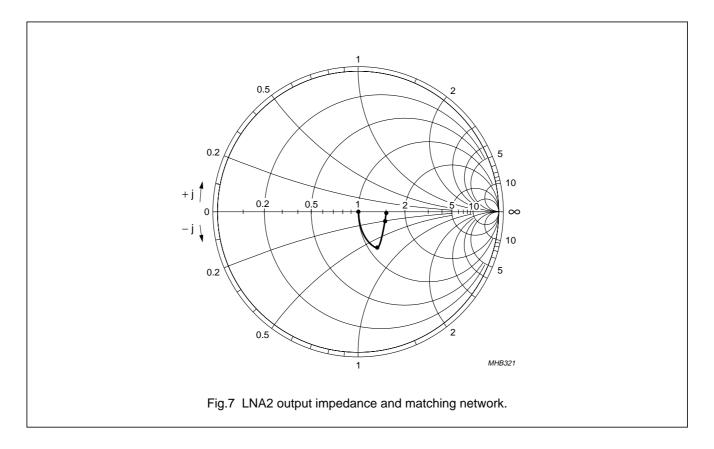

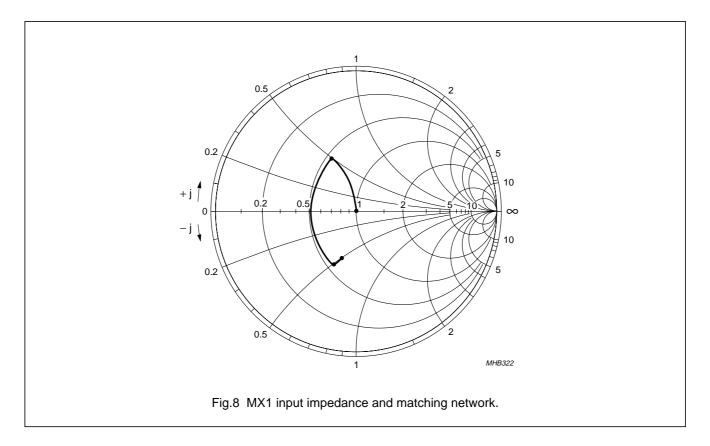

The RF match impedances at L1 (1.57542 GHz) are provided in Table 1 for all RF inputs and outputs.

Table 1 RF matching impedances

| PIN | REAL PART<br>(Ω) | IMAGINARY<br>PART (Ω) | FUNCTION        |

|-----|------------------|-----------------------|-----------------|

| 45  | 31               | −j32                  | LNA1 input      |

| 48  | 77.5             | <b>+</b> j6           | LNA1 output     |

| 3   | 24               | −j25                  | LNA2 input      |

| 6   | 74.5             | −j0.5                 | LNA2 output     |

| 14  | 33.5             | −j25.5                | 1st mixer input |

These RF port impedances are marked on the following Smith charts (see Figs 4 to 8; normalized to 50  $\Omega$ ) and suggested matching structure netlists are provided. They contain transmission lines defined by their characteristic impedance Z (in ohms), their electrical length E (in degrees) and the operating frequency f (in GHz). Capacitors C are given in pF. TLIN is a series transmission line and TLOC is an open-circuit stub transmission line. Node 1 is the UAA1570HL RF port being matched and Node 0 is ground. These matching networks are structurally identical to those illustrated on the GPS application block diagram, however, the component values in the application diagram are somewhat different to account for stray capacitances and other real world influences. The netlists are derived from EEZMATCH software (Besser Associates, Los Altos, CA, USA).

Generally, we assume a minimum shunt capacitance, due to the IC pin pad and adjacent pin strays, of approximately 0.25 pF as an initial stray element in the netlist below, that will always be present in the matching structure design. This value should be re-estimated and matched if the layout introduces significant additional strays at the pin pads.

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

### 7.1.1 LNA1IN

CAP 1 0 C = 0.25 ! C1 C = PF

TLIN 1 2 Z = 97.0 E = 34.5 F = 1.57542 ! TL1 Z = OH, E = DEG, F = GHZ

CAP 2 0 C = 2.0 ! C3 C = PF

Alternatively the 2 pF shunt capacitance at the input of the 97  $\Omega$  matching line above might be replaced with a 25  $\Omega$  microstrip open stub if space permits.

TLOC 2 0 Z = 25.0 E = 26.1 F = 1.57542

## Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

#### 7.1.2 LNA1OUT

To facilitate matching of both LNA outputs, a small shunt capacitance should be placed as close as possible to the output pin pad increasing the assumed 0.25 pF lumped pin capacitance by approximately 0.5 pF to 0.75 pF. This ensures that a simple, short, high impedance transmission line will provide a good 50  $\Omega$  match at high gain. A via to the opposite side of the board right at this output pin allows a stub or chip capacitance to be added without comprising the characteristics of the 97  $\Omega$  matching line.

CAP 1 0 C = 0.25 ! C22 C = PF

IND 1 28 L = 0.7 ! L7 = NH

CAP 28 0 C = 7.1658792e-1 ! C23 C = PF

TLIN 28 29 Z = 97.0 E = 26.239010 F = 1.57542 ! TL15

If an open line stub is used, the latter components have to be replaced by:

TLOC 28 0 Z = 20.0 E = 8.0 F = 1.57542 ! OTL7 Z = OH, E = DEG, F = GHZ

TLIN 28 30 Z = 97.0 E = 26.2 F = 1.57542 ! TL16 Z = OH, E = DEG, F = GHZ

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

7.1.3 LNA2IN

CAP 1 0 C = 0.25 ! C13 C = PF

TLIN 1 14 Z = 97.0 E = 30.0 F = 1.57542 ! TL9 Z = OH, E = DEG, F = GHZ

CAP 14 0 C = 2.3309277 ! C14 C = PF

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

7.1.4 LNA2OUT

CAP 1 0 C = 0.25 ! C22 C = PF

IND 1 31 L = 0.1 ! L8 L = NH

CAP 31 0 C = 0.5 ! C24 C = PF

TLIN 31 32 Z = 97.0 E = 25.077020 F = 1.57542 ! TL17 Z = OH, E = DEG, F = GHZ

In the event that the second capacitor is replaced by an open line stub, the last two components have to be changed:

TLOC 31 0 Z = 20.0 E = 5.5 F = 1.57542 ! OTL8 Z = OH, E = DEG, F = GHZ

TLIN 31 33 Z = 97.0 E = 24.460094 F = 1.57542 ! TL = 18 Z = OH, E = DEG, F = GHZ

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

7.1.5 MX1IN

CAP 1 0 C = 0.25 ! C5 C = PF

TLIN 1 13 Z = 100.0 E = 31.083933 F = 1.57542 ! TL9 Z = OH, E = DEG, F = GHZ

CAP 13 0 C = 1.673902 ! C6 C = PF

Again an alternative open stub line is suggested which could be used to replace the 1.67 pF capacitance at this end of the previous netlist.

TLOC 13 0 Z = 25.0 E = 23.0 F = 1.57542 ! OTL5 Z = OH, E = DEG, F = GHZ

## Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

#### 7.1.6 GENERAL REMARKS AND RESULTS

The RF match has an important effect on the gains, noise figure, and dynamic characteristics of the RF system blocks. Reflection coefficients better than –15 dB are easily attainable and can be improved to better than –25 dB with attention to details.

In the following graph (see Fig.10) the solid trace  $G_{LNA}$  (dB) represents the measured frequency response of the UAA1570HL LNAs as measured on a spectrum analyzer, while the dotted and dashed results were obtained using a noise figure meter over a more restricted frequency range.

19

1999 May 10

### Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

### 7.2 Correlation of the UAA1570HL data sheet, application and test boards

The application circuit does not allow easy measurement, calibration and documentation of the many sub-block characteristics which ensure good system performance. Therefore, test boards have been developed which allow direct measurement of the sub-block characteristics.

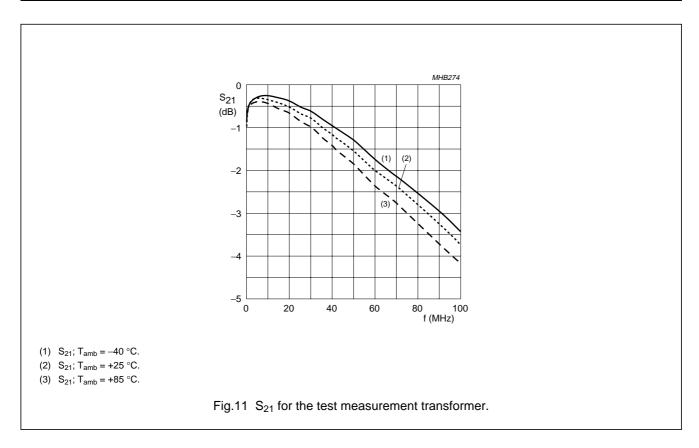

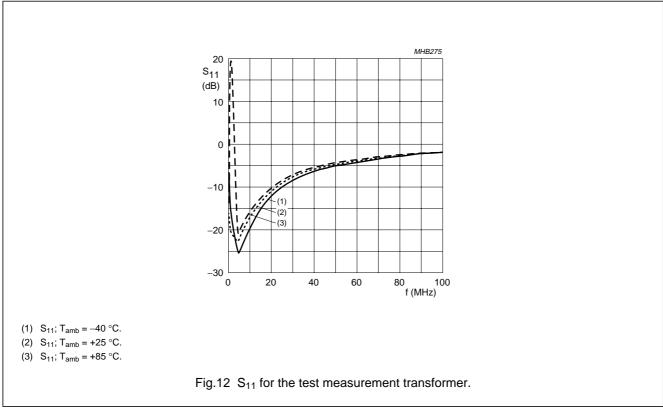

These boards use a 1 : 16  $\Omega$  ratio RF transformer to transform 50  $\Omega$  to the more appropriate value of 800  $\Omega$  at IF frequencies. The high-impedance side of these transformers is terminated with a physical resistor to adjust the UAA1570HL impedance at the port being measured, to approximately 800  $\Omega.$  This ensures that a calibrated signal is applied or received in the 50  $\Omega$  test environment. The transformer provides marginal performance at 41.8 MHz, so calibration results for this transformer are also included in this document.

The 800  $\Omega$  impedance environment is somewhat less than that used in the application board. The UAA1570HL Characteristic tables provided in this document are calibrated to this 800  $\Omega$  environment as quantified in the notes at the end of the table. The effects of the transformer and associated termination losses have also been removed to some extent, so that specifications reflect the performance of the IC. The measured graph results were all derived from the test boards and corrected to again reflect part performance as much as possible.

However, this was not always possible, so some discussion concerning the measurement limitations is provided where appropriate. Where possible, fundamental design relationships and limitations are indicated.

The following two graphs (Figs 11 and 12) reflect the measured performance of the 1 : 16  $\Omega$  ratio RF transformer used to test the IF functions. Two transformers were placed back-to-back to make these measurements. Figure 11 represents the transmission function of just one of these transformers over frequency. Figure 12 represents the associated return loss at one input with the second transformer terminated into 50  $\Omega$ . In the actual UAA1570HL test board a single transformer is terminated in 800  $\Omega$ .

In addition to the direct effects of power losses introduced by the transformer (approximately –1.3 dB at 41.82 MHz), which are reflected in the measured S21 results, the test board results may also be impacted by deficiencies in the transformer 1: 4 voltage step-up ratio at 41.8 MHz; however, this has not been quantified.

An additional correction must be made to the current test results to compensate for internal 4 pF shunt capacitors on each collector output of the first mixer, which have not been resonated out in the testing.

The first mixer measurements also include a 3 dB loss due to the 800  $\Omega$  transformer termination. This loss is also removed from the specification result. The second mixer has similar 2.1 dB input and 3 dB output transformer termination losses removed from the specification.

For measurements made at 3.48 MHz in the second IF, 0.4 dB must be added to the measured results to reflect transformer losses at IF2, also.

In summary the measured gain of the first mixer has been increased by 1.3 dB (transformer IL) + 1.4 dB (capacitive roll-off effects) + 0.2 dB (gain match) + 3 dB (output transformer termination loss) or 5.9 dB to calibrate out these losses in the specification.

The measured gain of the second mixer has been increased by 1.3 dB (input transformer IL) + 1.7 dB (input term loss) + 0.4 dB (output transformer IL) and + 3 dB (output term loss) or 6.4 dB to calibrate out these losses in the specification.

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

### Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

### 7.3 RF mixer with preamplifier

The 1st mixer (the RF mixer) consists of an RF preamplifier followed by a Gilbert cell mixer. The RF preamplifier consists of the same unbalanced common emitter and cascode stage as used in the LNAs, but without the compound feedback bootstrap output stage.

The cascode output is AC-coupled into one side of the lower tree of the Gilbert cell mixer. The other side is internally AC-coupled to mixer ground via a 20 pF decoupling capacitor. The Gilbert mixer RF input is degenerated with low loss inductive emitter feedback to increase the effective -1 dB compression point and intercept points. Referenced to the preamplifier input, the -1 dB compression point and 3rd-order intercept point are -25.4 dBm and -16.3 dBm, respectively. Another important first mixer parameter is its 2nd-order input intercept point, which will extrapolate to approximately  $1.38\ V$  (peak value) differential or +12.8 dBm in the 50  $\Omega$  mixer input environment.

The differential output of the Gilbert cell mixer is open-collector to allow optimization of conversion gain and matching to the first IF filter over a wide range of frequencies and filter options. The total conversion gain is therefore determined by the real part of the effective output load, which is given by the IF filter input impedance and loss and/or fixed filter input matching networks, if present.

The voltage conversion gain can be estimated by multiplying the effective single-ended to differential transconductance value for the first mixer (0.0531 A/V) by the total effective differential output resistance. The total power conversion gain to a differential load can be estimated from the voltage conversion gain by subtracting

$10 \log \frac{\text{diff\_load}}{50 \Omega}$  . The total power delivered by the mixer to

the output resistance is distributed between the fixed output termination, the IF filter input impedance, as well as equivalent loss impedances associated with the finite Q of filter components. The assumption has also been made that the output impedance which the mixer sees is real, at least in the IF band.

**Note**: The open-collector outputs of the first mixer each include internal 4 pF capacitors to ground. These capacitors should be included in the design of the first IF filter by removing 2 pF from the differential input capacitance for balanced filters and 4 pF from single-ended designs.

Therefore, the test circuit voltage conversion gain is estimated at 0.0531 A/V times the effective differential loading of approximately 440  $\Omega.$  This results in a voltage conversion gain of approximately 27.4 dBV. Subtracting 9.4 dB to convert from power in a 50  $\Omega$  environment to power into 440  $\Omega,$  we see that the first mixer delivers a total power conversion gain of approximately 18.0 dB in the test circuit. It is important to note that approximately 3 dB of this available power gain is lost in the test circuit output transformer termination and that much of this power can be recovered in application circuits.

The peak differential output voltage swing of the mixer should be limited to less than approximately 1 V (peak value) or 2 V (p-p) differential or 0.5 V (peak value) single-ended to prevent clipping by the internal output ESD protection diodes and to prevent mixer output saturation. This implies that effective differential output loads of approximately 2.5 k $\Omega$  could result in clipping at the output of the mixer.

The first mixer output structure also supports single-ended first IF filter applications. By taking one of the mixer outputs to the supply rail, the other can drive a single-ended first IF filter, thereby reducing external component cost in some applications. Maintaining the same single-ended loading impedance, as in the differential case (i.e. double the effective single-ended load) results in the same peak voltage across the same load, even with only half the transconductance  $\frac{1}{2}$ (0.0531 A/V) available. Therefore the same power is delivered to the same filter load and the conversion gain remains the same. However, an effective load of 1.25 k $\Omega$  would also bring this single-ended mixer output to the same clipping point as the full differential equivalent load of 2.5 k $\Omega$ . The maximum recommended first mixer single-sided voltage conversion gain (input to one output) is therefore approximately 32 for both single-ended and differential output applications.

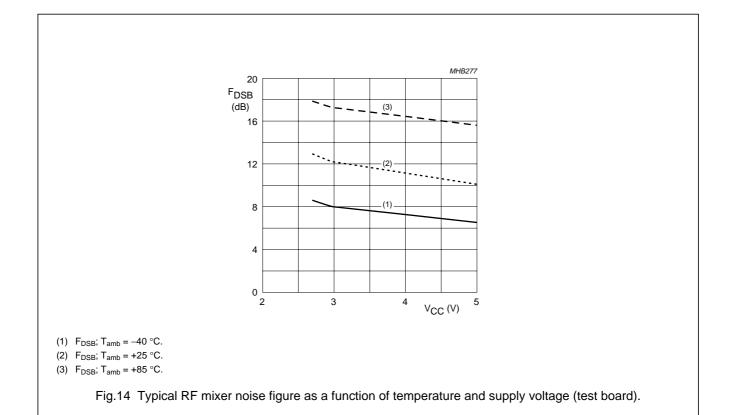

The power matched Double-Side Band (DSB) noise figure of the RF mixer with preamplifier is approximately 12 dB at 1.57542 GHz from a 3 V supply.

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

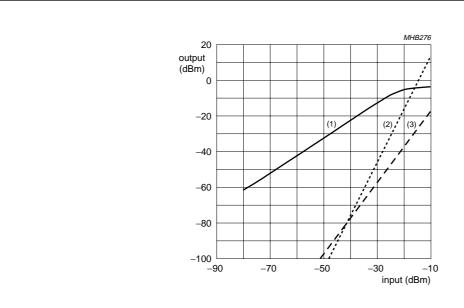

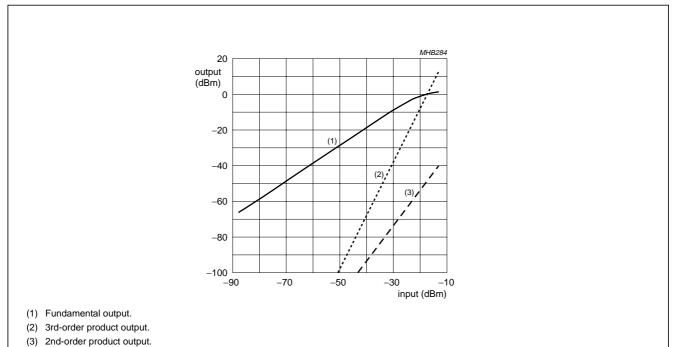

- (1) Fundamental output.

- (2) 3rd-order product output.

- (3) 2nd-order product output.

Fig.13 Typical first mixer fundamental, 2nd and 3rd-order product output levels as a function of input level.

## Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

#### 7.4 VCO

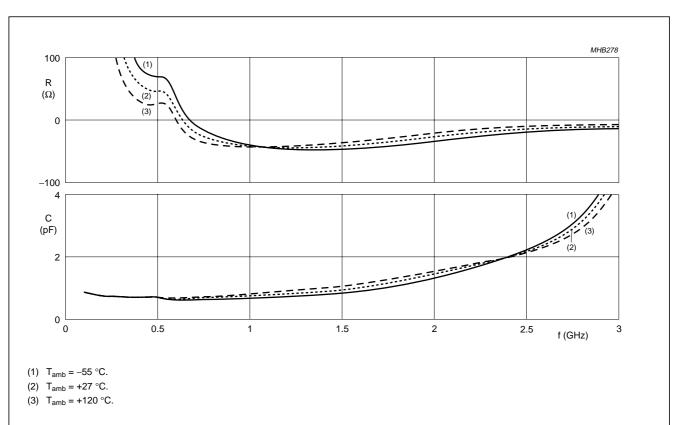

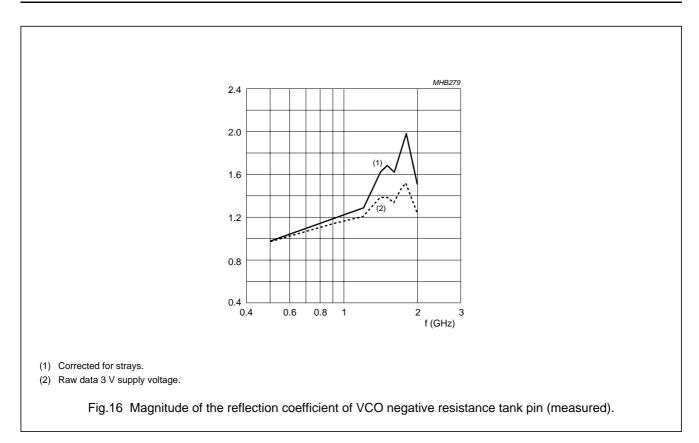

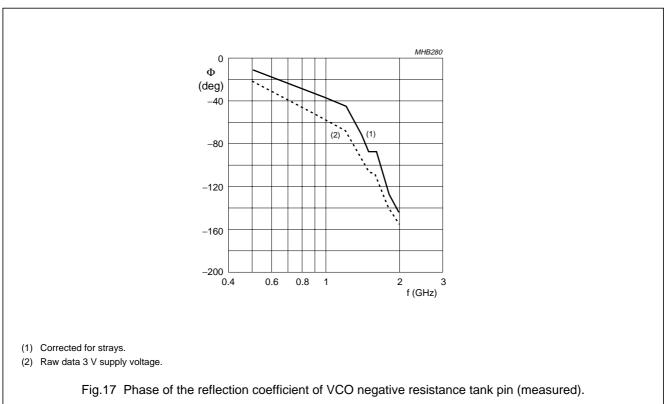

The VCO consists of a single transistor in common collector configuration with internal positive feedback realized by capacitors connected from emitter to ground and emitter to base. Together with the external resonator/inductor, this is a typical Colpitts circuit. With the transistor's base connected to pin 10 (TANK), the internal circuit arrangement produces a large negative input impedance at this pin.

At  $V_{CCA}=3~V$  and  $T_{amb}=27~^{\circ}C$  the oscillator transistor is initially biased with approximately 1.5 mA of start-up current. This value is relatively constant varying from approximately 1.56 mA at  $T_{amb}=+120~^{\circ}C$  to 1.4 mA at  $T_{amb}=-55~^{\circ}C$ . During operation, the average currents are higher due to the large amplitudes involved leading to rectification and bias point shifting.

The VCO operates as a negative impedance oscillator with a suitable external inductive resonator.

Series or parallel resonators can be used, while tuning is achieved by an external varactor diode.

VCO gain as well as the out-of-loop bandwidth phase noise are dependent on the choice of external elements used here. Consequently, they should be selected with great care; their quality factor is especially important and should be as high as possible.

Finally, the VCO is followed by a differential buffer stage with emitter follower inputs splitting the signal to the divider and LO driver stage path to increase isolation between mixer and synthesizer and their wanted or unwanted signals.

This first buffer stage is followed by two other specialized buffer amplifier stages in the individual signal paths bringing the signal to the required levels for driving a mixer or a divider.

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

### Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

#### 7.5 First IF filter

The first IF filter provides four functions:

- It provides selectivity to protect the 2nd mixer (the IF mixer) from high level spurious RF signals which pass through the wide band-pass envelope of the RF filters, typically 40 to 60 MHz.

- 2. The filter attenuates thermal noise and spurious signals in the 2nd mixer image band.

- 3. It can provide impedance matching/transformation from the RF mixer output to the IF mixer input.

- 4. It can reject spurious common mode and/or differential signals generated by high level local sources such as harmonics of the reference clock or sample clock.

The first IF can be structured to support a wide range of single-ended or balanced filters including LC or SAW realizations. High RF gain provides first IF signal levels high enough to accommodate first IF filter losses of 15 dB with optimum RF matching and conversion gain in the first mixer.

The Philips application board uses a 6th-order coupled resonator filter based on the butterworth response. The design method is described in the "Handbook of FILTER SYNTHESIS" by Anatol Zverev. The handbook tables formulate single-ended filter designs which we later convert to a balanced form.

The initial centre frequency and bandwidth were 41.82 and 4.5 MHz, respectively. The following list illustrates the tabular design 3 dB down k and q parameters from Zverev that were developed for the initial single-ended structure.

$R_s = 331.4 \Omega$

$R_1 = 689.6 \Omega$

$q_0 = 5.0$ ; insertion loss = 4.742;  $q_1 = 0.8226$ ;

$q_n=1.7115;\, k_{12}=0.6567;\, k_{23}=0.7060.$

This tabular listing was chosen based on the desired selectivity and minimal insertion loss, which could be realized with available surface mount inductors operating with quality factors (Q) in the range of 40 to 50. The impedance level is determined by the choice of design inductance (165 nH), with foresight given to eventual balancing of the design. Maximizing the load presented to the first mixer was also a consideration. With some frequency plans stability in both the first and second IF will also need to be considered when choosing the impedance level of the design.

The handbook calculations result in a preliminary single-ended three shunt tank structure with a coupling capacitor between each tank as follows:

$R_s = 331 \Omega$

Tank 1 = 165 nH in parallel with 81.6 pF

Coupling capacitor 1 = 6.2 pF

Tank 2 = 165 nH in parallel with 74.9 pF

Coupling capacitor 2 = 6.7 pF

Tank 3 = 165 nH in parallel with 81.1 pF

$R_L = 690 \Omega$ .

To convert this filter to a balanced design it can be mirrored in the ground plane which would result in the following balanced structure. It should be noted that the tank design inductances have doubled while the tank capacitances have halved, which can be seen by removing the virtual ground plane. The series elements remain unchanged in the balanced design, while the differential source and load have of course doubled.

$R_s = 663 \Omega$

Tank 1 = 330 nH in parallel with 40.8 pF

Coupling capacitor 1 = 6.2 pF

Tank 2 = 330 nH in parallel with 37.5 pF

Coupling capacitor 2 = 6.7 pF

Tank 3 = 330 nH in parallel with 40.6 pF

$R_1 = 1380 \Omega$ .

To optimize the power developed by the first mixer its load was maximized by driving the 1380  $\Omega$  side of this filter. It was also decided to bias the output of the first mixer through Tank 3 components by breaking the former differential 330 nH inductor back into two 165 nH inductors connected to the supply which also acts as a virtual ground.

The filter was then resimulated in 'SPICE' to optimize against available discrete surface mount component values with finite quality factors. All filters must be driven by their design impedances to produce their prescribed response. Since the finite quality factors of the filter inductors emulate an equivalent shunting load of approximately  $2\times\pi\times f\times L\times Q$ , the source and load terminating impedances can be increased to compensate for this parasitic element while maintaining ideal filter response and minimizing losses. In the default application, R322/306 in conjunction with the equivalent parallel resistance at the respective filter input and output give the desired terminating impedance.

### Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

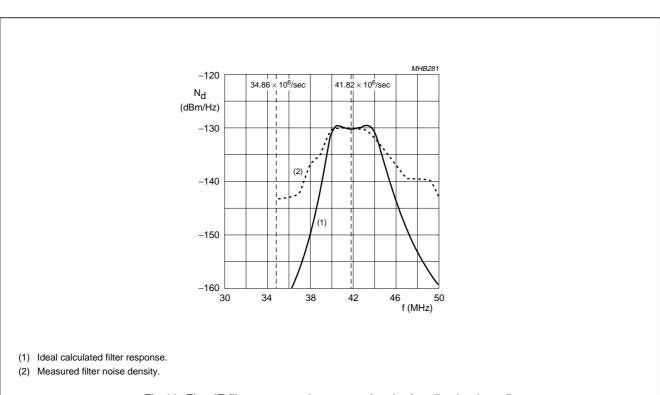

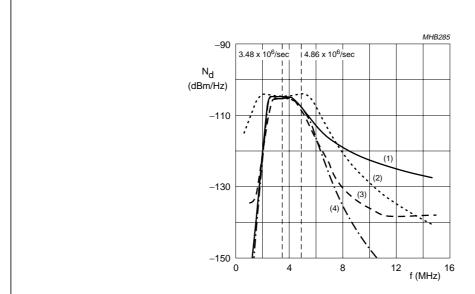

The limitation imposed by image noise is illustrated in Fig.18 where the ideal calculated filter response is compared against the measured noise density at the output of the first IF filter. The single sided FET probe measured result was corrected by +6 dB to account for

balanced processing and 10  $\log \frac{50~\Omega}{663~\Omega}$

or –11.2 dB to accommodate power conversion losses. The IF noise density selectivity is seen to be limited by the available RF gain and noise figure of the first mixer. At the image frequency, 34.86 MHz, the measured noise floor is approximately 13 dB below the desired IF level at 41.82 MHz. This will result in an image contribution to the noise figure of the system of approximately 0.2 dB.

The in-band noise density can be estimated based on the single-ended voltage gain to the output of the IF filter. With the antenna thermal input level at approximately –174 dBm/Hz, noise figure of approximately 4 dB and voltage gain from the antenna to the IF filter output of approximately 47 dBV (at 5 V supply voltage), we can expect the differential noise power density to be approximately –174 dBm + 4 dB + 47 dBV + 6 dB

(conversion to balanced) – 10 log  $\frac{663~\Omega}{50~\Omega}$

or –129 dBm/Hz. The final term converts the measured power using a high impedance FET probe, calibrated to a 50  $\Omega$  environment, to the actual 663  $\Omega$  differential filter output environment.

Fig.18 First IF filter output noise power density (application board).

### Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

#### 7.6 Second IF mixer

The second mixer is a standard Gilbert cell mixer operating with a total tail current of 4.3 mA, which is Proportional To Absolute Temperature (PTAT). The RF input, or lower tree of the mixer, is not internally terminated other than by 5 k $\Omega$  biasing resistors to each input. With no significant emitter degeneration, the real part of the RF port input impedance is dominated by the two differential junction  $R\pi s$  in parallel with the bias elements. The differential output of the Gilbert cell mixer is open-collector to allow the conversion gain and matching to the second IF filter to be optimized over a wide range of frequencies and to many types of IF filters.

The conversion voltage gain is determined by the tuned real part of the effective output load. This load may consist of the IF filter input impedance as well as fixed filter input matching compensation terminations and losses.

The voltage conversion gain can be estimated by multiplying the effective differential conversion transconductance value (0.0294 A/V) by the **total** effective differential load at the output of the mixer.

The conversion power gain is best described relative to specified mixer input and output impedance environments.

The power conversion gain is calculated by subtracting 10 log output resistance environment input resistance environment from the dBV value of the voltage conversion gain of the mixer. It should be

of the voltage conversion gain of the mixer. It should be noted that differential second mixer input terminations may be DC-coupled.

We can simplify and estimate the second mixer conversion gain in the default application by noting that the input impedance environment is approximately 663  $\Omega$ , while the output environment is approximately 1394  $\Omega$ . With effective output loading of 854  $\Omega$  (2.2 k $\Omega$  in parallel with  $0.7\times2\times996~\Omega$ ) the voltage conversion gain can therefore be expected to be approximately 25.1 V/V or 28 dBV. The power correction from 663  $\Omega$  at the input to 1394  $\Omega$  (0.7  $\times$  2  $\times$  996  $\Omega$ ) at the output is –3.2 dB, so the resulting power conversion gain is approximately 24.8 dB. The factor of 0.7 in the calculation of the impedance level is explained in Section 7.7.

It should be noted that a balanced coupled k filter can be converted to a single-ended equivalent with a single-ended input impedance exactly equal to that of the full differential filter by keeping the same tank resonator components, but placing the series coupling capacitors in single-ended series (i.e. halving the differential value) and AC grounding one side of the tanks.

The demonstration board was converted from a balanced second IF filter in this manner.

To optimize the noise figure of the second mixer the input termination admittance should be reduced. However, this will be at the expense of the mixers input compression and 3rd-order intercept characteristics. Since the RF input of the IF mixer is a simple differential stage, the input -1 dB compression point and 3rd-order intercept points are relatively fixed at approximately 67 and 215 mV (peak value), respectively, in the second mixer. This results from noting that an undegenerated differential input can be expected to have an input -1 dB compression point of approximately 36.6 mV (peak value) differential. With a small additional extrinsic emitter degeneration the -1 dB compression point is raised to approximately 67 mV (peak value) differential. This is approximately -24.7 dBm in the 663  $\Omega$  second mixer GPS application input environment with the 3rd-order intercept point being approximately 10 dB higher at -14.6 dBm. Another important second mixer parameter is its 2nd-order input intercept point, which will extrapolate to approximately 79.8 V (peak value) differential or 36.8 dBm in the 663  $\Omega$ mixer input environment.

The peak output voltage swing of the IF mixer should be limited to a peak differential swing of less than approximately 1 V (peak value) or 2 V (p-p) differential to prevent clipping by the internal output ESD protection diodes and to prevent mixer output saturation. This implies that an effective differential output load of approximately 3.2 k $\Omega$  could result in clipping at the output of the mixer.

The IF mixer supports single-ended first and second IF filter applications. A single-ended input is implemented by AC bypassing one side of the IF mixer input to ground and accepting an associated drop in mixer conversion voltage gain. It should be noted that single-ended input terminations can still be DC-coupled to the mixer input pins by using the above mentioned bypass capacitor. The IF mixer output can be made single-ended by connecting the unused mixer output to the supply rail.

Extra care should be taken to characterize single-ended first IF applications. Using a single-ended second IF filter in combination with a balanced first IF filter may help reject common mode signals not rejected by the first IF filter. However, it should be noted that the differential tank capacitors of the fully differential IF filters can be replaced by common mode capacitors by doubling the differential value and connecting two of these capacitors to ground. Any distribution between these two extremes is also acceptable.

### Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

As with the RF mixer maintaining the same single-ended load as an effective differential load would result in the same voltage applied to the equivalent resistance. However, a single-ended effective load of 1.6 k $\Omega$  could also bring this mixer output to its clipping point. The maximum recommended second mixer single-sided voltage conversion gain (one input to one output) is therefore approximately 16 for both single-ended and differential output applications.

The estimated Single-Side Band (SSB) noise figure of the IF mixer is approximately 7.5 dB at  $T_{amb}$  = 27 °C from a 3 V supply with an input termination matching resistor of 2 k $\Omega$ . Removing the termination results in an expected noise figure of 4.9 dB from a 1 k $\Omega$  source. This degradation is distributed between the input termination input loss and approximately a 1.6 dB increase in the actual mixer noise figure.

The conversion gain is expected to be relatively supply independent, increasing by only approximately 0.5 dB from a supply value of 2.7 to 5.5 V. The IF mixer RF bandwidth is also expected to only increase by approximately 4%, while the mixer noise figure is expected to decrease by less than 0.1 dB as the supply is increased over the same supply range.

The IF mixer RF bandwidth, if not resonated, is dominated by the mixer differential input capacitance of approximately 1 pF.

With tuned inputs, the IF mixer RF input bandwidth can be extended guite high, but practical consideration warrant that the RF filter terminating the input should provide band limiting, thereby restricting the RF high frequency roll-off to less than 200 MHz without special characterization efforts. This is also, generally, the upper limit that the programmable synthesizer supports. The noise figure of the IF mixer as well as the limiter can be expected to degrade as the operating frequencies are increased. For example, at 200 MHz in a terminated 100  $\Omega$  system the DSB noise figure of the IF mixer will increase by at least 10 dB to approximately 18 dB. If stability permits low impedance first IF filters can be matched into the IF mixer using step-up matching circuits such as baluns or transformer like tuned networks, to minimize the degradations.

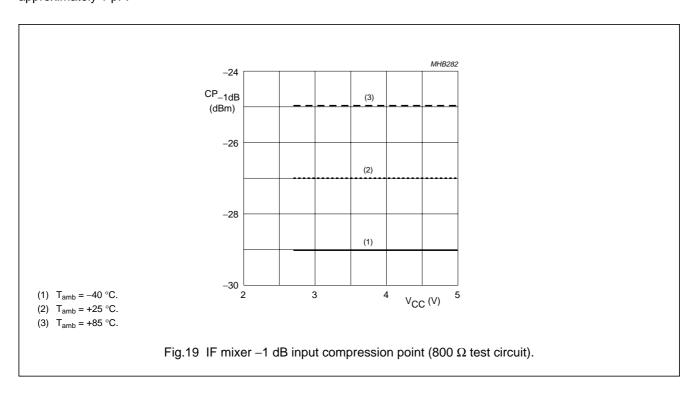

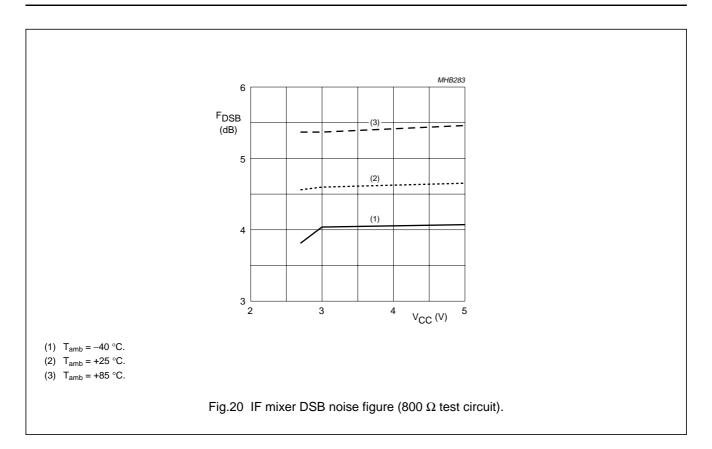

The input compression point and noise figure of the IF mixer, as measured in the characterization test board, are plotted against temperature and supply voltage in Figs 19 and 20. The characterization test board employs the 1 : 16  $\Omega$  ratio transformers to provide a 50  $\Omega$  match to the 800  $\Omega$  test environment. The losses of the input and output transformers, as well as transformer insertion losses at 41.82 and 3.48 MHz, have been removed before plotting. Therefore, this graph correlates to specification and expected performance of the second mixer in the referenced 800  $\Omega$  environment.

# Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

Fig.21 Typical second mixer fundamental, 2nd and 3rd-order product output levels as a function of input level

(800  $\Omega$  environment).

### Global Positioning System (GPS) front-end receiver circuit

UAA1570HL

#### 7.7 Second IF filter

The second IF filter provides five functions:

- 1. It provides selectivity to protect the limiter input from spurious signals which pass through the first IF band-pass filter envelope, typically 5 MHz wide.

- 2. The filter attenuates undesired second mixer output products, such as the LO leak, to levels which will not block/capture the following limiter stage.

- The filter defines and shapes the noise bandwidth to be amplitude quantized.

- 4. It can provide impedance matching/transformation from the IF mixer output to the limiter input while maintaining stability.

- It can reject spurious common mode and/or differential signals generated by high level local sources such as harmonics of the reference clock or sample clock and digital processing noise from associated devices such as the SAA1575HL.

The second IF can be structured to support a wide range of single-ended or balanced filters including LC or ceramic realizations. The available system gain can provide second IF signal levels sufficient to accommodate high second IF filter losses.

The Philips application board again uses a 6th-order coupled resonator filter based on the butterworth response. The design method is described in the "Handbook of FILTER SYNTHESIS" by Anatol Zverev. Initially a skewed centre frequency and bandwidth were input at 3.1 and 1.75 MHz, respectively, to help overcome the asymmetry which is intrinsic in geometric low frequency band-pass filter designs as they approach DC. The following table design 3 dB down k and q parameters were used:

$\begin{aligned} R_{\text{S}} &= 548~\Omega \\ R_{\text{L}} &= 996~\Omega \\ q_0 &= 20.0; \text{ insertion loss} = 0.958; \ q_1 = 0.8041; \\ q_n &= 1.4156; \ k_{12} = 0.7687; \ k_{23} = 0.6582. \end{aligned}$

This filter was originally mirrored by a virtual ground to convert it to a balanced form, but later the balanced components were converted back to a single-ended form (to reduce component count) simply by placing the balanced series capacitors in series on one side of the filter (effectively halving the capacitance value) and grounding the opposite side of the tanks where these series capacitors were removed. This effectively maintains the differential power gain while only using a single-sided output.