# Philips Components—Signetics

| Document No.  | 853-1499              |

|---------------|-----------------------|

| ECN No.       | 00731                 |

| Date of Issue | October 17, 1990      |

| Status        | Product Specification |

| ACL Products  |                       |

# AC11543: Preliminary Specification **ACT11543**: Product Specification Octal latched transceiver with dual enable (3-State)

#### **FEATURES**

- Combines '245 and '373 type functions in one chip

- 8-bit octal transceiver with D-type latch

- 3-State buffers

- Output capability: ±24 mA

- CMOS (AC) and TTL (ACT) voltage level inputs

- $50\Omega$  incident wave switching

- Center-pin V<sub>CC</sub> and ground configuration to minimize high-speed switching noise

- I<sub>CC</sub> category: MSI

### DESCRIPTION

The 74AC/ACT11543 high-performance CMOS devices combine very high speed and high output drive comparable to the most advanced TTL families.

The 74AC/ACT11543 Octal Latched Transceiver contains two sets of D-type latches for temporary storage of data flowing in either direction. Separate Latch Enable (LEAB, LEBA) and Output Enable (OEAB, OEBA) inputs are provided for each register to permit inde-(continued)

### QUICK REFERENCE DATA

| SYMBOL                                 | PARAMETER                                          | CONDI<br>T <sub>amb</sub> = 25°C;      |              | TYP | UNIT |      |

|----------------------------------------|----------------------------------------------------|----------------------------------------|--------------|-----|------|------|

| O'IIIBOL                               | TANAMETER                                          |                                        | 5.0V         | AC  |      | ACT  |

| t <sub>PLH</sub> /<br>t <sub>PHL</sub> | Propagation delay $A_n$ to $B_n$ or $B_n$ to $A_n$ | C <sub>L</sub> = 50pF                  |              | 5.5 | 6.4  | ns   |

| C <sub>PD</sub>                        | Power dissipation capacitance per                  | f = 1MHz;                              | Enabled      | 45  | 47   | pF   |

| 10                                     | transceiver <sup>1</sup>                           | C <sub>L</sub> = 50pF                  | Disabled     | 10  | 13   | , pi |

| C <sub>IN</sub>                        | Input capacitance                                  | V <sub>I</sub> = 0V or V <sub>CC</sub> | ·            | 4.5 | 4.5  | pF   |

| CNO                                    | I/Ocapacitance                                     | V <sub>V0</sub> = 0V or V <sub>0</sub> | cc; Disabled | 12  | 12   | рF   |

| LATCH                                  | Latch-up current                                   | Per Jedec JC-<br>Standard 17           | 40.2         | 500 | 500  | mA   |

- 1.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ):

- $P_D = C_{PD} \times V_{CC}^2 \times f_1 + \sum (C_L \times V_{CC}^2 \times f_0)$  where:

- $f_1$  = input frequency in MHz,  $C_L$  = output load capacitance in pF,  $f_0$  = output frequency in MHz,  $V_{CC}$  = supply voltage in V,  $\sum (C_L \times V_{CC}^2 \times f_0)$  = sum of outputs

### ORDERING INFORMATION

| PACKAGES                            | TEMPERATURE RANGE | ORDER CODE                |

|-------------------------------------|-------------------|---------------------------|

| 28-pin plastic DIP<br>(300mil-wide) | -40°C to +85°C    | 74AC11543N<br>74ACT11543N |

| 28-pin plastic SOL<br>(300mil-wide) | -40°C to +85°C    | 74AC11543D<br>74ACT11543D |

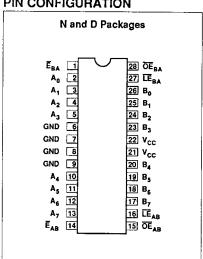

### PIN CONFIGURATION

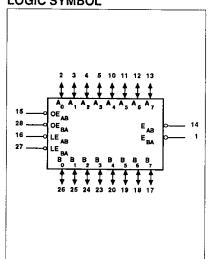

### LOGIC SYMBOL

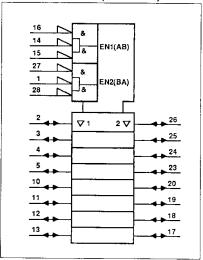

### LOGIC SYMBOL (IEEE/IEC)

# 74AC/ACT11543

pendent control of inputting and outputting in either direction of data flow.

### **FUNCTIONAL DESCRIPTION**

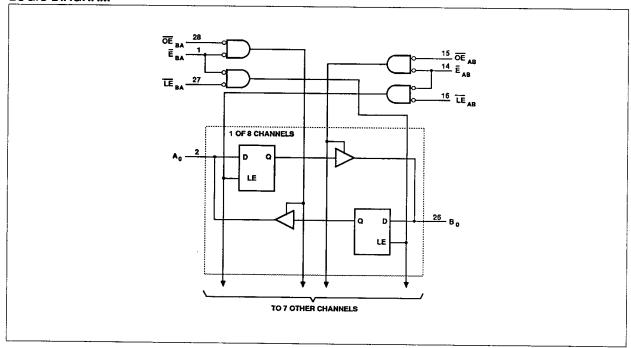

The 74AC/ACT11543 Octal Latched Transceiver contains two sets of eight D-type latches, with separate input and controls for each set. For data flow from A to B, for example, the A-to-B

Enable  $(\overline{E}_{AB})$  input must be Low in order to enter data from  $A_0$  -  $A_7$  or take data from  $B_0$  -  $B_7$  as indicated in the Function Table. With  $\overline{E}_{AB}$  Low, a Low signal on the A-to-B Latch Enable  $(\overline{LE}_{AB})$  input makes the A-to-B latches transparent; a subsequent Low-to-High transition of the  $\overline{LE}_{AB}$  signal puts the A latches in the storage mode and their

outputs no longer change with the A inputs. With  $\overline{E}_{AB}$  and  $\overline{OE}_{AB}$  both Low, the 3-State B output buffers are active and display the data present at the outputs of the A latches. Control of data flow from B to A is similar, but using the  $\overline{E}_{BA}$ ,  $\overline{LE}_{BA}$ , and  $\overline{OE}_{BA}$  inputs.

### **PIN DESCRIPTION**

| PIN NUMBER                        | SYMBOL                          | NAME AND FUNCTION                       |  |  |

|-----------------------------------|---------------------------------|-----------------------------------------|--|--|

| 15                                | OE <sub>AB</sub>                | A-to-B output enable input (active Low) |  |  |

| 28                                | OE <sub>BA</sub>                | B-to-A output enable input (active Low) |  |  |

| 16                                | LE <sub>AB</sub>                | A-to-B latch enable input (active Low)  |  |  |

| 27                                | LEBA                            | B-to-A latch enable input (active Low)  |  |  |

| 14                                | E <sub>AB</sub>                 | A-to-B enable input (active Low)        |  |  |

| 1                                 | E <sub>BA</sub>                 | B-to-A enable input (active Low)        |  |  |

| 2, 3, 4, 5,<br>10, 11, 12, 13     | A <sub>0</sub> - A <sub>7</sub> | Data inputs/outputs (A side)            |  |  |

| 26, 25, 24, 23,<br>20, 19, 18, 17 | B <sub>0</sub> - B <sub>7</sub> | Data inputs/outputs (B side)            |  |  |

| 6, 7, 8, 9                        | GND                             | Ground (0V)                             |  |  |

| 21, 22                            | V <sub>cc</sub>                 | Positive supply voltage                 |  |  |

# **FUNCTION TABLE**

|      | INP             | UTS              |        | CUTDUTO | OTATIO.             |

|------|-----------------|------------------|--------|---------|---------------------|

| OEXX | Ē <sub>XX</sub> | LE <sub>XX</sub> | Data   | OUTPUTS | STATUS              |

| Н    | Х               | х                | X      | Z       | Outputs disabled    |

| Х    | Н               | х                | X      | Z       | Outputs disabled    |

| L L  | <b>↑</b>        | L<br>L           | h<br>I | Z<br>Z  | Diasabled + latched |

| L    | L<br>L          | ↑<br>↑           | h<br>I | H<br>L  | Latch + display     |

| L    | Ł<br>L          | L<br>L           | H      | H<br>L  | Transparent         |

| Ł    | L               | Н                | Х      | NC      | Hold                |

H = High voltage level

h = High state must be present one setup time before the Low-to-High transition of  $\overline{LE}_{XX}$  or  $\overline{E}_{XX}$  (XX = AB or BA)

L = Low voltage level

I = Low state must be present one setup time before the Low-to-High transition of  $\overline{LE}_{XX}$  or  $\overline{E}_{XX}$  (XX = AB or BA)

$<sup>\</sup>uparrow$  = Low-to-High transition of  $\overline{LE}_{XX}$  or  $\overline{E}_{XX}$  (XX = AB or BA)

X = Don't care

NC = No change

Z = High-impedance state

# 74AC/ACT11543

# LOGIC DIAGRAM

# 74AC/ACT11543

### **RECOMMENDED OPERATING CONDITIONS**

| 0)/// DOI        | BARAMETER                            | 74AC11543        |          |                 | •   | UNIT |                 |      |

|------------------|--------------------------------------|------------------|----------|-----------------|-----|------|-----------------|------|

| SYMBOL           | PARAMETER                            | Min              | Nom      | Max             | Min | Nom  | Max             | UNIT |

| V <sub>cc</sub>  | DC supply voltage                    | 3.0 <sup>1</sup> | 5.0      | 5.5             | 4.5 | 5.0  | 5.5             | ٧    |

| Vı               | Input voltage                        | 0                |          | V <sub>cc</sub> | 0   |      | V <sub>cc</sub> | V    |

| V <sub>o</sub>   | Output voltage                       | 0                | <u> </u> | V <sub>cc</sub> | 0   |      | V <sub>cc</sub> | ٧    |

| Δ1/Δν            | Input transition rise or fall rate   | 0                |          | 10              | 0   |      | 10              | ns/V |

| T <sub>amb</sub> | Operating free-air temperature range | -40              |          | +85             | -40 |      | +85             | ္င   |

# ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| SYMBOL                 | PARAMETER                                                   | TEST CONDITIONS                       | RATING                       | UNIT |

|------------------------|-------------------------------------------------------------|---------------------------------------|------------------------------|------|

| Vcc                    | DC supply voltage                                           |                                       | -0.5 TO +7.0                 | V    |

| I <sub>IK</sub>        | 2                                                           | V <sub>I</sub> < 0                    | -20                          |      |

| or                     | DC input diode current <sup>2</sup>                         | V <sub>I</sub> > V <sub>CC</sub>      | 20                           | mA   |

| V <sub>I</sub>         | DC input voltage                                            |                                       | -0.5 to V <sub>CC</sub> +0.5 | V    |

| l au                   |                                                             | V <sub>0</sub> <0                     | -50                          |      |

| l OK<br>or             | DC output diode current <sup>2</sup>                        | V <sub>o</sub> >V <sub>cc</sub>       | 50                           | mA   |

| v <sub>o</sub>         | DCoutput voltage                                            |                                       | -0.5 to V <sub>CC</sub> +0.5 | V    |

| Io                     | DC output source or sink current per output pin             | V <sub>O</sub> = 0 to V <sub>CC</sub> | ±50                          | mA   |

| Icc                    | DC V <sub>CC</sub> current                                  |                                       | ±400                         |      |

| or<br>I <sub>GND</sub> | DC ground current                                           |                                       | ±400                         | - mA |

| T <sub>STG</sub>       | Storage temperature                                         |                                       | -65 to 150                   | °C   |

|                        | Power dissipation per package                               | Above 70°C; derate linearly by 8mW/K  | 500                          | mW   |

| P <sub>TOT</sub>       | Power dissipation per package<br>Plastic surface mount (SO) | Above 70°C; derate linearly by 8mW/K  | 400                          | mW   |

### NOTES:

NOTE:

1. No electrical or switching characteristics are specified at V<sub>CC</sub> < 3V. Operation between 2V and 3V is not recommended, but within that range, a device output will maintain a previously established logic state.

Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

# 74AC/ACT11543

# DC ELECTRICAL CHARACTERISTICS

|                  |                                     |                                                                        |                                            |     |                                        | _74AC | 11543                                   |      | 74ACT11543               |      |                                      |      |      |

|------------------|-------------------------------------|------------------------------------------------------------------------|--------------------------------------------|-----|----------------------------------------|-------|-----------------------------------------|------|--------------------------|------|--------------------------------------|------|------|

| SYMBOL           | MBOL PARAMETER                      |                                                                        | TEST CONDITIONS                            |     | V <sub>CC</sub> T <sub>amb</sub> = +25 |       | +25°C T <sub>amb</sub> = -40°C to +85°C |      | T <sub>amb</sub> = +25°C |      | T <sub>amb</sub> = -40°C<br>to +85°C |      | דואט |

|                  |                                     |                                                                        |                                            | V   | Min                                    | Max   | Min                                     | Max  | Min                      | Max  | Min                                  | Max  | 1    |

|                  | 1 timb to col                       |                                                                        |                                            | 3.0 | 2.10                                   |       | 2.10                                    |      |                          |      |                                      | i    |      |

| V <sub>IH</sub>  | High-level input voltage            |                                                                        |                                            | 4.5 | 3.15                                   |       | 3.15                                    |      | 2.0                      |      | 2.0                                  |      | 1 v  |

|                  |                                     |                                                                        |                                            | 5.5 | 3.85                                   |       | 3.85                                    |      | 2.0                      |      | 2.0                                  |      | 1    |

|                  | Low-level                           |                                                                        |                                            | 3.0 |                                        | 0.90  |                                         | 0.90 |                          |      |                                      |      |      |

| $V_{iL}$         | input voltage                       |                                                                        |                                            | 4.5 |                                        | 1.35  |                                         | 1.35 |                          | 0.8  |                                      | 0.8  | l v  |

|                  |                                     | L.,                                                                    |                                            | 5.5 |                                        | 1.65  |                                         | 1.65 |                          | 0.8  |                                      | 0.8  | 1    |

|                  |                                     |                                                                        |                                            | 3.0 | 2.9                                    |       | 2.9                                     |      |                          |      |                                      |      |      |

|                  |                                     |                                                                        | I <sub>OH</sub> = -50μA                    | 4.5 | 4.4                                    |       | 4.4                                     |      | 4.4                      |      | 4.4                                  |      | 1    |

|                  |                                     | ,, ,, <u>L</u>                                                         |                                            | 5.5 | 5.4                                    |       | 5.4                                     |      | 5.4                      |      | 5.4                                  |      |      |

| $V_{OH}$         | Voн High-level output voltage       | V <sub>I</sub> = V <sub>IL</sub><br>or V <sub>IH</sub>                 | 1 <sub>OH</sub> = -4mA                     | 3.0 | 2.58                                   |       | 2.48                                    |      |                          |      |                                      |      | v    |

|                  |                                     |                                                                        | l <sub>OH</sub> = -24mA                    | 4.5 | 3.94                                   |       | 3.8                                     |      | 3.94                     |      | 3.8                                  |      |      |

|                  |                                     | -                                                                      | IOH = -54IIIA                              | 5.5 | 4.94                                   |       | 4.8                                     |      | 4.94                     |      | 4.8                                  |      |      |

|                  |                                     |                                                                        | I <sub>OH</sub> = -75mA <sup>1</sup>       | 5.5 |                                        |       | 3.85                                    |      |                          |      | 3.85                                 |      |      |

|                  |                                     |                                                                        |                                            | 3.0 |                                        | 0.1   |                                         | 0.1  |                          |      |                                      |      |      |

|                  |                                     |                                                                        | l <sub>OL</sub> = 50μA                     | 4.5 |                                        | 0.1   |                                         | 0.1  |                          | 0.1  |                                      | 0.1  |      |

|                  |                                     |                                                                        |                                            | 5.5 |                                        | 0.1   |                                         | 0.1  |                          | 0.1  |                                      | 0.1  | 1    |

| V <sub>OL</sub>  | Low-level output voltage            | V <sub>I</sub> = V <sub>IL</sub><br>  or V <sub>IH</sub>               | I <sub>OL</sub> = 12mA                     | 3.0 |                                        | 0.36  |                                         | 0.44 |                          |      |                                      |      | l v  |

|                  | output voltage                      | 0, 1H                                                                  | I <sub>OL</sub> = 24mA                     | 4.5 |                                        | 0.36  |                                         | 0.44 |                          | 0.36 |                                      | 0.44 |      |

|                  |                                     |                                                                        | 10L = 24111A                               | 5.5 |                                        | 0.36  |                                         | 0.44 |                          | 0.36 |                                      | 0.44 |      |

|                  |                                     |                                                                        | I <sub>OL</sub> = 75mA <sup>1</sup>        | 5.5 |                                        |       |                                         | 1.65 |                          |      |                                      | 1.65 |      |

| l <sub>1</sub>   | Input leakage current               | V <sub>I</sub> = V <sub>CC</sub>                                       | or GND                                     | 5.5 |                                        | ±0.1  |                                         | ±1.0 |                          | ±0.1 |                                      | ±1.0 | μА   |

| loz              | 3-State output off-state current    | V <sub>I</sub> = V <sub>IL</sub> o<br>V <sub>0</sub> = V <sub>CC</sub> |                                            | 5.5 |                                        | ±0.5  |                                         | 5.0  |                          | ±0.5 |                                      | 5.0  | μA   |

| I <sub>cc</sub>  | Quiescent supply current            | V <sub>i</sub> = V <sub>CC</sub><br>I <sub>0</sub> = 0mA               |                                            | 5.5 |                                        | 8.0   |                                         | 80   | :                        | 8.0  |                                      | 80   | μА   |

| Δl <sub>CC</sub> | Supply current,<br>TTL inputs High² | One inpu                                                               | t at 3.4V, other<br>V <sub>CC</sub> or GND | 5.5 |                                        |       |                                         |      |                          | 0.9  |                                      | 1.0  | mA   |

Not more than one output should be tested at a time, and the duration of the test should not exceed 10ms.

This is the increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0V or V<sub>cc</sub>.

# 74AC/ACT11543

# AC ELECTRICAL CHARACTERISTICS AT 3.3V $\pm 0.3$ V

|                                      |                                                                                                  |          |                          | 7           | 74AC1154     | 3                                    |              | ,    |

|--------------------------------------|--------------------------------------------------------------------------------------------------|----------|--------------------------|-------------|--------------|--------------------------------------|--------------|------|

| SYMBOL                               | PARAMETER                                                                                        | WAVEFORM | T <sub>amb</sub> = +25°C |             |              | T <sub>amb</sub> = -40°C to<br>+85°C |              | UNIT |

|                                      |                                                                                                  |          | Min                      | Тур         | Max          | Min                                  | Max          |      |

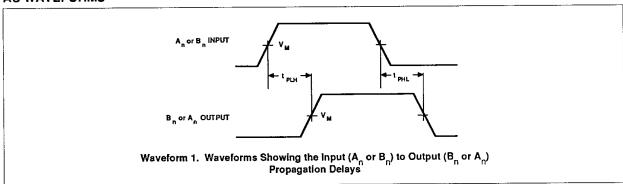

| t <sub>PLH</sub>                     | Propagation delay A <sub>n</sub> to B <sub>n</sub> or B <sub>n</sub> to A <sub>n</sub>           | 1        | 2.9<br>4.0               | 7.6<br>8.8  | 9.2<br>10.6  | 2.9<br>4.0                           | 10.4<br>11.9 | ns   |

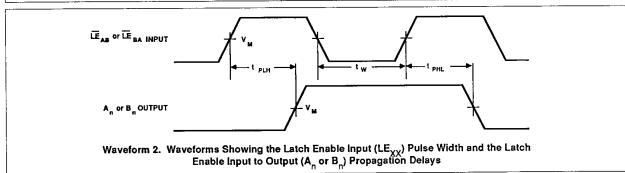

| t <sub>PLH</sub>                     | Propagation delay LE <sub>BA</sub> to A <sub>n</sub> or LE <sub>AB</sub> to B <sub>n</sub>       | 2        | 3.5<br>4.3               | 8.8<br>9.7  | 10.7<br>12.0 | 3.5<br>4.3                           | 12.0<br>13.5 | ns   |

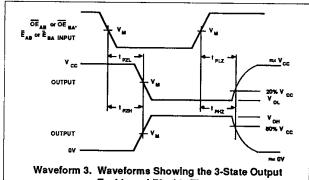

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output enable time OE <sub>BA</sub> to A <sub>n</sub> or OE <sub>AB</sub> to B <sub>n</sub>      | 3        | 3.6<br>5.2               | 8.7<br>10.4 | 10.4<br>12.8 | 3.6<br>5.2                           | 11.6<br>15.5 | ns   |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output enable time<br>E <sub>BA</sub> to A <sub>n</sub> or E <sub>AB</sub> to B <sub>n</sub>     | 3        | 4.1<br>5.7               | 9.6<br>11.3 | 11.4<br>14.1 | 4.1<br>5.7                           | 12.7<br>16.7 | ns   |

| t <sub>PHZ</sub>                     | Output disable time OE <sub>BA</sub> to A <sub>n</sub> or OE <sub>AB</sub> to B <sub>n</sub>     | 3        | 3.8<br>4.0               | 6.9<br>6.9  | 8.6<br>8.5   | 3.8<br>4.0                           | 9.3<br>9.1   | ns   |

| t <sub>PHZ</sub>                     | Output disable time<br>E <sub>BA</sub> to A <sub>n</sub> or E <sub>AB</sub> to B <sub>n</sub>    | 3        | 4.3<br>4.3               | 7.7<br>7.6  | 9.4<br>9.8   | 4.3<br>4.3                           | 10.1<br>10.4 | ns   |

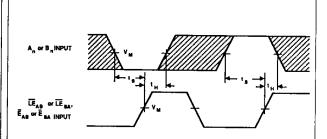

| t <sub>S</sub>                       | Setup time, High or Low A <sub>n</sub> to LE <sub>AB</sub> or B <sub>n</sub> to LE <sub>BA</sub> | 4        | 3.0                      |             |              | 3.0                                  |              | ns   |

| t <sub>H</sub>                       | Hold time, High or Low LE <sub>AB</sub> to A <sub>n</sub> or LE <sub>BA</sub> to B <sub>n</sub>  | 4        | 0.5                      |             |              | 0.5                                  |              | ns   |

| ts                                   | Setup time, High or Low $A_n$ to $\overline{E}_{AB}$ or $B_n$ to $\overline{E}_{BA}$             | 4        | 3.5                      |             |              | 3.5                                  |              | ns   |

| t <sub>H</sub>                       | Hold time, High or Low EAB to An or EBA to Bn                                                    | 4        | 0.0                      |             |              | 0.0                                  |              | ns   |

| t <sub>W</sub>                       | Latch enable pulse width Low                                                                     | 2        | 400                      |             |              | 4.0                                  |              | ns   |

# 74AC/ACT11543

# AC ELECTRICAL CHARACTERISTICS AT $5.0V\pm0.5V$

|                                      |                                                                                               |          | 74AC11543  |                          |             |            |                 |      |

|--------------------------------------|-----------------------------------------------------------------------------------------------|----------|------------|--------------------------|-------------|------------|-----------------|------|

| SYMBOL                               | PARAMETER                                                                                     | WAVEFORM | Т          | T <sub>amb</sub> = +25°C |             |            | -40°C to<br>5°C | UNIT |

| <del></del>                          |                                                                                               |          | Min        | Тур                      | Max         | Min        | Max             |      |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay $A_n$ to $B_n$ or $B_n$ to $A_n$                                            | 1        | 2.3<br>3.3 | 4.8<br>6.1               | 6.8<br>8.0  | 2.3<br>3.3 | 7.5<br>8.9      | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay  LE <sub>BA</sub> to A <sub>n</sub> or LE <sub>AB</sub> to B <sub>n</sub>   | 2        | 3.0<br>3.7 | 5.6<br>6.6               | 7.6<br>8.9  | 3.0<br>3.7 | 8.4<br>9.9      | ns   |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output enable time  OE <sub>BA</sub> to A <sub>n</sub> or OE <sub>AB</sub> to B <sub>n</sub>  | 3        | 3.1<br>4.4 | 5.7<br>7.7               | 7.6<br>9.9  | 3.1<br>4.4 | 8.3<br>11.2     | ns   |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output enable time $\overline{E}_{BA}$ to $A_n$ or $\overline{E}_{AB}$ to $B_n$               | 3        | 3.6<br>4.9 | 6.2<br>8.3               | 8.3<br>10,6 | 3.6<br>4.9 | 9.1<br>12.0     | ns   |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output disable time $\overline{OE}_{BA}$ to $A_n$ or $\overline{OE}_{AB}$ to $B_n$            | 3        | 3.5<br>3.6 | 5.5<br>5.5               | 7.2<br>7.3  | 3.5<br>3.6 | 7.7             | ns   |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output disable time<br>E <sub>BA</sub> to A <sub>n</sub> or E <sub>AB</sub> to B <sub>n</sub> | 3        | 3.9<br>4.0 | 6.0<br>6.0               | 7.7<br>8.1  | 3.9<br>4.0 | 8.3<br>8.5      | ns   |

| t <sub>S</sub>                       | Setup time, High or Low $A_n$ to $\overline{LE}_{AB}$ or $B_n$ to $\overline{LE}_{BA}$        | 4        | 2.0        |                          |             | 2.0        | 0.0             | ns   |

| t <sub>H</sub>                       | Hold time, High or Low LE <sub>BB</sub> to B <sub>n</sub>                                     | 4        | 1.0        |                          |             | 1.0        |                 | ns   |

| t <sub>S</sub>                       | Setup time, High or Low $A_n$ to $\overline{E}_{AB}$ or $B_n$ to $\overline{E}_{BA}$          | 4        | 2.5        | -                        |             | 2.5        |                 | ns   |

| Н                                    | Hold time, High or Low $\overline{E}_{AB}$ to $A_n$ or $\overline{E}_{BA}$ to $B_n$           | 4        | 0.5        |                          |             | 0.5        | -               | ns   |

| w                                    | Latch enable pulse width Low                                                                  | 2        | 4.0        |                          |             | 4.0        |                 | ns   |

# 74AC/ACT11543

AC ELECTRICAL CHARACTERISTICS AT 5.0V ±0.5V

|                                      |                                                                                                 |          |                          | 7          | 4ACT1154     | 13                   |                |      |

|--------------------------------------|-------------------------------------------------------------------------------------------------|----------|--------------------------|------------|--------------|----------------------|----------------|------|

| SYMBOL                               | PARAMETER                                                                                       | WAVEFORM | T <sub>amb</sub> = +25°C |            |              | T <sub>amb</sub> = - | 40°C to<br>5°C | UNIT |

|                                      |                                                                                                 |          | Min                      | Тур        | Max          | Min                  | Max            |      |

| PLH<br>PHL                           | Propagation delay A <sub>n</sub> to B <sub>n</sub> or B <sub>n</sub> to A <sub>n</sub>          | 1        | 3.5<br>3.2               | 6.2<br>6.5 | 9.1<br>10.8  | 3.5<br>3.2           | 10.2<br>12.1   | ns   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation delay LE <sub>BA</sub> to A <sub>n</sub> or LE <sub>AB</sub> to B <sub>n</sub>      | 2        | 3.0<br>3.7               | 6.1<br>7.2 | 10.1<br>11.7 | 3.0<br>3.7           | 11.2<br>13.2   | ns   |

| t <sub>PZH</sub>                     | Output enable time<br>OE <sub>BA</sub> to A <sub>n</sub> or OE <sub>AB</sub> to B <sub>n</sub>  | 3        | 3.3<br>3.0               | 6.4<br>8.0 | 10.5<br>12.8 | 3.3<br>3.0           | 11.5<br>15.3   | ns   |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Output enable time<br>E <sub>BA</sub> to A <sub>n</sub> or E <sub>AB</sub> to B <sub>n</sub>    | 3        | 3.5<br>3.2               | 6.7<br>8.4 | 11.1<br>13.4 | 3.5<br>3.2           | 12.2<br>16.0   | ns   |

| t <sub>PHZ</sub>                     | Output disable time<br>OE <sub>BA</sub> to A <sub>n</sub> or OE <sub>AB</sub> to B <sub>n</sub> | 3        | 4.6<br>5.0               | 6.9<br>7.1 | 9.6<br>9.8   | 4.6<br>5.0           | 10.4<br>10.5   | ns   |

| t <sub>PHZ</sub><br>t <sub>PLZ</sub> | Output disable time  E <sub>BA</sub> to A <sub>n</sub> or E <sub>AB</sub> to B <sub>n</sub>     | 3        | 4.8<br>5.1               | 7.3<br>7.5 | 10.1<br>10.3 | 4.8<br>5.1           | 11.0<br>11.1   | ns   |

| t <sub>S</sub>                       | Setup time, High or Low An to LEAB or Bn to LEBA                                                | 4        | 2.5                      |            |              | 2.5                  |                | ns   |

| t <sub>H</sub>                       | Hold time, High or Low LE <sub>AB</sub> to A <sub>n</sub> or LE <sub>BA</sub> to B <sub>n</sub> | 4        | 2.0                      |            |              | 2.0                  |                | ns   |

| t <sub>S</sub>                       | Setup time, High or Low $A_n$ to $\overline{E}_{AB}$ or $B_n$ to $\overline{E}_{BA}$            | 4        | 3.0                      |            |              | 3.0                  |                | ns   |

| t <sub>H</sub>                       | Hold time, High or Low EAB to An or EBA to Bn                                                   | 4        | 1.5                      |            |              | 1.5                  |                | ns   |

| t <sub>W</sub>                       | Latch enable pulse width<br>Low                                                                 | 2        | 4.0                      |            |              | 4.0                  |                | ns   |

# **AC WAVEFORMS**

# 74AC/ACT11543

# AC WAVEFORMS (Continued)

Enable and Disable Times

Waveform 4. Waveforms Showing the Data Setup and Hold Times for  $\mathbf{A}_{n}$  or  $\mathbf{B}_{p}$  input to Latch Enable ( $\overline{\mathsf{LE}}_{AB}$ ,  $\overline{\mathsf{LE}}_{BA}$ ) and Enable ( $\overline{\mathsf{E}}_{AB}$ ,  $\overline{\mathsf{E}}_{BA}$ ) inputs

# **WAVEFORM CONDITIONS**

|     | INPUTS                         | OUTPUTS                        |  |  |  |

|-----|--------------------------------|--------------------------------|--|--|--|

| AC  | $V_{IN} = GND$ to $V_{CC}$ ,   |                                |  |  |  |

| AC  | $V_{M} = 50\% V_{CC}$          | $V_{OUT} = V_{OL}$ to $V_{OH}$ |  |  |  |

| ACT | V <sub>IN</sub> = GND to 3.0V, |                                |  |  |  |

| AC1 | $V_{M} = 1.5V$                 | $V_{\rm M} = 50\% V_{\rm CC}$  |  |  |  |

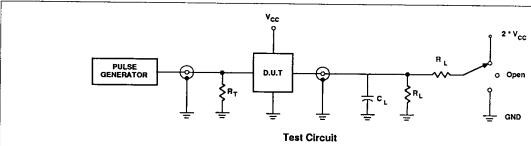

# **TEST CIRCUIT**

| TEST                               | S1                |

|------------------------------------|-------------------|

| t <sub>PLH</sub> /t <sub>PHL</sub> | Open              |

| t PLZ/t PZL                        | 2*V <sub>CC</sub> |

| t <sub>PHZ</sub> /t <sub>PZH</sub> | GND               |

## **SWITCH POSITION**

### **DEFINITIONS**

C<sub>L</sub> = Load capacitance, 50pF; includes jig and probe capacitance

$R_L = Load resistor, 500\Omega$

R<sub>T</sub> = Termination resistance should be equal to Z<sub>OUT</sub> of pulse generators

Input pulses: PRR ≤ 10MHz

$t_r = t_f = 3ns$

# **Definitions of Symbols**

#### **ACL Products**

### DEFINITIONS OF SYMBOLS AND TERMS USED IN ACL DATA SHEETS Current

Positive current is defined as conventional current flow into a device.

Negative current is defined as conventional current flow out of a device.

- I<sub>CC</sub> Quiescent power supply current; the current flowing into the V<sub>CC</sub> supply terminal.

- ΔI<sub>CC</sub> Additional quiescent supply current per input pin at a specified input voltage and V<sub>CC</sub>

- I<sub>GND</sub> Quiescent power supply current; the current flowing into the GND terminal.

- I<sub>1</sub> Input leakage current; the current flowing into a device at a specified input voltage and Vcc.

- I<sub>IK</sub> Input diode current; the current flowing into a device at a specified input voltage.

- I<sub>IO</sub> Input/output source or sink current; the current flowing into a device at a specified input/ output voltage.

- Output source or sink current; the current flowing into a device at a specified output voltage.

- I<sub>OK</sub> Output diode current; the current flowing into a device at a specified output voltage.

- I<sub>OZ</sub> OFF-state output current; the leakage current flowing into the output of a 3-State device in the OFF-state, when the output is connected to V<sub>CC</sub> or GND.

#### Voltages

All voltages are referenced to GND (ground), which is typically 0V.

- GND Supply voltage; for a device with a single negative power supply, the most negative power supply, used as the reference level for other voltages; typically ground.

- V<sub>CC</sub> Supply voltage; the most positive potential on the device.

- V<sub>EE</sub> Supply voltage; one of two (GND and V<sub>EE</sub>) negative power supplies.

- V<sub>H</sub> Hysteresis voltage; difference between the trigger levels when applying a positive and a negative-going input signal.

- V<sub>IH</sub> High-level input voltage; the range of input voltages that represents a logic High-level in the system.

- V<sub>IL</sub> Low-level input voltage; the range of input voltages that represents a logic Low-level in the system.

- VOH High-level output voltage; the range of voltages at an output terminal with a specified output loading and supply voltage.

Device inputs are conditioned to establish a High-level at the output.

- V<sub>OL</sub> Low-level output voltage; the range of voltages at an output terminal with a specified output loading and supply voltage.

Device inputs are conditioned to establish a Low-level at the output.

- V<sub>T+</sub> Trigger threshold voltage; positive-going signal.

V<sub>T</sub>. Trigger threshold voltage; negative-going signal.

#### Capacitances

- C<sub>I</sub> Input capacitance; the capacitance measured at a terminal connected to an input of a device.

- C<sub>I/O</sub> Input/Output capacitance; the capacitance measured at a terminal connected to an I/O-pin (e.g. a transceiver).

- C<sub>L</sub> Output load capacitance; the capacitance connected to an output terminal including jig and probe capacitance.

- C<sub>PD</sub> Power dissipation capacitance; the capacitance used to determine the dynamic power dissipation per logic function when no extra load is provided to the device.

### **AC Switching Parameters**

- f<sub>I</sub> Input frequency; for combinatorial logic devices the maximum number of inputs and outputs switching in accordance with the device function table. For sequential logic devices the clock frequency using alternate High and Low for data input or using the toggle mode, whichever is applicable.

- fo Output frequency; each output.

- f<sub>MAX</sub>

Maximum clock frequency; clock input waveforms should have a 50% duty factor and be such as to cause the outputs to be switching from 10% V<sub>CC</sub> to 90% V<sub>CC</sub> in accordance with device function table.

- t<sub>H</sub> Hold time; the interval immediately following the active transition of the timing pulse

# **Definitions of Symbols**

(usually the clock pulse) or following the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure their continued recognition. A negative hold time indicates that the correct logic level may be released prior to the timing pulse and still be recognized.

- t<sub>R</sub>, t<sub>F</sub> Clock input rise and fall times; 10% and 90% values.

- tpHL Propagation delay; the time between the specified reference points, normally the 50% points for 74AC devices on the input and output waveforms and the 1.5V points for the 74ACT devices, with the output changing from the defined High-level to the defined Lowlevel.

- tplh Propagation delay; the time between the specified reference points, normally the 50% points for 74AC devices on the input and output waveforms and the 1.5V point for the 74ACT devices, with the output changing from the defined Lowlevel to the defined High-level.

- tpHZ

3-State output disable time; the time between the specified reference points, normally the 50% points for the 74AC devices and the 1.5V points for the 74ACT devices on the output enable input voltage waveform and a point representing 20% of the output swing on the output voltage waveform of a 3-State device, with the output changing from a High-level (VOH) to a high-impedance OFF-state (Z).

- tpLZ

3-State output disable time;

the time between the specified

reference points, normally the

50% points for the 74AC

devices and the 1.5V points for

the 74ACT devices on the

output enable input voltage

waveform and a point representing 20% of the output

swing on the output voltage

waveform of a 3-State device,

with the output changing from a

Low-level (Vol.) to a highimpedance OFF-state (Z).

- tpzH 3-State output enable time; the time between the specified reference points, normally the 50% points for the 74AC devices and 1.5V points for the 74ACT devices on the output enable input voltage waveform and the 50% point on the output voltage waveform of a 3-State device, with the output changing from a high-impedance OFF-state (Z) to a High-level (VOH).

- t<sub>PZL</sub> 3-State output enable time; the time between the specified reference points, normally the 50% points for the 74AC devices and the 1.5V points for the 74ACT devices on the output enable input voltage waveform and the 50% point on the output voltage waveform of a 3-State device with the output changing from a high-impedance OFF-state (Z) to a Low-level (V<sub>OL</sub>).

- tree Recovery time; the time between the end of and overriding asynchronous input, typically a clear or reset input, and the earliest permissible beginning of a synchronous control input, typically a clock

- input, normally measured at the 50% points for 74AC devices and the 1.5V points for the 74ACT devices on both input voltage waveforms.

- Setup time; the interval immediately preceding the active transition of the timing pulse (usually the clock pulse) or preceding the transition of the control input to its latching level, during which interval data to be recognized must be maintained at the input to ensure their recognition. A negative setup time indicates that the correct logic level may be initiated sometime after the active transition of the timing pulse and still be recognized.

- t<sub>THL</sub> Output transition time; the time between two specified reference points on a waveform, normally 90% and 10% points, that is changing from High-to-Low.

- CTLH Output transition time; the time between two specified reference points on a waveform, normally 10% and 90% points, that is changing from Low-to-High.

- Pulse width; the time between the 50% amplitude points on the leading and trailing edges of a pulse for 74AC devices and at the 1.5V points for 74ACT devices,