PM73487 QRT

PMC-980618

Issue 3

622 Mbps ATM Traffic Management Device

# PM73487

# QRT

# 622 Mbps ATM Traffic Management Device

# DATASHEET

Released Issue 3: JUN 1999

Issue 3

622 Mbps ATM Traffic Management Device

AAL1gator, AAL1gator2, Evil Twin Switching, QRT, QSE, and SATURN are trademarks of PMC-Sierra, Inc.

AMCC is a registered trademark of Applied MicroCircuits Corporation.

i960 is a registered trademark of Intel Corporation.

National Semiconductor is a registered trademark of National Semiconductor Corporation.

is a trademark of PMC-Sierra, Inc.

Vitesse is a trademark of Vitesse Semiconductor Corporation.

All other brand or product names are trademarks of their respective companies or organizations.

U.S. Patents 5,557,607, 5,570,348, and 5,583,861

Copyright © 1998 PMC-Sierra, Inc. All Rights Reserved

Issue 3

622 Mbps ATM Traffic Management Device

## Public Revision History

| Issue Number | Issue Date   | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Issue 1      | March 1998   | Creation of Document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Issue 2      | October 1998 | This data sheet includes: registers added in B<br>version of device:<br>RX_QUEUE_ENGINE_TEST - bits 26:16<br>TX_QUEUE_ENGINE_TEST - bits 22:15<br>QUEUE_ENGINE_CONDITION_PRES_BIT<br>S<br>QUEUE_ENGINE_CONDITION_LATCH_B<br>ITS<br>QUEUE_ENGINE_INT_MASK<br>RX_LOWER16_SCG_CONFIG<br>RX_LOWER32_SCG_CONFIG<br>RX_LOWER32_SCG_STATE<br>RX_LOWER48_SCG_STATE<br>RX_LOWER48_SCG_STATE<br>TX_LOWER4_SCG_STATE<br>TX_LOWER4_SCG_STATE<br>TX_LOWER4_SCG_CONFIG<br>TX_LOWER8_SCG_CONFIG<br>TX_LOWER8_SCG_CONFIG<br>TX_LOWER8_SCG_STATE<br>TX_LOWER8_SCG_STATE<br>TX_LOWER12_SCG_CONFIG<br>TX_LOWER12_SCG_CONFIG<br>TX_LOWER12_SCG_STATE<br>Updated RX_SERVICE_TABLE |

| Issue 3      | June 1999    | Production Release Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

© 1999 PMC-Sierra, Inc. 105-8555 Baxter Place Burnaby BC Canada V5A 4V7 Phone: 604.415.6000 FAX: 604.415.6200

In any event, no part of this document may be reproduced in any form without the express written consent of PMC-Sierra, Inc.

Released Datasheet

PM73487 QRT

PMC-980618

Issue 3

622 Mbps ATM Traffic Management Device

622 Mbps ATM Traffic Management Device

# **Table of Contents**

| 1 System Applications                                            | . 4 |

|------------------------------------------------------------------|-----|

| 1.1 QRT System Overview                                          | . 4 |

| 1.2 622 Mbps Switch Configuration                                | . 5 |

| 1.3 32 x 32 Switch Application (5 Gbps)                          | . 6 |

| 1.4 64 x 64 Switch Application (10 Gbps)                         | . 6 |

| 1.5 5 Gbps to 20 Gbps Application Example - Seamless Growth      | . 7 |

| 1.6 5 Gbps to 160 Gbps Application Example – LAN-to-WAN          | . 9 |

| 2 Theory of Operations                                           | 14  |

| 2.1 Overview                                                     | 14  |

| 2.2 Interface Descriptions                                       | 14  |

| 2.2.1 Switch Fabric Interface.                                   | 14  |

| 2.2.2 Phase Aligners                                             | 15  |

| 2.2.3 UTOPIA Interface                                           | 15  |

| 2.2.4 Cell Buffer SDRAM Interface                                | 15  |

| 2.2.5 Channel RAM (CH_RAM) Interface                             | 15  |

| 2.2.6 Address Lookup RAM (AL_RAM) Interface                      | 15  |

| 2.2.7 AB_RAM Interface                                           | 15  |

| 2.2.8 Host Processor Interface                                   | 15  |

| 2.2.9 SE_SOC Encodings                                           | 16  |

| 2.2.10 BP_ACK Encodings                                          | 16  |

| 2.2.11 Relation Between External CELL_START and Local CELL_START | 17  |

| 2.3 Cell Flow Overview                                           | 18  |

| 2.4 UTOPIA Operation                                             | 19  |

| 2.4.1 General                                                    | 19  |

| 2.4.2 UTOPIA Interface                                           | 19  |

| 2.5 Receiver Operation                                           | 25  |

| 2.5.1 Receive Channel Lookup                                     | 25  |

| 2.5.2 Receive VC (Channel) Queuing.                              | 27  |

| 2.5.3 Receive Channel Ring                                       | 28  |

| 2.5.4 Receive Congestion Management                              | 29  |

| 2.5.5 Receive Queue Service Algorithm                            | 31  |

| 2.5.6 Receive Sequencing Algorithm                               | 34  |

| 2.6 Transmitter Operation                                        | 35  |

| 2.6.1 Transmit Queuing                                           | 35  |

| 2.6.2 Transmit Congestion Management.                            | 35  |

| 2.6.3 Transmit Queue Service Algorithm                           | 36  |

| 2.6.4 Transmit Resequencing Algorithm.                           | 39  |

| 2.6.5 Transmit Recovery Algorithm                                | 40  |

| 2.6.6 Transmit Multicast Cell Background Process                 |     |

| 2.6.7 Transmit Multicast Congestion Management.                  | 42  |

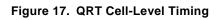

| 2.7 System Diagram of Internal QRT Blocks and External RAM       |     |

| 3 Fault Tolerance                                                | 44  |

|                                                                  |     |

Issue 3

| 3.1 The Data Path                                              |

|----------------------------------------------------------------|

| 3.1.1 UTOPIA Interface                                         |

| 3.1.2 Switch Fabric Interface                                  |

| 3.2 Fault Detection and Isolation                              |

| 3.2.1 Memory Parity Checking                                   |

| 3.2.2 UTOPIA Interface Fault Detection and Recovery Mechanisms |

| 3.2.3 Switch Fabric Fault Detection and Recovery Mechanisms    |

| 3.2.4 Tables of Switch Fabric Interface Failure Behaviors      |

| 4 Pin Descriptions                                             |

| 4.1 Package Diagram                                            |

| 4.2 Signal Locations                                           |

| 4.3 Signal Descriptions (372 Signal Pins)                      |

| 4.3.1 Processor Interface Signals                              |

| 4.3.2 Statistics Interface Signal                              |

| 4.3.3 Switch Element Interface Signals                         |

| 4.3.4 CH_RAM Interface Signals                                 |

| 4.3.5 AL_RAM Interface Signals                                 |

| 4.3.6 ABR_RAM Interface Signals                                |

| 4.3.7 Receive Cell Buffer DRAMs                                |

| 4.3.8 Transmit Cell Buffer DRAMs                               |

| 4.3.9 UTOPIA ATM Layer Interface Signals                       |

| 4.3.10 Boundary Scan Signals                                   |

| 4.3.11 Miscellaneous Signals                                   |

| 5 Physical Characteristics                                     |

| 6 Timing Diagrams                                              |

| 6.1 UTOPIA Timing                                              |

| 6.2 DRAM External Memory Timing                                |

| 6.3 SRAM Timings                                               |

| 6.4 QRT-QSE Interface Timing                                   |

| 6.4.1 Switch Fabric Cell Formats                               |

| 6.5 Processor Interface Timing                                 |

| 6.6 Miscellaneous Timing                                       |

| 7 Microprocessor Ports                                         |

| 7.1 Microprocessor Ports Summary                               |

| 7.2 Microprocessor Ports Bit Definitions                       |

| 7.2.1 REVISION                                                 |

| 7.2.2 RESET                                                    |

| 7.2.3 TEST_CONFIG                                              |

| 7.2.4 SRAM_CONFIG                                              |

| 7.2.5 SWITCH_CONFIG                                            |

| 7.2.6 RAM BIST RESULT                                          |

| 7.2.7 MARKED_CELLS_COUNT                                       |

| 7.2.8 CONDITION_PRES_BITS                                      |

| 7.2.9 CONDITION_LATCH_BITS                                     |

Issue 3

PMC-980618

622 Mbps ATM Traffic Management Device

| 7.2.10 INTR_MASK                                            | 115 |

|-------------------------------------------------------------|-----|

| 7.2.10 INTR_MASK                                            |     |

| 7.2.12 UT_PRIORITY                                          |     |

| 7.2.13 UT ENABLE                                            |     |

| 7.2.14 TX_UT_STAT                                           |     |

| 7.2.14 TX_UT_WD_ALIVE                                       |     |

|                                                             |     |

| 7.2.16 RX_CELL_START_ALIGN (Internal Structure)             |     |

|                                                             |     |

| 7.2.18 TX_QUEUE_ENGINE_TEST                                 |     |

| 7. 2. 19 QUEUE ENGINE CONDITION_PRES_BITS                   |     |

| 7. 2. 20 QUEUE_ENGINE_CONDITION_LATCH_BITS                  |     |

| 7. 2. 21 QUEUE_ENGINE_INT_MASK                              |     |

| 7.2.22 RX_DIR_CONFIG.                                       |     |

| 7.2.23 RX_DIR_STATE (Internal Structure)                    |     |

| 7.2.24 TX_DIR_CONFIG                                        |     |

| 7.2.25 TX_DIR_STATE (Internal Structure)                    |     |

| 7.2.26 RX_SENT_CELLS                                        |     |

| 7.2.27 RX_DROPPED_CELLS                                     |     |

| 7.2.28 TX_SENT_CELLS.                                       |     |

| 7.2.29 TX_DROPPED_CELLS                                     |     |

| 7. 2. 30 RX_LOWER16_SCG_CONFIG                              |     |

| 7. 2. 31 RX_LOWER16_SCG_STATE (Internal State)              |     |

| 7. 2. 32 RX_LOWER32_SCG_CONFIG                              |     |

| 7. 2. 33 RX_LOWER32_SCG_STATE (Internal State)              |     |

| 7. 2. 34 RX_LOWER48_SCG_CONFIG                              |     |

| 7. 2. 35 RX_LOWER48_SCG_STATE (Internal State)              |     |

| 7. 2. 36 TX_LOWER4_SCG_CONFIG                               |     |

| 7. 2. 37 TX_LOWER4_SCG_STATE (Internal State)               |     |

| 7. 2. 38 TX_LOWER8_SCG_CONFIG                               |     |

| 7. 2. 39 TX_LOWER8_SCG_STATE (Internal State)               |     |

| 7. 2. 40 TX_LOWER12_SCG_CONFIG                              |     |

| 7. 2. 41 TX_LOWER12_SCG_STATE (Internal State)              |     |

| 8 Internal RAM Memory Map                                   |     |

| 8.1 Internal RAM Summary                                    |     |

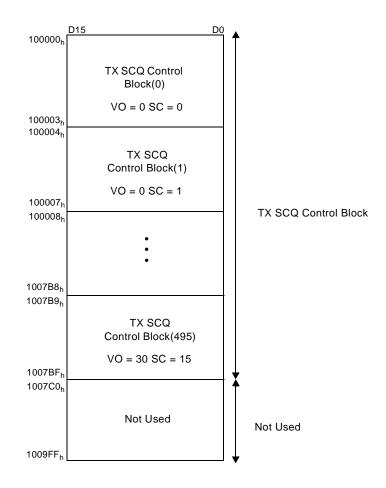

| 8.2 Transmit Service Class RAM (TSC_RAM) Summary            |     |

| 8.2.1 Transmit Service Class Queue (TX SCQ) Control Block   |     |

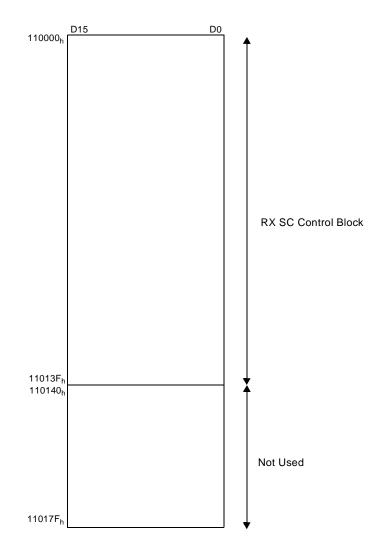

| 8.3 Receive Service Class RAM (RSC_RAM) Summary             |     |

| 8.3.1 Receive Service Class (RX SC) Control Block           |     |

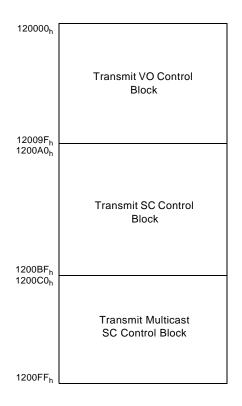

| 8.4 Virtual Output Control RAM (VO_RAM) Summary             |     |

| 8.4.1 Transmit VO Control Block                             |     |

| 8.4.2 Transmit SC Control Block                             |     |

| 8.4.3 Transmit Multicast SC Control Block Summary           |     |

| 8.5 Receive Switch Fabric Control RAM (RSF_CONTROL) Summary |     |

| 8.5.1 RX_RSF_CONFIG (Internal Structure)                    |     |

|                                                             | 107 |

Issue 3

622 Mbps ATM Traffic Management Device

| 8.5.2 RX_RSF_TAG (Internal Structure)                                        |

|------------------------------------------------------------------------------|

| 8.5.3 RX_RSF_NEW_VPI_VCI (Internal Structure)                                |

| 8.5.4 RX_RSF_SN_CHAN (Internal Structure)                                    |

| 8.5.5 RX_RSF_ER_CELL_PTR (Internal Structure)                                |

| 8.6 Transmit Switch Fabric Control RAM (TSF_CONTROL_RAM) Summary             |

| 8.6.1 TX_TSF_SN_CHAN (Internal Structure)                                    |

| 8.7 Test Access to the Receive UTOPIA RAM (RU_RAM)                           |

| 8.8 Test Access to the Transmit UTOPIA RAM (TU_RAM)                          |

| 8.9 Test Access to Receive Switch Element RAM (RS_RAM)                       |

| 8.10 Test Access to Transmit Swith Element RAM (TS_RAM) 173                  |

| 9 External RAM Memory Map                                                    |

| 9.1 External RAM Summary                                                     |

| 9.2 Address Lookup RAM (AL_RAM) 174                                          |

| 9.2.1 VI_VPI_TABLE                                                           |

| 9.2.2 VCI_TABLE                                                              |

| 9.2.3 Multicast Cell Instance Control Block (Internal Structure) 177         |

| 9.2.4 RX_NEXT_CELL (Internal Structure) 179                                  |

| 9.2.5 Transmit Cell Buffer Control Block (Internal Structure)                |

| 9.2.6 Service Order Control Block (Internal Structure)                       |

| 9.3 Channel RAM (CH_RAM)                                                     |

| 9.3.1 Channel Control Block                                                  |

| 9.3.2 Multicast Control Block                                                |

| 9.4 ABR_RAM                                                                  |

| 9.4.1 Receive Channel Queue Block                                            |

| 9.4.2 Receive Channel Statistics Block                                       |

| 9.5 SDRAM/SGRAM Interface Description                                        |

| 9.5.1 RX_DRAM_REGISTER                                                       |

| 9.5.2 TX_DRAM_REGISTER                                                       |

| 9.5.3 Receive Cell Buffer SDRAM/SGRAM Summary (Internal Structure)           |

| 9.5.4 Transmit Cell Buffer SDRAM/SGRAM Summary (Internal Structure)          |

| 10 JTAG                                                                      |

| 11 Application Notes                                                         |

| 11.1 Connecting QRTs to QSEs Using Gigabit Ethernet Transceivers             |

| 11.2 Connecting to Standard Serializer/Deserializer Chipsets                 |

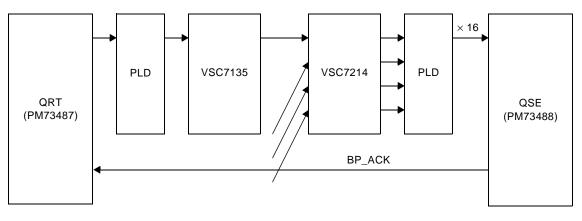

| 11.3 Connecting the QRT to the S/UNI-ATLAS PM7324                            |

| 11.4 Relationships Among Various Clock Domains                               |

| 11.4.1 Relationship Among the SYSCLK, SE_CLK, and the Switch Speed-Up Factor |

| 11.4.2 The Phase Aligner SE_CLK Frequency Constraint                         |

| 11.4.3 The SYSCLK DRAM Refresh Constraint                                    |

| 11.4.4 Relationship Between ATM_CLK and SYSCLK                               |

| 11.4.5 Relationship Between the PCLK and the SYSCLK                          |

| 11.1.5 Relationship between the Februare of Foedry                           |

622 Mbps ATM Traffic Management Device

## List of Figures

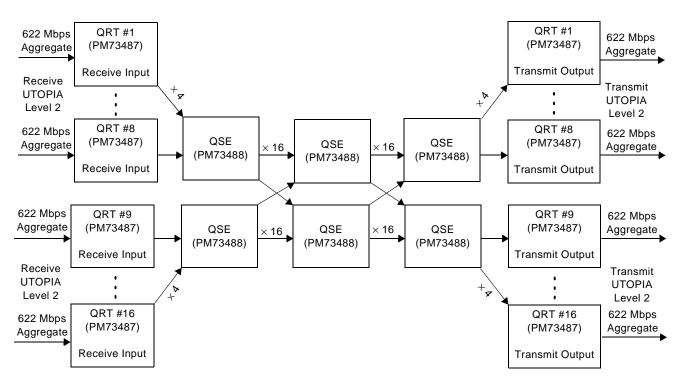

| Figure 1. QRT System Block Diagram                                                                          | . 3 |

|-------------------------------------------------------------------------------------------------------------|-----|

| Figure 2. QRT System Overview.                                                                              | . 5 |

| Figure 3. 622 Mbps Switch Configuration.                                                                    |     |

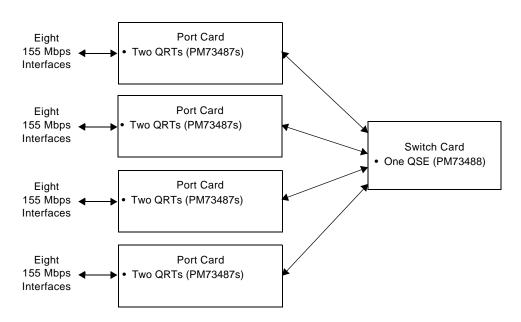

| Figure 4. 32 x 32 Switch Application (5 Gbps)                                                               | . 6 |

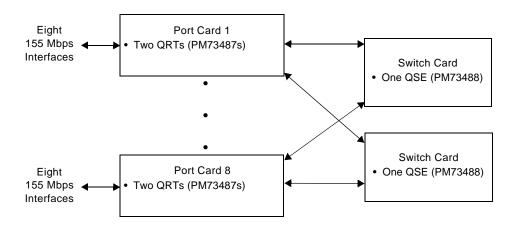

| Figure 5. 64 x 64 Switch Application (10 Gbps)                                                              |     |

| Figure 6. 5 Gbps ATM Switch Using 16 Dual S/UNIs, 8 QRTs, and 1 QSE                                         | . 7 |

| Figure 7. 10 Gbps ATM Switch Using 32 Dual S/UNIs, 16 QRTs, and 2 QSEs                                      | . 7 |

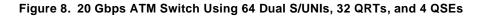

| Figure 8. 20 Gbps ATM Switch Using 64 Dual S/UNIs, 32 QRTs, and 4 QSEs                                      | . 8 |

| Figure 9. 5 Gbps to 160 Gbps Switches Modeled Using Only Two Cards                                          |     |

| Figure 10. 5 Gbps ATM Switch                                                                                | 10  |

| Figure 11. 10 Gbps ATM Switch                                                                               | 11  |

| Figure 12. 15 Gbps ATM Switch.                                                                              | 12  |

| Figure 13. 20 Gbps ATM Switch.                                                                              | 13  |

| Figure 14. QRT System Overview                                                                              | 14  |

| Figure 15. SE_SOC Encodings                                                                                 |     |

| Figure 16. BP_ACK Encodings                                                                                 | 16  |

| Figure 17. QRT Cell-Level Timing                                                                            | 17  |

| Figure 18. QRT Data Flow Diagram                                                                            |     |

| Figure 19. Receive UTOPIA Operation                                                                         | 20  |

| Figure 20. Transmit UTOPIA Operation                                                                        | 20  |

| Figure 21. Receive Standard Single Cell Available Polling                                                   | 21  |

| Figure 22. Transmit Standard Single Cell Available Polling.                                                 | 21  |

| Figure 23. Receive UTOPIA Multiplexed Status Polling (MSP), Including Cell Transfer.                        | 22  |

| Figure 24. Transmit UTOPIA 50 MHz Multiplexed Status Polling (MSP), Including Cell Transfer                 |     |

| Figure 25. VCC Channel Lookup                                                                               | 25  |

| Figure 26. VPC Channel Lookup                                                                               |     |

| Figure 27. Channel Linked List                                                                              |     |

| Figure 28. Channel Linked List – a New Cell Arrives                                                         | 27  |

| Figure 29. Channel Linked List – a Cell Is Sent to the Fabric.                                              |     |

| Figure 30. Receive Channel Ring                                                                             | 28  |

| Figure 31. Receive Channel Ring after Channel_A Becomes Run-Limited                                         | 28  |

| Figure 32. Receive Channel Ring after Channel_B is Served But It is Not Run-Limited                         |     |

| Figure 33. Receive Channel Ring After Channel_A Gets Cell Through Fabric and is Added to Ring               | 29  |

| Figure 34. Receive Congestion Limits.                                                                       | 29  |

| Figure 35. EPD/PTD Operation                                                                                | 30  |

| Figure 36. EPD/PTD with CLP Operation                                                                       | 30  |

| Figure 37. EFCI Operation.                                                                                  | 31  |

| Figure 38. Steps to Send a Cell to the Fabric                                                               | 31  |

| Figure 39. Receive Service Class (SC) Map.                                                                  |     |

|                                                                                                             |     |

| Figure 40. Transmit Per-SCQ Linked List                                                                     |     |

| Figure 40. Transmit Per-SCQ Linked List.         Figure 41. Transmit Maximum and Congested Threshold Checks | 35  |

Issue 3

622 Mbps ATM Traffic Management Device

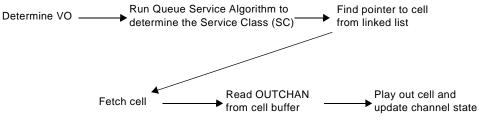

| Figure 43. Cell Playout Steps.                                    |     |

|-------------------------------------------------------------------|-----|

| Figure 44. Transmit Resequencing Operation                        |     |

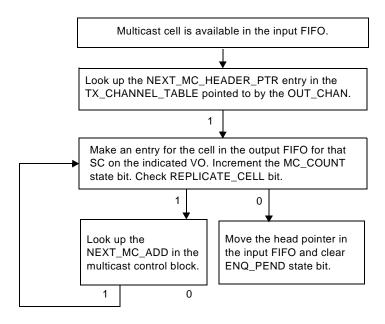

| Figure 45. Multicast Background Process                           |     |

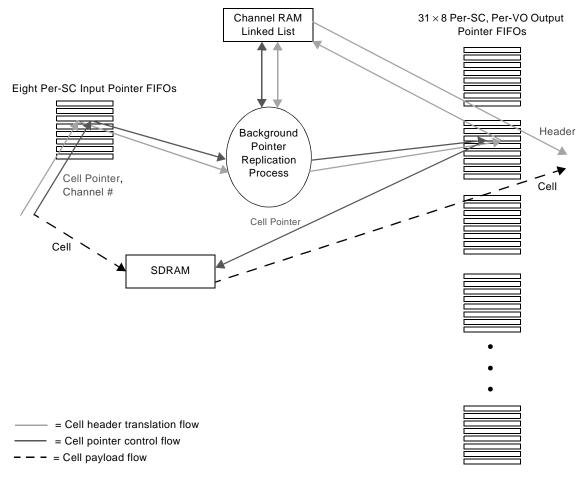

| Figure 46. Multicast Pointer FIFO Operation                       |     |

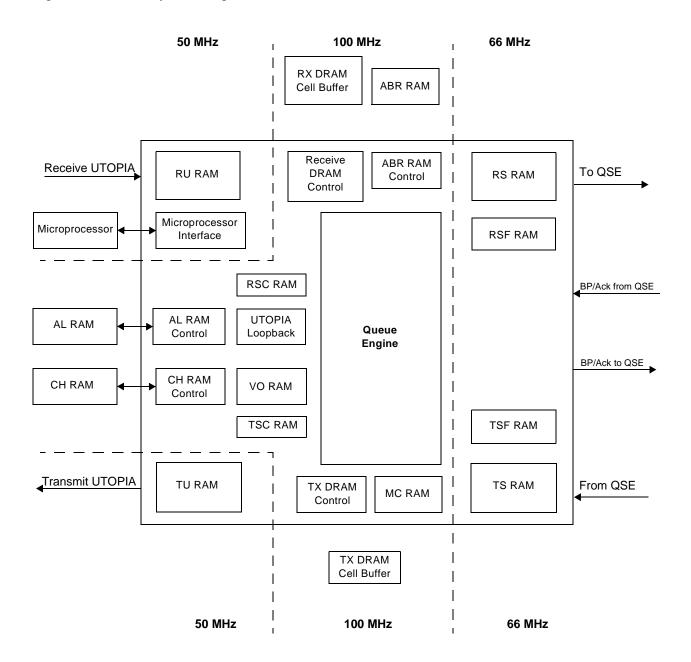

| Figure 47. System Diagram of Internal QRT Blocks and External RAM | 43  |

| Figure 48. Basic Data Path Through the Switch                     | 44  |

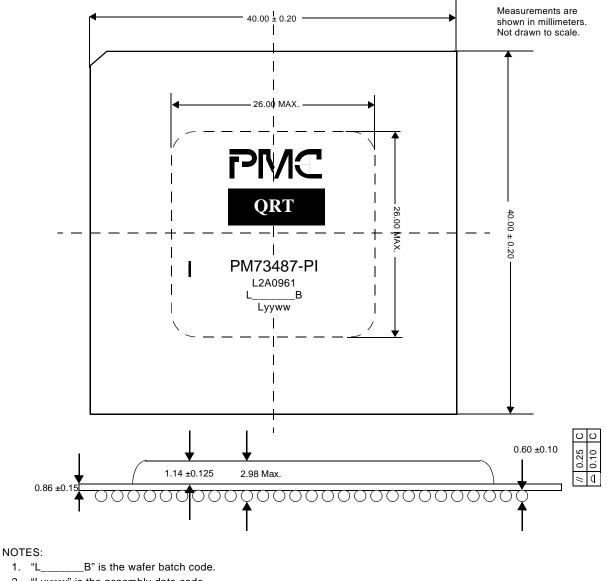

| Figure 49. 503-Pin EPBGA Top and Side Views (Part 1 of 2)         | 55  |

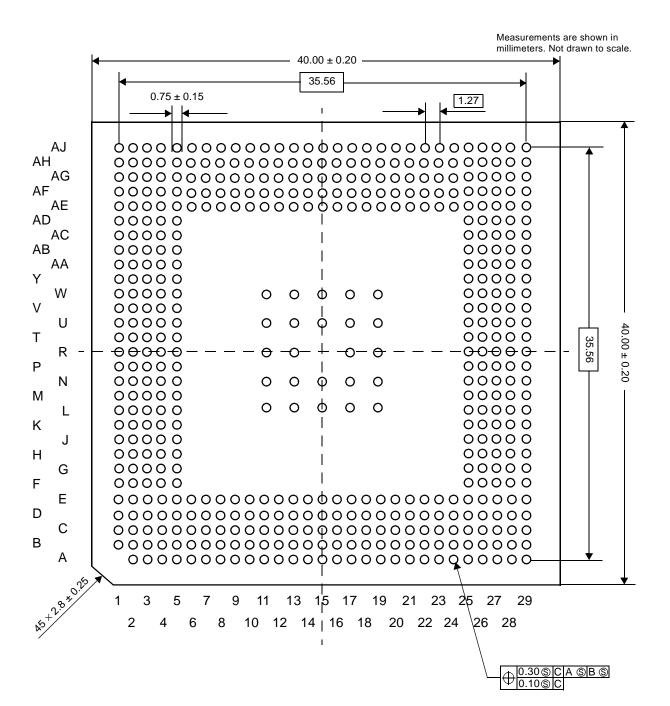

| Figure 49. 503-Pin EPBGA Bottom View (Part 2 of 2)                | 56  |

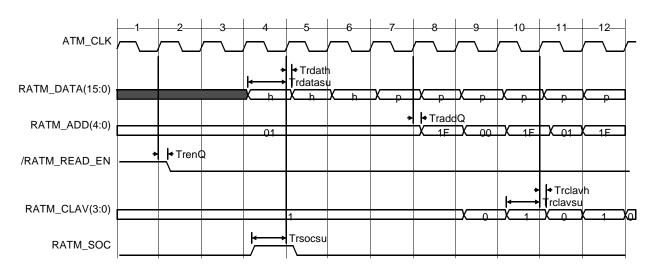

| Figure 50. Receive UTOPIA 50 MHz Timing                           | 77  |

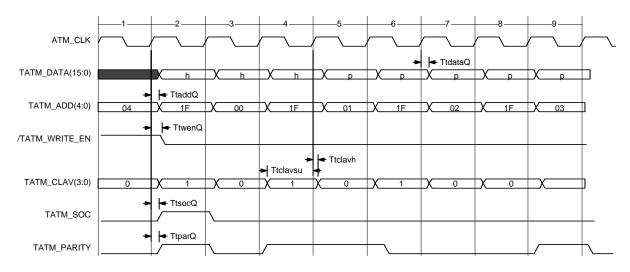

| Figure 51. Transmit UTOPIA 50 MHz Timing                          |     |

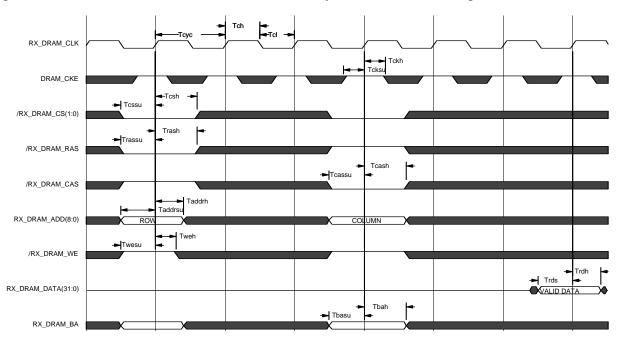

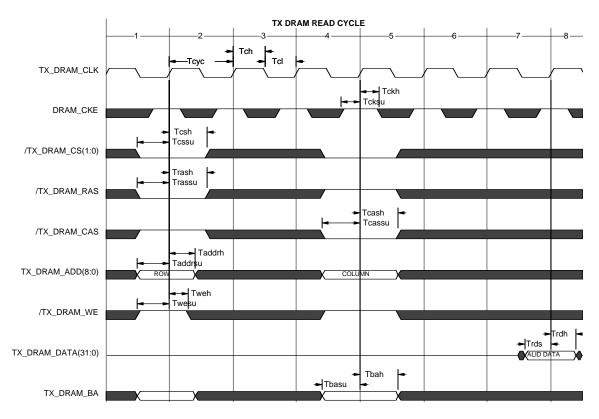

| Figure 52. Receive DRAM External Memory 100 MHz Read Timing       | 79  |

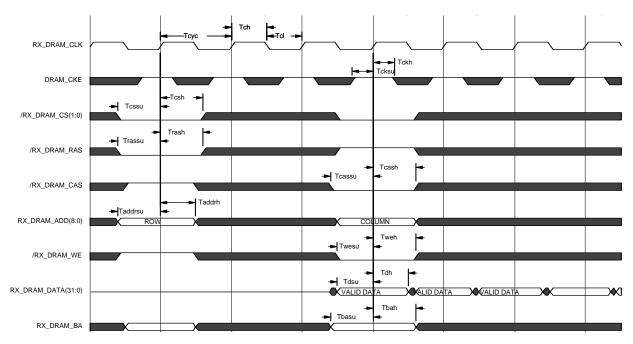

| Figure 53. Receive DRAM External Memory 100 MHz Write Timing      | 80  |

| Figure 54. Transmit DRAM External Memory 100 MHz Read Timing      | 81  |

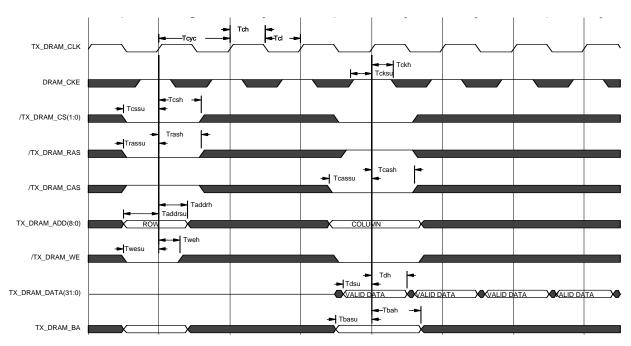

| Figure 55. Transmit DRAM External Memory 100 MHz Write Timing     | 82  |

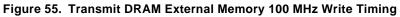

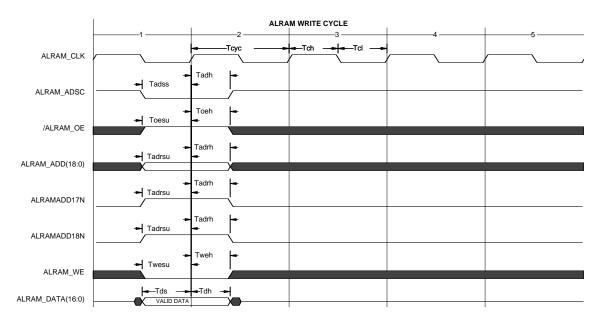

| Figure 56. Address Lookup RAM Read Timing                         | 83  |

| Figure 57. Address Lookup RAM Write Timing.                       | 84  |

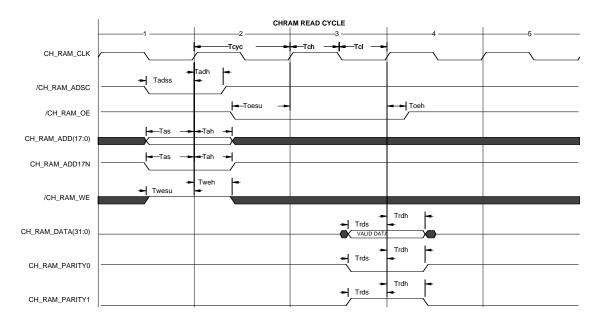

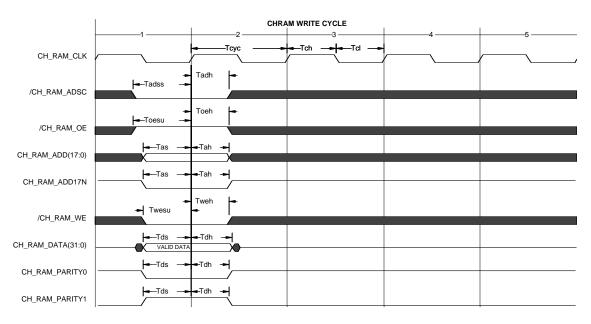

| Figure 58. Channel RAM Read Timing.                               | 85  |

| Figure 59. Channel RAM Write Timing                               | 86  |

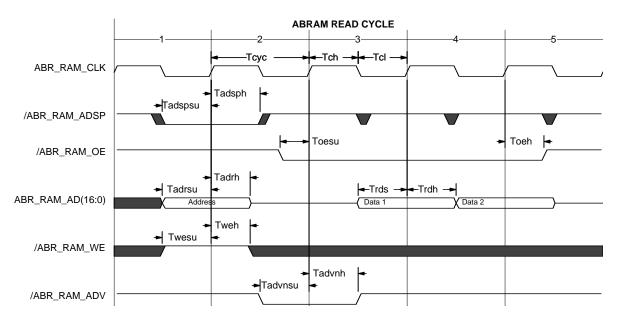

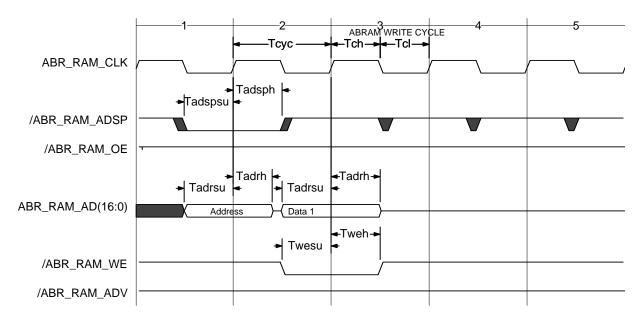

| Figure 60. AB RAM Read Timing.                                    | 87  |

| Figure 61. AB RAM Write Timing                                    | 88  |

| Figure 62. QRT Bit-Level Timing                                   | 90  |

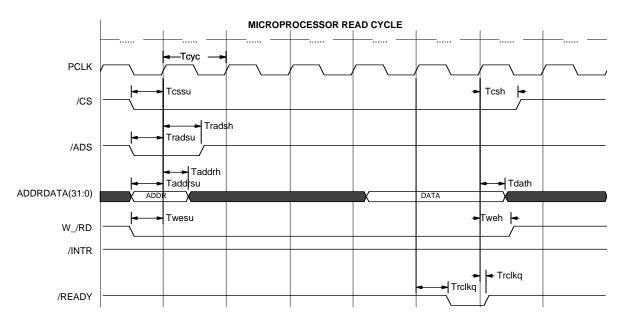

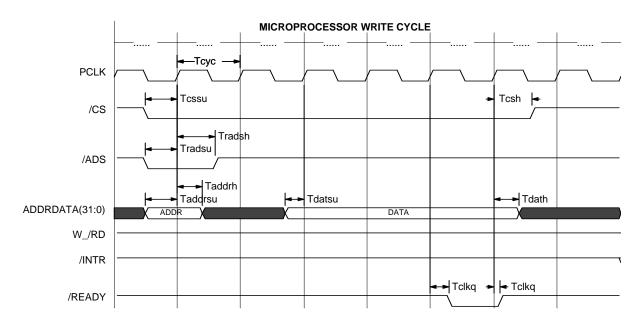

| Figure 63. Microprocessor Read Timing                             |     |

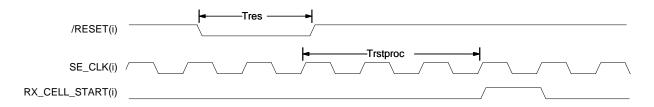

| Figure 65. Reset Timing.                                          |     |

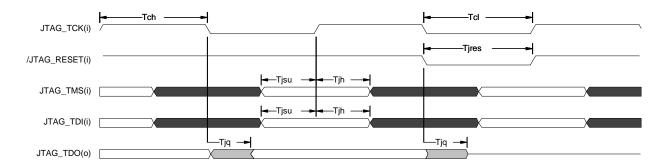

| Figure 66. JTAG Timing                                            |     |

| Figure 67. Transmit Service Class RAM (TSC_RAM) Memory Map        | 151 |

| Figure 68. Receive Service Class RAM (RSC_RAM) Memory Map         |     |

| Figure 69. Virtual Output Control RAM (VO_RAM) Memory Map         |     |

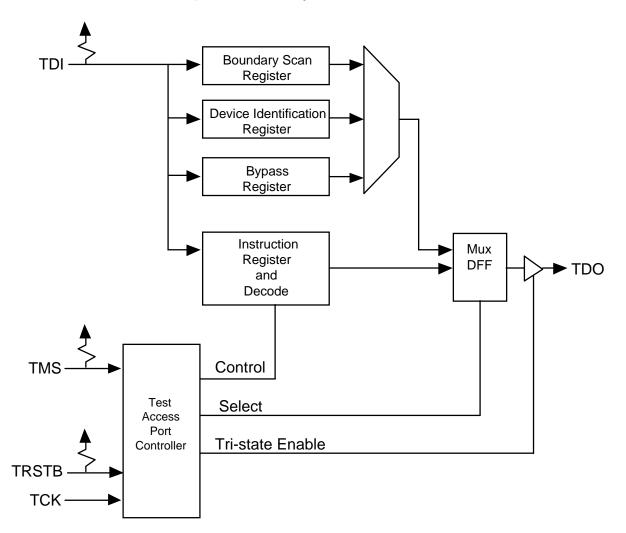

| Figure 70. Boundary Scan Architecture.                            |     |

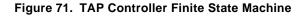

| Figure 71. TAP Controller Finite State Machine                    |     |

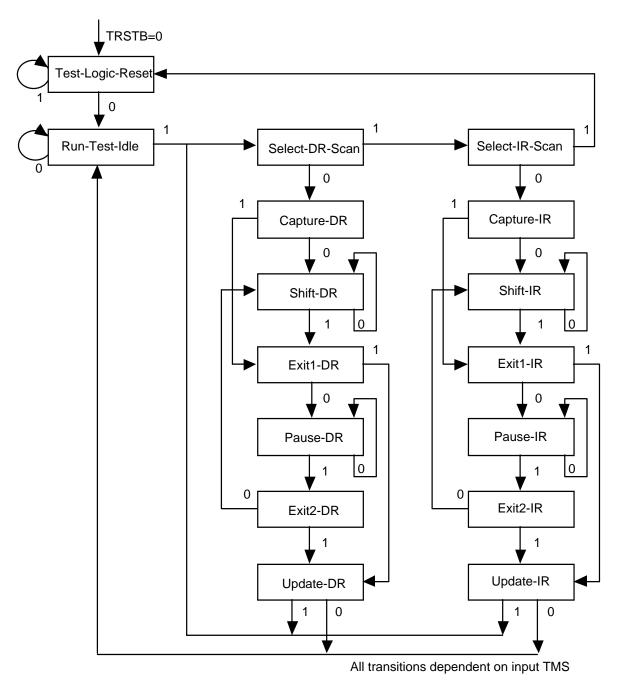

| Figure 72. Connecting the QRT to Gigabit Ethernet Transceivers    |     |

| Figure 73. Connecting the QRT to the RCMP-800                     |     |

|                                                                   |     |

622 Mbps ATM Traffic Management Device

## List of Tables

| Table 1. Backpressure and Acknowledgment Encodings                                      |     |

|-----------------------------------------------------------------------------------------|-----|

| Table 2. Failure Conditions, IRT-to-Switch Fabric Interface                             | 50  |

| Table 3. Failure Conditions, QSE Receive Interface                                      | 51  |

| Table 4. Failure Conditions, QSE Transmit Interface                                     |     |

| Table 5. Failure Conditions, Switch Fabric-to-ORT Interface                             | 52  |

| Table 6. Faults and Effects on the Network                                              | 53  |

| Table 7. Signal Locations                                                               |     |

| Table 8. Processor Interface Signals (38 Pins)                                          | 64  |

| Table 9. Statistics Interface Signal (1 Pin)                                            | 64  |

| Table 10. Switch Element Interface Signals (47 Pins)                                    | 65  |

| Table 11. CH_ RAM Interface Signals (58 Pins)                                           | 66  |

| Table 12. Address Lookup RAM Interface Signals (42 Pins)                                | 67  |

| Table 13. ABR_RAM Interface Signals (22 Pins)                                           | 68  |

| Table 14. Receive Cell Buffer RAM Interface Signals (49 Pins)                           | 69  |

| Table 15. Transmit Cell Buffers RAM Interface Signals (48 Pins)                         | 70  |

| Table 16. Transmit UTOPIA ATM Layer Interface Signals (29 Pins)                         | 72  |

| Table 17. Receive UTOPIA ATM Layer Interface Signals (27 Pins)                          | 72  |

| Table 18. Test Signals (8 Signal Pins)                                                  | 73  |

| Table 19. Miscellaneous Signals (3 Signal Pins)                                         | 74  |

| Table 20. Estimated Package Thermal Characteristics                                     | 76  |

| Table 21. QRT-QSE Interface Cell Format.                                                | 91  |

| Table 22. QRT-QSE Interface Idle Cell Format                                            | 92  |

| Table 23. Microprocessor Ports Summary                                                  | 98  |

| Table 24. Various ways to configure UTOPIA interface.    1                              | 117 |

| Table 25. Internal RAM Summary    1                                                     | 150 |

| Table 26. Transmit Service Class Queue (TX SCQ) Control Block Summary                   | 152 |

| Table 27. Receive Service Class (RX SC) Control Block Summary.    1                     | 156 |

| Table 28. Transmit VO Control Block Summary    1                                        | 160 |

| Table 29. Transmit SC Control Block Summary.    1                                       | 163 |

| Table 30. Transmit Multicast SC Control Block Summary.    Image: Control Block Summary. | 164 |

| Table 31. Receive Switch Fabric Control RAM (RSF_CONTROL) Summary       1               | 167 |

| Table 32. Receive UTOPIA Cell Buffers Summary    1                                      | 170 |

| Table 33. Transmit UTOPIA Cell Buffers Summary    1                                     | 171 |

| Table 34. Address Lookup RAM (AL_RAM) Summary    1                                      | 174 |

| Table 35. Determining the NUM_VPI Value    1                                            | 175 |

| Table 36. VI_VPI_TABLE Entry if VPC_ENTRY = 1       1                                   | 175 |

| Table 37. VI_VPI_TABLE Entry if VPC_ENTRY = 0                                           | 175 |

| Table 38. Service Order Control Block Summary                                           | 181 |

| Table 39. Channel RAM (CH_RAM) Summary                                                  | 183 |

| Table 40. Channel Control Block Summary    1                                            | 183 |

| Table 41. Multicast Control Block Summary    1                                          | 194 |

| Table 42. AB_RAM Summary    1                                                           | 196 |

РМС-980618

| Table 43. Receive Channel Queue Block Summary       | 196 |

|-----------------------------------------------------|-----|

| Table 44. Receive Channel Queue Block Summary       | 197 |

| Table 45. Receive Cell Buffers SDRAM/SGRAM Summary  | 202 |

| Table 46. Transmit Cell Buffers SDRAM/SGRAM Summary | 203 |

| Table 47. Boundary Scan Pin Order                   | 208 |

| Table 48. Prefixes and Associated Functions         | 232 |

| Table 49. QRT RAM Selection                         | 237 |

| Table 50. Ordering Information                      | 238 |

I

PMC-980618

Issue 3

622 Mbps ATM Traffic Management Device

# **Product Overview**

The PM73487 622 Mbps ATM Traffic Management Device (QRT<sup>™</sup>) is an advanced communications device capable of supporting very large, high-performance ATM switching systems. The rich feature set of the QRT enables systems to offer many sophisticated network services. The QRT provides 622 Mbps UTOPIA (Level 1 or Level 2) access to switch fabrics composed of PM73488 5 Gbps ATM Switch Fabric Elements (QSEs). Together, these devices can be used to build architectures with capacities from 622 Mbps to 160 Gbps. The QRT can also act as a standalone 622 Mbps switch.

The QRT/QSE architecture virtually eliminates head-of-line blocking by means of the QRT's per-Virtual Channel (VC) receive queues and congestion feedback from the QSE<sup>TM</sup> switch fabric. The distributed architecture acts as an output-buffered switch by incorporating Evil Twin Switching<sup>TM</sup> (a congestion-reducing routing algorithm in the switch fabric) and a speed-up factor in the switch fabric (running the fabric faster than the line rate).

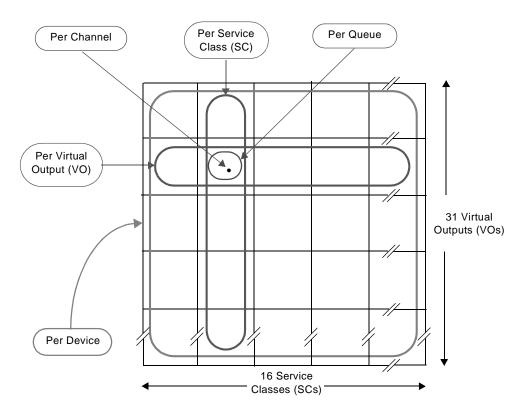

The QRT uses per-VC receive queues, 64 receive Service Classes (SCs), and 16 transmit SCs per each of the 31 Virtual Outputs (VOs) to enable flexible multi-priority scheduling algorithms. The scheduler can be used to ensure Quality-of-Service (QoS) guarantees for Constant Bit Rate (CBR), Variable Bit Rate (VBR), and Unspecified Bit Rate (UBR) VCs. The QRT also provides five separate congestion thresholds, each with hysteresis, that selectively control AAL5 Early Packet Discard (EPD) and/or Cell Loss Priority (CLP)-based cell dropping for UBR support. Additional highlights of the QRT include full Virtual Path Indicator (VPI)/Virtual Channel Indicator (VCI) header translation, separate input and output cell buffers (up to 64K each), Virtual Path (VP)/VC switching, and support for up to 16K VCs on both the receive and transmit sides.

PMC-Sierra also offers the QRT Device Control Package, which is a software package that harnesses the QRT's rich feature set and shortens system development times.

## FEATURES

#### QUEUING ALGORITHMS

Receive

- Maintains 64 weighted, bandwidth-controlled SCs with per-VC queues.

- Provides round-robin servicing of queues within each SC.

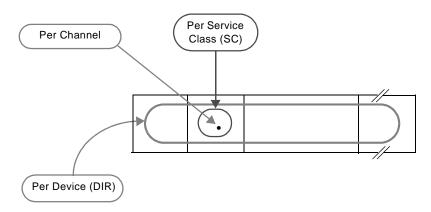

- Provides per-channel (VP or VC), per-SC, and per-direction congested and maximum queue depth limits.

- Provides up to 64K cell buffers.

Transmit

- Provides 31 VOs.

- Maintains 16 SCs for each VO with per-VC accounting.

**PMC**-Sierra, Inc. Issue 3 622

PMC-980618

- Provides per-channel (VP or VC), per-SC Queue (SCQ), per-SC, per-VO, and perdirection congested and maximum queue depth limits.

- Provides up to 64K cell buffers.

### CONGESTION MANAGEMENT ALGORITHMS

- Supports EPD and Partial Packet Discard (PPD) for UBR traffic, and as a backup for ABR traffic.

- Supports CLP-based cell discard and Explicit Forward Congestion Indicator (EFCI) cell marking.

- Supports three congestion limits (as well as EPD, CLP, and EFCI, and/or backpressure) for logical multicast on the transmit side.

### SWITCHING

- Supports VC and VP switching.

- Supports up to 16K VCs.

## ADDRESS MAPPING

- Supports all 12 VP and 16 VC bits through use of a double, indirect lookup table.

- Performs header translation at both the input (receive) and output (transmit) directions. Input header translation is used to pass the output queue channel number through the switch.

## MULTICAST

• Supports logical multicast with a superior queue-clearing algorithm.

## DIAGNOSTIC/ROBUSTNESS FEATURES

- Checks the header parity.

- Counts tagged cells.

- Runs error checks continually on all fabric lines.

- Checks liveness of control signal lines at both switch fabric and UTOPIA interfaces, working around partial fabric failures.

- Checks Static Random Access Memory (SRAM) and Dynamic Random Access Memory (DRAM) parity.

## STATISTICS FEATURES

- In the receive direction, counts cells transmitted and dropped.

- In the transmit direction, counts cells transmitted and dropped on a per-VC basis.

## I/O FEATURES

- Provides four switch element interfaces with phase aligners. The phase aligners allow for external serialization of the data stream enabling systems to be built that support device separation of up to 10 meters.

- Provides a UTOPIA Level 2 Multi-PHY (MPHY) 16-bit, 50 MHz interface.

- Provides a 2-level priority servicing algorithm for high and low bandwidth UTOPIA PHY layer devices.

- Provides a multiplexed address/data CPU interface.

- Provides two 100 MHz, 32-bit, synchronous DRAM cell buffer interfaces.

- Provides three 100 MHz, synchronous SRAM control interfaces.

Issue 3

• Provides a JTAG boundary scan interface.

#### COMPATIBILITY FEATURES

- Compatible with the ATM Forum 3.0, 3.1, and 4.0 specifications.

- Compatible with the ATM Forum UTOPIA Level 1 and Level 2 specifications.

- Compatible with the PM73488 ATM QSE.

#### PHYSICAL CHARACTERISTICS

- 3.3 V supply voltage.

- 5 V tolerant inputs on the microprocessor and UTOPIA interfaces.

- Available in a 503-pin Enhanced Plastic Ball Grid Array (EPBGA) package.

## **BLOCK DIAGRAM**

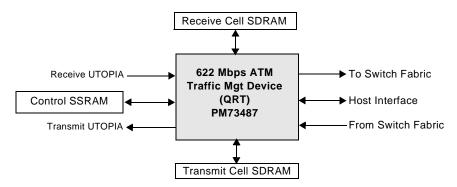

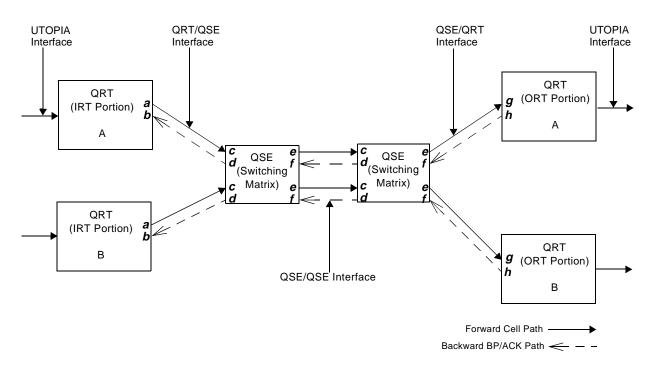

Figure 1 shows a QRT system block diagram.

Figure 1. QRT System Block Diagram

I

PMC-980618

622 Mbps ATM Traffic Management Device

## **1 SYSTEM APPLICATIONS**

The QRT, together with the QSE, support a wide range of high-performance ATM switching systems. These systems range in size from 622 Mbps to 160 Gbps. The systems can be developed such that this scalability is provided with linear cost. Another key feature of the QRT/QSE architecture is that it is exceptionally fault-tolerant, both in the switch fabric and the UTOPIA interface.

This section contains a quick overview of the QRT and several example applications:

- a stand-alone 622 Mbps switch using a single QRT,

- a 5 Gbps switch using QRTs and a QSE,

- a 10 Gbps switch using QRTs and QSEs,

- a switch architecture using QRTs and QSEs that scales from 5 Gbps to 20 Gbps,

- a switch architecture using QRTs and QSEs that scales from 5Gbps to 160 Gbps

#### 1.1 QRT System Overview

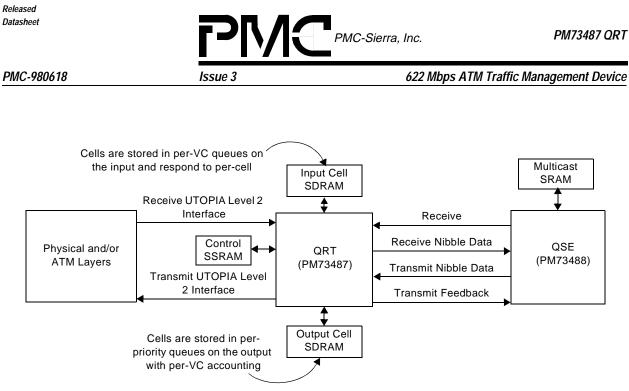

The QRT provides 622 Mbps of input and output buffered access to switch fabrics composed of QSEs (32 x 32 PM73488s). In addition, the QRT supports a stand-alone, purely output-buffered 622 Mbps switch mode. Head-of-line blocking, commonly associated with input buffers, is virtually eliminated via per-VC receive queues, three types of per-cell switch fabric feedback, and per-VC cell selection algorithms. The QRT also provides eight separate congestion thresholds, each with hysteresis, that selectively control AAL5 Early Packet Discard (EPD)/Packet Tail Discard (PTD), CLP-based cell dropping, and/or EFCI marking. Eight separate maximum thresholds are also supported. Additional highlights of the QRT include full VPI/VCI header translation, separate input and output cell buffers (up to 64K each), Virtual Path Connection (VPC)/Virtual Channel Connection (VCC) connections, and up to 16K VCs. The QRT provides a bidirectional connection between a UTOPIA Level 2 interface and 4-nibble wide, 66 MHz switch fabric interfaces, as shown in Figure 2 on page 5. A significant switch speed-up factor, up to 1.6 times the line rate, is used to support full throughput for many switch fabric configurations.

Figure 2. QRT System Overview

#### 1.2 622 Mbps Switch Configuration

The QRT can be used in a stand-alone application that supports ATM switching up to 622 Mbps, as shown in Figure 3. The four switch fabric interfaces are looped back to the QRT, allowing the UTOPIA interface to be fully used. In this application, the QRT operates as an output buffered switch.

Figure 3. 622 Mbps Switch Configuration

| Released<br>Datasheet | PM      | PMC-Sierra, Inc. | PM73487 QRT                 |

|-----------------------|---------|------------------|-----------------------------|

| PMC-980618            | Issue 3 | 622 Mbps ATN     | 1 Traffic Management Device |

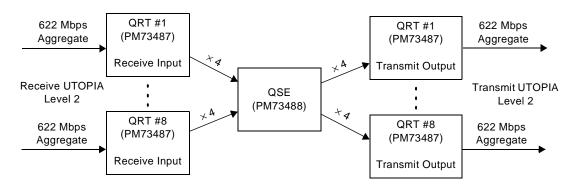

#### 1.3 32 x 32 Switch Application (5 Gbps)

Figure 4 shows a basic  $32 \times 32$  switch application (5 Gbps) using eight QRTs and one QSE.

Figure 4. 32 x 32 Switch Application (5 Gbps)

#### 1.4 64 x 64 Switch Application (10 Gbps)

Figure 5 shows a  $64 \times 64$  switch application (10 Gbps) using 16 QRTs and 6 QSEs. This application uses QSEs in a 3-stage fabric. This sized system can be implemented in a single 19-inch rack.

Figure 5. 64 x 64 Switch Application (10 Gbps)

#### 1.5 5 Gbps to 20 Gbps Application Example - Seamless Growth

This section illustrates the modularity of the QRT (PM73487) and QSE (PM73488) architecture. A 5 Gbps system can immediately be created (as shown in Figure 6 on page 7), and then be upgraded to 10 Gbps (as shown in Figure 7 on page 7), or 20 Gbps (as shown in Figure 8 on page 8). Since all these systems are based on a single-stage switch fabric, the per-port cost for each system will remain the same.

Figure 6. 5 Gbps ATM Switch Using 16 Dual S/UNIs, 8 QRTs, and 1 QSE

Figure 7. 10 Gbps ATM Switch Using 32 Dual S/UNIs, 16 QRTs, and 2 QSEs

Switch Card

• One QSE (PM73488)

Port Card 16

• Two QRTs (PM73487s)

Eight

Interfaces

155 Mbps 🔺

#### 1.6 5 Gbps to 160 Gbps Application Example – LAN-to-WAN

A powerful application of the QRT and the QSE devices is the creation of modules that can be used in a range of switches with only the interconnection changing between different sizes. ATM switches from 5 Gbps to 160 Gbps can be realized with only two unique cards. A port card has one QRT, and a switch card has two QSEs. The switch fabric consists of three stages, each with 32 QSEs (or 16 switch cards). To plan for future scalability, the middle stage must be built-in upfront. This is a one-time cost. Then, in order to scale in 5 Gbps increments, one switch card and its accompanying eight port cards should be added. Finer bandwidth scaling is possible by populating the additional switch card with port cards as needed (in increments of 622 Mbps). With this switch fabric topology, scaling is possible up to 160 Gbps. Once the initial middle stage cost has been incurred, the per-port cost for 5 Gbps through 160 Gbps systems remains almost constant

Figure 9. 5 Gbps to 160 Gbps Switches Modeled Using Only Two Cards

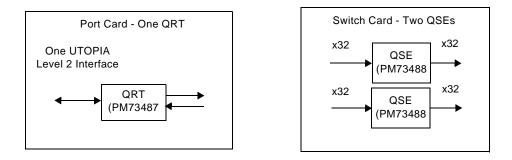

Figure 10. 5 Gbps ATM Switch

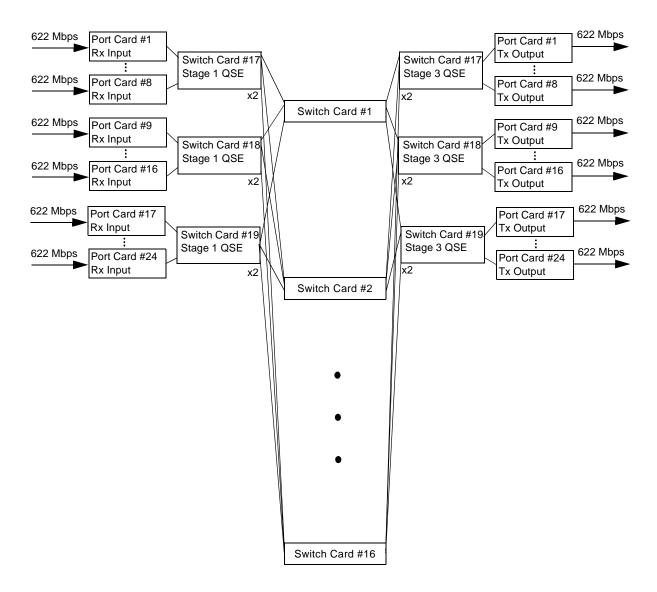

Figure 10 shows a 5 Gbps ATM switch using 8 port cards (8 QRTs) and 17 switch cards (34 QSEs). The middle stage is composed of 16 switch cards. The 5 Gbps bandwith is achieved by adding switch card #17 (which is depicted using two boxes: one stage 1 QSE and one stage 3 QSE), and eight port cards (each of which is depicted using two boxes: one for the Rx input side, and one for the Tx output side). Lines between stage 1 and stage 2, and stage 2 and stage 3 switch cards represent two sets of wires, one to each of the QSEs in the middle stage switch cards.

| Released<br>Datasheet | PM      | PMC-Sierra, Inc.                       | PM73487 QRT |

|-----------------------|---------|----------------------------------------|-------------|

| PMC-980618            | Issue 3 | 622 Mbps ATM Traffic Management Device |             |

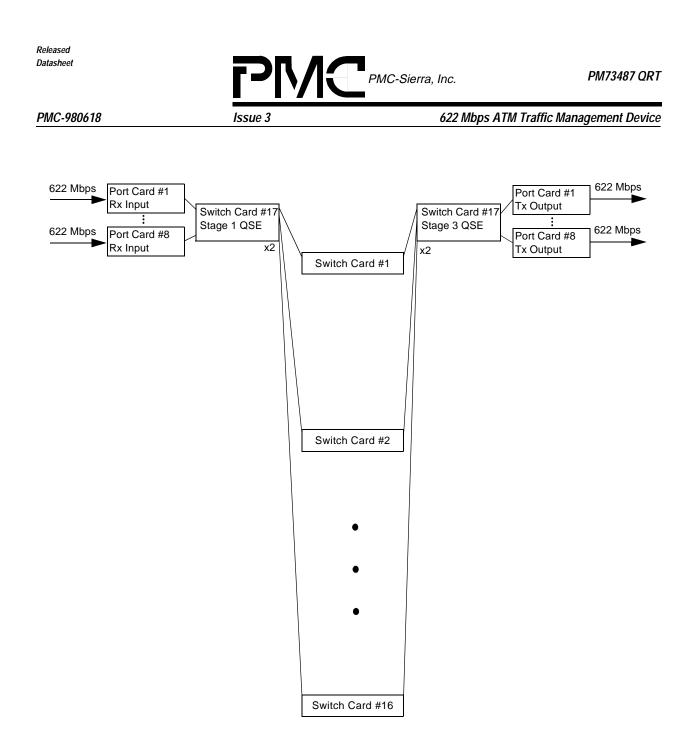

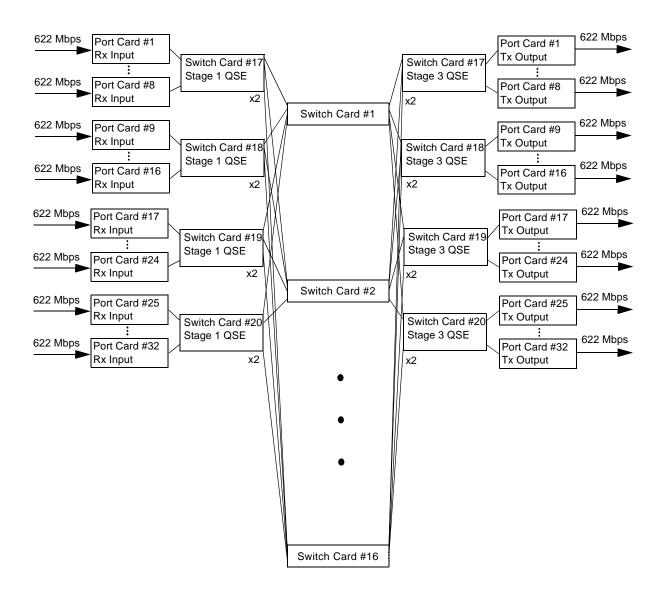

.Figure 11 shows a 10 Gbps ATM switch using 16 port cards (16 QRTs) and 18 switch cards (36 QSEs). Here, another switch card and eight port cards have been added to the 5 Gbps switch depicted in Figure 10.

Figure 11. 10 Gbps ATM Switch

| Released<br>Datasheet | PM      | PMC-Sierra, Inc.                       | PM73487 QRT |

|-----------------------|---------|----------------------------------------|-------------|

| PMC-980618            | Issue 3 | 622 Mbps ATM Traffic Management Device |             |

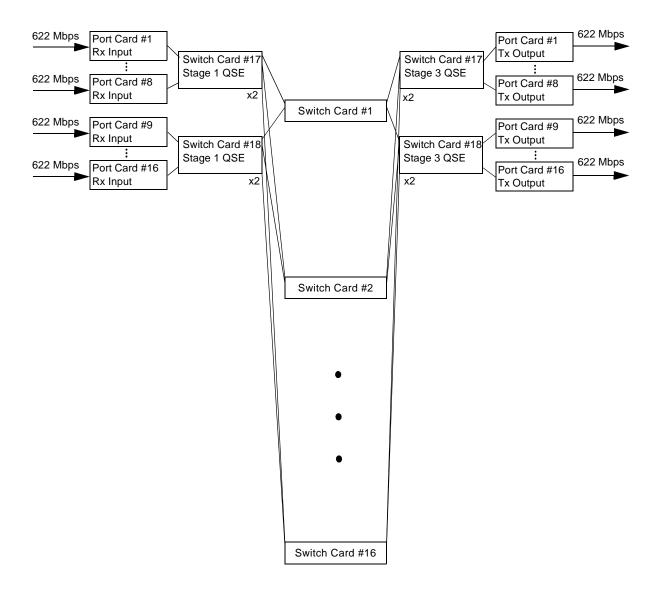

Figure 12 shows a 15 Gbps ATM switch using 24 port cards (24 QRTs) and 19 switch cards (38 QSEs).Here, once again, another switch card and eight port cards have been added

Figure 12. 15 Gbps ATM Switch

| Released<br>Datasheet | PM      | PMC-Sierra, Inc.                       | PM73487 QRT |  |

|-----------------------|---------|----------------------------------------|-------------|--|

| PMC-980618            | Issue 3 | 622 Mbps ATM Traffic Management Device |             |  |

Figure 13 shows a 20 Gbps ATM switch composed of 32 port cards (32 QRTs) and 20 switch cards (40 QSEs). By adding additional sets of a switch card and eight port cards in the same manner, this system can scale up to 160 Gbps.

Figure 13. 20 Gbps ATM Switch

622 Mbps ATM Traffic Management Device

## 2 THEORY OF OPERATIONS

#### 2.1 Overview

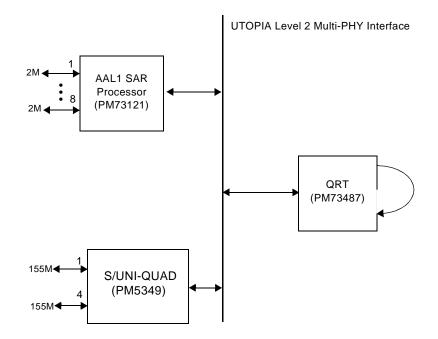

The QRT is a 622 Mbps, full duplex, intelligent routing table which, when used with a switch fabric composed of either SE or QSE devices, can implement ATM switches from 622 Mbps to 160 Gbps. The QRT supports a 16-bit UTOPIA Level 2 interface for ease of connection to PHY or AAL layer devices. Four nibble-wide data interfaces connect the QRT to the switch interface. External DRAM memory devices provide receive and transmit cell buffering, and external SRAM devices provide control data for the QRT. This section explains the algorithms for the data flow.

Figure 14 shows an overview of the QRT system.

Figure 14. QRT System Overview

#### 2.2 Interface Descriptions

#### 2.2.1 Switch Fabric Interface

The QRT switch fabric interface consists of four groups of signals from both the ingress (receive side) and the egress (transmit side). Each group consists of a Start-Of-Cell (SE\_SOC\_OUT) signal, a nibble-wide data bus, and a backpressure acknowledgment (BP\_ACK\_IN) signal. The Start-Of-Cell (SE\_SOC\_OUT) signal is transmitted at the ingress at the same time as the beginning of a cell. SE\_SOC\_OUT on the ingress is common to all four groups. The BP\_ACK\_OUT signal flows from the egress through the switch fabric, in the direction opposite the data, and indicates whether a cell has successfully passed through the switch fabric. Other signals associated with the switch fabric interface are the switch element clock (SE\_CLK) and RX\_CELL\_START. To support the highest possible throughput for various switch fabric configurations, a clock speed-up factor of 1.6 is used. That is, the switch fabric is run at a rate that is effectively 1.6 times faster than the line rate.

I

PM73487 QRT

PMC-980618

622 Mbps ATM Traffic Management Device

#### 2.2.2 Phase Aligners

Phase aligners are used to allow for extended device separation. The technique used is a clock recovery mechanism that requires only the switch fabric to be frequency synchronous. A master clock is distributed to all devices associated with the switch fabric, and the phase of the clock at each interface is dynamically adjusted to account for skew introduced to the signals. The phase aligner circuitry for each interface responds to the cell start and feedback signals, which contain a high number of transitions to ensure accurate phase adjustment of the clock for data and signal sampling.

## 2.2.3 UTOPIA Interface

The QRT's UTOPIA interface implements the ATM Forum standardized 16-bit, Level 2 configuration, which supports up to 31 Virtual Outputs (VOs) via five address bits. Up to 31 PHY or AAL layer devices with 16-bit UTOPIA Level 2 functionality can be connected to this interface, providing full duplex throughputs of 675 Mbps.

### 2.2.4 Cell Buffer SDRAM Interface

The QRT supports two Synchronous DRAM (SDRAM or SGRAM) interfaces providing up to 64K of cell buffering in both the receive and transmit directions. Each interface consists of a 32bit data bus, a 9-bit address bus, two chip select signals, and associated control signals. The frequency of these interfaces is 100 MHz. Both Synchronous Graphic RAM (SGRAM) and SDRAM devices are supported. Clocking for these two interfaces is provided through the device.

### 2.2.5 Channel RAM (CH\_RAM) Interface

The QRT supports up to 16K channels through a Synchronous SRAM (SSRAM) interface. The interface consists of a 32-bit data bus, a 16-bit address bus, and associated control signals. The frequency of this interface is 100 MHz. Clocking for this interface is provided through the device.

### 2.2.6 Address Lookup RAM (AL\_RAM) Interface

The QRT has data structures in the AL\_RAM, including VPI/VCI address translation. The interface consists of a 6-bit data bus, a 17-bit address bus, and associated control signals. The frequency of this interface is 100 MHz. Clocking for this interface is provided through the device.

## 2.2.7 AB\_RAM Interface

The QRT stores the per VC head / tail pointers and sent / dropped counters for the receive direction in the AB\_RAM. Each interface consists of a 17-bit multiplexed address/data bus and associated control signals. The frequency of this interface is 100 MHz.

## 2.2.8 Host Processor Interface

The QRT host processor interface allows connection of a microprocessor through a multiplexed 32-bit address/data bus. The suggested microprocessor for this interface is the Intel i960<sup>®</sup>. The microprocessor has direct access to all of the QRT control registers.

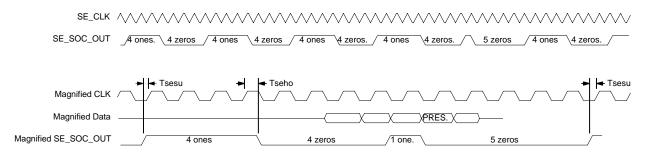

#### 2.2.9 SE\_SOC Encodings

The SE\_SOC and BP\_ACK signals have guaranteed transitions and special encodings, which are defined in this section and in "BP\_ACK Encodings" which follows. The SE\_SOC\_IN and SE\_SOC\_OUT signals have guaranteed transitions and SOC encodings as shown in Figure 15. The SE\_SOC signals carry a repeating pattern of four zeros and four ones to guarantee transitions required by the phase aligner. The "Start-Of-Cell" on the data lines associated with an SE\_SOC line is indicated by a change in this pattern. For a valid SE\_SOC, the change in pattern is followed by reset of the background pattern such that it is followed by four zeros and four ones. The first nibble (PRES) of the header is coincident with SE\_SOC (change in pattern).

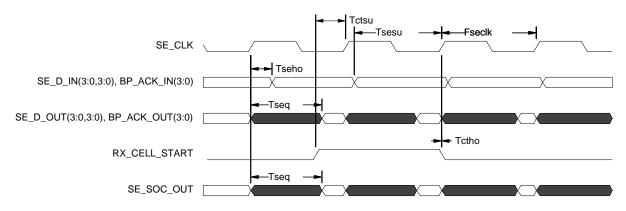

Figure 15. SE\_SOC Encodings

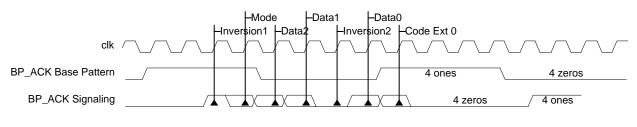

#### 2.2.10 BP\_ACK Encodings

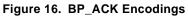

Figure 16 shows the BP\_ACK encodings.

The BP\_ACK\_IN and BP\_ACK\_OUT signals have guaranteed transitions, and BP and ACK encodings. The BP\_ACK signal is used to signal backpressure/cell acknowledgment to the fabric (QSE) at the egress and receive backpressure/cell acknowledgment at the ingress from the fabric (QSE).

To ensure the transitions required by the phase aligner, the BP\_ACK signal carries a repeating four zeros, four ones pattern. The actual information is transferred through encoded 7-bit packets that start with a change in this background pattern. The change (an inversion) on the line is followed by a mode bit, followed by two bits of coded message, and a second inversion (inverse of the first inversion). If it is an acknowledgment packet, this is followed by two bits of code exten-

PMC-Sierra, Inc. Issue 3

PM73487 QRT

PMC-980618

622 Mbps ATM Traffic Management Device

sion (these bits are for future use and currently are required to be "00"). In the case of a backpressure packet, the next bit is the backpressure bit on for low priority multicast cells, followed by one code extension bit.

The background is reset to four zeros and four ones after transmission of each packet.

The QRT and QSE allow back-to-back acknowledgment and backpressure packets. In the case of back-to-back acknowledgment and backpressure packets, the receiving device may see an inverted bit (a "1") followed by the rest of the packet instead of a reset background pattern.

One backpressure packet and either one or none acknowledgment packet are expected to be received during a cell time. The receipt of multiple acknowledgment or backpressure packets is a failure condition.

Table 1 describes the backpressure and acknowledgment encodings.

| Mode | Data 2                                                  | Data 1                                                      | Data 0                                                 | Code<br>Ext 0 | Description                                                                                                                                                                                                                 |

|------|---------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 1 = Backpressure<br>on high priority<br>multicast cell. | 1 = Backpressure<br>on medium prior-<br>ity multicast cell. | 1 = Backpressure<br>on low priority<br>multicast cell. | 0             | Backpressure information.<br>This signal is present each cell time,<br>regardless of whether a cell was transmit-<br>ted or not (on that link).<br>This signal is withheld if any problem is<br>detected on the input port. |

| 1    | 0                                                       | 0                                                           | 0                                                      | 0             | Signals no response. Treated as acknowl-<br>edgment.                                                                                                                                                                        |

| 1    | 0                                                       | 1                                                           | 0                                                      | 0             | Signals Mid-switch Negative ACKnowl-<br>edgment (MNACK).                                                                                                                                                                    |

| 1    | 1                                                       | 0                                                           | 0                                                      | 0             | Signals Output Negative ACKnowledg-<br>ment (ONACK).                                                                                                                                                                        |

| 1    | 1                                                       | 1                                                           | 0                                                      | 0             | Signals ACKnowledgment (ACK).                                                                                                                                                                                               |

Table 1. Backpressure and Acknowledgment Encodings

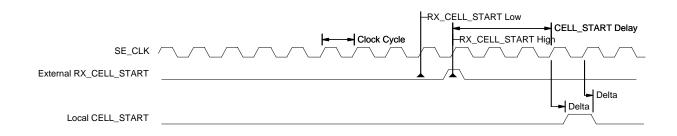

## 2.2.11 Relation Between External CELL\_START and Local CELL\_START

Figure 17 shows the relationship between external RX\_CELL\_START and local CELL\_START signals.

I

PM73487 QRT

PMC-980618

622 Mbps ATM Traffic Management Device

Delay between the external RX\_CELL\_START and local CELL\_START is programmable through the RX\_CELL\_START\_ALIGN register (refer to "RX\_CELL\_START\_ALIGN (Internal Structure)" on page 122).

The local CELL\_START impacts the start of cell transmission to the fabric. It also determines the period within a cell time during which the BP\_ACK\_IN(3:0) at ingress is valid. As such, the programmable CELL\_START delay allows the flexibility to synchronize the QRTs and QSEs in a system.

#### 2.3 Cell Flow Overview

The QRT functions as a 622 Mbps port for an ATM switch fabric composed of either the SE or QSE devices. The QRT transfers cells between a UTOPIA Level 2 interface and a switch fabric interface. The device supports header translation and congestion management. The basic flow of cells through the QRT is as follows (see Figure 18 on page 19):

- 1. A cell enters the QRT on the receive side from the UTOPIA interface and the channel number is looked up.

- 2. The cell is then either dropped or transferred to the receive cell buffer DRAM and queued in the receive queue controller depending on six congestion management checks (both maximum and congested thresholds for the device, Service Class Group (SCG), SC, and connection).

- 3. When an available cell time occurs, four cells are selected by the receive-side scheduler, which reads the cells from the receive cell buffer DRAM and transmits them from the QRT into the switch fabric.

- 4. Once a cell is received from the switch fabric on the transmit side, it is again either dropped or transferred to the transmit cell buffer DRAM and queued in the transmit queue controller, depending on ten congestion management checks (both maximum and congested thresholds for the device, VO, SC, Service Class Group (SCG), Service Class Queue (SCQ), and connection).

- 5. When the cell is selected for transmission by the transmit-side scheduler, it is removed from the transmit cell buffer DRAM and processed by the transmit multicast/header mapper for corresponding header translation and distribution.

Released Datasheet

622 Mbps ATM Traffic Management Device

6. The cell then is sent to the UTOPIA interface and exits the QRT on the transmit side.

Figure 18. QRT Data Flow Diagram

#### 2.4 UTOPIA Operation

#### 2.4.1 General

Cells received from the UTOPIA interface are first processed by the receive channel lookup block and then queued for transmission within the receive queue controller. The cell waits in the receive cell buffer DRAM for instruction from the receive queue controller to proceed to the switch fabric interface.

#### 2.4.2 UTOPIA Interface

The QRT interfaces directly to a UTOPIA interface device without needing an external FIFO. The receive side UTOPIA has a 4-cell internal FIFO, and the transmit side contains another 4-cell internal FIFO. The QRT UTOPIA interface is 16 bits wide and operates at frequencies up to 50 MHz. It provides the following modes:

- UTOPIA Level 1 single-PHY interface

- UTOPIA Level 2 multi-PHY interface

2.4.2.1 UTOPIA Level 2 Polling

Released Datasheet

The UTOPIA interface offers three modes of polling, as per the UTOPIA Level 2 specification:

- Standard single cell available polling •

- Multiplexed Status Polling (MSP) using four cell available signals •

- Direct status indication using four cell available signals •

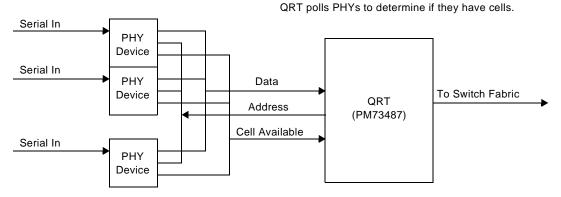

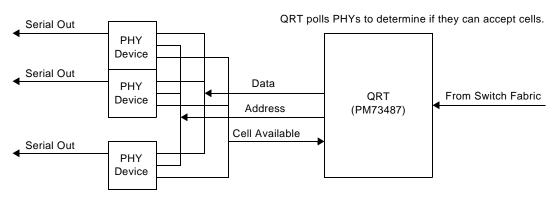

These polling modes allow the QRT to communicate with many different PHY devices. Figure 19 shows the QRT polling PHY devices in a receive UTOPIA operation.

Figure 19. Receive UTOPIA Operation

Figure 20 shows the QRT polling PHY devices in a transmit UTOPIA operation.

Figure 20. Transmit UTOPIA Operation

| Released<br>Datasheet | PM      | PMC-Sierra, Inc. | PM73487 QRT               |

|-----------------------|---------|------------------|---------------------------|

| РМС-980618            | Issue 3 | 622 Mbps ATM     | Traffic Management Device |

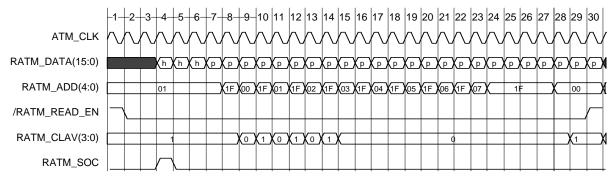

#### 2.4.2.1.1 Standard Single Cell Available Polling

In the standard single cell available polling mode, one cell available response occurs every two clocks. Figure 21 shows the receive standard single cell available polling.

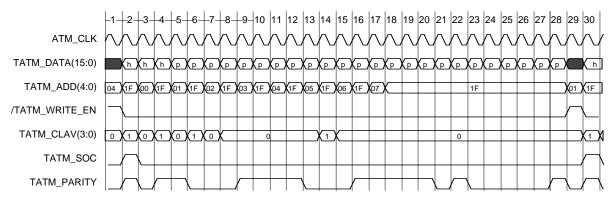

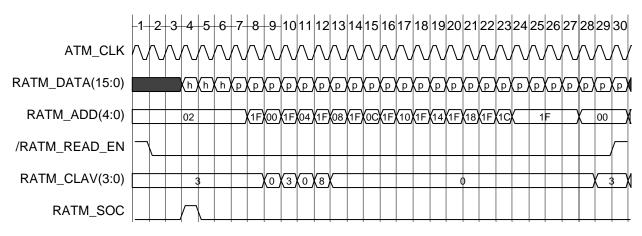

Figure 22. Transmit Standard Single Cell Available Polling

| Released<br>Datasheet | PM      | PMC-Sierra, Inc.                       | PM73487 QRT |

|-----------------------|---------|----------------------------------------|-------------|

| РМС-980618            | Issue 3 | 622 Mbps ATM Traffic Management Device |             |

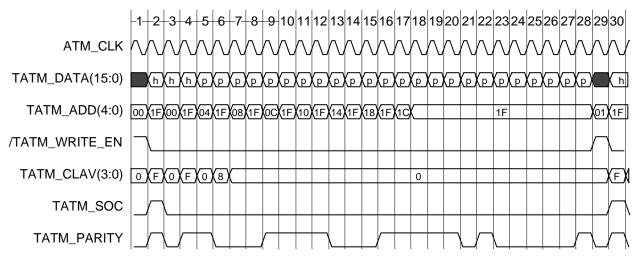

## 2.4.2.1.2 Multiplexed Status Polling (MSP) Using Four Cell Available Signals

With MSP using four cell available signals, up to four cell available responses occur every two clocks. The advantage offered by the MSP mode is the improved response time for PHY service selection. With this method, it is possible to poll 31 devices in a single cell time. PHY devices, however, must comply with this optional part of the UTOPIA Level 2 specification. A standard PHY device can be configured to use this mode even though it does not support it directly. To effect this, up to eight PHY devices can be configured with the addresses 0, 4, 8, 12, 16, 20, 24, and 28. Figure 23 shows the receive UTOPIA 50 MHz MSP, including cell transfer.

Figure 23. Receive UTOPIA Multiplexed Status Polling (MSP), Including Cell Transfer

Figure 24 shows the transmit UTOPIA 50 MHz MSP including cell transfer.

Figure 24. Transmit UTOPIA 50 MHz Multiplexed Status Polling (MSP), Including Cell Transfer

#### 2.4.2.1.3 Direct Status Indication Using Four Cell Available Signals

When configuring the device, setting the MSP mode bit implicitly turns on direct status indication, since it is a subset of the implemented MSP method.

#### 2.4.2.2 Priority Encoding and TDM Table

The Transmit UTOPIA selects PHY devices for service based upon:

- the assigned UT PRIORITY for the PHY(refer to "UT\_PRIORITY" on page 119).

- the configuration of the TDM (Time Division Multiplex) table

- per VO presence of the cells in the QEngine

- cell available assertions received from the PHYs.

The use of priority servicing is beneficial when using multi-phy configurations and the UTOPIA bandwidth is nearly fully subscribed.

#### 2.4.2.2.1 Basic 2 Level Priority Algorithm

When TDM is disabled (refer to section 7.2.10 UTOPIA\_CONFIG) a PHY device is assigned either a high or low UTOPIA priority based of the bandwidth of the PHY device. Within a priority level (high or low), further control over the service algorithm can be implemented by assigning the lowest numbered PHY addresses to the highest bandwidth PHYs. The general algorithm for deciding which PHY to service is as follows:

- 1. The High priority encoder has highest service priority. From the high priority PHYs, the lowest address PHY that has indicated it can accept a cell (and for which a cell is present in the QEngine) is selected. If no high priority PHY is selected, then the low priority set is considered next.

- 2. The Low priority encoder has the next highest service priority. The lowest address PHY that has indicated it can accept a cell (and for which a cell is present in the QEngine) is selected. If no low priority PHY is selected then the cell time is wasted unless the Watchdog is configured for operation, in which case the stale priority set is considered next. The Watchdog is only available on the Transmit side.

- 3. The Transmit Stale priority encoder has the lowest priority and is created for the PHY devices that the Watchdog deems stale. The lowest address PHY that has been detected dead or "stale" by the WatchDog (and for which a cell is present in the Qengine) is selected. The cell is played out on the interface in order to relieve VO queue depth congestion. The Watchdog plays the role of making a best effort delivery, even though the PHY is considered dead.

Caveat: Service selection is performed each cell time with the CLAV information gathered from the previous cell time. This is particularly important, when the standard polling method is used and not all phy's can be polled in a single cell time. In this mode, UTOPIA Priorities have relative meaning within 4 address groups of 8 (0to7, 8to15, 16to24 and 25to31). For example a high priority phy of address=1 will compete for service with a low priority phy of address=7, but will not compete for service against a low priority phy of address=10 since they are in different groups. It is conceivable that a low priority phy can receive as much service as a high priority phy. This could be the case if the phy at address=10 is the only phy in its address group. It will get the entire cell time bandwidth simply because there are no other phys to compete with.

This problem does not exist in MSP mode since all CLAV information is gathered in one cell time.

#### 2.4.2.2.2 TDM and the Basic 2 Level Priority Algorithm

When TDM is enabled, (refer to section 7.2.10 UTOPIA\_CONFIG and to section 7.2.12 UT\_ENABLE for configuring the TDM Pool) another level is added on top of the Basic 2 Level Priority Algorithm. The TDM table has primary service priority if the UTOPIA interface is configured to use the TDM feature. Each cell time, the TDM pointer is advanced through the TDM Pool in a round-robin fashion. When a PHY is pointed to and a cell is present in the QEngine for the PHY, it will be selected. If a PHY is selected and a cell is NOT present in the QEngine for the PHY, the selection process is deferred to the Basic 2 Level Priority Algorithm so that the cell time is not wasted. The TDM table is most useful when configurations require uniformally distributed bandwidths, such as 4xOC3 configurations. In the event that the TDM bit is not set in the UTOPIA\_CONFIG then the servicing algorithm reduces to the Basic 2 level Priority encoding scheme consisting of 1, 2 and 3 above.

The Receive side of the QRT operates in the same fashion as the Transmit side with the exception of the Stale Priority level since there is no Watchdog present in the Receive side.

The UTOPIA Level 2 specification is not designed to support oversubscription due to its lack of multi-priority cell presence indications. The QRT interface assumes this is the case in order to operate correctly.

#### 2.4.2.3 Independently Configurable Interfaces

The receive and transmit sides of the UTOPIA interface are independently configurable for either single-PHY OC-12 or multi-PHY operation. The RX\_OC\_12C\_MODE, TX\_OC\_12C\_MODE, and UTOPIA\_2 bits (refer to section 7.2.11 "UTOPIA\_CONFIG" starting on page 117) configure the device for such operation. This allows versatility in the types of PHY environments that can be supported (for example, environments that contain high-speed, single-PHY devices can be supported, as well as environments in which the QRT must perform single-chip, multi-PHY to high-speed, single-PHY muxing operations). This versatility is particularly helpful when interfacing to the PMC-Sierra, Inc. PM7322 RCMP-800 Operations, Administration, and Maintenance (OAM) processor, since the output of that device has an interface similar to a single-PHY SAT-URN interface.

#### 2.4.2.4 Output Channel Number Insertion

The transmit side of the UTOPIA can be configured to insert the QRT output channel identifier in the HEC/UDF field of outgoing cells. The output channel identifier is a value used by the QRT transmit portion to identify cells of a particular cell stream as they come in from the fabric. Insertion is configured by means of setting the UTOPIA\_CONFIG(7) register. If the configuration bit is set to 0, the UTOPIA inserts a value of FFFFh in the HEC/UDF field. The transmit UTOPIA does not calculate the HEC for outgoing cells.

#### 2.5 Receiver Operation

#### 2.5.1 Receive Channel Lookup

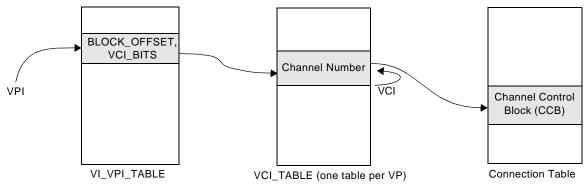

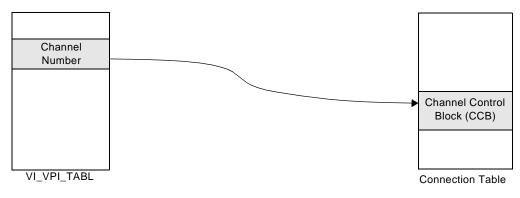

The receive channel lookup uses two tables: VI\_VPI\_TABLE (refer to "VI\_VPI\_TABLE" on page 175) and VCI\_TABLE (refer to "VCI\_TABLE" on page 176) to generate a channel number for an incoming cell. The channel number in turn is used to access the Channel Control Block (CCB), in the connection table. The CCB contains the configuration and state for the connection.

Figure 25 shows the method used to generate the channel number for VCCs: the Virtual Input (VI) number and the VPI bits are used to index into a VI\_VPI\_TABLE of up to 4K entries per VI. Each entry contains the base address of a block in the VCI\_TABLE for that VP and the size of that block. A VCI\_TABLE entry contains a channel number for that VCC. On the other hand, if channel is a VPC, its VI\_VPI\_TABLE contains the channel number directly (see Figure 26).

The number of active VC bits can be modified during operation of the QRT by creating a new VCI\_TABLE and then changing the VC\_BASE and VCI\_BITS (refer to "VCI\_BITS" on page 176) values to point to the new table in one write. This is possible since the BLOCK\_OFFSET (refer to "BLOCK\_OFFSET" on page 176) is just a pointer to the VCI\_TABLE, and the VCI\_TABLE holds no state information. Thus, when the first connection arrives, the eventual size of the VCI block can be initially guessed. Later, if the guess proves to be too low and the table grows too big, there is no penalty: a new VCI\_TABLE can be created on-the-fly.

This method of determining the CCB allows a flexible and wide range of active VPI and VCI bits without requiring an expensive Content-Addressable Memory (CAM) or causing fragmentation of the CCBs.

Figure 25. VCC Channel Lookup

622 Mbps ATM Traffic Management Device

Figure 26 shows the mapping for VPCs.

Figure 26. VPC Channel Lookup

#### 2.5.2 Receive VC (Channel) Queuing

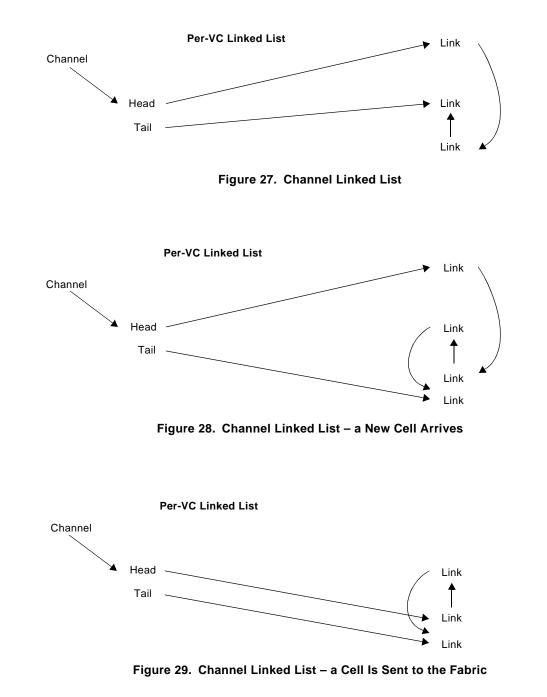

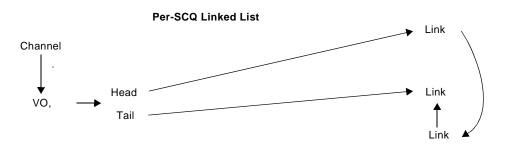

Receive cells are enqueued on a per-VC (channel) basis. This means that there are up to 16K queues. Singly-linked lists are used to queue the cells. The head pointers, the tail pointers, and the linked lists are all in external RAM.

Figure 27, Figure 28, and Figure 29 show the operation of the channel linked list structure.

### 2.5.3 Receive Channel Ring

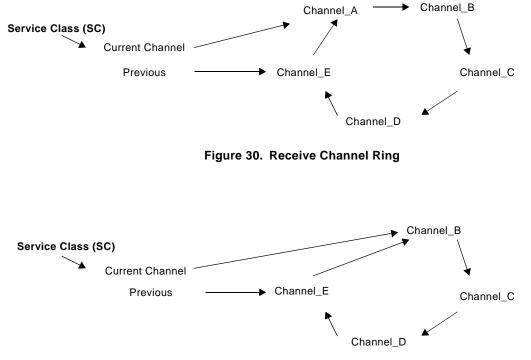

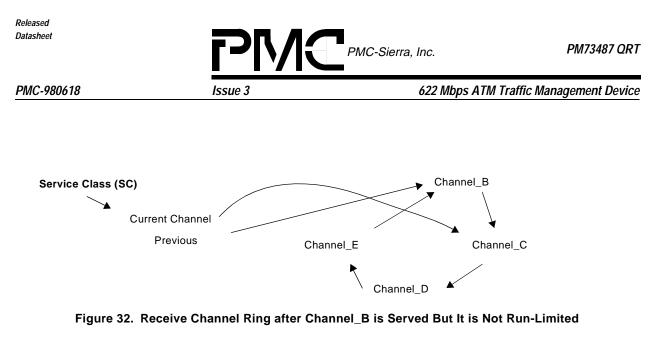

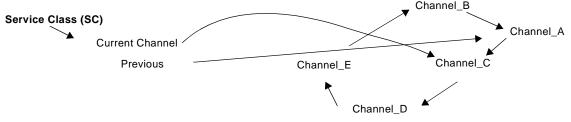

The list of channels eligible to send a cell to the fabric are kept in per-SC rings. The ring is kept in external memory and pointers to the previous and current channels for each SC are kept in internal memory. A channel number is entered into the ring when the first cell for that channel arrives. While cells for that channel are present in the queuing system, the channel can be removed from the ring by the dequeue process (if the channel is run-limited because of the resequencing algorithm as explained in "Receive Sequencing Algorithm" on page 34) and sometimes re-added to the ring by the process that updates the data structures with the results of the last cell time.

Figure 30, Figure 31, Figure 32, and Figure 33 on page 29 show the operation of the receive channel ring.

Figure 31. Receive Channel Ring after Channel\_A Becomes Run-Limited

Figure 33. Receive Channel Ring After Channel\_A Gets Cell Through Fabric and is Added to Ring

#### 2.5.4 Receive Congestion Management

The receive queue controller maintains current, congested, and maximum queue depth counts of cells on a per-VC, per-SC, and per-device basis. Three congestion management algorithms are available for use on a per-channel basis. In each channel's RX\_CH\_CONFIG word (refer to section 9.3.1.1 "RX\_CH\_CONFIG" starting on page 184) there are bits that enable EPD, CLP-based discard, and EFCI. These may be used in combination. In addition, PTD is supported as a mode of the EPD operation.

Figure 34. Receive Congestion Limits

| Released<br>Datasheet | PM      | PMC-Sierra, Inc. | PM73487 QRT                 |

|-----------------------|---------|------------------|-----------------------------|

| PMC-980618            | Issue 3 | 622 Mbps ATN     | I Traffic Management Device |

A congestion hysteresis bit is kept for each threshold. This bit is set whenever the queue depth exceeds the congestion limit for that threshold. This bit remains asserted until the queue depth falls below one-half of the congestion threshold.

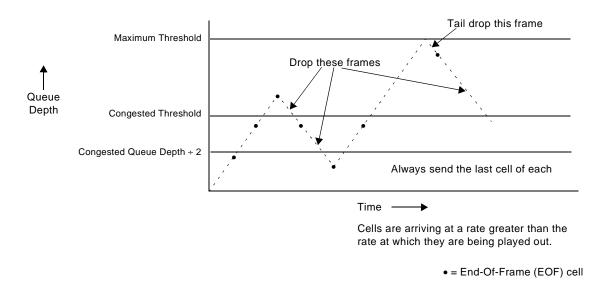

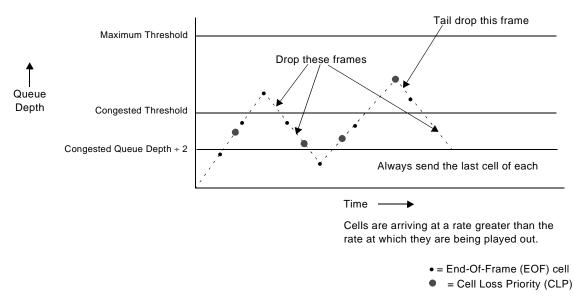

Figure 35 illustrates the operation of EPD/PTD.

Figure 35. EPD/PTD Operation

Figure 36 shows the operation of EPD in combination with CLP-based dropping.

Figure 36. EPD/PTD with CLP Operation

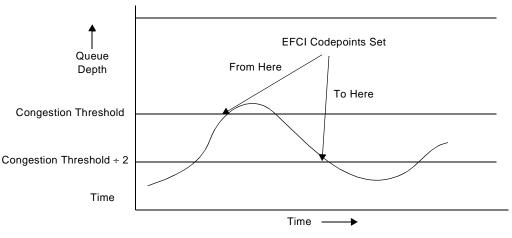

Figure 37 shows the operation of EFCI.

The congestion limits are kept in an exponential form. The interpretation of the limits is the same for all measurements, except the device limit. For the other measurements, the value of "0" causes the measurement to always find congestion. The value of "1" may not be used. The value of  $F_h$  causes congestion to be found for the limit when the queue depth is 31744. This allows a 15-bit value to be used to store the state of each measurement except the device measurement, which has a 16-bit value.

#### 2.5.5 Receive Queue Service Algorithm

Each switch fabric cell time, the receive queue controller selects up to four cells for transmission to the switch fabric. The controller supports per-channel (per-VC) queues with 64 SCs. The controller addresses the following issues: QoS, Cell Delay Variation (CDV) minimization, Minimum Cell Rate (MCR) guarantees, and fairness maximization. The flexibility of the controller ensures that VCs receive their expected bandwidth in a timely fashion depending upon their traffic requirements.

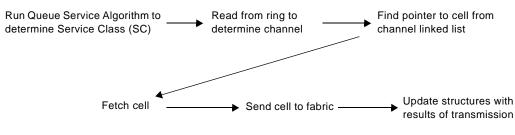

Figure 38. Steps to Send a Cell to the Fabric

The controller has a scheduler that selects cells to be placed in pipelined, "ping-pong" buffers. Once a cell is selected, it is placed in one of these buffers. Each of the four outputs to the switch fabric has two buffers: while a cell in buffer A is being transmitted, another cell is selected and placed into buffer B. On the subsequent switch fabric cell time, the buffers are "ping-ponged", and the cell in buffer B is sent. Meanwhile, another cell is selected for buffer A.

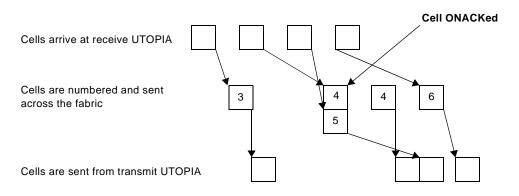

An exception to this process is when the controller receives a negative acknowledgment (NACK) for transmission of a cell. There are two cases: the NACK is an MNACK, indicating cell transmission failed due to collision in the middle of the network, or else the NACK is an ONACK, indicating cell transmission failed due to collision at an output of the network. In the former case, the cell's switch fabric priority (assigned during VC setup) is compared with that of the cell (if any) in the other ping-pong buffer. Call the first cell X, and the second cell Y. If the priority of cell X is greater than or equal to that of cell Y, the buffers are not ping-ponged, and cell X will be resent next time. If the priority of cell X is less than that of cell Y, cell X remains in its buffer, and the buffers are ping-ponged as usual, with cell Y being sent next. In the latter case, the cell is requeued at the head of its VC's queue. Thus, the cell will be retransmitted, but at a later time than if the cell was MNACKed.

The switch fabric has been specially designed to minimize the possibility of consecutive collisions at the same place in the middle of the network, and thus a cell's transmission that failed in that manner stands a good probability of being successful in an immediately subsequent transmission attempt. Collisions at an output of the network are more likely to be recurring for a period of time, and thus the next transmission attempt is delayed.

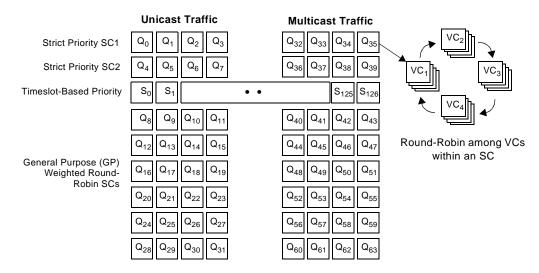

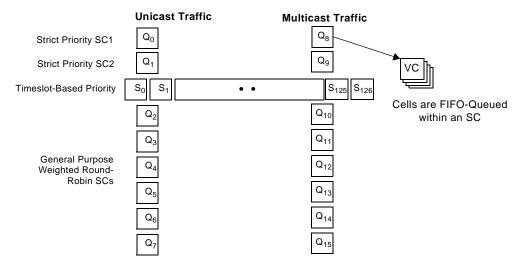

The scheduler that places cells in the ping-pong buffers operates as follows: The SCs are arranged in a tabular fashion as seen in Figure 39. An SC is designated for either unicast or multicast traffic. Additionally, an SC is designated as either strict priority SC1, strict priority SC2, or General Purpose (GP). Associated with each SC is a weight of either 1, 4, 16, or 64. This information is

| Released<br>Datasheet | PM      | PMC-Sierra, Inc. | PM73487 QRT                 |

|-----------------------|---------|------------------|-----------------------------|

| PMC-980618            | Issue 3 | 622 Mbps ATN     | 1 Traffic Management Device |

used by the controller to decide which SC to service. Following this decision, the selected SC's VCs are serviced in a round-robin manner. The selected VC then transmits the first cell in its queue.

Figure 39. Receive Service Class (SC) Map

The general algorithm for deciding which SC to service is as follows (certain multicast SCs may be ineligible for selection in particular modes or operating conditions; these will be described after the numbered list that follows):

- 1. Strict priority SC1 has primary service priority. If there is an SC1 with a cell, it will be selected. The SC1 service classes are serviced in a weighted round-robin manner, alternating between unicast and multicast classes (Q0, Q32, Q1, Q33, Q2, Q34, Q3, Q35, Q0, ...). The SC1 round-robin pointer will remain pointed at an SC for up to *w* cell selections, where *w* is the SC's weight. If no cells are available in an SC, the round-robin pointer is advanced. Thus, the most time-critical VCs should be placed in an SC1 service classes. The pointer for the SC1 service classes is separate from the pointer to the SC2 and GP service classes.

- 2. Strict priority SC2 has secondary service priority. It is treated in the same fashion as SC1, except it has its own independent round-robin pointer and the weighted round-robin order is: Q4, Q36, Q5, Q37, Q6, Q38, Q7, Q39, Q4, ....

- 3. If no cell exists in the strict priority classes, then the controller accesses the timeslot-based priority table in a round-robin manner. Each entry of this table contains a GP SC number. If the SC pointed to by the active entry has cells, that SC is selected. The active entry is incremented to the next timeslot each time the timeslot table is accessed. The table has 127 entries and wraps around. This servicing mechanism provides the MCR guarantee on a per-SC basis. The number of times an SC is placed in the timeslot table can be used to determine its MCR.

- 4. If no cell exists in the strict priority classes, and no cell exists in the SC pointed to by the active entry of the timeslot-based priority table, then the GP SCs are serviced in a weighted round-robin manner similar to the SC1 and SC2 classes (Q8, Q40, Q9, Q41, Q10, Q42, Q11, Q43, Q12, Q44, ..., Q31, Q63, Q8, ...). Again this has a separate round-robin pointer than that kept for the SC1 and SC2 service classes.

| Released<br>Datasheet |         | PMC-Sierra, Inc. | PM73487 QRT                 |

|-----------------------|---------|------------------|-----------------------------|

| PMC-980618            | Issue 3 |                  | 1 Traffic Management Device |