ISSUE 1

SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

PM5381

S/UNI-2488

### SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

### **DATASHEET**

PROPRIETARY AND CONFIDENTIAL

PRELIMINARY

ISSUE 1: MARCH 2000

i

DATASHEET

PMC-2000489

ISSUE 1

### SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

### **CONTENTS**

| 4                                                              |

|----------------------------------------------------------------|

| 4                                                              |

| 4                                                              |

|                                                                |

|                                                                |

|                                                                |

| ,                                                              |

| 9                                                              |

| 10                                                             |

|                                                                |

| 13                                                             |

|                                                                |

| 17                                                             |

| 19                                                             |

|                                                                |

| 04                                                             |

| 20                                                             |

|                                                                |

| 20                                                             |

| 20                                                             |

| 20                                                             |

| 20<br>2 <sup>2</sup>                                           |

| 20<br>22<br>23                                                 |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

| 20<br>22<br>22<br>24<br>33<br>39<br>40<br>44<br>42<br>44<br>50 |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

|                                                                |

### ISSUE 1

| 1  | 0.7  | RECEIVE CELLAND FRAME PROCESSOR (RCFP)               | 65  |

|----|------|------------------------------------------------------|-----|

|    | 0.8  | RECEIVE SCALABLE DATA QUEUE (RXSDQ)                  |     |

|    | 0.9  | RECEIVE PHY INTERFACE (RXPHY)                        |     |

|    | 0.10 | ,                                                    |     |

| 1  | 0.11 | SONET/SDH TRANSMIT LINE INTERFACE (STLI)             |     |

| 1  | 0.12 | ,                                                    |     |

| 1  | 0.13 | TRANSMIT TAIL TRACE PROCESSOR (TTTP)                 | 75  |

| 1  | 0.14 | TRANSMIT HIGH ORDER PATH PROCESSOR (THPP)            | 76  |

| 1  | 0.15 | TRANSMIT CELL AND FRAME PROCESSOR (TCFP)             | 76  |

| 1  | 0.16 | TRANSMIT SCALABLE DATA QUEUE (TXSDQ)                 | 79  |

| 1  | 0.17 | TRANSMIT PHY INTERFACES (RXPHY AND TXPHY)            | 79  |

| 1  | 0.18 | SONET/SDH BIT ERROR RATE MONITOR (SBER)              | 80  |

| 1  | 0.19 | SONET/SDH ALARM REPORTING CONTROLLER (SARC)          | 80  |

| 1  | 0.20 | ` ,                                                  |     |

| 1  | 0.21 |                                                      |     |

| 1  | 0.22 |                                                      |     |

| 1  | 0.23 | MICROPROCESSOR INTERFACE                             | 83  |

| 11 | N    | IORMAL MODE REGISTER DESCRIPTION                     | 97  |

| 12 | c    | PERATION                                             | 430 |

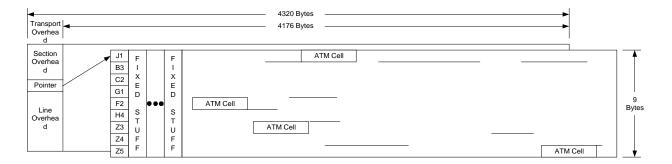

| 1  | 2.2  | SONET/SDH FRAME MAPPINGS AND OVERHEAD BYTE USAGE     | 433 |

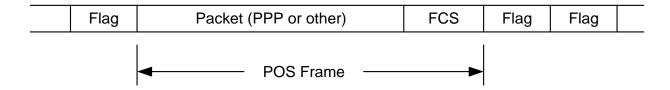

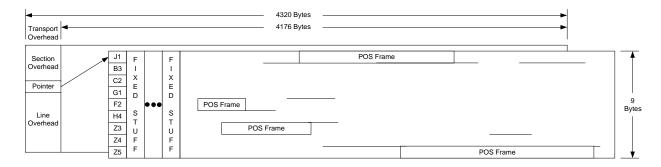

|    | 2.3  | POS/HDLC DATA STRUCTURE                              |     |

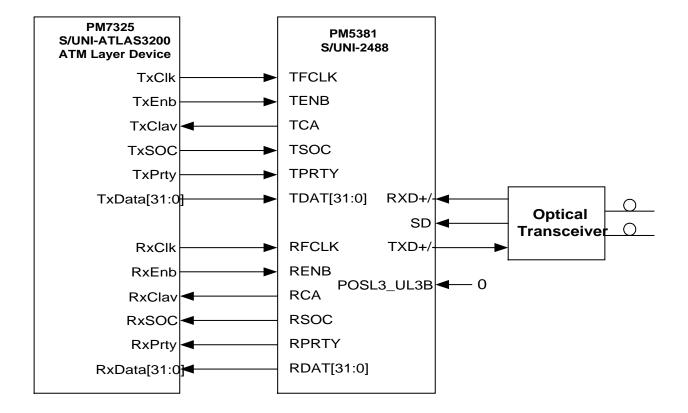

|    | 2.4  | SETTING ATM MODE OF OPERATION                        |     |

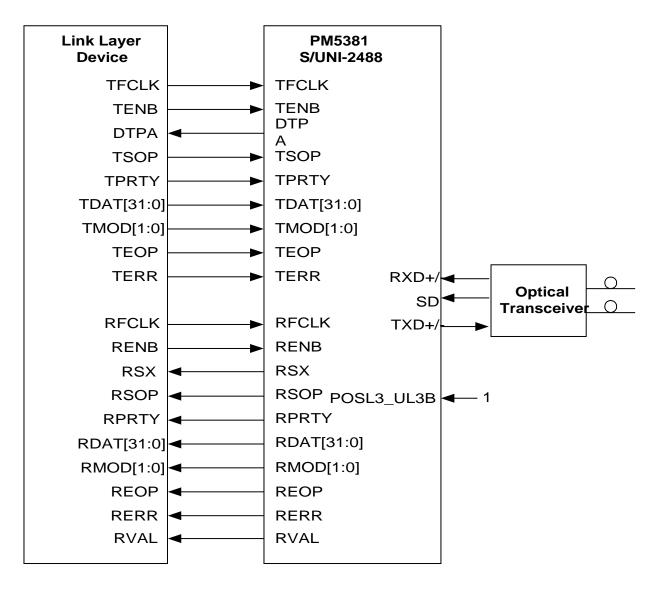

|    | 2.5  | SETTING PACKET OVER SONET/SDH MODE OF OPERATION      |     |

| 1  | 2.6  | BIT ERROR RATE MONITOR                               |     |

| 1  | 2.7  | CLOCKING OPERATIONS                                  | 439 |

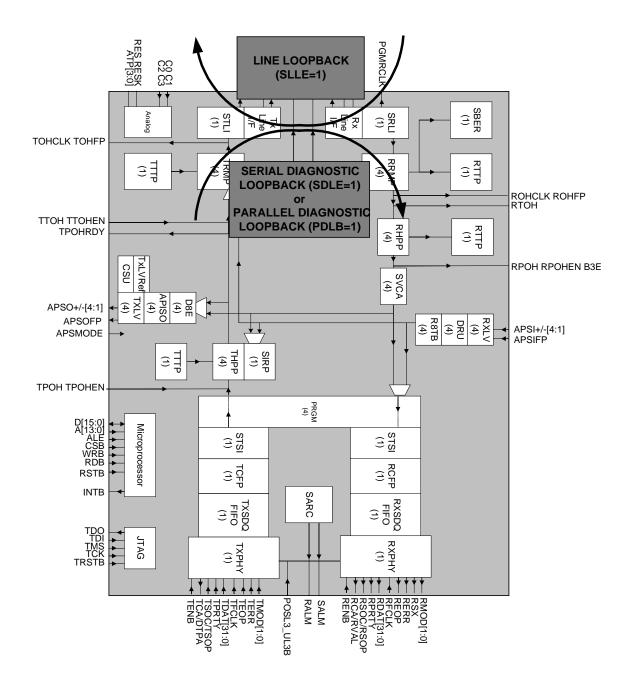

| 1  | 2.8  | LOOPBACK OPERATION                                   | 439 |

| 1  | 2.9  | BOARD DESIGN RECOMMENDATIONS                         | 440 |

| 1  | 2.10 | Power Supplies                                       | 440 |

| 1  | 2.11 | INTERFACING TO ECL OR PECL DEVICES                   | 440 |

| 13 | F    | UNCTIONAL TIMING                                     | 441 |

| 1  | 3.1  | SERIAL LINE INTERFACE                                | 441 |

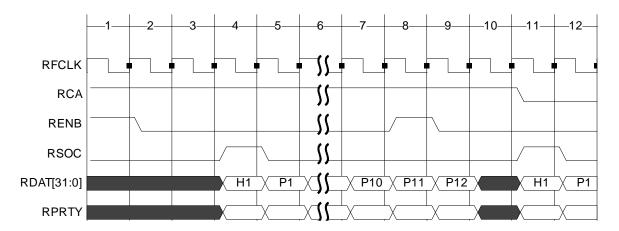

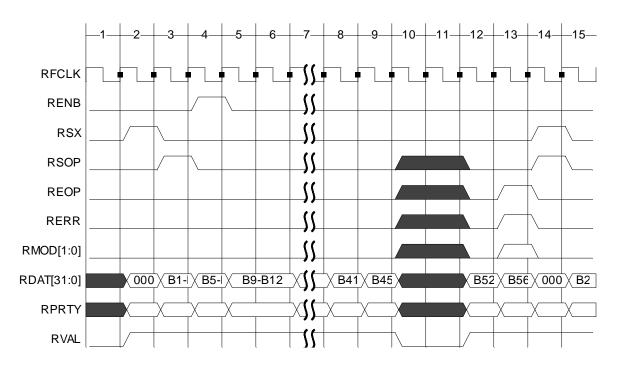

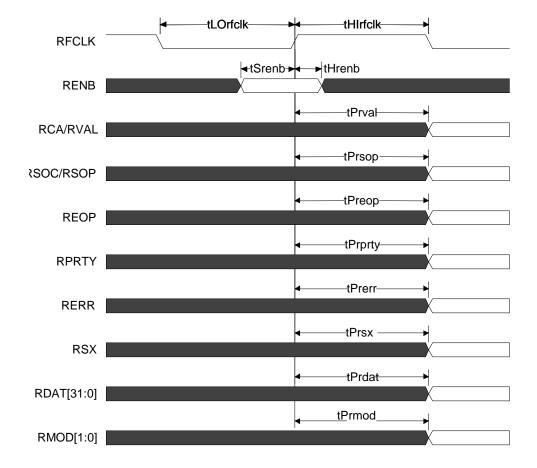

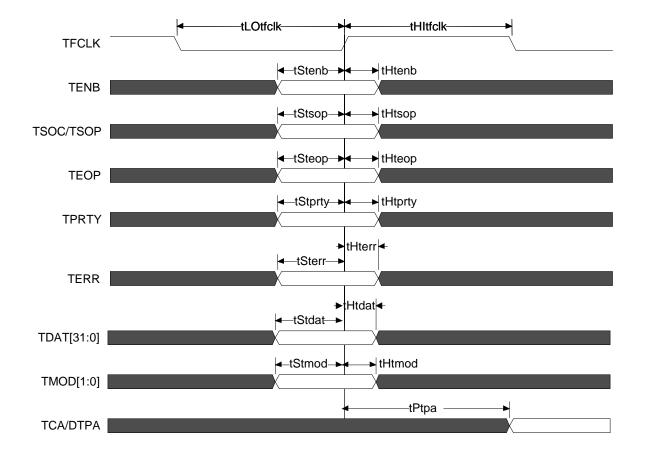

| 1  | 3.2  | ATM UTOPIA LEVEL 3 SYSTEM INTERFACE                  | 441 |

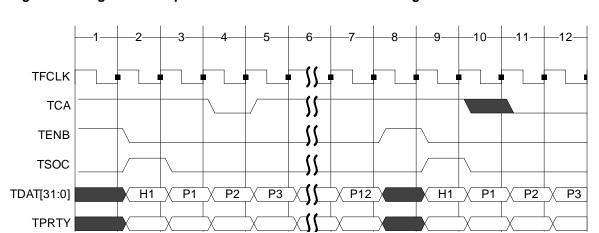

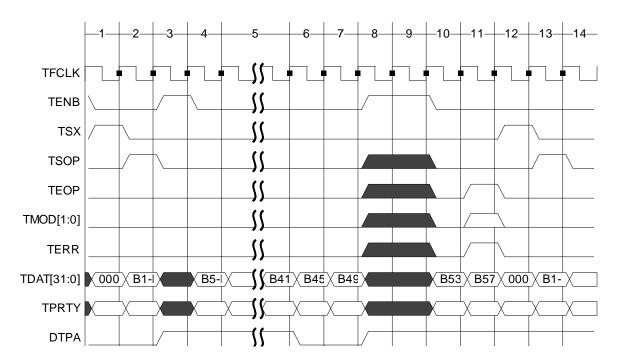

| 1  | 3.3  | PACKET OVER SONET/SDH (POS) LEVEL 3 SYSTEM INTERFACE | 443 |

| 1  | 3.4  | SECTION AND LINE DATA COMMUNICATION CHANNELS         | 446 |

| 1  | 3.5  | S/UNI-2488 CONCEPTUAL REGIONS                        | 446 |

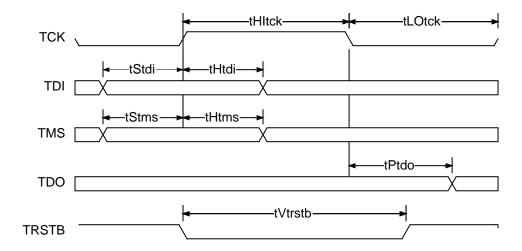

| 14 | Т    | EST FEATURES DESCRIPTION                             | 447 |

| 15 | F    | UNCTIONAL TIMING                                     | 448 |

|    |      |                                                      |     |

| 16 | Α    | BSOLUTE MAXIMUM RATINGS                              | 449 |

| 17 | г    | C CHARACTERISTICS                                    | 450 |

### ISSUE 1

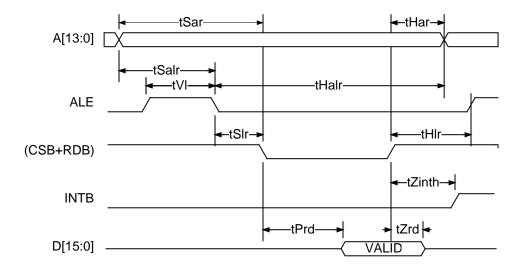

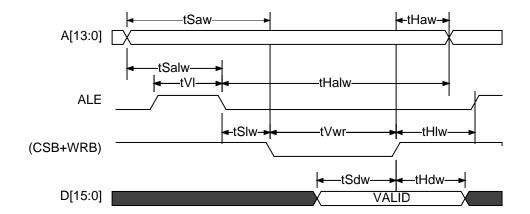

| 18  | MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS | 453 |

|-----|-------------------------------------------------|-----|

| 19  | A.C. TIMING CHARACTERISTICS                     | 457 |

| 19. | .1 APS PORT INTERFACE                           | 461 |

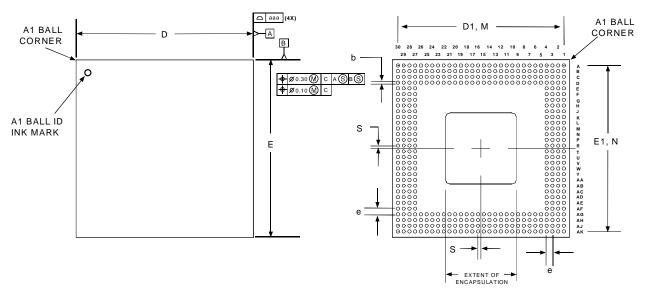

| 20  | ORDERING AND THERMAL INFORMATION                | 463 |

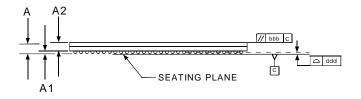

| 21  | MECHANICAL INFORMATION                          | 464 |

ISSUE 1

### SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

### **LIST OF REGISTERS**

| REGISTER 0000H: S/UNI-2488 IDENTITY, AND GLOBAL PERFORMANCE MONITOR UPDATE. | 98  |

|-----------------------------------------------------------------------------|-----|

| REGISTER 0001H: S/UNI-2488 MASTER RESET, CONFIGURATION, AND LOOPBACK        | 99  |

| REGISTER 0003H: S/UNI-2488 CLOCK MONITORS                                   | 102 |

| REGISTER 0004H: S/UNI-2488 MASTER INTERRUPT STATUS #1#1                     | 104 |

| REGISTER 0005H: S/UNI-2488 MASTER INTERRUPT STATUS #2                       | 105 |

| REGISTER 0006H: S/UNI-2488 MASTER INTERRUPT STATUS #3#                      | 106 |

| REGISTER 0007H: S/UNI-2488 MASTER INTERRUPT STATUS #4                       | 107 |

| REGISTER 0008H: S/UNI-2488 MASTER INTERRUPT STATUS #5                       | 108 |

| REGISTER 0009H: S/UNI-2488 MASTER INTERRUPT STATUS #6#                      | 110 |

| REGISTER 000AH: S/UNI-2488 MASTER INTERRUPT STATUS #7                       | 112 |

| REGISTER 000BH: UNUSED                                                      | 113 |

| REGISTER 000CH: APS INPUT TELECOMBUS SYNCHRONIZATION DELAY                  | 114 |

| REGISTER 000DH: APS OUTPUT TELECOMBUS SYNCHRONIZATION DELAY                 | 115 |

| REGISTER 000EH: S/UNI-2488 DIAGNOSTICS                                      | 116 |

| REGISTER 000FH: S/UNI-2488 FREE REGISTER                                    | 118 |

| REGISTER 0010H: RX2488 ANALOG INTERRUPT CONTROL/STATUS                      | 119 |

| REGISTER 0011H: RX2488 ANALOG CRU CONTROL                                   | 122 |

| REGISTER 0012H: RX2488 ANALOG CRU CLOCK TRAINING CONFIGURATION AND STATUS.  | 125 |

| REGISTER 0013H: RX2488 ANALOG PRBS CONTROL                                  | 127 |

| REGISTER 0014H: RX2488 ANALOG PATTERN REGISTER                              | 129 |

| REGISTER 0030H: SRLI CLOCK CONFIGURATION                                    | 130 |

| REGISTER 0031H: SRLI PGM CLOCK CONFIGURATION                                | 132 |

ISSUE 1

| REGISTER 0038H: STLI CLOCK CONFIGURATION                                                                                                                                                                                                                                           | 134 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| REGISTER 0039H: STLI PGM CLOCK CONFIGURATION                                                                                                                                                                                                                                       | 135 |

| THE PROGRAMMABLE TRANSMIT CLOCK FREQUENCY SELECTION (PGMTCLKSEL) BIT SELECTS THE FREQUENCY OF THE PGMTCLK OUTPUT CLOCK. WHEN PGMTCLKSEL IS SE HIGH, PGMTCLK IS A NOMINAL 8 KHZ CLOCK. WHEN PGMTCLKSEL IS SET TO LOGIC ZERO PGMTCLK IS A NOMINAL REGISTER 0040H: RRMP CONFIGURATION | ),  |

| REGISTER 0041H: RRMP STATUS                                                                                                                                                                                                                                                        | 138 |

| REGISTER 0042H: RRMP INTERRUPT ENABLE                                                                                                                                                                                                                                              | 140 |

| REGISTER 0043H: RRMP INTERRUPT STATUS                                                                                                                                                                                                                                              | 141 |

| REGISTER 0044H: RRMP RECEIVE APS                                                                                                                                                                                                                                                   | 143 |

| REGISTER 0045H: RRMP RECEIVE SSM                                                                                                                                                                                                                                                   | 144 |

| REGISTER 0046H: RRMP AIS ENABLE                                                                                                                                                                                                                                                    | 145 |

| REGISTER 0047H: RRMP SECTION BIP ERROR COUNTER                                                                                                                                                                                                                                     | 147 |

| REGISTER 0048H: RRMP LINE BIP ERROR COUNTER (LSB)                                                                                                                                                                                                                                  | 148 |

| REGISTER 0049H: RRMP LINE BIP ERROR COUNTER (MSB)                                                                                                                                                                                                                                  | 148 |

| REGISTER 004AH: RRMP LINE REI ERROR COUNTER (LSB)                                                                                                                                                                                                                                  | 149 |

| REGISTER 004BH: RRMP LINE REI ERROR COUNTER (MSB)                                                                                                                                                                                                                                  | 149 |

| REGISTER 0080H: TRMP CONFIGURATION                                                                                                                                                                                                                                                 | 150 |

| REGISTER 0081H: TRMP REGISTER INSERTION                                                                                                                                                                                                                                            | 153 |

| REGISTER 0082H: TRMP ERROR INSERTION                                                                                                                                                                                                                                               | 156 |

| REGISTER 0083H: TRMP TRANSMIT J0 AND Z0                                                                                                                                                                                                                                            | 158 |

| REGISTER 0084H: TRMP TRANSMIT E1 AND F1                                                                                                                                                                                                                                            | 159 |

| REGISTER 0085H: TRMP TRANSMIT D1D3 AND D4D12                                                                                                                                                                                                                                       | 160 |

| REGISTER 0086H: TRMP TRANSMIT K1 AND K2                                                                                                                                                                                                                                            | 161 |

| REGISTER 0087H: TRMP TRANSMIT S1 AND Z1                                                                                                                                                                                                                                            | 162 |

ISSUE 1

| REGISTER 0088H: TRMP TRANSMIT Z2 AND E2                 | 163 |

|---------------------------------------------------------|-----|

| REGISTER 0089H: TRMP TRANSMIT H1 AND H2 MASK            | 164 |

| REGISTER 008A: TRMP TRANSMIT B1 AND B2 MASK             | 165 |

| REGISTER 00A0H: TRMP AUX2 CONFIGURATION                 | 166 |

| REGISTER 00C0H: TRMP AUX3 CONFIGURATION                 | 166 |

| REGISTER 00E0H: TRMP AUX4 CONFIGURATION                 | 166 |

| REGISTER 00A2H: TRMP AUX2 ERROR INSERTION               | 167 |

| REGISTER 00C2H: TRMP AUX3 ERROR INSERTION               | 167 |

| REGISTER 00E2H: TRMP AUX4 ERROR INSERTION               | 167 |

| REGISTER 0110H: SBER CONFIGURATION                      | 168 |

| REGISTER 0111H: SBER STATUS                             | 170 |

| REGISTER 0112H: SBER INTERRUPT ENABLE                   | 171 |

| REGISTER 0113H: SBER INTERRUPT STATUS                   | 172 |

| REGISTER 0114H: SBER SF BERM ACCUMULATION PERIOD (LSB)  | 173 |

| REGISTER 0115H: SBER SF BERM ACCUMULATION PERIOD (MSB)  | 173 |

| REGISTER 0116H: SBER SF BERM SATURATION THRESHOLD (LSB) | 174 |

| REGISTER 0117H: SBER SF BERM SATURATION THRESHOLD (MSB) | 174 |

| REGISTER 0118H: SBER SF BERM DECLARING THRESHOLD (LSB)  | 175 |

| REGISTER 0119H: SBER SF BERM DECLARING THRESHOLD (MSB)  | 175 |

| REGISTER 011AH: SBER SF BERM CLEARING THRESHOLD (LSB)   | 176 |

| REGISTER 011BH: SBER SF BERM CLEARING THRESHOLD (MSB)   | 176 |

| REGISTER 011CH: SBER SD BERM ACCUMULATION PERIOD (LSB)  | 177 |

| REGISTER 011DH: SBER SD BERM ACCUMULATION PERIOD (MSB)  | 177 |

| REGISTER 011EH: SBER SD BERM SATURATION THRESHOLD (LSB) | 178 |

### PMC-Sierra, Inc.

### ISSUE 1

| REGISTER 011FH: SBER SD BERM SATURATION THRESHOLD (MSB)                                                                                                                                                                                                               | 178 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| REGISTER 0120H: SBER SD BERM DECLARATION THRESHOLD (LSB)                                                                                                                                                                                                              | 179 |

| REGISTER 0121H: SBER SD BERM DECLARATION THRESHOLD (MSB)                                                                                                                                                                                                              | 179 |

| REGISTER 0122H: SBER SD BERM CLEARING THRESHOLD (LSB)1                                                                                                                                                                                                                | 180 |

| REGISTER 0123H: SBER SD BERM CLEARING THRESHOLD (MSB)1                                                                                                                                                                                                                | 180 |

| REGISTER 0130H: RTTP SECTION INDIRECT ADDRESS1                                                                                                                                                                                                                        | 181 |

| REGISTER 0131H: RTTP SECTION INDIRECT DATA1                                                                                                                                                                                                                           | 183 |

| REGISTER 0132H: RTTP SECTION TRACE UNSTABLE STATUS1                                                                                                                                                                                                                   | 184 |

| REGISTER 0133H: RTTP SECTION TRACE UNSTABLE INTERRUPT ENABLE1                                                                                                                                                                                                         | 185 |

| REGISTER 0134H: RTTP SECTION TRACE UNSTABLE INTERRUPT STATUS1                                                                                                                                                                                                         | 186 |

| REGISTER 0135H: RTTP SECTION TRACE MISMATCH STATUS1                                                                                                                                                                                                                   | 187 |

| REGISTER 0136H: RTTP SECTION TRACE MISMATCH INTERRUPT ENABLE1                                                                                                                                                                                                         | 188 |

| REGISTER 0137H: RTTP SECTION TRACE MISMATCH INTERRUPT STATUS1                                                                                                                                                                                                         | 189 |

| INDIRECT REGISTER 00H: RTTP SECTION TRACE CONFIGURATION                                                                                                                                                                                                               | 190 |

| INDIRECT REGISTER 40H TO 7FH: RTTP SECTION CAPTURED TRACE                                                                                                                                                                                                             | 192 |

| INDIRECT REGISTER 80H TO BFH: RTTP SECTION ACCEPTED TRACE                                                                                                                                                                                                             | 193 |

| INDIRECT REGISTER C0H TO FFH: RTTP SECTION EXPECTED TRACE                                                                                                                                                                                                             | 194 |

| REGISTER 0138H: TTTP SECTION INDIRECT ADDRESS                                                                                                                                                                                                                         | 195 |

| REGISTER 0139H: TTTP SECTION INDIRECT DATA                                                                                                                                                                                                                            | 197 |

| INDIRECT REGISTER 0138H: TTTP SECTION TRACE CONFIGURATION                                                                                                                                                                                                             | 198 |

| INDIRECT REGISTER 40H TO 7FH: TTTP SECTION TRACE1                                                                                                                                                                                                                     | 199 |

| REGISTER 0200H: RHPP STS-1/STM-0 #1 THROUGH #12 INDIRECT ADDRESS REGISTER 0280H RHPP STS-1/STM-0 #13 THROUGH #24 INDIRECT ADDRESS REGISTER 0300H: RHPP STS-1/STM 0 #25 THROUGH #36 INDIRECT ADDRESS REGISTER 0380H: RHPP STS-1/STM-0 #37 THROUGH #48 INDIRECT ADDRESS | M-  |

ISSUE 1

| REGISTER 0201H: RHPP STS-1/STM-0 #1 THROUGH #12 INDIRECT DATA REGISTER 028<br>STS-1/STM-0 #13 THROUGH #24 INDIRECT DATA REGISTER 0301H: RHPP STS-1/STM-0<br>THROUGH #36 INDIRECT DATA REGISTER 0381H: RHPP STS-1/STM-0 #37 THROUGH #4<br>INDIRECT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | #25                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| REGISTER 0208H, 0210H, 0218H, 0220H, 0228H, 0230H, 0238H, 0240H, 0248H, 0250H, 0320H, 0330H, 0338H, 0340H, 0350H, 0358H, 0360H REGISTER 0388H, 0390H, 0398H, 03A0H, 03A8H, 03B0H, 03B8H, 030C8H, 03D0H, 03D8H, 03E0H:  STS-1/STM-0 #N (WHERE N=1 TO 48) POINTER INTERPRETER STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2D0H,<br>48H,             |

| REGISTER 0209H, 0211H, 0219H, 0221H, 0229H, 0231H, 0239H, 0241H, 0249H, 0251H, 02501H, 03501H, | 2D1H,<br>49H,             |

| REGISTER 020AH, 0212H, 021AH, 0222H, 022AH, 0232H, 023AH, 0242H, 024AH, 0252H, 0<br>0262H REGISTER 028AH, 0292H, 029AH, 02A2H, 02AAH, 02B2H, 02BAH, 02C2H, 02CAH,<br>02DAH, 02E2H REGISTER 030AH, 0312H, 031AH, 0322H, 032AH, 0332H, 033AH, 0342H, 0<br>0352H, 035AH, 0362H REGISTER 038AH, 0392H, 039AH, 03A2H, 03AAH, 03B2H, 03BAH, 0<br>03CAH, 03D2H, 03DAH, 03E2H:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 02D2H,<br>34AH,<br>03C2H, |

| P STS-1/STM-0 #N (WHERE N=1 TO 48) POINTER INTERPRETER INTERRUPT STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RHP<br>207                |

| REGISTER 020B: RHPP STS-1/STM-0 #1 ERROR MONITOR STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 209                       |

| REGISTER 020C: RHPP STS-1/STM-0 #1 ERROR MONITOR INTERRUPT ENABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 211                       |

| REGISTER 020D: RHPP STS-1/STM-0 #1 ERROR MONITOR INTERRUPT STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 213                       |

| REGISTER 020E: RHPP STS-1/STM-0 #1 PATH BIP ERROR COUNTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 215                       |

| REGISTER 020F: RHPP STS-1/STM-0 #1 PATH REI ERROR COUNTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 216                       |

| INDIRECT REGISTER 00H: RHPP POINTER INTERPRETER CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 217                       |

| INDIRECT REGISTER 01H: RHPP ERROR MONITOR CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 219                       |

| INDIRECT REGISTER 02H: RHPP POINTER VALUE AND ERDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 222                       |

| INDIRECT REGISTER 03H: RHPP CAPTURED AND ACCEPTED PSL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 223                       |

| INDIRECT REGISTER 04H: RHPP EXPECTED PSL AND PDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 224                       |

ISSUE 1

| INDIRECT REGISTER 05H: RHPP GPO AND OTHER STATUS                                                                                                                                                                                                                  | 225           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| REGISTER 0400H: THPP STS-1/STM-0 #1 THROUGH #12 INDIRECT ADDRESS REGISTER 0480 THPP STS-1/STM-0 #13 THROUGH #24 INDIRECT ADDRESS REGISTER 0500H: THPP STS-1/ST #25 THROUGH #36 INDIRECT ADDRESS REGISTER 0580H: THPP STS-1/STM-0 #37 THROUGH INDIRECT ADDRESS     | TM-0<br>  #48 |

| REGISTER 0401H: THPP STS-1/STM-0 #1 THROUGH #12 INDIRECT DATA REGISTER 0481H: TI<br>STS-1/STM-0 #13 THROUGH #24 INDIRECT DATA REGISTER 0501H: THPP STS-1/STM-0 #25<br>THROUGH #36 INDIRECT DATA REGISTER 0581H: THPP STS-1/STM-0 #37 THROUGH #48<br>INDIRECT DATA |               |

| REGISTER 0402: THPP PAYLOAD CONFIGURATION                                                                                                                                                                                                                         |               |

| INDIRECT REGISTER 00H: THPP CONTROL REGISTER                                                                                                                                                                                                                      | 231           |

| INDIRECT REGISTER 01H: THPP SOURCE AND POINTER CONTROL REGISTER                                                                                                                                                                                                   | 233           |

| INDIRECT REGISTER 02H: THPP CURRENT POINTER REGISTER                                                                                                                                                                                                              | 235           |

| INDIRECT REGISTER 03H: THPP ARBITRARY POINTER REGISTER                                                                                                                                                                                                            | 236           |

| INDIRECT REGISTER 05H: THPP B3 MASK AND FIXED STUFF BYTE                                                                                                                                                                                                          | 238           |

| INDIRECT REGISTER 06H: THPP TRANSMIT C2 AND J1                                                                                                                                                                                                                    | 239           |

| INDIRECT REGISTER 07H: THPP TRANSMIT H4 MASK AND G1                                                                                                                                                                                                               | 240           |

| INDIRECT REGISTER 08H: THPP TRANSMIT F2 AND Z3                                                                                                                                                                                                                    | 241           |

| INDIRECT REGISTER 09H: THPP TRANSMIT Z4 AND Z5                                                                                                                                                                                                                    | 242           |

| REGISTER 0600H: RSVCA INDIRECT ADDRESS                                                                                                                                                                                                                            | 243           |

| REGISTER 0601H: RSVCA INDIRECT DATA                                                                                                                                                                                                                               | 245           |

| REGISTER 0603H: RSVCA POSITIVE JUSTIFICATION INTERRUPT STATUS                                                                                                                                                                                                     | 248           |

| REGISTER 0604H: RSVCA NEGATIVE JUSTIFICATION INTERRUPT STATUS                                                                                                                                                                                                     | 249           |

| REGISTER 0605H: RSVCA FIFO OVERFLOW INTERRUPT STATUS                                                                                                                                                                                                              | 250           |

| REGISTER 0606H: RSVCA FIFO UNDERFLOW INTERRUPT STATUS                                                                                                                                                                                                             |               |

| INDIRECT REGISTER 00H: RSVCA POINTER JUSTIFICATION INTERRUPT ENABLE                                                                                                                                                                                               |               |

| INDIRECT REGISTER 01H: RSVCA FIFO INTERRUPT ENABLE                                                                                                                                                                                                                | 253           |

ISSUE 1

| INDIRECT REGISTER 02H: RSVCA POSITIVE JUSTIFICATIONS PERFORMANCE MONITOR | 254 |

|--------------------------------------------------------------------------|-----|

| INDIRECT REGISTER 03H: RSVCA NEGATIVE JUSTIFICATIONS PERFORMANCE MONITOR | 255 |

| INDIRECT REGISTER 04H: RSVCA DIAGNOSTIC/CONFIGURATION                    | 256 |

| REGISTER 0680H: TSVCA INDIRECT ADDRESS                                   | 258 |

| REGISTER 0601H: TSVCA INDIRECT DATA                                      | 260 |

| REGISTER 0603H: TSVCA POSITIVE JUSTIFICATION INTERRUPT STATUS            | 261 |

| REGISTER 0604H: TSVCA NEGATIVE JUSTIFICATION INTERRUPT STATUS            | 262 |

| REGISTER 0605H: TSVCA FIFO OVERFLOW INTERRUPT STATUS                     | 263 |

| REGISTER 0606H: TSVCA FIFO UNDERFLOW INTERRUPT STATUS                    | 264 |

| INDIRECT REGISTER 00H: TSVCA POINTER JUSTIFICATION INTERRUPT ENABLE      | 265 |

| INDIRECT REGISTER 01H: TSVCA FIFO INTERRUPT ENABLE                       | 266 |

| INDIRECT REGISTER 02H: TSVCA POSITIVE JUSTIFICATIONS PERFORMANCE MONITOR | 267 |

| INDIRECT REGISTER 03H: TSVCA NEGATIVE JUSTIFICATIONS PERFORMANCE MONITOR | 268 |

| INDIRECT REGISTER 04H: TSVCA DIAGNOSTIC/CONFIGURATION                    | 269 |

| REGISTER 0700H: RTTP PATH INDIRECT ADDRESS                               | 271 |

| REGISTER 0701H: RTTP PATH INDIRECT DATA                                  | 273 |

| REGISTER 0702H: RTTP PATH TRACE UNSTABLE STATUS                          | 274 |

| REGISTER 0703H: RTTP PATH TRACE UNSTABLE INTERRUPT ENABLE                | 275 |

| REGISTER 0704H: RTTP PATH TRACE UNSTABLE INTERRUPT STATUS                | 276 |

| REGISTER 0705H: RTTP PATH TRACE MISMATCH STATUS                          | 277 |

| REGISTER 0706H: RTTP PATH TRACE MISMATCH INTERRUPT ENABLE                | 278 |

| REGISTER 0707H: RTTP PATH TRACE MISMATCH INTERRUPT STATUS                | 279 |

| INDIRECT REGISTER 00H: RTTP PATH TRACE CONFIGURATION                     | 280 |

| INDIRECT REGISTER 40H TO 7FH: RTTP PATH CAPTURED TRACE                   | 282 |

ISSUE 1

| INDIRECT REGISTER 80H TO BFH: RTTP PATH ACCEPTED TRACE | 283 |

|--------------------------------------------------------|-----|

| INDIRECT REGISTER C0H TO FFH: RTTP PATH EXPECTED TRACE | 284 |

| REGISTER 0708H: TTTP PATH INDIRECT ADDRESS             | 285 |

| REGISTER 0709H: TTTP PATH INDIRECT DATA                | 287 |

| INDIRECT REGISTER 00H: TTTP PATH TRACE CONFIGURATION   | 288 |

| INDIRECT REGISTER 40H TO 7FH: TTTP PATH TRACE          | 289 |

| REGISTER 0720H: SARC INDIRECT ADDRESS                  | 290 |

| REGISTER 0722H: SARC SECTION CONFIGURATION             | 291 |

| REGISTER 0723H: SARC SECTION SALM ENABLE               | 292 |

| REGISTER 0724H: SARC SECTION RLAISINS ENABLE           | 295 |

| REGISTER 0725H: SARC SECTION TLRDIINS ENABLE           | 296 |

| REGISTER 0728H: SARC PATH CONFIGURATION                | 297 |

| REGISTER 0729H: SARC PATH RALM ENABLE                  | 299 |

| REGISTER 072A: SARC PATH RPAISINS ENABLE               | 300 |

| REGISTER 0730H: SARC LOP POINTER STATUS                | 301 |

| REGISTER 0731H: SARC LOP POINTER INTERRUPT ENABLE      | 302 |

| REGISTER 0732H: SARC LOP POINTER INTERRUPT STATUS      | 303 |

| REGISTER 0733H: SARC AIS POINTER STATUS                | 304 |

| REGISTER 0734H: SARC AIS POINTER INTERRUPT ENABLE      | 305 |

| REGISTER 0735H: SARC AIS POINTER INTERRUPT STATUS      | 306 |

| REGISTER 0740H: RCFP CONFIGURATION                     | 307 |

| REGISTER 0741H: RCFP INTERRUPT ENABLE                  | 310 |

| REGISTER 0742H: RCFP INTERRUPT INDICATION AND STATUS   | 312 |

| REGISTER 0743H: RCFP MINIMUM PACKET LENGTH             | 314 |

ISSUE 1

| REGISTER 0744H: RCFP MAXIMUM PACKET LENGTH                       | 315                      |

|------------------------------------------------------------------|--------------------------|

| REGISTER 0745H: RCFP LCD COUNT THRESHOLD                         | 316                      |

| REGISTER 0746H: RCFP IDLE CELL HEADER AND MASK                   | 317                      |

| REGISTER 0747H: RCFP RECEIVE BYTE/IDLE CELL COUNTER (LSB)        | 319                      |

| REGISTER 0748H: RCFP RECEIVE BYTE/IDLE CELL COUNTER              | 319                      |

| REGISTER 0749H: RCFP RECEIVE BYTE/IDLE CELL COUNTER (MSB)        | 319                      |

| REGISTER 074AH: RCFP PACKET/CELL COUNTER (LSB)                   | 320                      |

| REGISTER 074BH: RCFP RECEIVE PACKET/ATM CELL COUNTER (MSB)       | 320                      |

| REGISTER 074CH: RCFP RECEIVE ERRED FCS/HCS COUNTER               | 321                      |

| REGISTER 074DH: RCFP RECEIVE ABORTED PACKET COUNTER              | 322                      |

| REGISTER 074EH: RCFP RECEIVE MINIMUM LENGTH PACKET ERROR COUNTER | 323                      |

| REGISTER 074FH: RCFP RECEIVE MAXIMUM LENGTH PACKET ERROR COUNTER | 324                      |

| REGISTER 0750H: TCFP CONFIGURATION                               | 325                      |

| REGISTER 0751H: TCFP INTERRUPT INDICATION                        | 328                      |

| REGISTER 0752H: TCFP IDLE/UNASSIGNED ATM CELL HEADER             | 329                      |

| REGISTER 0753H: TCFP DIAGNOSTICS                                 | 331                      |

|                                                                  |                          |

| REGISTER 0754H: TCFP TRANSMIT CELL/PACKET COUNTER (LSB)          | 333                      |

| REGISTER 0754H: TCFP TRANSMIT CELL/PACKET COUNTER (LSB)          |                          |

| · · ·                                                            | 333                      |

| REGISTER 0755H: TCFP TRANSMIT CELL/PACKET COUNTER (MSB)          | 333                      |

| REGISTER 0755H: TCFP TRANSMIT CELL/PACKET COUNTER (MSB)          | 333<br>334               |

| REGISTER 0755H: TCFP TRANSMIT CELL/PACKET COUNTER (MSB)          | 333<br>334<br>334        |

| REGISTER 0755H: TCFP TRANSMIT CELL/PACKET COUNTER (MSB)          | 333<br>334<br>334<br>335 |

ISSUE 1

| REGISTER 0763H: RXSDQ FIFO OVERFLOW PORT AND INTERRUPT INDICATION          | 338 |

|----------------------------------------------------------------------------|-----|

| REGISTER 0764H: RXSDQ FIFO SOP ERROR PORT AND INTERRUPT INDICATION         | 339 |

| REGISTER 0765H: RXSDQ FIFO EOP ERROR PORT AND INTERRUPT INDICATION         | 340 |

| REGISTER 0768H: RXSDQ FIFO INDIRECT ADDRESS                                | 341 |

| REGISTER 0769H: RXSDQ FIFO INDIRECT CONFIGURATION                          | 343 |

| REGISTER 076AH: RXSDQ FIFO INDIRECT DATA AVAILABLE THRESHOLD               | 345 |

| REGISTER 076BH: RXSDQ FIFO INDIRECT CELLS AND PACKETS COUNT                | 346 |

| REGISTER 076CH: RXSDQ FIFO CELLS AND PACKETS ACCEPTED AGGREGATE COUNT (LSE | •   |

| REGISTER 076DH: RXSDQ FIFO CELLS AND PACKETS ACCEPTED AGGREGATE COUNT (MSI | В)  |

| REGISTER 076EH: RXSDQ FIFO CELLS AND PACKETS DROPPED AGGREGATE COUNT       |     |

| REGISTER 0770H: TXSDQ FIFO RESET                                           | 349 |

| REGISTER 0771H: TXSDQ FIFO INTERRUPT ENABLE                                | 350 |

| REGISTER 0773H: TXSDQ FIFO OVERFLOW PORT AND INTERRUPT INDICATION          | 351 |

| REGISTER 0774H: TXSDQ FIFO SOP ERROR PORT AND INTERRUPT INDICATION         | 352 |

| REGISTER 0775H: TXSDQ FIFO EOP ERROR PORT AND INTERRUPT INDICATION         | 353 |

| REGISTER 0778H: TXSDQ FIFO INDIRECT ADDRESS                                | 354 |

| REGISTER 0779H: TXSDQ FIFO INDIRECT CONFIGURATION                          | 356 |

| REGISTER 077AH: TXSDQ FIFO INDIRECT DATA AND BUFFER AVAILABLE THRESHOLDS   | 358 |

| REGISTER 077BH: TXSDQ FIFO INDIRECT CELLS AND PACKETS COUNT                | 360 |

| REGISTER 077CH: TXSDQ FIFO CELLS AND PACKETS ACCEPTED AGGREGATE COUNT (LSB | •   |

| REGISTER 077DH: TXSDQ FIFO CELLS AND PACKETS ACCEPTED AGGREGATE COUNT (MSE | •   |

| REGISTER 077EH: TXSDQ FIFO CELLS AND PACKETS DROPPED AGGREGATE COUNT       | 362 |

ISSUE 1

| REGISTER 0780H: RXPHY CONFIGURATION                        | 363 |

|------------------------------------------------------------|-----|

| REGISTER 0781H: RXPHY INTERRUPT STATUS                     | 364 |

| REGISTER 0782H: RXPHY INTERRUPT ENABLE                     | 365 |

| REGISTER 0783H: RXPHY INDIRECT BURST SIZE                  | 366 |

| REGISTER 0784H: RXPHY CALENDAR LENGTH                      | 368 |

| REGISTER 0785H: RXPHY CALENDAR INDIRECT ADDRESS DATA       | 369 |

| REGISTER 0786H: RXPHY DATA TYPE FIELD                      | 371 |

| REGISTER 0788H: TXPHY CONFIGURATION                        | 372 |

| REGISTER 0789H: TXPHY INTERRUPT STATUS                     | 374 |

| REGISTER 078AH: TXPHY INTERRUPT ENABLE                     | 375 |

| REGISTER 078BH: TXPHY DATA TYPE FIELD                      | 376 |

| REGISTER 0790H: SIRP CONFIGURATION TIMESLOT                | 377 |

| REGISTER 079CH: SIRP CONFIGURATION                         | 380 |

| REGISTER 0800H: PRGM INDIRECT ADDRESS                      | 382 |

| REGISTER 0810H: PRGM AUX 2 INDIRECT ADDRESS                | 382 |

| REGISTER 0820H: PRGM AUX 3 INDIRECT ADDRESS                | 382 |

| REGISTER 0830H: PRGM AUX 4 INDIRECT ADDRESS                | 382 |

| REGISTER 0801H: PRGM INDIRECT DATA                         | 384 |

| REGISTER 0811H: PRGM AUX 2 INDIRECT DATA                   | 384 |

| REGISTER 0821H: PRGM AUX 3 INDIRECT DATA                   | 384 |

| REGISTER 0831H: PRGM AUX 4 INDIRECT DATA                   | 384 |

| REGISTER 0802H: PRGM GENERATOR PAYLOAD CONFIGURATION       | 385 |

| REGISTER 0812H: PRGM AUX 2 GENERATOR PAYLOAD CONFIGURATION | 385 |

| REGISTER 0822H: PRGM AUX 3 GENERATOR PAYLOAD CONFIGURATION | 385 |

ISSUE 1

| REGISTER 0832H: PRGM AUX 4 GENERATOR PAYLOAD CONFIGURATION          | 385 |

|---------------------------------------------------------------------|-----|

| REGISTER 0803H: PRGM MONITOR PAYLOAD CONFIGURATION REGISTER         | 386 |

| REGISTER 0813H: PRGM AUX 2 MONITOR PAYLOAD CONFIGURATION            | 386 |

| REGISTER 0823H: PRGM AUX 3 MONITOR PAYLOAD CONFIGURATION            | 386 |

| REGISTER 0833H: PRGM AUX 4 MONITOR PAYLOAD CONFIGURATION            | 386 |

| REGISTER 0804H: PRGM MONITOR BYTE ERROR INTERRUPT STATUS            | 387 |

| REGISTER 0814H: PRGM AUX 2 MONITOR BYTE ERROR INTERRUPT STATUS      | 387 |

| REGISTER 0824H: PRGM AUX 3 MONITOR BYTE ERROR INTERRUPT STATUS      | 387 |

| REGISTER 0834H: PRGM AUX 4 MONITOR BYTE ERROR INTERRUPT STATUS      | 387 |

| REGISTER 0805H: PRGM MONITOR BYTE ERROR INTERRUPT ENABLE            | 388 |

| REGISTER 0815H: PRGM AUX 2 MONITOR BYTE ERROR INTERRUPT ENABLE      | 388 |

| REGISTER 0825H: PRGM AUX 3 MONITOR BYTE ERROR INTERRUPT ENABLE      | 388 |

| REGISTER 0835H: PRGM AUX 4 MONITOR BYTE ERROR INTERRUPT ENABLE      | 388 |

| REGISTER 0806H: MONITOR B1/E1 BYTES INTERRUPT STATUS                | 389 |

| REGISTER 0807H: MONITOR B1/E1 BYTES INTERRUPT ENABLE                | 390 |

| REGISTER 0808H: MONITOR B1/E1 BYTES STATUS                          | 391 |

| REGISTER 0809H: PRGM MONITOR SYNCHRONIZATION INTERRUPT STATUS       | 392 |

| REGISTER 0819H: PRGM AUX 2 MONITOR SYNCHRONIZATION INTERRUPT STATUS | 392 |

| REGISTER 0829H: PRGM AUX 3 MONITOR SYNCHRONIZATION INTERRUPT STATUS | 392 |

| REGISTER 0839H: PRGM AUX 4 MONITOR SYNCHRONIZATION INTERRUPT STATUS | 392 |

| REGISTER 080AH: PRGM MONITOR SYNCHRONIZATION INTERRUPT ENABLE       | 393 |

| REGISTER 081AH: PRGM AUX 2 MONITOR SYNCHRONIZATION INTERRUPT ENABLE | 393 |

| REGISTER 082AH: PRGM AUX 3 MONITOR SYNCHRONIZATION INTERRUPT ENABLE | 393 |

| REGISTER 083AH: PRGM AUX 4 MONITOR SYNCHRONIZATION INTERRUPT ENABLE | 393 |

ISSUE 1

| REGISTER 080BH: PRGM MONITOR SYNCHRONIZATION STATUS                  | 394 |

|----------------------------------------------------------------------|-----|

| REGISTER 081BH: PRGM AUX 2 MONITOR SYNCHRONIZATION STATUS            | 394 |

| REGISTER 082BH: PRGM AUX 3 MONITOR SYNCHRONIZATION STATUS            | 394 |

| REGISTER 083BH: PRGM AUX 4 MONITOR SYNCHRONIZATION STATUS            | 394 |

| INDIRECT REGISTER 0800H: PRGM MONITOR TIMESLOT CONFIGURATION PAGE    | 395 |

| INDIRECT REGISTER 0801H: PRGM MONITOR PRBS[22:7] ACCUMULATOR PAGE    | 397 |

| INDIRECT REGISTER 0802H: PRGM MONITOR PRBS[6:0] ACCUMULATOR PAGE     | 397 |

| INDIRECT REGISTER 0803H: PRGM MONITOR B1/E1 VALUE PAGE               | 398 |

| INDIRECT REGISTER 0804H: PRGM MONITOR ERROR COUNT PAGE               | 399 |

| INDIRECT REGISTER 0805H: PRGM MONITOR RECEIVED B1/E1 BYTES PAGE      | 400 |

| INDIRECT REGISTER 0808H: PRGM GENERATOR TIMESLOT CONFIGURATION PAGE  | 401 |

| INDIRECT REGISTER 0809H : PRGM GENERATOR PRBS[22:7] ACCUMULATOR PAGE | 403 |

| INDIRECT REGISTER 080AH: PRGM GENERATOR PRBS[6:0] ACCUMULATOR PAGE   | 403 |

| INDIRECT REGISTER 080BH: PRGM GENERATOR B1/E1 VALUE PAGE             | 404 |

| REGISTER 0840H: R8TD APS1 CONTROL AND STATUS                         | 405 |

| REGISTER 0848H: R8TD APS2 CONTROL AND STATUS                         | 405 |

| REGISTER 0850H: R8TD APS3 CONTROL AND STATUS                         | 405 |

| REGISTER 0858H: R8TD APS4 CONTROL AND STATUS                         | 405 |

| REGISTER 0841H: R8TD APS1 INTERRUPT STATUS                           | 408 |

| REGISTER 0849H: R8TD APS2 INTERRUPT STATUS                           | 408 |

| REGISTER 0851H: R8TD APS3 INTERRUPT STATUS                           | 408 |

| REGISTER 0859H: R8TD APS4 INTERRUPT STATUS                           | 408 |

| REGISTER 0842H: R8TD APS1 LINE CODE VIOLATION COUNT                  | 410 |

| REGISTER 084AH: R8TD APS2 LINE CODE VIOLATION COUNT                  | 410 |

ISSUE 1

| REGISTER 0852H: R8TD APS3 LINE CODE VIOLATION COUNT | 410 |

|-----------------------------------------------------|-----|

| REGISTER 085AH: R8TD APS4 LINE CODE VIOLATION COUNT | 410 |

| REGISTER 0843H: R8TD APS1 ANALOG CONTROL 1          | 411 |

| REGISTER 084BH: R8TD APS2 ANALOG CONTROL 1          | 411 |

| REGISTER 0853H: R8TD APS3 ANALOG CONTROL 1          | 411 |

| REGISTER 085BH: R8TD APS4 ANALOG CONTROL 1          | 411 |

| REGISTER 0844H: R8TD APS1 ANALOG CONTROL 2          | 412 |

| REGISTER 084CH: R8TD APS2 ANALOG CONTROL 2          | 412 |

| REGISTER 0854H: R8TD APS3 ANALOG CONTROL 2          | 412 |

| REGISTER 085CH: R8TD APS4 ANALOG CONTROL 2          | 412 |

| REGISTER 0860H: T8TE APS1 CONTROL AND STATUS        | 413 |

| REGISTER 0868H: T8TE APS2 CONTROL AND STATUS        | 413 |

| REGISTER 0870H: T8TE APS3 CONTROL AND STATUS        | 413 |

| REGISTER 0878H: T8TE APS4 CONTROL AND STATUS        | 413 |

| REGISTER 0861H: T8TE APS1 INTERRUPT STATUS          | 415 |

| REGISTER 0869H: T8TE APS2 INTERRUPT STATUS          | 415 |

| REGISTER 0871H: T8TE APS3 INTERRUPT STATUS          | 415 |

| REGISTER 0879H: T8TE APS4 INTERRUPT STATUS          | 415 |

| REGISTER 0862H: T8TE APS1 TELECOMBUS MODE #1        | 416 |

| REGISTER 086AH: T8TE APS2 TELECOMBUS MODE #1        | 416 |

| REGISTER 0872H: T8TE APS3 TELECOMBUS MODE #1        | 416 |

| REGISTER 087AH: T8TE APS4 TELECOMBUS MODE #1        | 416 |

| REGISTER 0863H: T8TE APS1 TELECOMBUS MODE #2        | 417 |

| REGISTER 086BH: T8TE APS2 TELECOMBUS MODE #2        | 417 |

ISSUE 1

| REGISTER 0873H: T8TE APS3 TELECOMBUS MODE #2              | 417 |

|-----------------------------------------------------------|-----|

| REGISTER 087BH: T8TE APS4 TELECOMBUS MODE #2              | 417 |

| REGISTER 0864H: T8TE APS1 TEST PATTERN                    | 418 |

| REGISTER 086CH: T8TE APS2 TEST PATTERN                    | 418 |

| REGISTER 0874H: T8TE APS3 TEST PATTERN                    | 418 |

| REGISTER 087CH: T8TE APS4 TEST PATTERN                    | 418 |

| REGISTER 0865H: T8TE APS1 ANALOG CONTROL                  | 419 |

| REGISTER 086DH: T8TE APS2 ANALOG CONTROL                  | 419 |

| REGISTER 0875H: T8TE APS3 ANALOG CONTROL                  | 419 |

| REGISTER 087DH: T8TE APS4 ANALOG CONTROL                  | 419 |

| REGISTER 0866H: T8TE APS1 DTB BUS                         | 421 |

| REGISTER 086EH: T8TE APS2 DTB BUS                         | 421 |

| REGISTER 0876H: T8TE APS3 DTB BUS                         | 421 |

| REGISTER 087EH: T8TE APS4 DTB BUS                         | 421 |

| REGISTER 0880H-0883H: RFCLK DLL RESERVED                  | 422 |

| REGISTER 0884H-0887H: TFCLK DLL RESERVED                  | 423 |

| REGISTER 0888H: CSTR CONTROL                              | 424 |

| REGISTER 0889H: CSTR INTERRUPT ENABLE AND CSU LOCK STATUS | 425 |

| REGISTER 088AH: CSTR CSU LOCK INTERRUPT INDICATION        | 426 |

| REGISTER 088BH: CSTR CSU LOCK INTERRUPT INDICATION        | 427 |

| REGISTER 0890H-0897: S/UNI-2488 RX STSI RESERVED          | 428 |

| REGISTER 0898H-089F: S/UNI-2488 TX STSI RESERVED          | 429 |

ISSUE 1

### SATURN USER NETWORK INTERFACE FOR 2488 MBIT/S

### **LIST OF TABLES**

| TABLE 1: PLM-P, UNEQ-P AND PDI-P DEFECTS DECLARATION              | 60  |

|-------------------------------------------------------------------|-----|