PM7329 S/UNI-APEX-1K800

DATASHEET PMC-2010141

ISSUE 2

ATM TRAFFIC MANAGER AND SWITCH

# PM7329

S/UNI -APEX-1k800

# S/UNI-APEX-1K800

# ATM/PACKET TRAFFIC MANAGER AND SWITCH

# DATASHEET

**ISSUE 2: JUNE, 2001**

DATASHEET PMC-2010141

ISSUE 2

ATM TRAFFIC MANAGER AND SWITCH

## **REVISION HISTORY**

| Issue No. | Issue Date     | Details of Change |

|-----------|----------------|-------------------|

| Issue 1   | February, 2001 | Document created. |

| Issue 2   | June, 2001     | Document revision |

ATM TRAFFIC MANAGER AND SWITCH

#### **CONTENTS**

| <u>1</u>  | DEFI         | <u>NITIONS</u> 1                                                     |  |  |  |

|-----------|--------------|----------------------------------------------------------------------|--|--|--|

| <u>2</u>  | <u>FEAT</u>  | <u>TURES</u>                                                         |  |  |  |

| <u>3</u>  | APPLICATIONS |                                                                      |  |  |  |

| <u>4</u>  | REFE         | RENCES                                                               |  |  |  |

| <u>5</u>  | APPL         | ICATION EXAMPLES                                                     |  |  |  |

| <u>6</u>  | BLOC         | CK DIAGRAM                                                           |  |  |  |

| <u>7</u>  | DESC         | CRIPTION                                                             |  |  |  |

| <u>8</u>  | <u>PIN D</u> | <u>DIAGRAM</u>                                                       |  |  |  |

| <u>9</u>  | <u>PIN D</u> | DESCRIPTION                                                          |  |  |  |

|           | <u>9.1</u>   | LOOP ANY-PHY RECEIVE MASTER/TRANSMIT SLAVE<br>INTERFACE (28 SIGNALS) |  |  |  |

|           | <u>9.2</u>   | LOOP ANY-PHY TRANSMIT MASTER/RECEIVE SLAVE<br>INTERFACE (34 SIGNALS) |  |  |  |

|           | <u>9.3</u>   | WAN ANY-PHY RECEIVE MASTER/TRANSMIT SLAVE<br>INTERFACE (25 SIGNALS)  |  |  |  |

|           | <u>9.4</u>   | WAN ANY-PHY TRANSMIT MASTER/RECEIVE SLAVE<br>INTERFACE (25 SIGNALS)  |  |  |  |

|           | <u>9.5</u>   | CONTEXT MEMORY SYNCHRONOUS SSRAM INTERFACE (59<br>SIGNALS)           |  |  |  |

|           | <u>9.6</u>   | CELL BUFFER SDRAM INTERFACE (52 SIGNALS)                             |  |  |  |

|           | <u>9.7</u>   | MICROPROCESSOR INTERFACE (44 SIGNALS) 40                             |  |  |  |

|           | <u>9.8</u>   | GENERAL (10 SIGNALS)                                                 |  |  |  |

|           | <u>9.9</u>   | JTAG & SCAN INTERFACE (7 SIGNALS)                                    |  |  |  |

|           | <u>9.10</u>  | POWER                                                                |  |  |  |

| <u>10</u> | <u>FUNC</u>  | TIONAL DESCRIPTION                                                   |  |  |  |

| 0141      |              | ISSUE 2                                                 | ATM TRAFFIC MANAGER AND SWITCH |

|-----------|--------------|---------------------------------------------------------|--------------------------------|

|           | <u>10.1</u>  | ANY-PHY INTERFACES                                      |                                |

|           |              | 10.1.1 RECEIVE INTERFACE                                |                                |

|           |              | 10.1.2 TRANSMIT INTERFACE                               | 51                             |

|           | <u>10.2</u>  | LOOP PORT SCHEDULER                                     |                                |

|           | <u>10.3</u>  | WAN PORT SCHEDULER                                      |                                |

|           | <u>10.4</u>  | WAN PORT ALIASING                                       |                                |

|           | <u>10.5</u>  | WAN AND LOOP ICI SELECTION                              |                                |

|           | <u>10.6</u>  | MICROPROCESSOR INTERFACE                                |                                |

|           | <u>10.7</u>  | MEMORY PORT                                             |                                |

|           | <u>10.8</u>  | SAR ASSIST                                              | 63                             |

|           |              | 10.8.1 TRANSMIT                                         | 63                             |

|           |              | 10.8.2 RECEIVE                                          | 64                             |

|           | <u>10.9</u>  | QUEUE ENGINE                                            |                                |

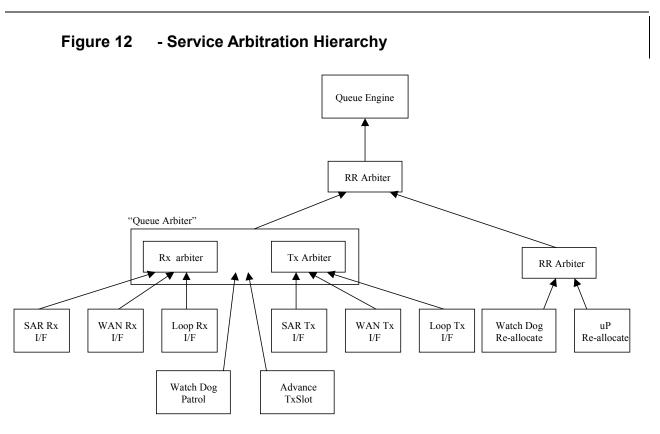

|           |              | 10.9.1 SERVICE ARBITRATION                              |                                |

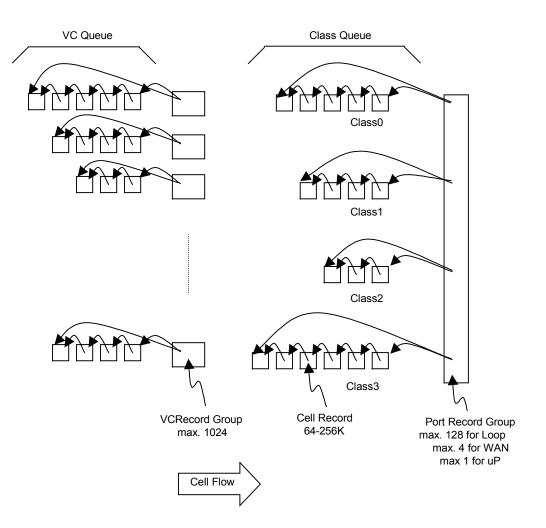

|           |              | 10.9.2 CELL QUEUING                                     |                                |

|           |              | 10.9.3 CLASS SCHEDULING                                 | 74                             |

|           |              | 10.9.4 CONGESTION CONTROL                               |                                |

|           |              | 10.9.5 STATISTICS                                       |                                |

|           |              | 10.9.6 MICROPROCESSOR QUEUE BUF<br>ALLOCATION/TEAR DOWN | <u>FER RE-</u><br>85           |

|           | <u>10.10</u> | CONTEXT MEMORY SSRAM INTERFACE                          |                                |

|           | <u>10.11</u> | CELL BUFFER SDRAM INTERFACE                             |                                |

|           | <u>10.12</u> | JTAG TEST ACCESS PORT                                   |                                |

| <u>11</u> | PERF         | ORMANCE                                                 |                                |

|           | <u>11.1</u>  | THROUGHPUT                                              |                                |

# PMC PMC-Sierra

ISSUE 2

|                        | <u>11.2</u>  | LATENCY                              | 3 |

|------------------------|--------------|--------------------------------------|---|

|                        | <u>11.3</u>  | <u>CDV</u>                           | 3 |

| <u>12</u>              | <u>REGI</u>  | <u>STER</u>                          | 7 |

|                        | <u>12.1</u>  | GENERAL CONFIGURATION AND STATUS     | 3 |

|                        | <u>12.2</u>  | LOOP CELL INTERFACE                  | 7 |

|                        | <u>12.3</u>  | WAN CELL INTERFACE                   | 3 |

|                        | <u>12.4</u>  | MEMORY PORT                          | Э |

|                        | <u>12.5</u>  | <u>SAR</u>                           | 5 |

|                        |              | <u>12.5.1 RECEIVE</u>                | 5 |

|                        |              | <u>12.5.2 TRANSMIT</u>               | 7 |

|                        |              | 12.5.3 CELL BUFFER DIAGNOSTIC ACCESS | 3 |

|                        | <u>12.6</u>  | QUEUE ENGINE                         | Э |

|                        | <u>12.7</u>  | MEMORY INTERFACE                     | 1 |

|                        | <u>12.8</u>  | CBI INTERFACE                        | 5 |

| <u>13</u>              | <u>CBI F</u> | REGISTER PORT MAPPING                | 7 |

| 14 MEMORY PORT MAPPING |              |                                      | 3 |

|                        | <u>14.1</u>  | CONTEXT SIZE AND LOCATION            | 3 |

|                        | <u>14.2</u>  | QUEUE CONTEXT DEFINITION             | 3 |

|                        |              | 14.2.1 VC CONTEXT RECORDS            | 7 |

|                        |              | 14.2.2 PORT CONTEXT RECORDS          | 5 |

|                        |              | 14.2.3 CLASS CONTEXT RECORDS         | Э |

|                        |              | 14.2.4 SHAPING CONTEXT RECORDS       | 1 |

|                        |              | 14.2.5 CELL CONTEXT RECORD           | 3 |

|                        |              | <u>14.2.6 MISC CONTEXT</u>           | 3 |

# PMC-Sierra

| DATASHEET<br>PMC-2010141 |               | ISSUE 2                         | ATM TRAFFIC MANAGER AND SWITCH      |

|--------------------------|---------------|---------------------------------|-------------------------------------|

|                          | <u>14.3</u>   | WAN PORT SCHEDULER CO           | <u>NTEXT</u> 180                    |

|                          |               | 14.3.1 WAN TRANSMIT PORT        | <u>FPOLLING WEIGHT RECORD</u> . 180 |

|                          |               | 14.3.2 WAN TRANSMIT CLAS        | S STATUS RECORD 181                 |

|                          | <u>14.4</u>   | LOOP PORT SCHEDULER CO          | <u>ONTEXT</u> 182                   |

|                          |               | 14.4.1 LOOP TRANSMIT POR<br>182 | T POLLING SEQUENCE RECORD           |

|                          |               | 14.4.2 LOOP TRANSMIT POR        | T POLLING WEIGHT RECORD 183         |

|                          |               | 14.4.3 LOOP TRANSMIT CLA        | <u>SS STATUS RECORD</u> 184         |

| <u>15</u>                | <u>TEST</u>   | FEATURES DESCRIPTION            |                                     |

|                          | <u>15.1</u>   | JTAG TEST PORT                  |                                     |

| <u>16</u>                | <u>OPEF</u>   | ATION                           |                                     |

| <u>17</u>                | <u>FUNC</u>   | TIONAL TIMING                   |                                     |

|                          | <u>17.1</u>   | MICROPROCESSOR INTERF           | ACE 191                             |

|                          | <u>17.2</u>   | SDRAM INTERFACE                 |                                     |

|                          | <u>17.3</u>   | ZBT SSRAM INTERFACE             |                                     |

|                          | <u>17.4</u>   | LATE WRITE SSRAM INTERF         | FACE 196                            |

|                          | <u>17.5</u>   | ANY-PHY/UTOPIA INTERFAC         | <u>ES</u> 197                       |

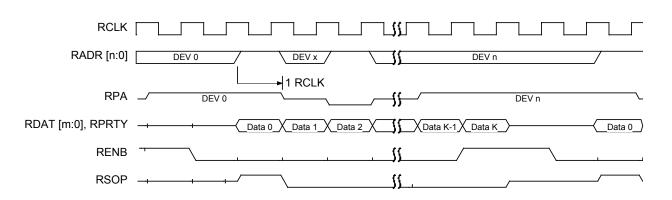

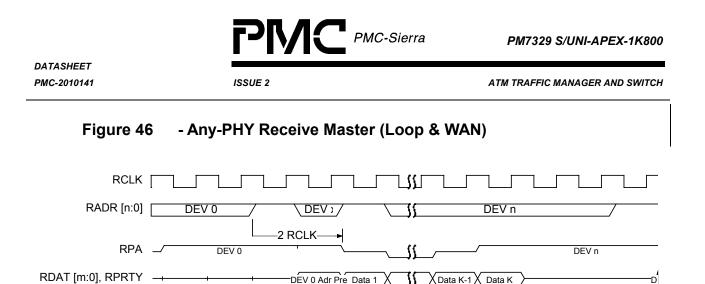

|                          |               | 17.5.1 RECEIVE MASTER/TR        | ANSMIT SLAVE INTERFACES. 197        |

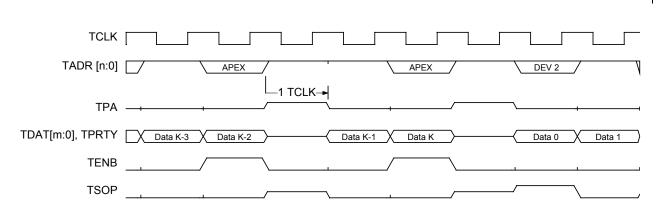

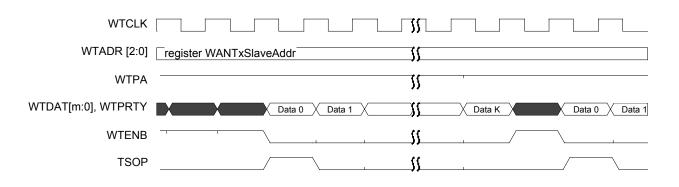

|                          |               | 17.5.2 TRANSMIT MASTER/R        | ECEIVE SLAVE INTERFACES. 200        |

| <u>18</u>                | ABSC          | ULUTE MAXIMUM RATINGS           |                                     |

| <u>19</u>                | <u>D.C. (</u> | CHARACTERISTICS                 |                                     |

| <u>20</u>                | <u>A.C.</u>   | IMING CHARACTERISTICS           |                                     |

|                          | <u>20.1</u>   | JTAG INTERFACE                  |                                     |

| <u>21</u>                | ORD           | ERING AND THERMAL INFORM        | <u>MATION</u>                       |

| <u>22</u>                | MECH          | HANICAL INFORMATION             |                                     |

ATM TRAFFIC MANAGER AND SWITCH

#### LIST OF REGISTERS

| REGISTER 0X00: RESET AND IDENTITY                              | } |

|----------------------------------------------------------------|---|

| REGISTER 0X10: HI PRIORITY INTERRUPT STATUS REGISTER 99        | ) |

| REGISTER 0X14: HIGH PRIORITY INTERRUPT MASK                    | l |

| REGISTER 0X18: LOW PRIORITY INTERRUPT ERROR REGISTER 102       | 2 |

| REGISTER 0X1C: LOW PRIORITY INTERRUPT ERROR MASK               | ł |

| REGISTER 0X20: LOW PRIORITY INTERRUPT STATUS REGISTER 105      | 5 |

| REGISTER 0X24: LOW PRIORITY INTERRUPT STATUS MASK              | 3 |

| REGISTER 0X100: LOOP CELL RX INTERFACE CONFIGURATION           | , |

| REGISTER 0X104: LOOP CELL TX INTERFACE CONFIGURATION           | ) |

| REGISTER 0X200: WAN CELL RX INTERFACE CONFIGURATION            | 3 |

| REGISTER 0X204: WAN CELL TX INTERFACE CONFIGURATION            | 3 |

| REGISTER 0X300: MEMORY PORT CONTROL                            | ) |

| REGISTER 0X340-0X34C: MEMORY WRITE DATA (BURSTABLE) 121        | l |

| REGISTER 0X350: MEMORY WRITE DATA OVERFLOW (BURSTABLE) 122     | 2 |

| REGISTER 0X380-0X38C: MEMORY READ DATA (BURSTABLE) 123         | 3 |

| REGISTER 0X390: MEMORY READ DATA OVERFLOW (BURSTABLE) 124      | ł |

| REGISTER 0X400-0X43C: SAR RECEIVE DATA (BURSTABLE)             | 5 |

| REGISTER 0X500-0X53C: SAR TRANSMIT DATA, CLASS 0 (BURSTABLE)12 | 7 |

| REGISTER 0X540-0X57C: SAR TRANSMIT DATA, CLASS 1 (BURSTABLE)12 | 7 |

| REGISTER 0X580-0X5BC: SAR TRANSMIT DATA, CLASS 2 (BURSTABLE)12 | 7 |

| REGISTER 0X5C0-0X5FC: SAR TRANSMIT DATA, CLASS 3 (BURSTABLE)12 | 7 |

| REGISTER 0X600: CELL BUFFER DIAGNOSTIC CONTROL                 | 3 |

| REGISTER 0X700: QUEUE CONTEXT CONFIGURATION 129          | ) |

|----------------------------------------------------------|---|

| REGISTER 0X704: RECEIVE AND TRANSMIT CONTROL 132         | ) |

| REGISTER 0X710: MAX DIRECTION CONGESTION THRESHOLDS 134  |   |

| REGISTER 0X714: CLP0 DIRECTION CONGESTION THRESHOLDS 135 | ; |

| REGISTER 0X718: CLP1 DIRECTION CONGESTION THRESHOLDS 136 | ) |

| REGISTER 0X71C: RE-ASSEMBLY MAXIMUM LENGTH               | , |

| REGISTER 0X720: WATCH DOG ICI PATROL RANGE               | ; |

| REGISTER 0X724: TEAR DOWN QUEUE ID                       | ) |

| REGISTER 0X728: WATCH DOG / TEAR DOWN STATUS 140         | ) |

| REGISTER 0X730: SHAPER 0 CONFIGURATION (N = 0)           |   |

| REGISTER 0X734: SHAPER 1 CONFIGURATION (N = 1) 141       |   |

| REGISTER 0X738: SHAPER 2 CONFIGURATION (N = 2) 141       |   |

| REGISTER 0X73C: SHAPER 3 CONFIGURATION (N = 3) 141       |   |

| REGISTER 0X800: SDRAM/SSRAM CONFIGURATION                |   |

| REGISTER 0XA00: CBI REGISTER PORT                        | ; |

| CBI REGISTER 0X00: CONFIGURATION                         | , |

| CBI REGISTER 0X01: VERNIER CONTROL                       | ) |

| CBI REGISTER 0X02: DELAY TAP STATUS                      | ) |

| CBI REGISTER 0X03: CONTROL STATUS                        |   |

|                                                          |   |

#### LIST OF FIGURES

| FIGURE 1 - S/UNI-APEX-1K800 IN OC3 MINI-DSLAM APPLICATION     |

|---------------------------------------------------------------|

| FIGURE 2 - S/UNI-APEX-1K800 BLOCK DIAGRAM WITH DATAPATH       |

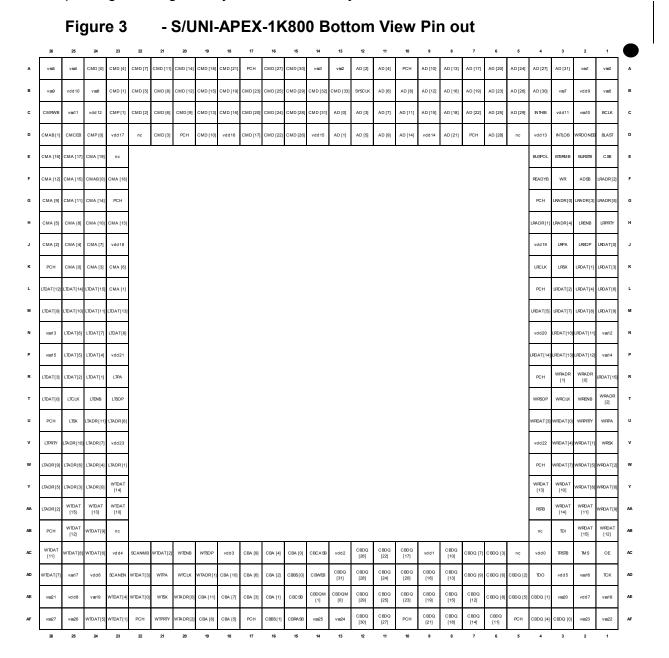

| FIGURE 3 - S/UNI-APEX-1K800 BOTTOM VIEW PIN OUT               |

| FIGURE 4 - 16BIT RECEIVE CELL TRANSFER FORMAT                 |

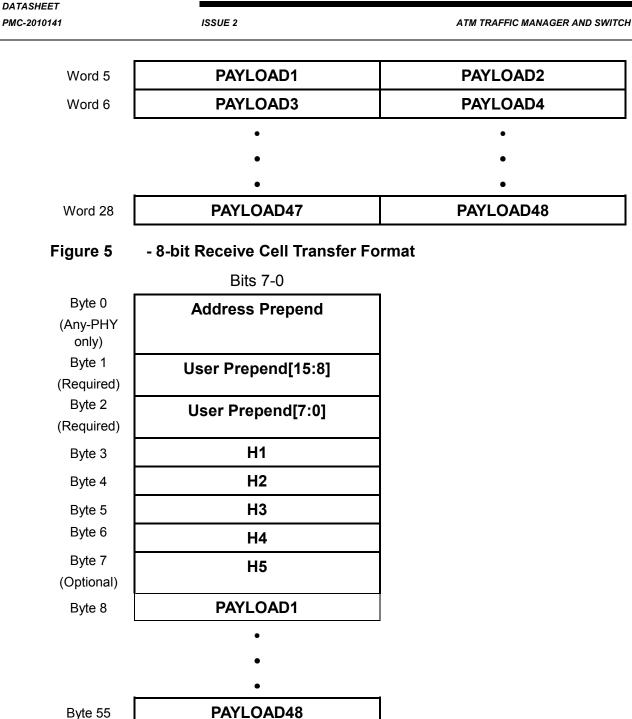

| FIGURE 5 - 8-BIT RECEIVE CELL TRANSFER FORMAT                 |

| FIGURE 6 - 16-BIT TRANSMIT CELL TRANSFER FORMAT               |

| FIGURE 7 - 8-BIT TRANSMIT CELL TRANSFER FORMAT                |

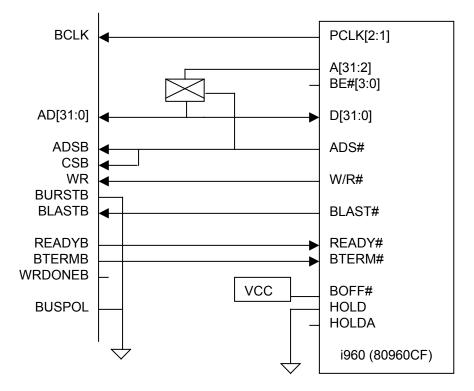

| FIGURE 8 - 1960 (80960CF) INTERFACE 61                        |

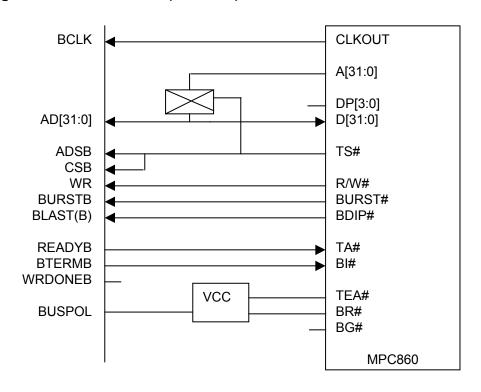

| FIGURE 9 - POWERPC (MPC860) INTERFACE                         |

| FIGURE 10- SAR ASSIST TRANSMIT CELL TRANSFER FORMAT 64        |

| FIGURE 11 - SAR ASSIST RECEIVE CELL TRANSFER FORMAT           |

| FIGURE 12- SERVICE ARBITRATION HIERARCHY 67                   |

| FIGURE 13- QUEUE LINKED LIST STRUCTURE                        |

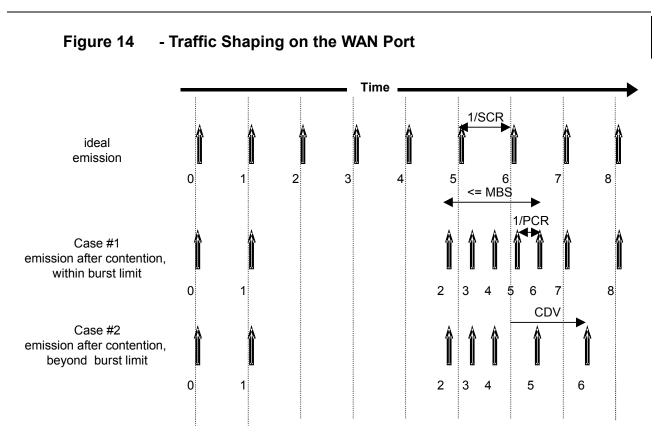

| FIGURE 14- TRAFFIC SHAPING ON THE WAN PORT                    |

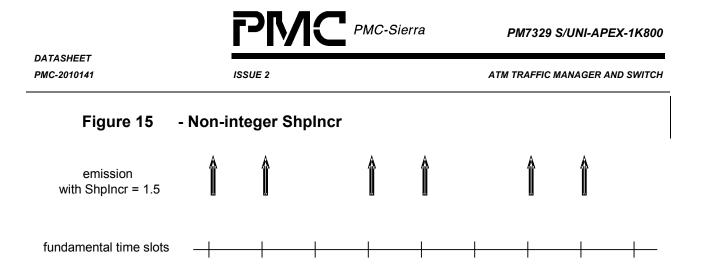

| FIGURE 15- NON-INTEGER SHPINCR                                |

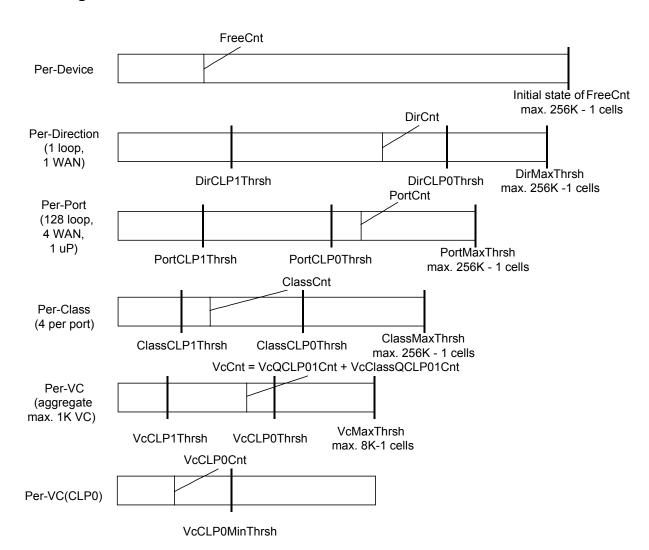

| FIGURE 16- THRESHOLDS AND COUNT DEFINITIONS                   |

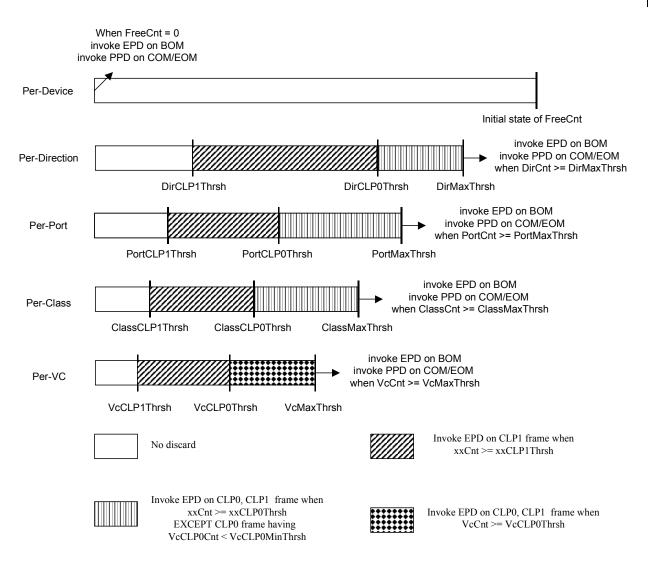

| FIGURE 17- EPD/PPD CONGESTION DISCARD RULES                   |

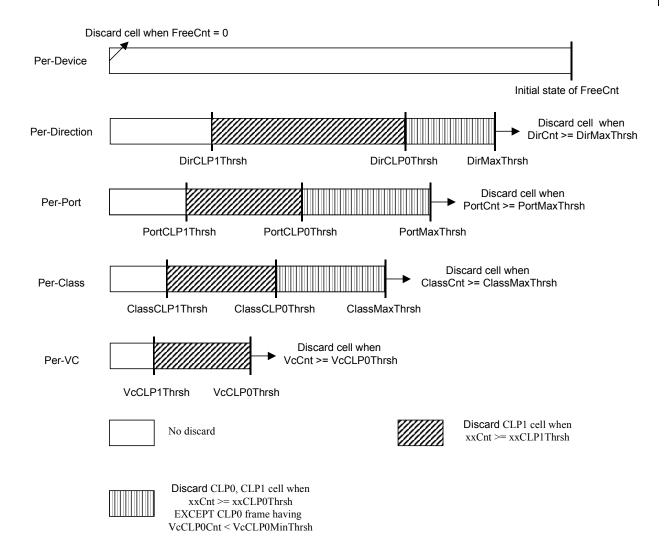

| FIGURE 18 - CELL CONGESTION DISCARD RULES                     |

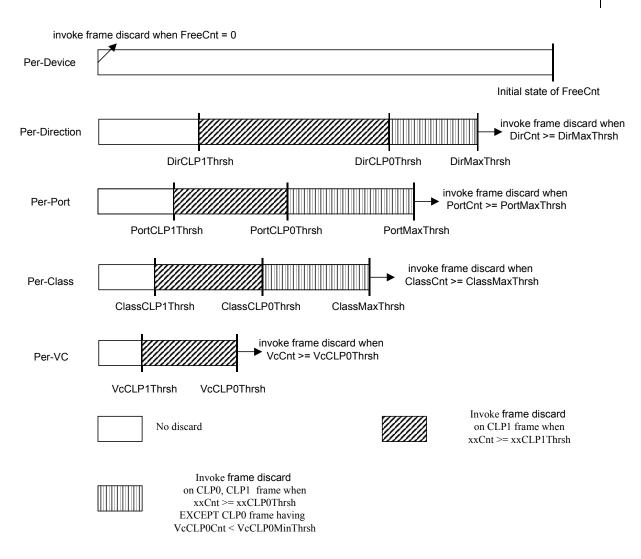

| FIGURE 19 - FCQ DISCARD RULES                                 |

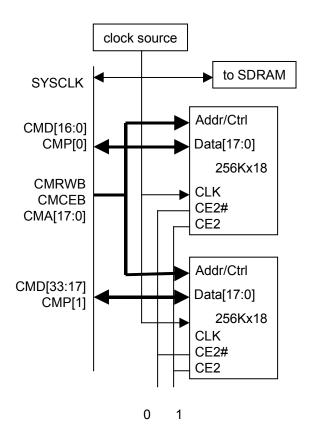

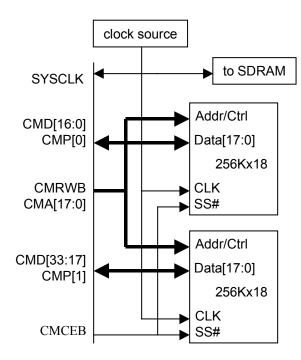

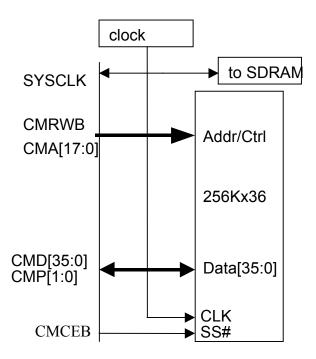

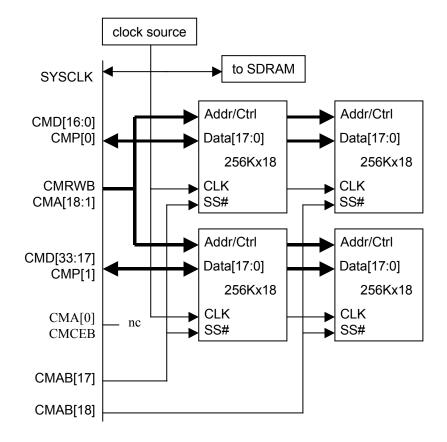

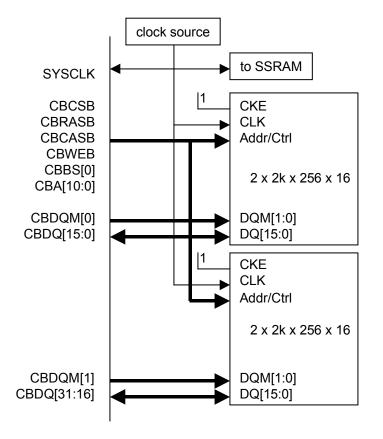

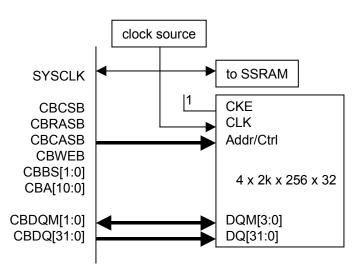

| FIGURE 20- 1 BANK CONFIGURATION FOR 1MB OF ZBT SSRAM          |

| FIGURE 21- 1 BANK OF 1MB OF LATE WRITE SSRAM (2 X 256K*18) 87 |

| FIGURE 22- 1 BANK OF 1MB OF LATE WRITE SSRAM (1 X 256K*36) 87 |

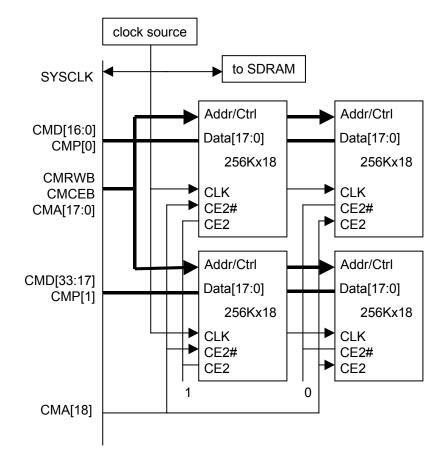

| FIGURE 23-2 BANK CONFIGURATION FOR 2MB OF ZBT SSRAM            |

|----------------------------------------------------------------|

| FIGURE 24-2 BANK CONFIGURATION FOR 2MB OF LATE WRITE SSRAM89   |

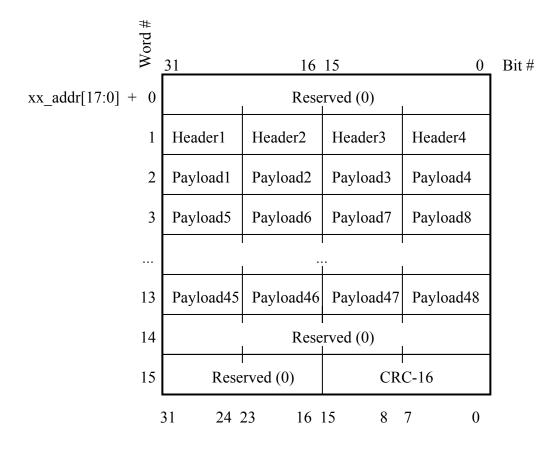

| FIGURE 25- CELL STORAGE MAP                                    |

| <u>FIGURE 26- 4 MB – 64K CELLS</u>                             |

| <u>FIGURE 27- 8 MB – 128K CELLS</u> 91                         |

| <u>FIGURE 28- 16 MB – 256K CELLS</u>                           |

| FIGURE 29- CONTEXT LOCATION                                    |

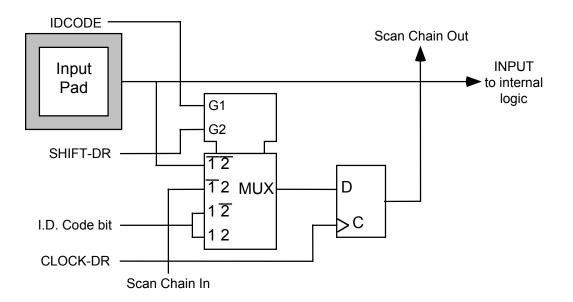

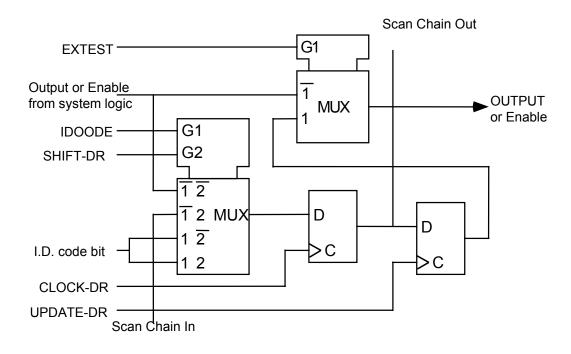

| FIGURE 30- INPUT OBSERVATION CELL (IN_CELL) 187                |

| FIGURE 31- OUTPUT CELL (OUT_CELL)                              |

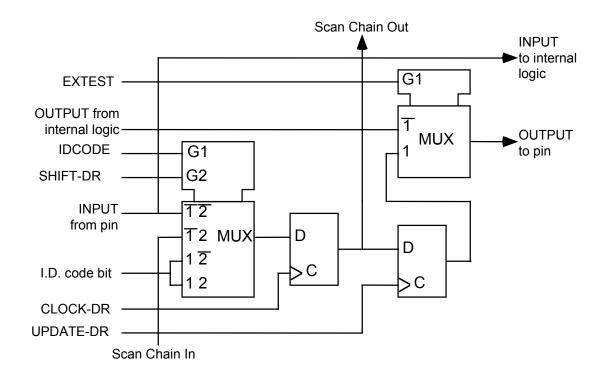

| FIGURE 32- BI-DIRECTIONAL CELL (IO_CELL)                       |

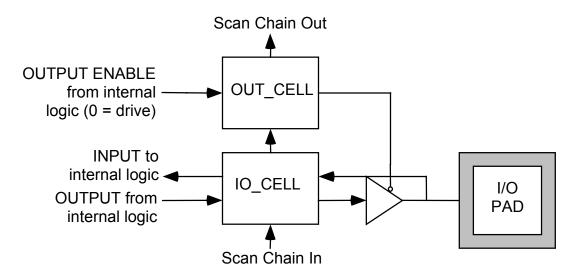

| FIGURE 33- LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS 189 |

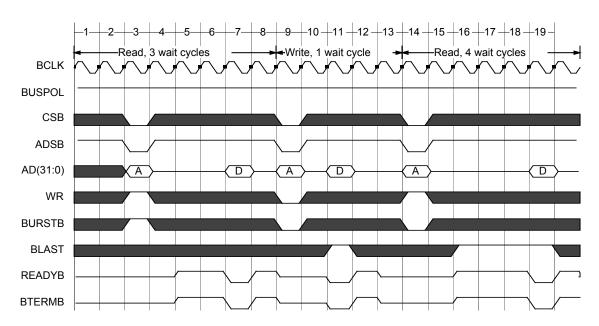

| FIGURE 34- SINGLE WORD READ AND WRITE 191                      |

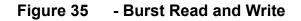

| FIGURE 35- BURST READ AND WRITE                                |

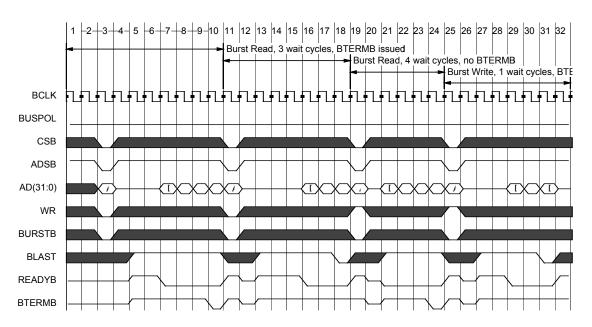

| FIGURE 36- CONSECUTIVE WRITE ACCESSES USING WRDONEB 193        |

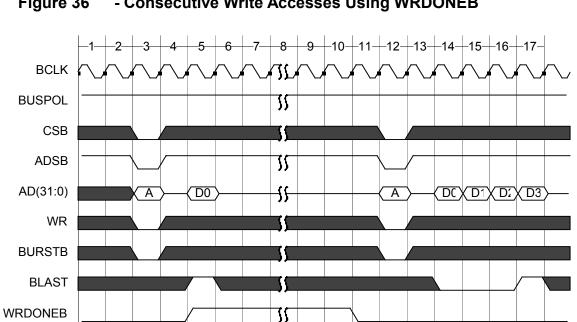

| FIGURE 37- READ TIMING 194                                     |

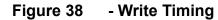

| FIGURE <u>38- WRITE TIMING</u>                                 |

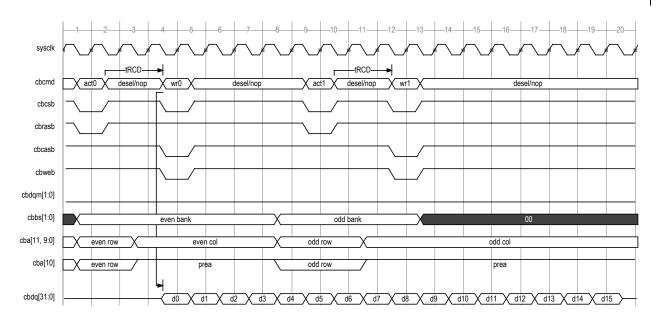

| FIGURE 39- REFRESH                                             |

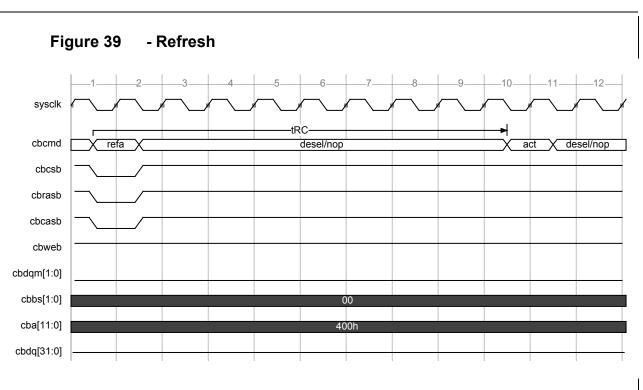

| FIGURE 40- POWER UP AND INITIALIZATION SEQUENCE                |

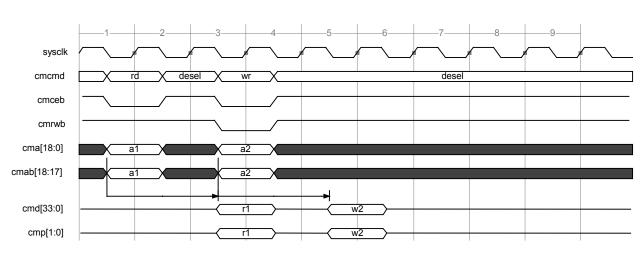

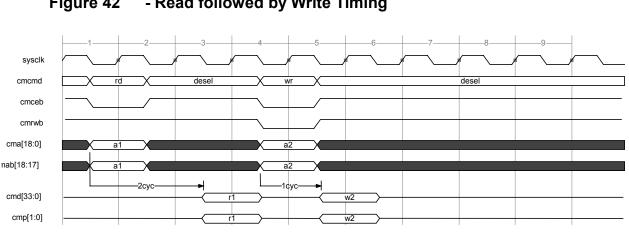

| FIGURE 41- READ FOLLOWED BY WRITE TIMING 196                   |

| FIGURE 42- READ FOLLOWED BY WRITE TIMING 197                   |

| FIGURE 43- UTOPIA L2 TRANSMIT SLAVE (LOOP & WAN) 198           |

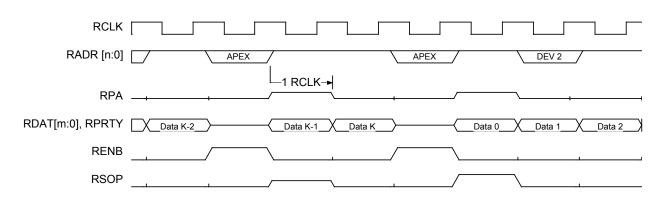

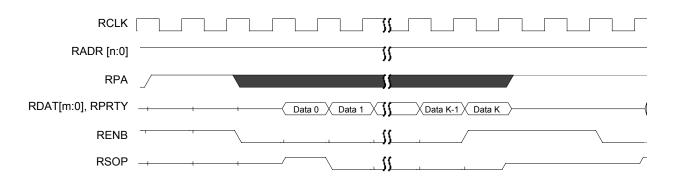

| FIGURE 44- UTOPIA L1 RECEIVE MASTER (LOOP & WAN) 198           |

| FIGURE 45- UTOPIA L2 RECEIVE MASTER (LOOP & WAN) 199           |

| FIGURE 46- ANY-PHY RECEIVE MASTER (LOOP & WAN) 200             |

| FIGURE 47- UTOPIA L2 RECEIVE SLAVE (LOOP & WAN)                 |  |

|-----------------------------------------------------------------|--|

| FIGURE 48- WAN UTOPIA L1 TRANSMIT MASTER 201                    |  |

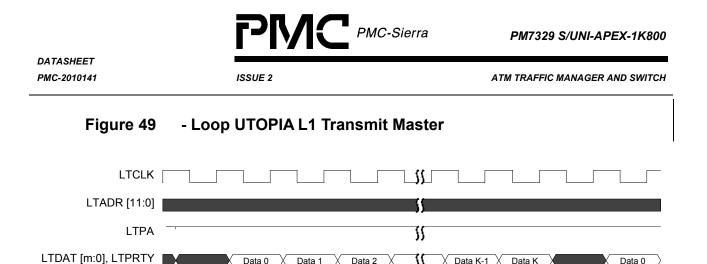

| FIGURE 49- LOOP UTOPIA L1 TRANSMIT MASTER                       |  |

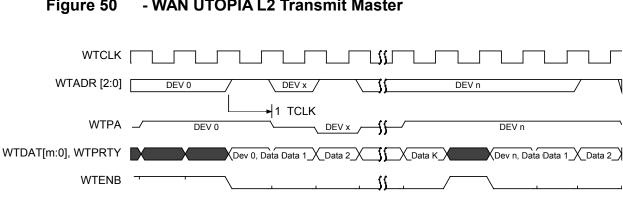

| FIGURE 50- WAN UTOPIA L2 TRANSMIT MASTER                        |  |

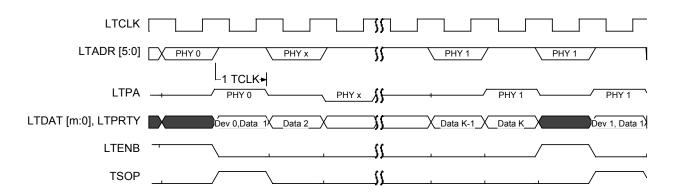

| FIGURE 51- LOOP UTOPIA L2 TRANSMIT MASTER                       |  |

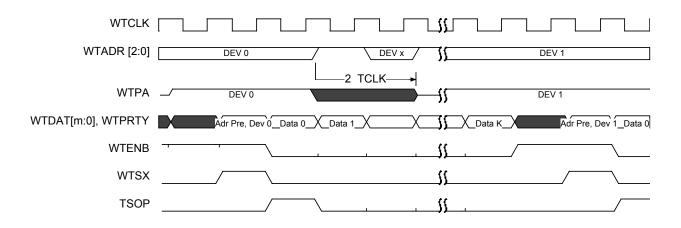

| FIGURE 52- WAN ANY-PHY TRANSMIT MASTER                          |  |

| FIGURE 53- LOOP ANY-PHY TRANSMIT MASTER                         |  |

| FIGURE 54- RSTB TIMING                                          |  |

| FIGURE 55- SYNCHRONOUS I/O TIMING                               |  |

| FIGURE 56- JTAG PORT INTERFACE TIMING                           |  |

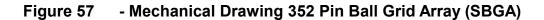

| FIGURE 57- MECHANICAL DRAWING 352 PIN BALL GRID ARRAY (SBGA)216 |  |

ATM TRAFFIC MANAGER AND SWITCH

## LIST OF TABLES

| TABLE 1  | - TERMINOLOGY 1                                          |

|----------|----------------------------------------------------------|

| TABLE 2  | - SAMPLE FEATURE SET AS A FUNCTION OF MEMORY<br>CAPACITY |

| TABLE 3  | - PIN TYPE DEFINITION 17                                 |

| TABLE 4  | - NUMBER OF PORTS SUPPORTED, RECEIVE INTERFACE 51        |

| TABLE 5  | - NUMBER OF PORTS SUPPORTED, TRANSMIT INTERFACE 54       |

| TABLE 6  | - EXAMPLE WIRR TRANSMISSION SEQUENCE                     |

| TABLE 7  | - AVAILABLE QUEUING PROCEDURES 69                        |

| TABLE 8  | - OAM & RRM CELL IDENTIFICATION                          |

| TABLE 9  | - CONGESTION ERROR FLAGS                                 |

| TABLE 10 | - CONGESTION DISCARD RULES SELECTION                     |

| TABLE 11 | - STATISTICAL COUNTS                                     |

| TABLE 12 | - IN/OUT BOUND CLP STATE FOR STATISTICAL COUNTS 84       |

| TABLE 13 | - CONGESTION RULE & COUNT SUMMARY 84                     |

| TABLE 14 | - RECEIVE INTERFACE THROUGHPUT, MCELLS/SEC               |

| TABLE 15 | - QUEUE ENGINE THROUGHPUT, MCELLS/SEC                    |

| TABLE 16 | - TRANSMIT INTERFACE THROUGHPUT, MCELLS/SEC              |

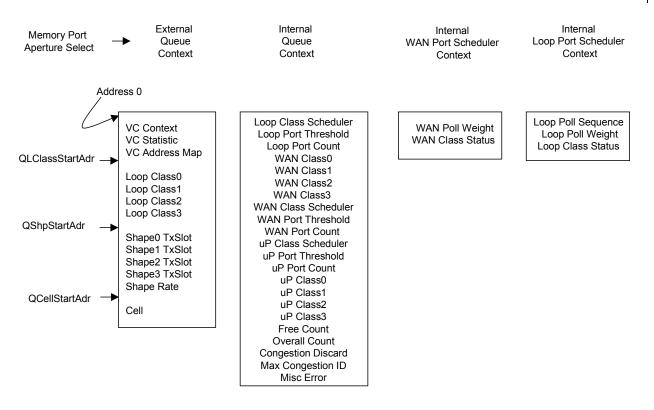

| TABLE 17 | - EXTERNAL QUEUE CONTEXT MEMORY MAP 154                  |

| TABLE 18 | - INTERNAL QUEUE CONTEXT MEMORY MAP 154                  |

| TABLE 19 | - INTERNAL WAN PORT SCHEDULER CONTEXT MEMORY MAP<br>155  |

| TABLE 20 | - INTERNAL LOOP PORT SCHEDULER CONTEXT MEMORY MAP<br>155 |

| TABLE 21 | - 2 BIT LOGARITHMIC, 2 BIT FRACTIONAL 156                |

| TABLE 22    - 4 BIT LOGARITHMIC, 2 BIT FRACTIONAL         |  |

|-----------------------------------------------------------|--|

| TABLE 23       - 4 BIT LOGARITHMIC, 4 BIT FRACTIONAL      |  |

| TABLE 24       - VC CONTEXT RECORD STRUCTURE              |  |

| TABLE 25       - VC STATISTICS RECORD STRUCTURE       163 |  |

| TABLE 26       - VC ADDRESS MAP RECORD STRUCTURE          |  |

| TABLE 27       - PORT THRESHOLD CONTEXT RECORD STRUCTURE  |  |

| TABLE 28 - PORT COUNT CONTEXT RECORD STRUCTURE            |  |

| TABLE 29       - CLASS SCHEDULER RECORD STRUCTURE         |  |

| TABLE 30       - CLASS CONTEXT RECORD STRUCTURE       172 |  |

| TABLE 31       - SHAPE TXSLOT CONTEXT RECORD STRUCTURE    |  |

| TABLE 32       - SHAPE RATE CONTEXT RECORD STRUCTURE      |  |

| TABLE 33 - CELL CONTEXT RECORD STRUCTURE       176        |  |

| TABLE 34 - FREE COUNT CONTEXT STRUCTURE    177            |  |

| TABLE 35       - OVERALL COUNT CONTEXT STRUCTURE          |  |

| TABLE 36       - CONGESTION DISCARD CONTEXT STRUCTURE     |  |

| TABLE 37       - MAXIMUM CONGESTION ID CONTEXT STRUCTURE  |  |

| TABLE 38 - MISC ERROR CONTEXT STRUCTURE       179         |  |

| TABLE 39 - WAN TRANSMIT PORT POLLING WEIGHT               |  |

| TABLE 40    - WAN POLL WEIGHT FORMAT    181               |  |

| TABLE 41 - WAN CLASS STATUS    181                        |  |

| TABLE 42       - LOOP TRANSMIT PORT POLLING SEQUENCE      |  |

| TABLE 43       - LOOP TRANSMIT PORT POLLING WEIGHT        |  |

| TABLE 44    - LOOP CLASS STATUS    184                    |  |

| TABLE 45 - INSTRUCTION REGISTER                           |  |

| TABLE 46 | - IDENTIFICATION REGISTER 186                         |  |

|----------|-------------------------------------------------------|--|

| TABLE 47 | - BOUNDARY SCAN REGISTER 186                          |  |

| TABLE 48 | - ABSOLUTE MAXIMUM RATINGS                            |  |

| TABLE 49 | - D.C. CHARACTERISTICS                                |  |

| TABLE 50 | - RTSB TIMING 208                                     |  |

| TABLE 51 | - SYSCLK TIMING                                       |  |

| TABLE 52 | - CELL BUFFER SDRAM INTERFACE                         |  |

| TABLE 53 | - CONTEXT MEMORY ZBT & LATE WRITE SSRAM INTERFACE 209 |  |

| TABLE 54 | - MICROPROCESSOR INTERFACE                            |  |

| TABLE 55 | - LOOP ANY-PHY TRANSMIT INTERFACE                     |  |

| TABLE 56 | - WAN ANY-PHY TRANSMIT INTERFACE                      |  |

| TABLE 57 | - LOOP ANY-PHY RECEIVE INTERFACE                      |  |

| TABLE 58 | - WAN ANY-PHY RECEIVE INTERFACE                       |  |

| TABLE 59 | - JTAG PORT INTERFACE                                 |  |

ISSUE 2

- Terminology

ATM TRAFFIC MANAGER AND SWITCH

#### 1 DEFINITIONS

Table 1

| Term    | Definition                                                           |  |  |  |  |

|---------|----------------------------------------------------------------------|--|--|--|--|

| AAL5    | ATM Adaptation Layer                                                 |  |  |  |  |

| ABR     | Available Bit Rate                                                   |  |  |  |  |

| Any-PHY | Interoperable version of UTOPIA and SCI-PHY, with inband addressing. |  |  |  |  |

| ATM     | Asynchronous Transfer Mode                                           |  |  |  |  |

| BOM     | Beginning of Message                                                 |  |  |  |  |

| CBI     | Common Bus Interface                                                 |  |  |  |  |

| CBR     | Constant Bit Rate                                                    |  |  |  |  |

| CDV     | Cell Delay Variation                                                 |  |  |  |  |

| CDVT    | Cell Delay Variation Tolerance                                       |  |  |  |  |

| CES     | Circuit Emulation Service                                            |  |  |  |  |

| CLP     | Cell Loss Priority                                                   |  |  |  |  |

| СОМ     | Continuation of Message                                              |  |  |  |  |

| COS     | Class of Service                                                     |  |  |  |  |

| CTD     | Cell Transfer Delay                                                  |  |  |  |  |

| DLL     | Delay Locked Loop                                                    |  |  |  |  |

| DSL     | Digital Subscriber Loop                                              |  |  |  |  |

| DSLAM   | DSL access Multiplexer                                               |  |  |  |  |

| DUPLEX  | PMC UTOPIA deserializer                                              |  |  |  |  |

| ECI     | Egress Connection Identifier                                         |  |  |  |  |

| EFCI    | Early forward congestion indicator                                   |  |  |  |  |

| EOM     | End of Message                                                       |  |  |  |  |

| EPD     | Early Packet Discard                                                 |  |  |  |  |

| FIFO    | First-In-First-Out                                                   |  |  |  |  |

| GCRA    | Generic Cell Rate Algorithm                                          |  |  |  |  |

| GFR     | Guaranteed Frame Rate                                                |  |  |  |  |

#### PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE

ISSUE 2

| IBT         | Intrinsic Burst Tolerance                         |  |  |  |  |  |

|-------------|---------------------------------------------------|--|--|--|--|--|

| ICI         | Ingress Connection Identifier                     |  |  |  |  |  |

| MBS         | Maximum Burst Size                                |  |  |  |  |  |

| MCR         | Minimum Cell Rate                                 |  |  |  |  |  |

| OAM         | Operation, Administration and Maintenance         |  |  |  |  |  |

| PCR         | Peak Cell Rate                                    |  |  |  |  |  |

| PDU         | Packet Data Unit                                  |  |  |  |  |  |

| PHY         | Physical Layer Device                             |  |  |  |  |  |

| PPD         | Partial Packet Discard                            |  |  |  |  |  |

| PTI         | Payload Type Indicator                            |  |  |  |  |  |

| QOS         | Quality of Service                                |  |  |  |  |  |

| QRT         | PMC's traffic management device                   |  |  |  |  |  |

| QSE         | PMC's switch fabric device                        |  |  |  |  |  |

| RRM         | Reserved or Resource Management                   |  |  |  |  |  |

| SAR         | Segmentation and Re-assembly                      |  |  |  |  |  |

| SCI-PHY     | PMC-Sierra enhanced UTOPIA bus                    |  |  |  |  |  |

| SCR         | Sustained Cell Rate                               |  |  |  |  |  |

| S/UNI-ATLAS | PMC's OAM and Address Resolution device           |  |  |  |  |  |

| UBR         | Unspecified Bit Rate                              |  |  |  |  |  |

| UTOPIA      | Universal Test & Operations PHY Interface for ATM |  |  |  |  |  |

| VBR         | Variable Bit Rate                                 |  |  |  |  |  |

| VCC         | Virtual Channel Connection                        |  |  |  |  |  |

| VORTEX      | PMC UTOPIA/Any-PHY slave serializer               |  |  |  |  |  |

| VPC         | Virtual Path Connection                           |  |  |  |  |  |

| WAN         | Wide Area Network                                 |  |  |  |  |  |

| WIRR        | Weighted Interleaved Round Robin                  |  |  |  |  |  |

| WRR         | Weighted Round Robin                              |  |  |  |  |  |

| ZBT         | Zero Bus Turnaround                               |  |  |  |  |  |

ATM TRAFFIC MANAGER AND SWITCH

## 2 FEATURES

- Monolithic single chip ATM traffic manager providing VC queuing/shaping and VC, Class Of Service(COS), and Port scheduling, congestion management, and switching across 128 ports.

- Targeted at systems where many low speed ATM data ports are multiplexed onto few high speed ports.

- 869 Kcells/s non shaped throughput in full duplex.

- 1.73 Mcells/s non shaped throughput in half duplex.

- 1.42 Mcells/s shaped throughput (aggregate of the four shapers).

- Supports four WAN uplink ports, with port aliasing.

- Supports 128 loop ports. Loop port can support an uncongested rate up to 230Kcells/sec.

- Provides 4 Classes of Service per port with configurable traffic parameters enabling support for a mix of CBR, VBR, GFR, and UBR classes.

- Provides 1024 per-VC queues individually assignable to any COS in any port.

- Provides support of up to 256k cells of shared buffer.

- Provides 2 independent cell emission schedulers, 1 for the WAN ports, and 1 for the Loop ports. The schedulers have the following features: Three level hierarchical cell emission scheduling at the port, class, and VC levels.

- WAN Port Scheduling:

- Weighted Interleaved Round Robin WAN port scheduling.

- Per port Priority Fair Queued class scheduling with port independence.

- Per Class:

- Weighted Fair Queued VC scheduling with class independence or,

- Shaped Fair Queued VC scheduling applying rate based per VC shaping or,

- Frame Continuous Queued VC scheduling for VC Merge and packet re-assembly.

- Loop Port Scheduling:

- Weighted Interleaved Round Robin Loop port scheduling.

- Per port Priority Fair Queued class scheduling with port independence.

- Per Class:

- Weighted Fair Queued VC scheduling with class independence or,

- Frame Continuous Queued scheduling for VC Merge and packet re-assembly.

- Congestion Control applied per-VC, per-class, per-port and per-direction.

- Flexible, progressive hierarchical throttling of buffer consumption. Provides sharing of resources during low congestion, memory reservation during high congestion.

- Applies EPD and PPD on a per-VC, per-class, per-port, and per-direction basis with CLP differentiation, following emerging GFR standards.

- Provides EFCI marking on a per VC basis.

- Provides interrupts and indication of most recent VC/Class/Port that exceeded maximum thresholds.

- Provides flexible VPC or VCC switching selectable on a per VC basis as follows:

- Any WAN port to any WAN port.

- Any WAN port to any Loop port.

- Any Loop port to any WAN port.

- Any Loop port to any Loop port.

- Microprocessor port to any loop or WAN port.

- Any loop or WAN port to microprocessor port.

- VP Termination (in conjunction with the S/UNI-ATLAS).

- VPI or VPI/VCI header mapping.

- VC merge.

- Provides flexible signaling and control capabilities:

- Provides 4 independent uP transmit queues.

- Provides simultaneous AAL5 SAR assistance for traffic to/from the uP on up to 1024 VCs.

- Supports uP cell injection into any queue.

- Provides per VC selectable OAM cell pass through or switching to microprocessor port.

- Supports CRC10 calculation for OAM cells destined for/originating from the microprocessor.

- Diagnostic access provided to context memory and cell buffer memory via the microprocessor.

- Provides per VC CLP0/1 transmit counts.

- Provide global per CLP0/1 discard counts.

- Provides various error statistics accumulation.

- Determines the ingress connection identifier from one of several locations: the cell prepend, the VPI/VCI field, or the HEC/UDF field.

- Interface support:

- Provides a 8/16-bit Any-PHY compliant master/slave Loop side interface supporting up to 128 ports (logical PHYs).

- Provides an 8/16-bit Any-PHY compliant master/slave WAN side interface supporting up to 4 ports (PHYs).

| PMC | PMC-Sierra |

|-----|------------|

|     |            |

- Provides a 32-bit multiplexed microprocessor bus interface for signaling, control, and cell message extraction and insertion, context memory access, control and status monitoring, and configuration of the IC.

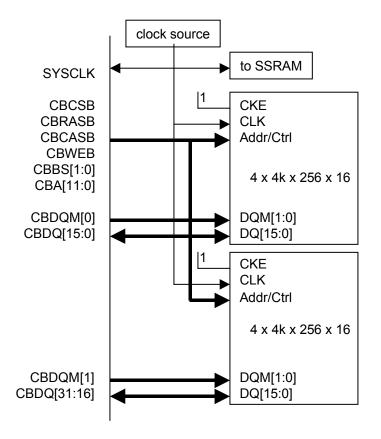

- Provides a 32-bit SDRAM interface for cell buffering.

- Provides a 36-bit pipelined ZBT or register to register late write SSRAM interface for context storage.

- Packaging:

- Provides a standard 5 signal P1149.1 JTAG test port for boundary scan board test purposes.

- Implemented in low power, 0.25 micron, +2.5/3.3V CMOS technology with CMOS compatible inputs and outputs.

- 352-pin high-performance ball grid array (SBGA) package.

ISSUE 2

ATM TRAFFIC MANAGER AND SWITCH

#### 3 APPLICATIONS

- Mini-DSL Access Multiplexers (Mini-DSLAMs).

- Subscriber Access terminal devices.

- APON Customer Located Subscriber Access Equipment

- LMDS Customer Located Subscriber Access Equipment.

- Integrated Access Devices.

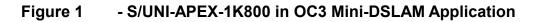

Figure 1 shows the S/UNI-APEX-1K800 in a mini-DSLAM application. The S/UNI-APEX-1K800 acts as a cell buffer and traffic manager. The S/UNI-ATLAS-1K800 provides address resolution and policing.

The mini-DSLAM application supports eight LIU devices per Line Card. Each xDSL modem is connected by its Utopia port to a FPGA which provides an interface to the AnyPhy bus. If Hot Swap capability is needed the bus signals need to be passed through switching or tristate drivers to isolate the card when being plugged in.

The FPGA performs the task of interfacing several 31 logical port Utopia bus signals to the single 128 logical port Any-PHY bus supported by the S/UNI-APEX-1K800.

ISSUE 2

ATM TRAFFIC MANAGER AND SWITCH

### 4 REFERENCES

- 1. PMC-Sierra; "Saturn Compatible Interface For ATM PHY Layer And ATM Layer Devices, Level 2"; PMC-940212; Dec. 8, 1995.

- 2. PMC-Sierra; DSLAM engineering document.

- 3. "Traffic Management And Switching With The Vortex Chip Set: S/UNI-APEX Technical Overview", PMC-981024.

- 4. ATM Forum, "Universal Test & Operations PHY Interface for ATM (UTOPIA), Level 2", Version 1.0, af-phy-0039.000, June 1995.

- 5. ITU-T Recommendation I.432.1, "B-ISDN user-network interface Physical layer specification: General characteristics", 08/96.

- 6. ITU-T Recommendation I.363, "B-ISDN ATM Adaptation Layer (AAL) Specification", March 1993.

- 7. AF Traffic Management Specification Version 4.1 AF-TM-0121.000, March 1999.

- 8. AF Traffic Management Baseline Text Document BTD-TM-01.01, April 1998.

- 9. I.610 OAM.

- 10. PMC Sierra, "Saturn Interface Specification and Interoperability Framework for Packet and Cell Transfer Between Physical Layer and Link Layer Devices", PMC980902.

- 11. PMC Sierra, "S/UNI APEX H/W Programmer's Guide", PMC-991454.

ISSUE 2

ATM TRAFFIC MANAGER AND SWITCH

#### 5 APPLICATION EXAMPLES

Please refer to the document "Traffic Management And Switching With The Vortex Chip Set: S/UNI-APEX Technical Overview", PMC-981024.

ISSUE 2

ATM TRAFFIC MANAGER AND SWITCH

#### 6 BLOCK DIAGRAM

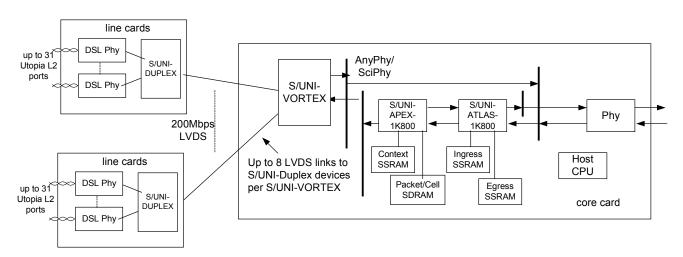

Figure 2 shows the function block diagram of the S/UNI-APEX-1K800 ATM traffic manager. The functional diagram is arranged such that cell traffic flows through the S/UNI-APEX-1K800 from left to right.

ISSUE 2

PM7329 S/UNI-APEX-1K800

DATASHEET PMC-2010141

ISSUE 2

ATM TRAFFIC MANAGER AND SWITCH

#### 7 DESCRIPTION

The PM7329 S/UNI-APEX-1K800 is a full duplex ATM traffic management device, providing cell switching, per VC queuing, traffic shaping, congestion management, and hierarchical scheduling to up to 128 loop ports and up to 4 WAN ports.

The S/UNI-APEX-1K800 provides per-VC queuing for 1024 VCs. A per-VC queue may be allocated to any Class of Service (COS), within any port, in either direction (ingress or egress path). Per-VC queuing enables PCR or SCR per-VC shaping on WAN ports and greater fairness of bandwidth allocation between VCs within a COS.

The S/UNI-APEX-1K800 provides three level hierarchical scheduling for port, COS, and VC level scheduling. There are two, three level schedulers; one for the loop ports and one for the WAN ports. The three level scheduler for the WAN ports provides:

- Weighted Interleaved Round Robin (WIRR) scheduling across the 4 WAN ports enabling selectability of bandwidth allocation between the ports.

- Priority Fair scheduling across the 4 COS's within each port. This class scheduler is a modified priority scheduler allowing minimum bandwidth allocations to lower priority classes within the port. Class scheduling within a port is independent of activity on all other ports.

- There are three types of VC schedulers. VC scheduling within a class is independent of activity on all other classes

- Shaped fair queuing is available for 4 classes. If the COS is shaped, each VC within the class is scheduled for emission based on its VCs shaping rate. During class congestion, the VC scheduler may lower a VCs rate in proportion to a normalization factor calculated as a function of the VCs rate and the aggregate rate of all active VCs within the class.

- Weighted Fair Queuing in which weights are used to provide fairness between the VCs within a class.

- Frame continuous scheduling where an entire packet is accumulated prior to transferring to a class queue.

The three-level scheduler for the loop ports provides:

• Weighted Interleaved Round Robin (WIRR) scheduling across the 128 loop ports enabling selectability of bandwidth allocation between the ports

DATASHEET PMC-2010141

and ensuring minimal PHY layer FIFOing is required to support a wide range of port bandwidths.

- Priority scheduling across the 4 COS's within each port. Class scheduling within a port is independent of activity on all other ports.

- VCs within a class are scheduled with a Weighted Fair Queue (WFQ) scheduler or Frame Continuous scheduling. VC scheduling within a class is independent of activity on all other classes. Shaping is not supported on loop ports.

The S/UNI-APEX-1K800 forwards cells via tail of queue enqueuing and head of queue dequeuing (emission) where tail of queue enqueuing is controlled by the VC context record and subject to congestion control, and head of queue dequeuing is controlled by the three-level hierarchical schedulers. The VC context record allows for enqueuing to any queue associated with any port, thus full switching is supported, any port to any port.

The S/UNI-APEX-1K800 supports up to 256k cells of shared buffering in a 32-bit wide SDRAM. Memory protection is provided via an inband CRC on a cell-by-cell basis. Buffering is shared across direction, port, class, and VC levels. The congestion control mechanism provides guaranteed resources to all active VCs, allows sharing of available resources to VCs with excess bandwidth, and restricts buffer allocation on a per-VC, per-class, per-port, and per-direction basis. The congestion control mechanism supports PPD and EPD on a CLP0 and CLP1 basis across per-VC, per-class, per-port, and per-direction structures. EFCI marking is supported on a per-VC basis. Congestion thresholds and packet awareness is selectable on a per connection basis.

The S/UNI-APEX-1K800 provides flexible capabilities for signaling, management, and control traffic. There are 4 independent uP receive queues to which both cell and AAL5 frame traffic may be en-queued for termination by the uP. A staging buffer is also provided enabling the uP to en-queue both cell and AAL5 frame traffic to any outgoing queue. AAL5 SAR assistance is provided for AAL5 frame traffic to and from the uP. AAL5 SAR assistance includes the generation and checking of the 32-bit CRC field and the ability to reassemble all the cells from a frame in the VC queue prior to placement on the uP queues. Any or all of the 1024 VCs may be configured to be routed to/from the uP port. Any or all of the VCs configured to be routed to/from the uP port may also be configured for AAL5 SAR assistance simultaneously. OAM cells may optionally (per-VC selectable) be routed to a uP receive queue or switched with the user traffic. CRC10 generation and checking is optionally provided on OAM cells to/from the uP.

The S/UNI-APEX-1K800 maintains cell counts of CLP0 and CLP1 cell transmits on a per-VC basis. Global CLP0 and CLP1 congestion discards are also

ATM TRAFFIC MANAGER AND SWITCH

maintained. Various error monitoring conditions and statistics are accumulated or flagged. The uP has access to both internal S/UNI-APEX-1K800 registers and the context memory as well as diagnostic access to the cell buffer memory.

The S/UNI-APEX-1K800 provides a 8/16-bit Any-PHY compliant loop side master/slave interface supporting up to 128 ports. Egress cell transfers across the interface are identified via an inband port identifier prepended to the cell. The slave devices must match the inband port identifier with their own port ID or port ID range in order to accept the cell. Per port egress flow control is effected via a 8-bit address polling bus to which the appropriate slave device responds with out of band per port flow control status. Ingress cell transfers across the interface are effected via a combination of UTOPIA L2 flow control polling and device selection for up to 32 slave devices. The Any-PHY loop side interface may be reconfigured as a standard single port UTOPIA L2 compliant slave interface. 16-bit prepends are optionally supported on both ingress and egress for cell flow identification enabling use with external address resolution devices, switch fabric interfaces, or other layer devices.

The S/UNI-APEX-1K800 provides an 8/16-bit Any-PHY or UTOPIA L2 compliant WAN side master/slave interface supporting up to 4 ports. 16-bit prepends are optionally supported on both ingress and egress for cell flow identification enabling use with external address resolution devices, switch fabric interfaces, or other layer devices. The WAN port has port aliasing on the egress, providing in service re-direction without requiring re-programming the context of active VCs.

The S/UNI-APEX-1K800 provides a 32-bit microprocessor bus interface for signaling, control, cell and frame message extraction and insertion, VC. Class and port context access, control and status monitoring, and configuration of the IC. Microprocessor burst access for registers, cell and frame traffic is supported.

The S/UNI-APEX-1K800 provides a 36-bit ZBT or late write SSRAM interface for context storage supporting up to 4MB of context for up to 1024 VCs and up to 256k cell buffer pointer storage. Context Memory protection is provided via 2 bits of parity over each 34-bit word.

The total number of cells, the total number of VCs, support for address mapping and shaped fair queuing is limited to the amount of context and cell buffer memory available. Below is a table illustrating the most common combinations of memory/features.

ATM TRAFFIC MANAGER AND SWITCH

| Table 2 | - Sample feature set as a function of memory capacity |

|---------|-------------------------------------------------------|

|---------|-------------------------------------------------------|

| Context<br>Memory Size<br>SSRAM | Cell Buffer<br>Memory Size<br>SDRAM | # VC | # Cell<br>Buffers | Address<br>Mapping<br>Support | Shaping<br>Support |

|---------------------------------|-------------------------------------|------|-------------------|-------------------------------|--------------------|

| 1 MB                            | 4MB                                 | 1024 | 64 K              | Yes                           | No                 |

| 2 MB                            | 4MB                                 | 1024 | 64 K              | Yes                           | Yes                |

| 2 MB                            | 16MB                                | 1024 | 256 K             | Yes                           | Yes                |

The S/UNI-APEX-1K800 provides facilities to enable sparing capability with another S/UNI-APEX-1K800 device. The facilities enable a 'warm standby' capability in which connection setup between the two devices can be maintained identically but some cell loss will occur at the point of device swapping. The facilities do not include a cell by cell lock step between the two S/UNI-APEX-1K800 devices. To avoid any cell replication, queues in the 'spare' S/UNI-APEX-1K800 will be kept empty, thus causing all queued traffic in the 'active' S/UNI-APEX-1K800 to be lost at the point of switch over. However, since connection setup is maintained identically between the two S/UNI-APEX-1K800 devices, switch over can happen instantaneously, thus avoiding any connection timeout or tear down issues.

The S/UNI-APEX-1K800 facilities provided are the disable and filter control bits in the Receive and Transmit Control register. These control bits are asserted in the spare S/UNI-APEX-1K800 to ensure the queues remain empty until swapping is initiated. Alternatively, asserting only the filter enable bits allow signaling and control traffic continuity to be maintained to the spare S/UNI-APEX-1K800 to enable datapath integrity testing on the spare plane and to ensure control communications paths to the spare plane are usable.

ISSUE 2

ATM TRAFFIC MANAGER AND SWITCH

#### 8 PIN DIAGRAM

The S/UNI-APEX-1K800 is packaged in a 352-pin ball grid array (SBGA) package having a body size of 35 mm by 35 mm.

ATM TRAFFIC MANAGER AND SWITCH

#### 9 PIN DESCRIPTION

#### Notes on Pin Description:

- 1. All S/UNI-APEX-1K800 inputs and bi-directionals present minimum capacitative loading

- 2. LVCMOS, LVTTL compatible logic levels.

- 3. All pins are 5V tolerant.

- 4. Inputs RSTB, OE, TMS, TDI and TRSTB have internal pull-up resistors.

- 5. The recommended power supply sequencing is as follows:

3.1 VDD power must be supplied either before or simultaneously with PCH.

3.2 The VDD power must be applied before input pins are driven or the input current per pin must be limited to less than the maximum DC input current specification. (20 mA)

3.3 Power down the device in the reverse sequence.

Table 3- Pin Type Definition

| Туре      | Definition                                     |

|-----------|------------------------------------------------|

| Input     | Input                                          |

| Output    | Pin is always driven                           |

| Tri-State | Pin is either driven, or held in Hi-Z          |

| BiDi      | Bidirectional                                  |

| OD        | Open drain. Either driven low or held in Hi-Z. |

## 9.1 Loop Any-PHY Receive Master/Transmit Slave Interface (28 Signals)

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                           |

|----------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LRCLK    | Input | K4         | <b>Loop Receive Clock.</b> LRCLK is used to transfer data blocks in the receive directions across the Any-PHY interface. LRCLK must cycle at a 52 MHz or lower instantaneous rate. |

ISSUE 2

| Pin Name                                                                             | Туре                 | Pin<br>No.                                                                                                                                                                                                                                                                                           | Function                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LRPA                                                                                 | Input<br>(Master)    | J3                                                                                                                                                                                                                                                                                                   | <b>Loop Receive Packet Available.</b> LRPA indicates whether at least one cell is queued for transfer in the selected PHY device.                                                                                                                                                                                                                                  |

|                                                                                      | Tri-state<br>(Slave) |                                                                                                                                                                                                                                                                                                      | This pin is in Hi-Z when the loop receive interface is not enabled.                                                                                                                                                                                                                                                                                                |

|                                                                                      |                      |                                                                                                                                                                                                                                                                                                      | If receive master mode is selected, this signal is an input. The selected PHY device drives LRPA with the cell availability status N LRCLK cycles after LRADR[5:0] matches the PHY device address. If the PHY device is a UTOPIA device, N=1. If the PHY device is an Any-PHY device, N=2. Assertion of LRPA indicates that at least one entire cell is available. |

| state output. The S<br>high 1 LRCLK after<br>programmed Loopl<br>high indicates that |                      | If transmit slave mode is selected, this signal is a tri-<br>state output. The S/UNI-APEX-1K800 drives LRPA<br>high 1 LRCLK after LRADR[5:0] matches the<br>programmed LoopRxSlaveAddr register. A logical<br>high indicates that the S/UNI-APEX-1K800 is<br>capable of accepting at least one cell. |                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                      |                      |                                                                                                                                                                                                                                                                                                      | LRPA is sampled/updated/Hi-Z'd on the rising edge of LRCLK.                                                                                                                                                                                                                                                                                                        |

ISSUE 2

| Pin Name | Туре                       | Pin<br>No.                                                                                                                                                                                                                                                                                             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LRENB    | Input<br>(Slave)<br>Output | (Slave)                                                                                                                                                                                                                                                                                                | <b>Loop Receive Enable.</b> The active low receive<br>enable (LRENB) signal is used to initiate the<br>transfer of a data block from the selected Physical<br>layer device to the S/UNI-APEX-1K800.                                                                                                                                                                                                                                                                                                       |

|          | (Master)                   |                                                                                                                                                                                                                                                                                                        | This pin is in Hi-Z when the loop receive interface is not enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |                            | output and the start of block transf<br>or 2 LRCLK cycles after device set<br>the PHY device is a UTOPIA device<br>PHY device is an Any-PHY device<br>selection occurs when the selected<br>is placed on LRADR[5:0] with LRE<br>followed by LRENB low in the next<br>LRENB is held low for M cycles wh | If receive master mode is selected, this signal is an output and the start of block transfer must occur 1 or 2 LRCLK cycles after device selection occurs. If the PHY device is a UTOPIA device, N=1. If the PHY device is an Any-PHY device, N=2. Device selection occurs when the selected device address is placed on LRADR[5:0] with LRENB held high followed by LRENB low in the next LRCLK period. LRENB is held low for M cycles where M is the number of 8 or 16-bit words in the block transfer. |

|          |                            |                                                                                                                                                                                                                                                                                                        | If transmit slave mode is selected, this signal is an input and LRDAT[15:0] word is accepted coincident with LRENB being sampled.                                                                                                                                                                                                                                                                                                                                                                         |

|          |                            |                                                                                                                                                                                                                                                                                                        | LRENB is sampled/updated on the rising edge of LRCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

ISSUE 2

| Pin Name                 | Туре                       | Pin<br>No.                 | Function                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

|--------------------------|----------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| LRADR[0]<br><br>LRADR[5] | Input<br>(Slave)<br>Output | G3<br>H4<br>F1<br>G2<br>H3 | <b>Loop Receive Address.</b> The LRADR[5:0] signals are used to address up to thirty two Physical layer devices for the purposes of polling and device selection.                                                                                                                                                                                               |                                                                            |

|                          | (Master)                   | G1                         | This pin is in Hi-Z when the loop receive interface is not enabled.                                                                                                                                                                                                                                                                                             |                                                                            |

|                          |                            |                            | If UL2 or Any-PHY receive master mode is selected,<br>these signals are outputs. LRADR[5:0] selects a<br>device for polling by applying the device address N<br>LRCLK cycles prior to sampling LRPA. If the PHY<br>device is a UTOPIA device, N=1. If the PHY device<br>is an Any-PHY device, N=2. LRADR will insert 1<br>NULL address between address changes. |                                                                            |

|                          |                            |                            |                                                                                                                                                                                                                                                                                                                                                                 | If UL1 master mode is selected, this bus is driven to a high NULL address. |

|                          |                            |                            |                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

|                          |                            |                            | LRADR[5:0] = 3F hex is used as the NULL address.<br>No PHY device can match the NULL address.                                                                                                                                                                                                                                                                   |                                                                            |

|                          |                            |                            | If transmit slave mode is selected, these signals are inputs. The S/UNI drives the LRPA 1 LRCLK after the LRADR[4:0] matches the programmed LoopRxSlaveAddr register, and LRADR[5] is zero.                                                                                                                                                                     |                                                                            |

|                          |                            |                            | LRADR[5:0] is sampled/updated or on the rising edge of LRCLK.                                                                                                                                                                                                                                                                                                   |                                                                            |

| LRSX                     | Input                      | K3                         | <b>Loop Receive Start of Transfer.</b> LRSX is asserted<br>by the selected PHY device during the first cycle of<br>a data block transfer coinciding with the port<br>address prepend. Required only during Any-PHY<br>mode.                                                                                                                                     |                                                                            |

|                          |                            |                            | For UTOPIA modes, this signal should be tied low.                                                                                                                                                                                                                                                                                                               |                                                                            |

|                          |                            |                            | LRSX is sampled on the rising edge of LRCLK.                                                                                                                                                                                                                                                                                                                    |                                                                            |

ISSUE 2

| Pin Name                  | Туре  | Pin<br>No.                                                                                                                                                                                                   | Function                                                                                                                                                                                                                                                                                                                                   |                                                     |

|---------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| LRSOP                     | Input | J2                                                                                                                                                                                                           | <b>Loop Receive Start of Packet</b> . LRSOP marks the start of the cell on the LRDAT[15:0] bus. When LRSOP is high, the first data word of the cell is present on the LRDAT[15:0] stream. If the selected device is an Any-PHY device, the LRSOP cycle will be preceded by the LRSX cycle marking the Any-PHY port address transfer cycle. |                                                     |

|                           |       |                                                                                                                                                                                                              | LRSOP considered valid only when the LRENB signal is low. LRSOP becomes high impedance upon sampling LRENB high or if no physical layer device was selected for transfer.                                                                                                                                                                  |                                                     |

|                           |       |                                                                                                                                                                                                              | LRSOP is sampled on the rising edge of LRCLK.                                                                                                                                                                                                                                                                                              |                                                     |

| LRDAT[0]<br><br>LRDAT[15] | Input | K2       t         L3       K1         K1       L2         M4       L         L1       L         M3       M2         M1       C         N3       C         P2       i         P3       P4         R1       L | <b>Loop Receive Data.</b> LRDAT[15:0] carries the transfer block words that have been read from the physical layer device to the S/UNI-APEX-1K800 internal cell buffers.                                                                                                                                                                   |                                                     |

|                           |       |                                                                                                                                                                                                              | LRDAT bus is considered valid only when the<br>LRENB signal was low N cycles previous. LRDAT is<br>expected to become high impedance N LRCLK<br>cycles after sampling LRENB high or upon<br>completion of a data block transfer. If the PHY<br>device is a UTOPIA device, N=1. If the PHY device<br>is an Any-PHY device, N=2.             |                                                     |

|                           |       |                                                                                                                                                                                                              | All 16 bits are used in 16-bit mode. In 8 bit mode,<br>LRDAT[15:8] should either be tied high or low, as<br>only the first 8 bits LTDAT[7:0] are valid.                                                                                                                                                                                    |                                                     |

|                           |       |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                            | LRDAT[15:0] is sampled on the rising edge of LRCLK. |

ISSUE 2

ATM TRAFFIC MANAGER AND SWITCH

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                      |

|----------|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LRPRTY   | Input | H1         | <b>Loop Receive Parity.</b> LRPRTY provides programmable odd/even parity of the LRDAT[15:0] bus.                                                                                                                                                                              |

|          |       |            | LRPRTY is considered valid only when the LRENB<br>signal was low N cycles previous. If the PHY device<br>is a UTOPIA device, N=1. If the PHY device is an<br>Any-PHY device, N=2. LRPRTY is expected to<br>become high impedance N LRCLK cycles after<br>sampling LRENB high. |

|          |       |            | A parity error is indicated by a status bit and a maskable interrupt.                                                                                                                                                                                                         |

|          |       |            | LRPRTY is sampled on the rising edge of LRCLK.                                                                                                                                                                                                                                |

## 9.2 Loop Any-PHY Transmit Master/Receive Slave Interface (34 Signals)

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                      |

|----------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTCLK    | Input | T25        | <b>Loop Transmit Clock.</b> LTCLK is used to transfer<br>data blocks in the transmit direction across the Any-<br>PHY interface. LTCLK must cycle at a 52 MHz or<br>lower instantaneous rate. |

ISSUE 2

| Pin Name                  | Туре                                   | Pin<br>No.                                                                 | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------|----------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

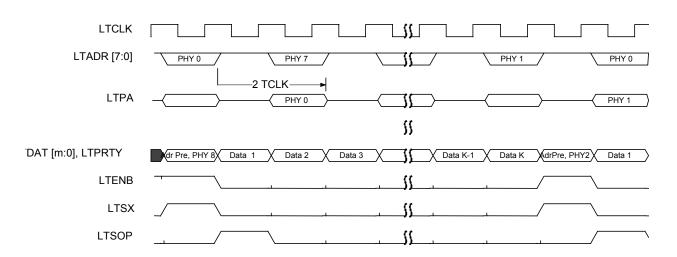

| LTADR[0]<br><br>LTADR[11] | Output<br>(Master)<br>Input<br>(Slave) | Y24<br>W23<br>AA26<br>Y25<br>W24<br>Y26<br>W25<br>V24<br>U23<br>W26<br>W25 | Loop Transmit Address. The LTADR[7:0] signals<br>are used to address up to 128 logical channels for<br>the purposes of polling on the LTPA signal. 1 or<br>more PHY devices can share the LTPA signal.<br>This pin is in Hi-Z when the loop transmit interface is<br>not enabled.<br>If transmit master mode is selected, these signals<br>are outputs. LTADR[7:0] selects a logical channel |

|                           |                                        | V25<br>U24                                                                 | for polling by applying the logical channel address N LTCLK cycles prior to sampling LTPA. If the PHY device is a UTOPIA device, N=1. If the PHY device is an Any-PHY device, N=2. LTADR inserts NULL cycles between addresses.                                                                                                                                                              |

|                           |                                        |                                                                            | For Any-PHY transmit master, LTADR[6:0] corresponds to the PORTID[6:0] fields in the Any-PHY address word prepend format.                                                                                                                                                                                                                                                                    |

|                           |                                        |                                                                            | For UTOPIA L2 transmit master, LTADR[4:0] is also used to select a UTOPIA device to transfer a cell to, when LTENB is last sampled high.                                                                                                                                                                                                                                                     |