#### TELECOMMUNICATION SYSTEM SECONDARY PROTECTION

## Ion-Implanted Breakdown Region Precise and Stable Voltage Low Voltage Overshoot under Surge

| DEVICE  | $V_{DRM}$ | V <sub>(BO)</sub> |

|---------|-----------|-------------------|

| DEVICE  | ٧         | ٧                 |

| '3125F3 | 100       | 125               |

| '3150F3 | 120       | 150               |

| '3180F3 | 145       | 180               |

## Planar Passivated Junctions Low Off-State Current < 10 μA</li>

### Rated for International Surge Wave Shapes

| WAVE SHAPE | STANDARD         | I <sub>TSP</sub><br>A |

|------------|------------------|-----------------------|

| 2/10 µs    | FCC Part 68      | 175                   |

| 8/20 µs    | ANSI C62.41      | 120                   |

| 10/160 µs  | FCC Part 68      | 60                    |

| 10/560 µs  | FCC Part 68      | 45                    |

| 0.5/700 µs | RLM 88           | 38                    |

|            | FTZ R12          | 50                    |

| 10/700 μs  | VDE 0433         | 50                    |

|            | CCITT IX K17/K20 | 50                    |

| 10/1000 μs | REA PE-60        | 35                    |

#### Surface Mount and Through-Hole Options

| PACKAGE             | PART # SUFFIX |

|---------------------|---------------|

| Small-outline       | D             |

| Small-outline taped | DR            |

| and reeled          | DIX           |

| Plastic DIP         | Р             |

| Single-in-line      | SL            |

#### UL Recognized, E132482

#### description

These medium voltage dual symmetrical transient voltage suppressor devices are designed to protect ISDN and telecommunication applications with ground backed ringing against transients caused by lightning strikes and a.c. power lines. Offered in three voltage variants to meet battery and protection requirements they are guaranteed to suppress and withstand the listed international lightning surges in both polarities. Transients are initially clipped by breakdown clamping until the voltage rises to the breakover level, which causes the device to

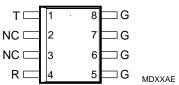

## D PACKAGE (TOP VIEW)

NC - No internal connection

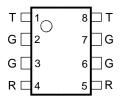

#### P PACKAGE (TOP VIEW)

MDXXAF

Specified T terminal ratings require connection of pins 1 and 8. Specified R terminal ratings require connection of pins 4 and 5.

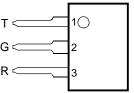

## SL PACKAGE (TOP VIEW)

MDXXAG MD23AA

### device symbol

Terminals T, R and G correspond to the alternative line designators of A, B and C

crowbar. The high crowbar holding current prevents d.c. latchup as the current subsides.

These monolithic protection devices are fabricated in ion-implanted planar structures to

MARCH 1994 - REVISED SEPTEMBER 1997

#### description (Continued)

ensure precise and matched breakover control and are virtually transparent to the system in normal operation

The small-outline 8-pin assignment has been carefully chosen for the TISP series to maximise the inter-pin clearance and creepage distances which are used by standards (e.g. IEC950) to establish voltage withstand ratings.

## absolute maximum ratings

| RATING                                                                                   |                  |                  | VALUE       | UNIT  |

|------------------------------------------------------------------------------------------|------------------|------------------|-------------|-------|

|                                                                                          | '3125F3          |                  | ± 100       |       |

| Repetitive peak off-state voltage (0°C < T <sub>J</sub> < 70°C)                          | '3150F3          | $V_{DRM}$        | ± 120       | V     |

|                                                                                          | '3180F3          |                  | ± 145       |       |

| Non-repetitive peak on-state pulse current (see Notes 1, 2 and 3)                        | •                |                  |             |       |

| 1/2 µs (Gas tube differential transient, open-circuit voltage wave shape                 | 1/2 µs)          |                  | 350         |       |

| 2/10 μs (FCC Part 68, open-circuit voltage wave shape 2/10 μs)                           |                  |                  | 175         |       |

| 8/20 μs (ANSI C62.41, open-circuit voltage wave shape 1.2/50 μs)                         |                  |                  | 120         |       |

| 10/160 μs (FCC Part 68, open-circuit voltage wave shape 10/160 μs)                       |                  |                  | 60          |       |

| 5/200 μs (VDE 0433, open-circuit voltage wave shape 2 kV, 10/700 μs)                     |                  | $I_{TSP}$        | 50          | Α     |

| 0.5/310 μs (RLM 88, open-circuit voltage wave shape 1.5 kV, 0.5/700 μ                    | s)               |                  | 38          |       |

| 5/310 μs (CCITT IX K17/K20, open-circuit voltage wave shape 2 kV, 10                     | /700 µs)         |                  | 50          |       |

| 5/310 μs (FTZ R12, open-circuit voltage wave shape 2 kV, 10/700 μs)                      |                  |                  | 50          |       |

| 10/560 μs (FCC Part 68, open-circuit voltage wave shape 10/560 μs)                       |                  |                  | 45          |       |

| 10/1000 μs (REA PE-60, open-circuit voltage wave shape 10/1000 μs)                       |                  |                  | 35          |       |

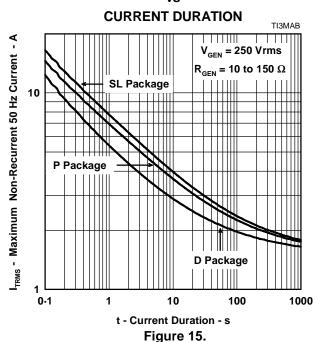

| Non-repetitive peak on-state current (see Notes 2 and 3)                                 | D Package        |                  | 4           |       |

| 50 Hz, 1 s P Package                                                                     |                  | I <sub>TSM</sub> | 6           | A rms |

|                                                                                          | SL Package       |                  | 6           |       |

| Initial rate of rise of on-state current, Linear current ramp, Maximum ramp value < 38 A |                  |                  | 250         | A/µs  |

| Junction temperature                                                                     |                  |                  | -40 to +150 | °C    |

| Storage temperature range                                                                | T <sub>stg</sub> | -40 to +150      | °C          |       |

- NOTES: 1. Further details on surge wave shapes are contained in the Applications Information section.

- Initially the TISP must be in thermal equilibrium with 0°C < T<sub>J</sub> <70°C. The surge may be repeated after the TISP returns to its initial

conditions.</li>

- 3. Above 70°C, derate linearly to zero at 150°C lead temperature.

## electrical characteristics for the T and R terminals, T<sub>J</sub> = 25°C

| PARAMETER        |                                       | TEST CONDITION                                       | vic.       | TISP3125F3 |     | ISP3125F3 TISP3 |     | TISP3 | TISP3180F3 |      |

|------------------|---------------------------------------|------------------------------------------------------|------------|------------|-----|-----------------|-----|-------|------------|------|

|                  | FANAMETEN                             | TEST CONDITION                                       | 10         | MIN        | MAX | MIN             | MAX | MIN   | MAX        | UNIT |

| I <sub>DRM</sub> | Repetitive peak off-<br>state current | $V_D = \pm 2V_{DRM}, 0^{\circ}C < T_J < 70^{\circ}C$ | ;          |            | ±10 |                 | ±10 |       | ±10        | μΑ   |

| I <sub>D</sub>   | Off-state current                     | V <sub>D</sub> = ±50 V                               |            |            | ±10 |                 | ±10 |       | ±10        | μA   |

|                  |                                       | $f = 100 \text{ kHz}, V_d = 100 \text{ mV}$          | D Package  | 50†        | 150 | 50†             | 150 | 50†   | 150        |      |

| $C_{off}$        | Off-state capacitance                 | $V_D = 0$ , (see Notes 4 and 5)                      | P Package  | 65†        | 200 | 65†             | 200 | 65†   | 200        | fF   |

|                  |                                       | Third terminal = -50 to +50 V                        | SL Package | 30†        | 100 | 30†             | 100 | 30†   | 100        |      |

NOTES: 4. These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The third terminal is connected to the guard terminal of the bridge.

<sup>5.</sup> Further details on capacitance are given in the Applications Information section.

<sup>†</sup> Typical value of the parameter, not a limit value.

## electrical characteristics for the T and G or the R and G terminals, $T_J$ = 25°C

|                   | PARAMETER                                  | TEST CONDITIONS                                                         | TISP3125F3 |       | TISP3125F3 TISP3 |       | TISP3150F3 TISP3180F3 |       | UNIT  |

|-------------------|--------------------------------------------|-------------------------------------------------------------------------|------------|-------|------------------|-------|-----------------------|-------|-------|

|                   | FARAMETER                                  | TEST CONDITIONS                                                         |            | MAX   | MIN              | MAX   | MIN                   | MAX   | ONII  |

| I <sub>DRM</sub>  | Repetitive peak off-<br>state current      | $V_D = \pm V_{DRM}, 0^{\circ}C < T_J < 70^{\circ}C$                     |            | ±10   |                  | ±10   |                       | ±10   | μΑ    |

| V <sub>(BO)</sub> | Breakover voltage                          | dv/dt = $\pm 250$ V/ms,<br>Source Resistance = $300 \Omega$             |            | ±125  |                  | ±150  |                       | ±180  | V     |

| V <sub>(BO)</sub> | Impulse breakover voltage                  | $dv/dt = \pm 1000 V/μs$ , $di/dt < 20 A/μs$<br>Source Resistance = 50 Ω |            | ±139† |                  | ±164† |                       | ±194† | V     |

| I <sub>(BO)</sub> | Breakover current                          | dv/dt = $\pm 250$ V/ms,<br>Source Resistance = $300 \Omega$             | ±0.15      | ±0.6  | ±0.15            | ±0.6  | ±0.15                 | ±0.6  | А     |

| V <sub>T</sub>    | On-state voltage                           | $I_T = \pm 5 \text{ A},  t_W = 100  \mu\text{s}$                        |            | ±3    |                  | ±3    |                       | ±3    | V     |

| I <sub>H</sub>    | Holding current                            | di/dt = -/+30  mA/ms                                                    | ±0.15      |       | ±0.15            |       | ±0.15                 |       | Α     |

| dv/dt             | Critical rate of rise of off-state voltage | Linear voltage ramp,  Maximum ramp value < 0.85V <sub>(BR)MIN</sub>     | ±5         |       | ±5               |       | ±5                    |       | kV/µs |

| I <sub>D</sub>    | Off-state current                          | $V_D = \pm 50 \text{ V}$                                                |            | ±10   |                  | ±10   |                       | ±10   | μA    |

|                   |                                            | $f = 100 \text{ kHz},  V_d = 100 \text{ mV}  V_D = 0,$                  | 55†        | 95    | 55†              | 95    | 55†                   | 95    | pF    |

| $C_{\text{off}}$  | Off-state capacitance                      | Third terminal = -50 to +50 V $V_D = -5 V$                              | 31†        | 50    | 31†              | 50    | 31†                   | 50    | pF    |

|                   |                                            | (see Notes 6 and 7) $V_D = -50 \text{ V}$                               | 15†        | 25    | 15†              | 25    | 15†                   | 25    | pF    |

NOTES: 6 These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The third terminal is connected to the guard terminal of the bridge.

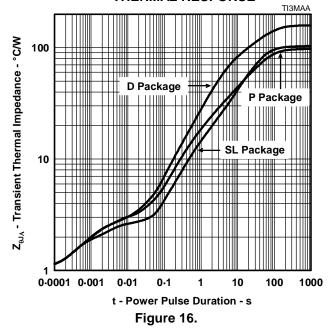

#### thermal characteristics

| PARAMETER       |                                         |            |  | TYP | MAX | UNIT |

|-----------------|-----------------------------------------|------------|--|-----|-----|------|

|                 |                                         | D Package  |  |     | 160 |      |

| $R_{\theta JA}$ | Junction to free air thermal resistance | P Package  |  |     | 100 | °C/W |

|                 |                                         | SL Package |  |     | 105 |      |

<sup>7.</sup> Further details on capacitance are given in the Applications Information section.

<sup>†</sup> Typical value of the parameter, not a limit value.

## PARAMETER MEASUREMENT INFORMATION

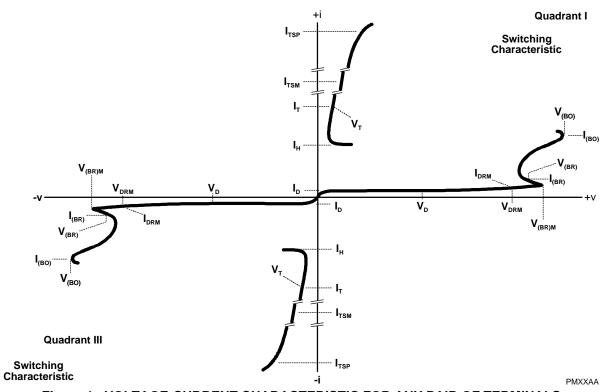

Figure 1. VOLTAGE-CURRENT CHARACTERISTIC FOR ANY PAIR OF TERMINALS

# **TYPICAL CHARACTERISTICS**

# T and G, or R and G terminals

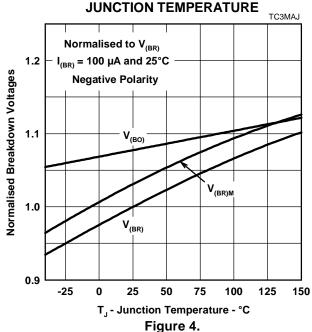

## JUNCTION TEMPERATURE ТСЗМАІ Normalised to $V_{(BR)}$ $I_{(BR)}$ = 100 $\mu A$ and 25°C 1.2 Normalised Breakdown Voltages **Positive Polarity** 1.1 $V_{(BO)}$ 1.0 V<sub>(BR)</sub> V<sub>(BR)M</sub> 0.9 -25 25 50 75 100 125 150 T<sub>J</sub> - Junction Temperature - °C Figure 3.

NORMALISED BREAKDOWN VOLTAGES

# TYPICAL CHARACTERISTICS T and G, or R and G terminals

## NORMALISED BREAKDOWN VOLTAGES

VS TEMPEDATURE

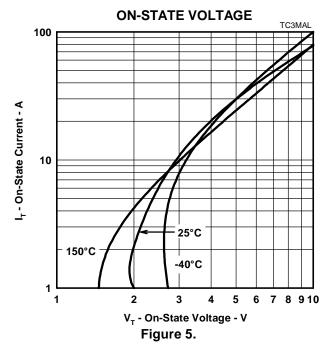

## **ON-STATE CURRENT**

VS

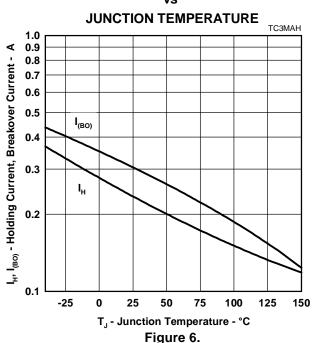

## **HOLDING CURRENT & BREAKOVER CURRENT**

VS

# TYPICAL CHARACTERISTICS T and G, or R and G terminals

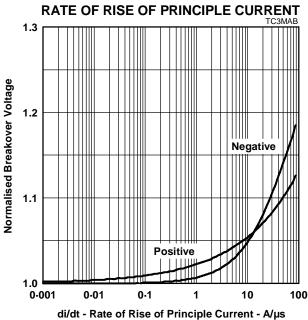

## NORMALISED BREAKOVER VOLTAGE

VS

Figure 7.

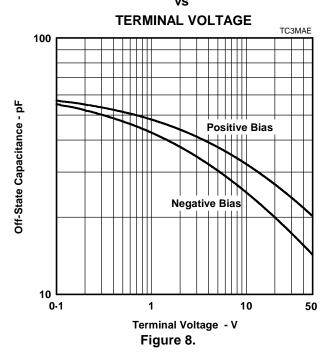

## **OFF-STATE CAPACITANCE**

vs

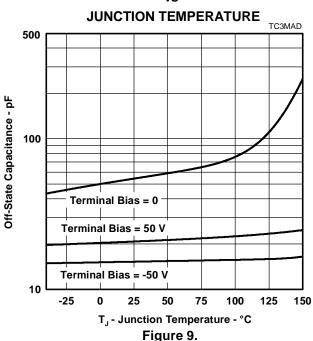

## **OFF-STATE CAPACITANCE**

VS

# TYPICAL CHARACTERISTICS T and G, or R and G terminals

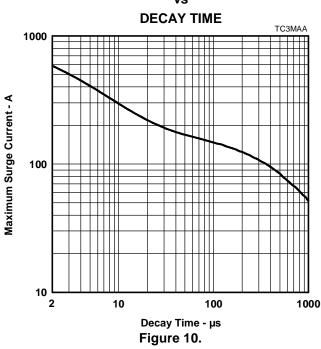

## **SURGE CURRENT**

vs

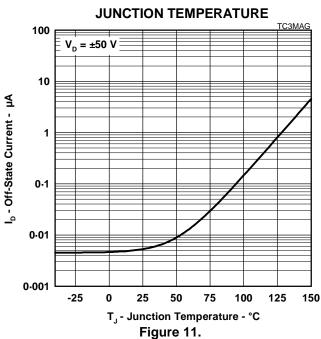

# TYPICAL CHARACTERISTICS T and R terminals

## **OFF-STATE CURRENT**

VS

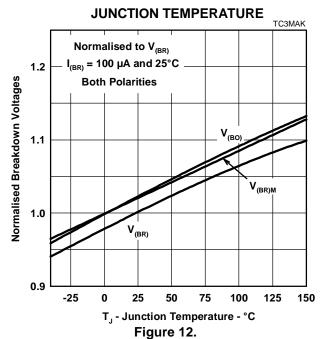

## **NORMALISED BREAKDOWN VOLTAGES**

VS

# TYPICAL CHARACTERISTICS T and R terminals

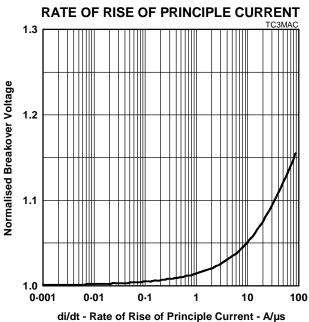

## NORMALISED BREAKOVER VOLTAGE

vs

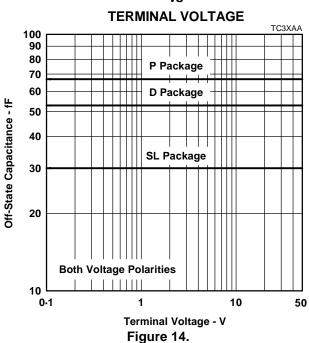

## OFF-STATE CAPACITANCE

VS

#### THERMAL INFORMATION

#### **MAXIMUM NON-RECURRING 50 Hz CURRENT**

Figure 13.

vs

#### THERMAL RESPONSE

MARCH 1994 - REVISED SEPTEMBER 1997

#### APPLICATIONS INFORMATION

## electrical characteristics

The electrical characteristics of a TISP are strongly dependent on junction temperature,  $T_J$ . Hence a characteristic value will depend on the junction temperature at the instant of measurement. The values given in this data sheet were measured on commercial testers, which generally minimise the temperature rise caused by testing. Application values may be calculated from the parameters' temperature curves, the power dissipated and the thermal response curve ( $Z_{\rm h}$ ).

#### lightning surge

### wave shape notation

Most lightning tests, used for equipment verification, specify a unidirectional sawtooth waveform which has an exponential rise and an exponential decay. Wave shapes are classified in terms of peak amplitude (voltage or current), rise time and a decay time to 50% of the maximum amplitude. The notation used for the wave shape is *amplitude*, *rise time/decay time*. A 50A,  $5/310 \, \mu s$  wave shape would have a peak current value of 50 A, a rise time of 5  $\mu s$  and a decay time of 310  $\mu s$ . The TISP surge current graph comprehends the wave shapes of commonly used surges.

#### generators

There are three categories of surge generator type, single wave shape, combination wave shape and circuit defined. Single wave shape generators have essentially the same wave shape for the open circuit voltage and short circuit current (e.g.  $10/1000~\mu s$  open circuit voltage and short circuit current). Combination generators have two wave shapes, one for the open circuit voltage and the other for the short circuit current (e.g.  $1.2/50~\mu s$  open circuit voltage and  $8/20~\mu s$  short circuit current) Circuit specified generators usually equate to a combination generator, although typically only the open circuit voltage waveshape is referenced (e.g.  $a 10/700~\mu s$  open circuit voltage generator typically produces a  $a 5/310~\mu s$  short circuit current). If the combination or circuit defined generators operate into a finite resistance the wave shape produced is intermediate between the open circuit and short circuit values.

#### current rating

When the TISP switches into the on-state it has a very low impedance. As a result, although the surge wave shape may be defined in terms of open circuit voltage, it is the current wave shape that must be used to assess the required TISP surge capability. As an example, the CCITT IX K17 1.5 kV,  $10/700~\mu s$  surge is changed to a 38 A,  $5/310~\mu s$  waveshape when driving into a short circuit. Thus the TISP surge current capability, when directly connected to the generator, will be found for the CCITT IX K17 waveform at 310  $\mu s$  on the surge graph and not 700  $\mu s$ . Some common short circuit equivalents are tabulated below:

| STANDARD                     | OPEN CIRCUIT<br>VOLTAGE              | SHORT CIRCUIT<br>CURRENT         |

|------------------------------|--------------------------------------|----------------------------------|

| CCITT IX K17<br>CCITT IX K20 | 1.5 kV, 10/700 μs<br>1 kV, 10/700 μs | 38 A, 5/310 μs<br>25 A, 5/310 μs |

| RLM88                        | 1.5 kV, 0.5/700 μs                   | 38 A, 0.2/310 µs                 |

| VDE 0433                     | 2.0 kV, 10/700 µs                    | 50 A, 5/200 µs                   |

| FTZ R12                      | 2.0 kV, 10/700 µs                    | 50 A, 5/310 µs                   |

Any series resistance in the protected equipment will reduce the peak circuit current to less than the generators' short circuit value. A 2 kV open circuit voltage, 50 A short circuit current generator has an effective output impedance of 40  $\Omega$  (2000/50). If the equipment has a series resistance of 25  $\Omega$  then the surge current requirement of the TISP becomes 31 A (2000/65) and not 50 A.

#### APPLICATIONS INFORMATION

#### protection voltage

The protection voltage,  $(V_{(BO)})$ , increases under lightning surge conditions due to thyristor regeneration. This increase is dependent on the rate of current rise, di/dt, when the TISP is clamping the voltage in its breakdown region. The  $V_{(BO)}$  value under surge conditions can be estimated by multiplying the 50 Hz rate  $V_{(BO)}$  (250 V/ms) value by the normalised increase at the surge's di/dt (Figure 7.) . An estimate of the di/dt can be made from the surge generator voltage rate of rise, dv/dt, and the circuit resistance.

As an example, the CCITT IX K17 1.5 kV,  $10/700~\mu s$  surge has an average dv/dt of 150 V/ $\mu s$ , but, as the rise is exponential, the initial dv/dt is higher, being in the region of 450 V/ $\mu s$ . The instantaneous generator output resistance is 25  $\Omega$ . If the equipment has an additional series resistance of 20  $\Omega$ , the total series resistance becomes 45  $\Omega$ . The maximum di/dt then can be estimated as  $450/45 = 10~A/\mu s$ . In practice the measured di/dt and protection voltage increase will be lower due to inductive effects and the finite slope resistance of the TISP breakdown region.

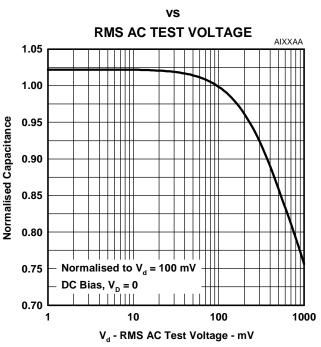

#### capacitance

#### off-state capacitance

The off-state capacitance of a TISP is sensitive to junction temperature,  $T_J$ , and the bias voltage, comprising of the dc voltage,  $V_D$ , and the ac voltage,  $V_d$ . All the capacitance values in this data sheet are measured with an ac voltage of 100 mV. The typical 25°C variation of capacitance value with ac bias is shown in Figure 17. When  $V_D >> V_d$  the capacitance value is independent on the value of  $V_d$ . The capacitance is essentially constant over the range of normal telecommunication frequencies.

#### NORMALISED CAPACITANCE

Figure 17.

#### APPLICATIONS INFORMATION

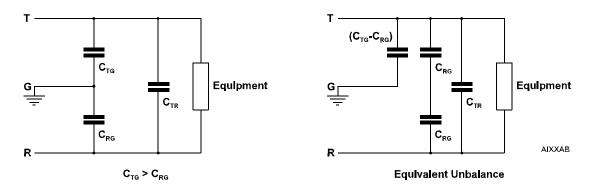

## longitudinal balance

Figure 18 shows a three terminal TISP with its equivalent "delta" capacitance Each capacitance,  $C_{TG}$ ,  $C_{RG}$  and  $C_{TR}$ , is the true terminal pair capacitance measured with a three terminal or guarded capacitance bridge. If wire R is biased at a larger potential than wire T then  $C_{TG} > C_{RG}$ . Capacitance  $C_{TG}$  is equivalent to a capacitance of  $C_{RG}$  in parallel with the capacitive difference of  $(C_{TG} - C_{RG})$ . The line capacitive unbalance is due to  $(C_{TG} - C_{RG})$  and the capacitance shunting the line is  $C_{TR} + C_{RG}/2$ .

Figure 18.

All capacitance measurements in this data sheet are three terminal guarded to allow the designer to accurately assess capacitive unbalance effects. Simple two terminal capacitance meters (unguarded third terminal) give false readings as the shunt capacitance via the third terminal is included.

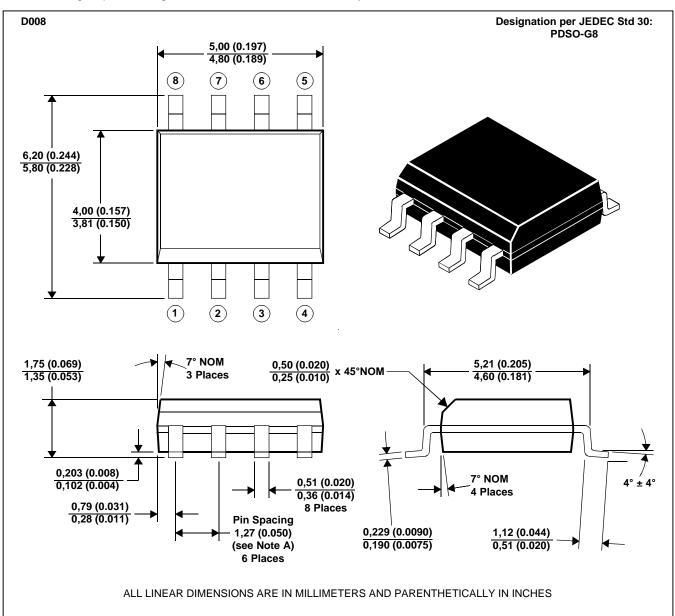

#### **MECHANICAL DATA**

#### **D008**

## plastic small-outline package

This small-outline package consists of a circuit mounted on a lead frame and encapsulated within a plastic compound. The compound will withstand soldering temperature with no deformation, and circuit performance characteristics will remain stable when operated in high humidity conditions. Leads require no additional cleaning or processing when used in soldered assembly.

MDXXAA

- NOTES: A. Leads are within 0,25 (0.010) radius of true position at maximum material condition.

- B. Body dimensions do not include mold flash or protrusion.

- C. Mold flash or protrusion shall not exceed 0,15 (0.006).

- D. Lead tips to be planar within  $\pm 0,051$  (0.002).

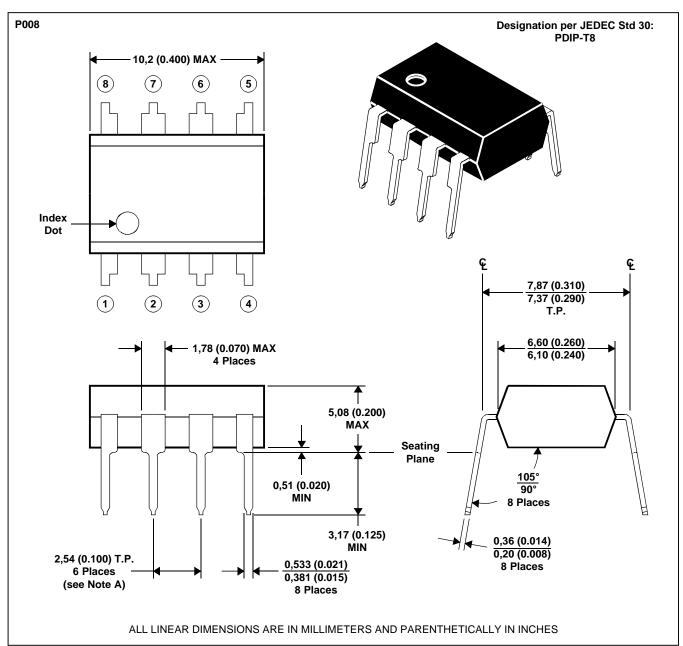

#### **MECHANICAL DATA**

#### P008

## plastic dual-in-line package

This dual-in-line package consists of a circuit mounted on a lead frame and encapsulated within a plastic compound. The compound will withstand soldering temperature with no deformation, and circuit performance characteristics will remain stable when operated in high humidity conditions. The package is intended for insertion in mounting-hole rows on 7,62 (0.300) centers. Once the leads are compressed and inserted, sufficient tension is provided to secure the package in the board during soldering. Leads require no additional cleaning or processing when used in soldered assembly.

NOTE A: Each pin centerline is located within 0,25 (0.010) of its true longitudinal position

MDXXABA

#### **MECHANICAL DATA**

#### **SL003**

## 3-pin plastic single-in-line package

This single-in-line package consists of a circuit mounted on a lead frame and encapsulated within a plastic compound. The compound will withstand soldering temperature with no deformation, and circuit performance characteristics will remain stable when operated in high humidity conditions. Leads require no additional cleaning or processing when used in soldered assembly.

NOTES: A. Each pin centerline is located within 0,25 (0.010) of its true longitudinal position.

B. Body molding flash of up to 0,15 (0.006) may occur in the package lead plane.

MDXXAD

MARCH 1994 - REVISED SEPTEMBER 1997

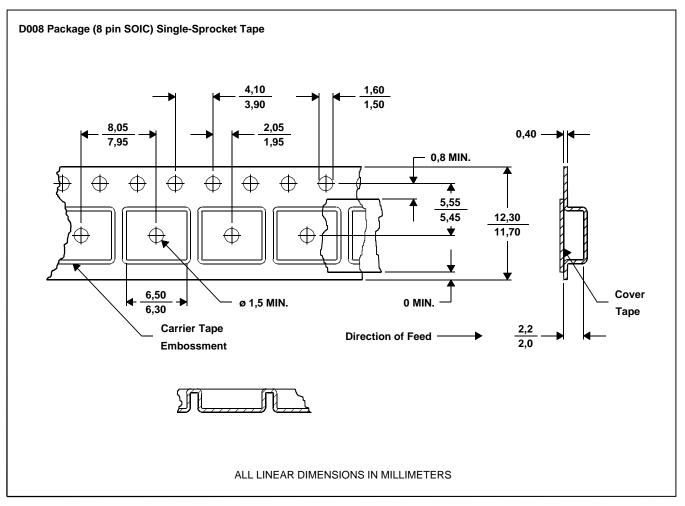

## **MECHANICAL DATA**

#### D008

## tape dimensions

NOTES: A. Taped devices are supplied on a reel of the following dimensions:-

MDXXAT

Reel diameter: 330 +0,0/-4,0 mm Reel hub diameter: 100  $\pm$ 2,0 mm Reel axial hole: 13,0  $\pm$ 0,2 mm

B. 2500 devices are on a reel.

MARCH 1994 - REVISED SEPTEMBER 1997

#### **IMPORTANT NOTICE**

Power Innovations Limited (PI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to verify, before placing orders, that the information being relied on is current.

PI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with PI's standard warranty. Testing and other quality control techniques are utilized to the extent PI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except as mandated by government requirements.

PI accepts no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor is any license, either express or implied, granted under any patent right, copyright, design right, or other intellectual property right of PI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

PI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS.

Copyright © 1997, Power Innovations Limited