PRODUCT INFORMATION

### **Description**

The Raytheon RMLA3565-58 is a single bias wideband low noise MMIC amplifier that meets the following specifications over the 3.5 - 6.5 GHz frequency range. The MMIC requires no external matching circuits no external gate bias supply. This device uses Raytheon's advanced  $0.25~\mu m$  PHEMT process to provide low noise, high linearity and low current.

#### **Features**

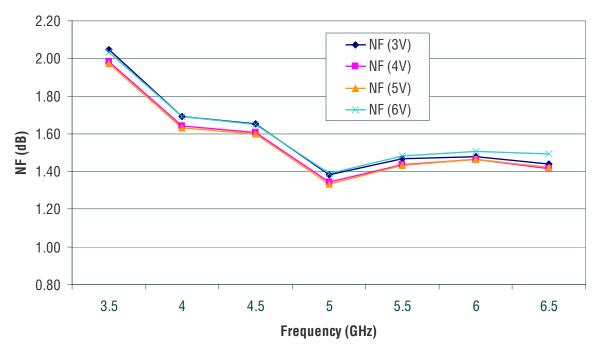

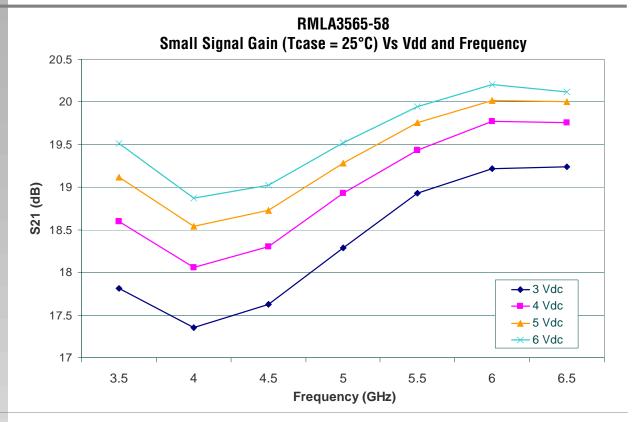

- ◆ 19.0 dB Gain Typical

- ◆ 1.5 dB Noise Figure, Typical 5.0 6.5 GHz

- Single Positive Bias

- Small Outline Metal Base Quad Plastic Package

- Internal 50Ω Matching

### Absolute Maximum Ratings<sup>1</sup>

| Parameter                               | Symbol  | Value      | Unit |

|-----------------------------------------|---------|------------|------|

| Positive Drain DC Voltage (No RF)       | Vdd     | 6.5        | V    |

| RF Input Power (from $50\Omega$ source) | Pin(CW) | 0          | dBm  |

| Drain Current                           | ldd     | 130        | mA   |

| Case Operating Temperature              | Tc      | -35 to 85  | °C   |

| Storage Temperature Range               | Tstg    | -40 to 110 | °C   |

| Soldering Temperature                   | Tsolder | 220        | °C   |

## Electrical Characteristics<sup>2</sup>

| Parameter                                         | Min  | Тур        | Max        | Unit     |

|---------------------------------------------------|------|------------|------------|----------|

| Frequency Range                                   | 3.5  |            | 6.5        | GHz      |

| Gain (Small Signal)3,4                            | 17.0 | 19.0       |            | dB       |

| Gain Variation vs Temp                            |      | -0.008     |            | dB/°C    |

| Noise Figure <sup>4</sup> 3.5 - 5 GHz 5 - 6.5 GHz | 0.0  | 1.4<br>1.5 | 2.2<br>1.6 | dB<br>dB |

| Power Out, P1dB @ 5.5 GHz                         | 8.0  | 10.0       |            | dBm      |

| Parameter                                   | Min | Тур   | Max  | Unit |

|---------------------------------------------|-----|-------|------|------|

| OIP3 @ 5.5 GHz, +3 dBm<br>Pout total        | 17  | 21.0  |      | dBm  |

| Idd                                         |     | 70.0  | 85.0 | mA   |

| Vdd                                         | 3.0 | 4.0   | 6.0  | V    |

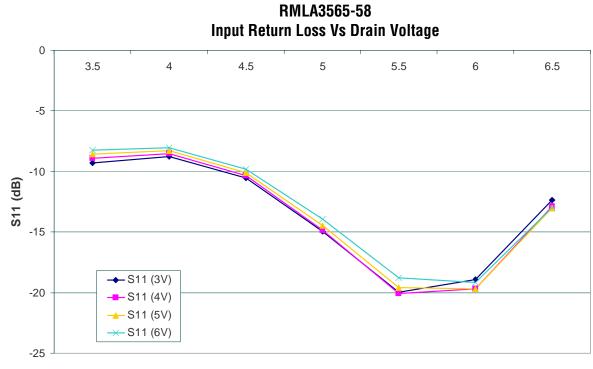

| Input Return Loss                           |     | -15.0 |      | dB   |

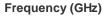

| Output Return Loss                          |     | -10.0 |      | dB   |

| Thermal Resistance Rjc<br>(Channel to Case) |     | 135   |      | °C/W |

#### Notes

- 1. No permanent damage with only one parameter set at maximum limit and all other parameters at typical conditions

- 2. All parameters met at Tc = +25 °C, Vdd = 4.0V

- 3. Pin = -20 dBm, Vdd = 4.0 V, Frequency 3.5 6.5 GHz

- 4. Data de-embedded from fixture loss

PRODUCT INFORMATION

### **Application Information**

#### **CAUTION: THIS IS AN ESD SENSITIVE DEVICE**

The following briefly describes a procedure for evaluating the high efficiency PHEMT amplifier packaged in a surface mount package. It may be noted that the chip is a fully monolithic single ended two stage amplifier for 3.5 to 6.5 GHz applications.

#### **Test Fixture**

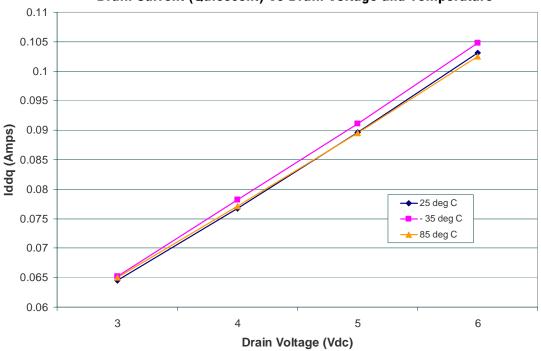

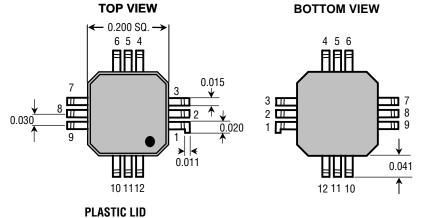

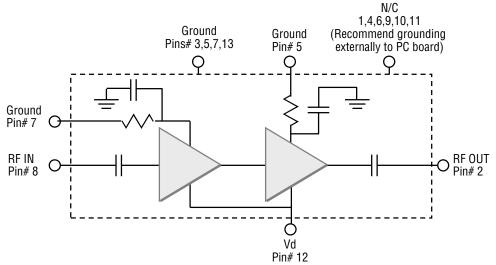

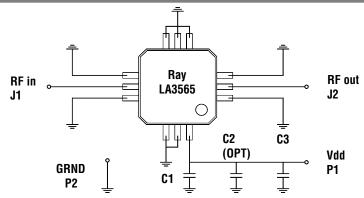

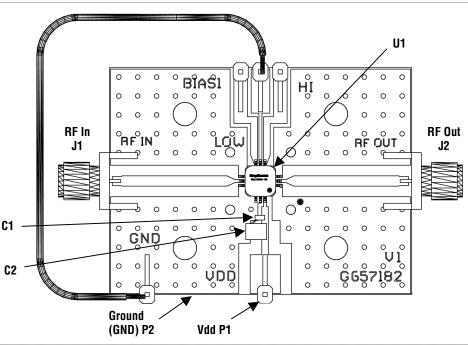

Figure 1 shows the outline and pin-out descriptions for the packaged device. Figure 2 shows the functional block diagram of the packaged product. A typical test fixture schematic showing external bias components is shown in figure 3. Figure 4 shows typical layout of an evaluation board corresponding to the schematic diagram. A typical performance obtained from the test fixture is shown in figure 5. The following should be noted:

- (1) Package pin designations are as shown in figure 1.

- (2) Vd is the Drain Voltage (positive) applied at the pins of the package

- (3) Vdd is the positive supply voltage at the evaluation board terminal

Figure 1

Package Outline and

Pin Designations

Dimensions in inches

| Pin# | Description    |  |

|------|----------------|--|

| 1    | N/C            |  |

| 2    | RF Out         |  |

| 3    | GND            |  |

| 4    | N/C            |  |

| 5    | GND            |  |

| 6    | N/C            |  |

| 7    | GND            |  |

| 8    | RF In          |  |

| 9    | N/C            |  |

| 10   | N/C            |  |

| 11   | N/C            |  |

| 12   | Vd             |  |

| 13   | GND            |  |

|      | (Package Base) |  |

Figure 2

Functional Block

Diagram

PRODUCT INFORMATION

Figure 3 Schematic for a Typical Test Evaluation Board (RMLA3565-58-TB)

Figure 4 Layout and Assembly of Test Evaluation Board (RMLA3565-58-TB)

### **Test Procedure**

The following sequence of procedure must be followed to properly test the power amplifier:

for the evaluation board (RMLA3565-58-TB)

**Step 1:** Turn off RF input power.

Step 2: Use GND terminal of the evaluation board for

DC supplies.

**Step 3:** Apply drain supply voltages of +4.0 V to

evaluation board terminal Vdd.

**Step 4:** After the bias condition is established, RF input signal may now be applied.

Step 5: Follow turn-off sequence of:

(i) Turn off RF Input Power

(ii) Turn down and off Vdd

#### Parts List

for Test Evaluation Board (RMLA3565-58-TB)

| Part   | Value          | EIA Size          | Vendor(s)                  |

|--------|----------------|-------------------|----------------------------|

| C1     | 330 pF         | .04" x .02"       | AVX, Murata, Novacap,      |

| C2     | 4.75 uF        | .14"x .11"        | Sprague, ATC, AVX, Murata, |

| U1     | RMLA3565-58    | .28" x .28" x .07 | Raytheon                   |

| P1, P2 | Terminal       |                   | Samtec                     |

| J1, J2 | SMA Connectors |                   | E.F. Johnson               |

| Board  | R04003(Rogers) | 1.99x1.50x.032    | Raytheon                   |

PRODUCT INFORMATION

### Performance Data

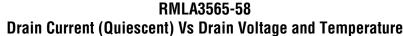

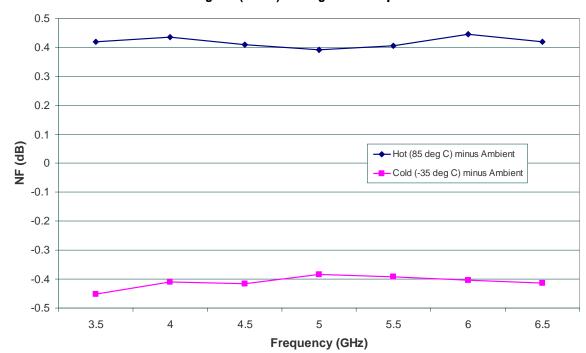

RMLA3565-58

Noise Figure (4Vdc) Change Vs Temperature

PRODUCT INFORMATION

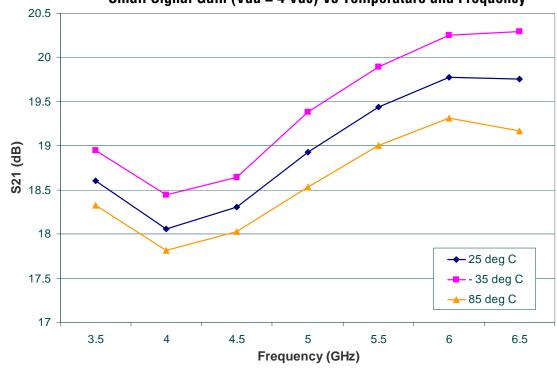

### Performance Data

RMLA3565-58

Small Signal Gain (Vdd = 4 Vdc) Vs Temperature and Frequency

PRODUCT INFORMATION

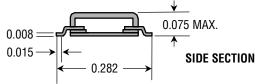

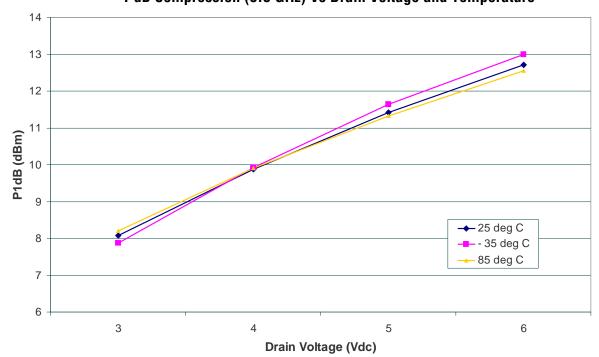

### Performance Data

PRODUCT INFORMATION

### Performance Data

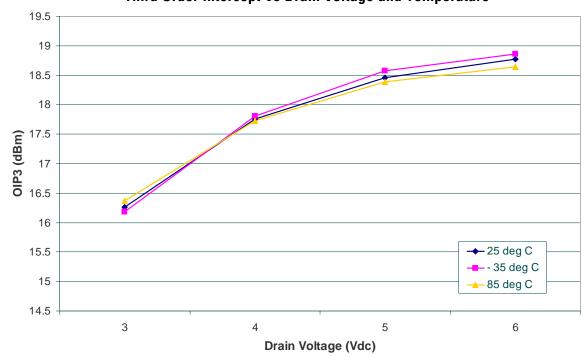

RMLA3565-58

Third Order Intercept Vs Drain Voltage and Temperature

PRODUCT INFORMATION

Performance Data