#### TRANSMIT MODULATOR, IF AGC, AND **UPCONVERTER**

#### Typical Applications

- CDMA/FM Cellular Systems

- CDMA PCS Systems

- GSM/DCS Systems

- TDMA Systems

- Spread Spectrum Cordless Phones

- Wireless Local Loop Systems

#### **Product Description**

The RF2658 is an integrated complete Quadrature Modulator, IF AGC amplifier, and Upconverter developed for the transmit section of dual-mode CDMA/FM cellular and PCS applications and for GSM/DCS and TDMA systems. It is designed to modulate baseband I and Q signals, amplify the resulting IF signals while providing 95dB of gain control range, and perform the final upconversion to UHF. Noise Figure, IP3, and other specifications are designed to be compatible with the IS-98 Interim Standard for CDMA cellular communications. This circuit is part of RFMD's line of complete solutions for digital radio applications. The IC is manufactured on an advanced 15GHz F<sub>T</sub> Silicon Bipolar process, and is supplied in a 28-lead plastic SSOP package.

Optimum Technology Matching® Applied

▼ Si BJT ☐ GaAs HBT GaAs MESFET ☐ SiGe HBT ☐ Si Bi-CMOS ☐ Si CMOS

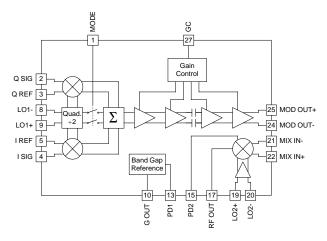

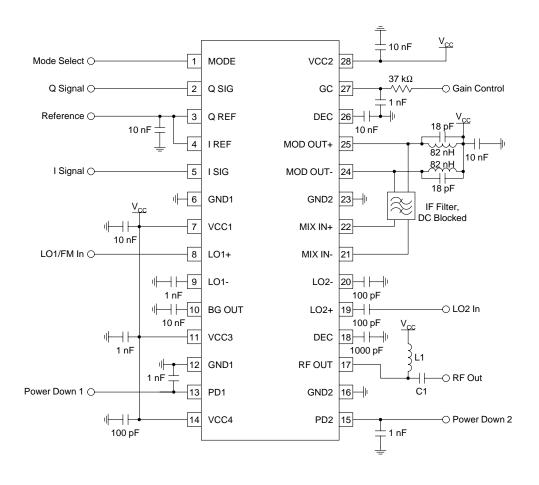

Functional Block Diagram

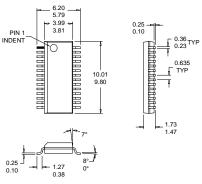

- NOTES:

1. Shaded lead is Pin1.

2. Lead frame material: Copper 194

3. Mold flash shall not exceed 0.006 (0.15 mm) per end.

4. Interlead flash shall not exceed 0.010 (0.25 mm) per sidd

5. All dimensions are excluding mold flash and protrusions.

Package Style: QSOP-28

#### **Features**

- Similar to RF9958 with increased IF range

- Supports Dual Mode Operation

- Digitally Controlled Power Down Modes

- 2.7 V to 3.3 V Operation

- Double-Balanced UHF Upconvert Mixer

- IF AGC Amp with 95 dB Gain Control

#### Ordering Information

RF2658 Transmit Modulator, IF AGC, and Upconverter RF2658 PCBA Fully Assembled Evaluation Board

RF Micro Devices, Inc. Tel (336) 664 1233 7628 Thorndike Road Fax (336) 664 0454 Greensboro, NC 27409, USA http://www.rfmd.com

## **RF2658**

#### **Absolute Maximum Ratings**

| Parameter                             | Rating                        | Unit     |  |  |  |

|---------------------------------------|-------------------------------|----------|--|--|--|

| Supply Voltage                        | -0.5 to +5                    | $V_{DC}$ |  |  |  |

| Power Down Voltage (V <sub>PD</sub> ) | -0.5 to V <sub>CC</sub> + 0.7 | V        |  |  |  |

| I and Q Levels, per pin               | 1                             | $V_{PP}$ |  |  |  |

| LO1 Level, balanced                   | +3                            | dBm      |  |  |  |

| LO2 Level, balanced                   | +6                            | dBm      |  |  |  |

| Operating Ambient Temperature         | -40 to +85                    | °C       |  |  |  |

| Storage Temperature                   | -40 to +150                   | °C       |  |  |  |

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Parameter                                       | Specification        |             | Unit | Condition |                                                                       |

|-------------------------------------------------|----------------------|-------------|------|-----------|-----------------------------------------------------------------------|

| Farameter                                       | Min.                 | Тур.        | Max. | Offic     | Condition                                                             |

|                                                 |                      |             |      |           | T=25 °C, $V_{CC}$ =3.0 V, $Z_{LOAD}$ =50 Ω,<br>LO1 =-8 dBm @ 260 MHz, |

| I/Q Modulator & AGC                             |                      |             |      |           | LO2=-3dBm@960MHz.                                                     |

| I/Q INICIDITATION & ACC                         |                      |             |      |           | I SIG=Q SIG=300mV <sub>PP</sub>                                       |

|                                                 |                      |             |      |           | RF Output externally matched                                          |

| I/Q Input Frequency Range                       |                      | 0 to 20     |      | MHz       | Balanced                                                              |

| I/Q Input Impedance                             | 50                   | 80          | 110  | kΩ        | Balanced                                                              |

| I/Q Input Reference Level                       |                      | 0.6         |      | $V_{DC}$  | Per Pin                                                               |

| LO1/FM Frequency Range                          |                      | 240 to 600  |      | MHz       |                                                                       |

| LO1/FM Input Level                              | -15                  | -8          | -5   | dBm       |                                                                       |

| LO1/FM Input Impedance                          | 170                  | 200         | 230  | Ω         | Balanced                                                              |

| Sideband Suppression                            | 35                   | 40          |      | dBc       | I/Q Amplitude adjusted to within ±20 mV                               |

|                                                 |                      | 30          |      | dBc       | Unadjusted                                                            |

| Carrier Suppression                             | 40                   | 50          |      | dBc       | I/Q DC Offset adjusted to within ±20 mV                               |

|                                                 |                      | 30          |      | dBc       | Unadjusted                                                            |

| Max Output, FM Mode                             | +2.5                 | +4          |      | dBm       | $V_{GC}=2.5 V_{DC}$                                                   |

| Max Output, CDMA Mode                           | -3                   | 0           |      | dBm       | $V_{GC}=2.5 V_{DC}$                                                   |

| Min Output, CDMA Mode                           |                      | -95         | -89  | dBm       | $V_{GC}=0.5 V_{DC}$                                                   |

| Adjacent Channel Power Rejec-                   |                      | -55         |      | dBc       | IS-95A CDMA Modulation                                                |

| tion @ 885kHz                                   |                      |             |      |           | P <sub>OUT</sub> =-5dBm                                               |

| Adjacent Channel Power Rejec-                   |                      | -67         |      | dBc       | IS-95A CDMA Modulation                                                |

| tion @ 1.98MHz                                  |                      |             |      |           | P <sub>OUT</sub> =-5dBm                                               |

| Output Noise Power                              |                      | -116        | -111 | dBm/Hz    | P <sub>OUT</sub> =-3 dBm                                              |

| Output Noise Power                              |                      | -164        | -159 | dBm/Hz    | P <sub>OUT</sub> < -70 dBm                                            |

| Output Power Accuracy                           | -3                   |             | +3   | dB        | T=-20 to +85 °C, Ref=25 °C                                            |

| Output Impedance                                | 170                  | 200         | 230  | Ω         | Balanced                                                              |

| UHF Upconverter                                 |                      |             |      |           | Output externally matched                                             |

| Conversion Gain                                 | -1                   | 0.5         |      | dB        |                                                                       |

| Noise Figure (SSB)                              |                      | 15          |      | dB        |                                                                       |

| Output IP3                                      |                      | +14         |      | dBm       |                                                                       |

| IF Input Impedance                              | 170                  | 200         | 230  | Ω         | Balanced                                                              |

| IF Input Frequency Range                        |                      | 120 to 300  |      | MHz       |                                                                       |

| LO2 Input Impedance                             |                      | 50          |      | Ω         | Single Ended                                                          |

| LO2 Input Level                                 | -6                   | -3          | 0    | dBm       |                                                                       |

| LO2 Input Frequency Range                       |                      | 700 to 1100 |      | MHz       |                                                                       |

| RF to LO2 Isolation                             |                      | 20          |      | dB        |                                                                       |

| Power Supply                                    | 0.7                  | 0.0         | 0.0  |           |                                                                       |

| Supply Voltage                                  | 2.7                  | 3.0         | 3.3  | 4         | Mark later and ACC and a CDMAR                                        |

| Current Consumption                             |                      | 43          |      | mA<br>m ^ | Modulator and AGC only, CDMA Mode                                     |

| Current Consumption                             |                      | 20          | 20   | mA<br>    | Mixer Only                                                            |

| Power Down Current V <sub>PD</sub> HIGH Voltage | V <sub>CC</sub> -0.7 |             | 20   | μΑ        |                                                                       |

| 1                                               | VCC-0.7              |             | 0.5  |           |                                                                       |

| V <sub>PD</sub> LOW Voltage                     |                      |             | 0.5  |           |                                                                       |

5-62 Rev A8 010720

| Dia |           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Interfere Calcametic         |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Pin | Function  | Description Selects between CDMA and EM mode. This is a digitally controlled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Interface Schematic          |

| 1   | MODE      | Selects between CDMA and FM mode. This is a digitally controlled input. A logic "high" ( $\geq$ V <sub>CC</sub> -0.7V <sub>DC</sub> ) selects CDMA mode. A logic "low" ( $\geq$ 0.5V <sub>DC</sub> ) selects FM mode. In FM mode, this switch enables the FM amplifier and turns off the I&Q modulator. The impedance on this pin is $30k\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BIAS 60 kΩ 60 kΩ MODE        |

| 2   | Q SIG     | Baseband input to the Q mixer. This pin is DC coupled. The DC level of 0.6V must be supplied to this pin to bias the transistor. Input impedance of this pin is $50 \text{k}\Omega$ minimum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BIAS BIAS  8 kQ  9 SIG       |

| 3   | Q REF     | Reference voltage for the Q mixer. This voltage should be the same as the DC voltage supplied to the Q SIG pin. For maximum carrier suppression, DC voltage on this pin relative to the Q SIG DC voltage may be adjusted. Input impedance of this pin is $50\mathrm{k}\Omega$ minimum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | See pin 2.                   |

| 4   | I REF     | Reference voltage for the I mixer. This voltage should be the same as the DC voltage supplied to the I SIG pin. For maximum carrier suppression, DC voltage on this pin relative to the I SIG DC voltage may be adjusted. Input impedance of this pin is $50 \text{k}\Omega$ minimum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | See pin 5.                   |

| 5   | I SIG     | Baseband input to the I mixer. This pin is DC coupled. The DC level of 0.6V must be supplied to this pin to bias the transistor. Input impedance of this pin is $50  k\Omega$ minimum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BIAS BIAS  8 kΩ  8 kΩ  1 SIG |

| 6   | GND1      | Ground connection for all baseband circuits including bandgap, AGC, flip-flop, modulator and FM amp. Keep traces physically short and connect immediately to ground plane for best performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                              |

| 7   | VCC1      | Supply voltage for the LO1 flip-flop and limiting amp only. This supply is isolated to minimize the carrier leakage. A 1nF external bypass capacitor is required, and an additional $0.1\mu F$ will be required if no other low frequency bypass capacitors are nearby. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane. The part is designed to work from 2.7V to 3.3V supply.                                                                                                                                                                                                                                                                                                            |                              |

| 8   | LO1+, FM+ | One half of the balanced modulator LO1 input. The other half of the input, LO1-, is AC grounded for single-ended input applications. The frequency on these pins is divided by a factor of 2, hence the carrier frequency for the modulator becomes one half of the applied frequency. The single-ended input impedance is $100\Omega$ (balanced is $200\Omega$ ). This pin is NOT internally DC blocked. An external blocking capacitor (1nF recommended) must be provided if the pin is connected to a device with DC present. When FM mode is selected, the output of the flip-flop divider circuit is switched to the AGC amplifier inputs and the modulator mixers are not used. Note that the frequency deviation input here will be reduced by a factor of two, due to the frequency divider operation. | V <sub>CC</sub>              |

| 9   | LO1-, FM- | One half of the balanced modulator LO1 input. In single-ended applications (100 $\!\Omega$ input impedance), this pin is AC grounded with a 1 nF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | See pin 8.                   |

| 10  | BG OUT    | Bandgap voltage reference. This voltage, constant over temperature and supply variation, is used to bias internal circuits. A 1 nF external bypass capacitor is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |

## RF2658

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Interface Schematic                         |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 11  | VCC3     | Supply voltage for the AGC and the Bandgap circuitry. A 1nF external bypass capacitor is required and an additional 0.1µF will be required if no other low frequency bypass capacitors are nearby. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane. The part is designed to work from 2.7V to 3.3V supply.                                                                                           |                                             |

| 12  | GND1     | Same as pin 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |

| 13  | PD1      | Power down control for overall circuit. When logic "high" ( $\geq$ V <sub>CC</sub> -0.7V), all circuits are operating; when logic "low" ( $<$ 0.5V), all circuits are turned off. The input impedance of this pin is >10k $\Omega$ .                                                                                                                                                                                                                                                                                     | PD1 Ο 10 kΩ                                 |

| 14  | VCC4     | Supply for the mixer stage only. The supply for the mixer is separated to maximize IF to RF isolations and reduce the carrier leakage. A 100 pF external bypass capacitor is required and an additional $0.1\mu F$ will be required if no other low frequency bypass capacitors are near by. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane. The part is designed to work from 2.7V to 3.3V supply. |                                             |

| 15  | PD2      | Power down control for mixer only. When connected to pin 10 (BG OUT) the mixer circuits are operating; when connected to ground (≤0.5 V), the mixer is turned off but all other circuits are operating.                                                                                                                                                                                                                                                                                                                  | PD2 Ο 1 kΩ                                  |

| 16  | GND2     | Ground connection for the mixer stage. Keep traces physically short and connect immediately to ground plane for best performance.                                                                                                                                                                                                                                                                                                                                                                                        |                                             |

| 17  | RF OUT   | RF output pin. An external shunt inductor to $V_{CC}$ plus a series blocking/matching capacitor are required for $50\Omega$ output.                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>CCs</sub><br>§300 Ω<br>RF OUT        |

| 18  | DEC      | Current mirror decoupling pin. A 1000pF external capacitor is required to bypass this pin. The ground side of the bypass capacitors should connect immediately to ground plane.                                                                                                                                                                                                                                                                                                                                          |                                             |

| 19  | LO2+     | One half of the balanced mixer LO2 input. In single-ended applications, the other half of the input, LO2- is AC grounded. This is a $50\Omega$ impedance port. This pin is NOT internally DC blocked. An external blocking capacitor (100pF recommended) must be provided if the pin is connected to a device with DC present.                                                                                                                                                                                           | BIAS BIAS                                   |

| 20  | LO2-     | One half of the balance mixer LO2 input. In single ended applications, this pin is AC grounded with a 100pF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                   | See pin 19.                                 |

| 21  | MIX IN-  | One half of the $200\Omega$ balanced impedance input to the mixer stage. This pin is NOT internally DC blocked. An external blocking capacitor (2200 pF recommended) must be provided if the pin is connected to a device with DC present. If no IF filter is needed, this pin may be connected to MOD OUT+ through a DC blocking capacitor. An appropriate matching network may be needed if an IF filter is used.                                                                                                      | BIAS BIAS  \$100 Ω \$100 Ω  MIX IN- MIX IN- |

| 22  | MIX IN+  | Same as pin 21, except complementary input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | See pin 21.                                 |

5-64 Rev A8 010720

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interface Schematic                                                           |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 23  | GND2     | Same as pin 16.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                               |

| 24  | MOD OUT- | One half of the balanced AGC output port. The impedance of this port is $200\Omega$ balanced. If no filtering is required, this pin can be connected to the MIX IN- pin through a DC blocking capacitor. This pin requires an inductor to $V_{CC}$ to achieve full dynamic range. In order to maximize gain, this inductor should be a high-Q type and should be parallel resonated out with a capacitor (see application schematic). This pin is NOT DC blocked. A blocking capacitor of 2200pF is needed when this pin is connected to a DC path. An appropriate matching network may be needed if an IF filter is used. | V <sub>CC3</sub> V <sub>CC3</sub><br>\$100 Ω<br>\$100 Ω<br>MOD OUT-  MOD OUT- |

| 25  | MOD OUT+ | Same as pin 24, except complementary output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | See pin 24.                                                                   |

| 26  | DEC      | AGC decoupling pin. An external bypass capacitor of 10nF capacitor is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.                                                                                                                                                                                                                                                                                                                                                                       |                                                                               |

| 27  | GC       | Analog gain control for AGC amplifiers. Valid control voltage ranges are from $0.5 V_{DC}$ to $2.5 V_{DC}.$ The gain range for the AGC is 88dB. These voltages are valid ONLY for a $37k\Omega$ source impedance.                                                                                                                                                                                                                                                                                                                                                                                                          | BIAS \$21 kΩ \$40 kΩ \$\$                                                     |

| 28  | VCC2     | Supply for the modulator stage only. A 10nF external bypass capacitor is required and an additional 0.1µF will be required if no other low frequency bypass capacitors are nearby. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane. The part is designed to work from 2.7V to 3.3V supply.                                                                                                                                                                                                             |                                                                               |

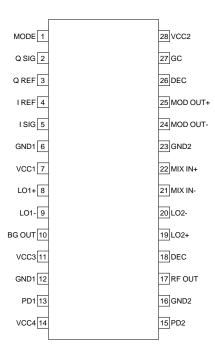

#### RF2658 Pin-Out

5-66 Rev A8 010720

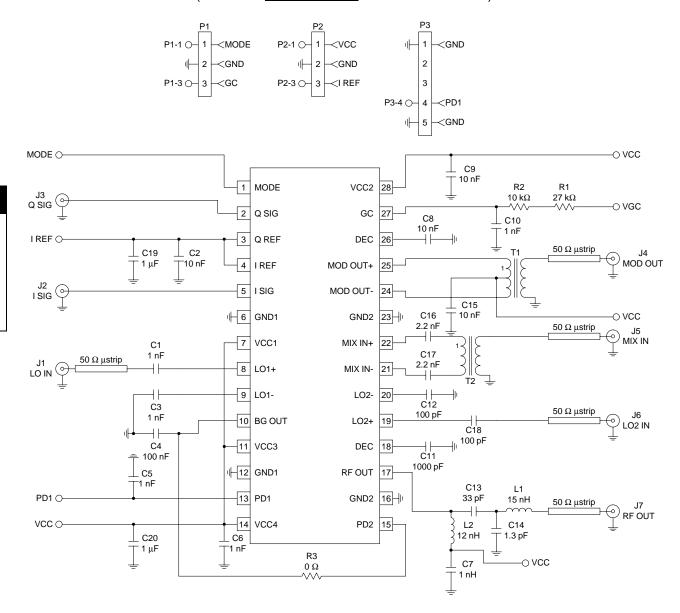

### **Application Schematic**

## **RF2658**

#### **Evaluation Board Schematic**

(Download Bill of Materials from www.rfmd.com.)

5-68 Rev A8 010720

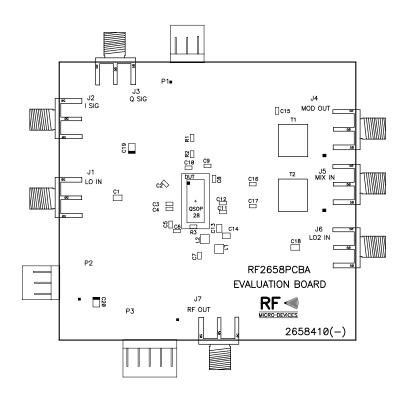

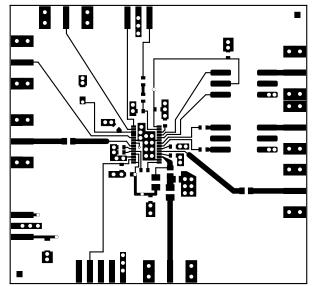

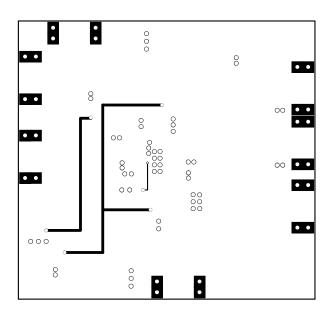

# Evaluation Board Layout Board Size 2.689" x 2.521"

5-70 Rev A8 010720